Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 3022                                                        |

| Number of Logic Elements/Cells | 60440                                                       |

| Total RAM Bits                 | 2544192                                                     |

| Number of I/O                  | 364                                                         |

| Number of Gates                | -                                                           |

| Voltage - Supply               | 1.15V ~ 1.25V                                               |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 780-BBGA                                                    |

| Supplier Device Package        | 780-FBGA (29x29)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2sgx60df780c3n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

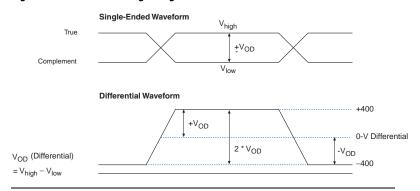

Differential signaling conventions are shown in Figure 2–9. The differential amplitude represents the value of the voltage between the true and complement signals. Peak-to-peak differential voltage is defined as 2 × (V<sub>HIGH</sub> – V<sub>LOW</sub>) = 2 × single-ended voltage swing. The common mode voltage is the average of  $V_{high}$  and  $V_{low}$

Figure 2-9. Differential Signaling

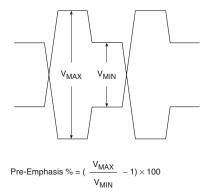

#### **Programmable Pre-Emphasis**

The programmable pre-emphasis module controls the output driver to boost the high frequency components, and compensate for losses in the transmission medium, as shown in Figure 2–10. The pre-emphasis is set statically using the ALT2GXB megafunction or dynamically through the dynamic reconfiguration controller.

Figure 2-10. Pre-Emphasis Signaling

- Lane deskew

- Rate matcher

- 8B/10B decoder

- Byte deserializer

- Byte ordering

- Receiver phase compensation FIFO buffer

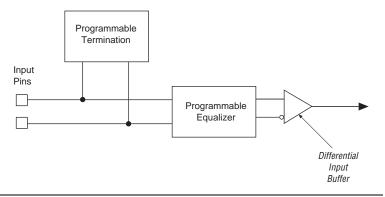

## Receiver Input Buffer

The Stratix II GX receiver input buffer supports the 1.2-V and 1.5-V PCML I/O standard at rates up to 6.375 Gbps. The common mode voltage of the receiver input buffer is programmable between 0.85 V and 1.2 V. You must select the 0.85 V common mode voltage for AC- and DC-coupled PCML links and the 1.2 V common mode voltage for DC-coupled LVDS links.

The receiver has programmable on-chip 100-, 120-, or 150- $\Omega$  differential termination for different protocols, as shown in Figure 2–12. The receiver's internal termination can be disabled if external terminations and biasing are provided. The receiver and transmitter differential termination resistances can be set independently of each other.

Figure 2–12. Receiver Input Buffer

#### Programmable Termination

The programmable termination can be statically set in the Quartus II software. Figure 2–13 shows the setup for programmable receiver termination. The termination can be disabled if external termination is provided.

The receiver PLL can also drive the regional clocks and regional routing adjacent to the associated transceiver block. Figure 2–30 shows which global clock resource can be used by the recovered clock. Figure 2–31 shows which regional clock resource can be used by the recovered clock.

CLK[15..12] 11 5 Stratix II GX GCLK[15..12] Transceiver Block GCLK[3..0] GCLK[11..8] CLK[3..0] Stratix II GX Transceiver Block GCLK[4..7] 8 12 6 CLK[7..4]

Figure 2–30. Stratix II GX Receiver PLL Recovered Clock to Global Clock Connection Notes (1), (2)

Notes to Figure 2-30:

- (1) CLK# pins are clock pins and their associated number. These are pins for global and regional clocks.

- (2) GCLK# pins are global clock pins.

Figure 2-36. Stratix II GX ALM Details

|            | Destination             |             |                |                    |                          |                 |                  |                 |                  |     |                |               |             |            |            |         |

|------------|-------------------------|-------------|----------------|--------------------|--------------------------|-----------------|------------------|-----------------|------------------|-----|----------------|---------------|-------------|------------|------------|---------|

| Source     | Shared Arithmetic Chain | Carry Chain | Register Chain | Local Interconnect | Direct Link Interconnect | R4 Interconnect | R24 Interconnect | C4 Interconnect | C16 Interconnect | ALM | M512 RAM Block | M4K RAM Block | M-RAM Block | DSP Blocks | Column 10E | Bow IOE |

| Column IOE |                         |             |                |                    | <b>✓</b>                 |                 |                  | <b>✓</b>        | <b>✓</b>         |     |                |               |             |            |            |         |

| Row IOE    |                         |             |                |                    | /                        | /               | /                | /               |                  |     |                |               |             |            |            |         |

# TriMatrix Memory

TriMatrix memory consists of three types of RAM blocks: M512, M4K, and M-RAM. Although these memory blocks are different, they can all implement various types of memory with or without parity, including true dual-port, simple dual-port, and single-port RAM, ROM, and FIFO buffers. Table 2–19 shows the size and features of the different RAM blocks.

| Table 2–19. TriMatrix Memo   | ry Features (Part 1 of 2)        |                                  |                                |

|------------------------------|----------------------------------|----------------------------------|--------------------------------|

| Memory Feature               | M512 RAM Block<br>(32 × 18 Bits) | M4K RAM Block<br>(128 × 36 Bits) | M-RAM Block<br>(4K × 144 Bits) |

| Maximum performance          | 500 MHz                          | 550 MHz                          | 420 MHz                        |

| True dual-port memory        |                                  | <b>✓</b>                         | <b>✓</b>                       |

| Simple dual-port memory      | ✓                                | <b>✓</b>                         | ✓                              |

| Single-port memory           | ✓                                | ✓                                | ✓                              |

| Shift register               | ✓                                | ✓                                |                                |

| ROM                          | ✓                                | <b>✓</b>                         | (1)                            |

| FIFO buffer                  | ✓                                | <b>✓</b>                         | <b>✓</b>                       |

| Pack mode                    |                                  | <b>✓</b>                         | <b>✓</b>                       |

| Byte enable                  | ✓                                | ✓                                | ✓                              |

| Address clock enable         |                                  | ✓                                | ✓                              |

| Parity bits                  | <b>✓</b>                         | ✓                                | ✓                              |

| Mixed clock mode             | <b>✓</b>                         | <b>✓</b>                         | <b>✓</b>                       |

| Memory initialization (.mif) | ✓                                | <b>✓</b>                         |                                |

Table 2–20 shows the input and output data signal connections along with the address and control signal input connections to the row unit interfaces (L0 to L5 and R0 to R5).

| Table 2–20. M-RAM    | Row Interface Unit Signals                                              |                 |

|----------------------|-------------------------------------------------------------------------|-----------------|

| Unit Interface Block | Input Signals                                                           | Output Signals  |

| L0                   | datain_a[140]<br>byteena_a[10]                                          | dataout_a[110]  |

| L1                   | datain_a[2915]<br>byteena_a[32]                                         | dataout_a[2312] |

| L2                   | datain_a[3530] addressa[40] addr_ena_a clock_a clocken_a renwe_a aclr_a | dataout_a[3524] |

| L3                   | addressa[155]<br>datain_a[4136]                                         | dataout_a[4736] |

| L4                   | datain_a[5642]<br>byteena_a[54]                                         | dataout_a[5948] |

| L5                   | datain_a[7157]<br>byteena_a[76]                                         | dataout_a[7160] |

| R0                   | datain_b[140]<br>byteena_b[10]                                          | dataout_b[110]  |

| R1                   | datain_b[2915]<br>byteena_b[32]                                         | dataout_b[2312] |

| R2                   | datain_b[3530] addressb[40] addr_ena_b clock_b clocken_b renwe_b aclr_b | dataout_b[3524] |

| R3                   | addressb[155]<br>datain_b[4136]                                         | dataout_b[4736] |

| R4                   | datain_b[5642]<br>byteena_b[54]                                         | dataout_b[5948] |

| R5                   | datain_b[7157]<br>byteena_b[76]                                         | dataout_b[7160] |

Refer to the *TriMatrix Embedded Memory Blocks in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II GX Device Handbook* for more information on TriMatrix memory.

The connections to the global and regional clocks from the top clock pins and enhanced PLL outputs are shown in Table 2–28. The connections to the clocks from the bottom clock pins are shown in Table 2–29.

| Table 2–28. Global and Reg<br>(Part 1 of 2)                   | ional (  | Clock (  | Connec   | ctions   | from T   | Top Clo  | ock Pi   | ns and   | l Enha   | nced F   | PLL Ou   | ıtputs   |          |

|---------------------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Top Side Global and<br>Regional Clock Network<br>Connectivity | DLLCLK   | CLK12    | CLK13    | CLK14    | CLK15    | RCLK24   | RCLK25   | RCLK26   | RCLK27   | RCLK28   | RCLK29   | RCLK30   | RCLK31   |

| Clock pins                                                    | •        |          |          |          |          |          |          |          | •        |          |          | •        |          |

| CLK12p                                                        | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| CLK13p                                                        | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| CLK14p                                                        | <b>✓</b> |          |          | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| CLK15p                                                        | <b>✓</b> |          |          | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| CLK12n                                                        |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| CLK13n                                                        |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| CLK14n                                                        |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| CLK15n                                                        |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| Drivers from internal logic                                   |          |          |          |          |          |          |          |          | •        |          |          |          |          |

| GCLKDRV0                                                      |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |          |          |

| GCLKDRV1                                                      |          |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |          |

| GCLKDRV2                                                      |          |          |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |

| GCLKDRV3                                                      |          |          |          |          | <b>✓</b> |          |          |          |          |          |          |          |          |

| RCLKDRV0                                                      |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| RCLKDRV1                                                      |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| RCLKDRV2                                                      |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| RCLKDRV3                                                      |          |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| RCLKDRV4                                                      |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| RCLKDRV5                                                      |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| RCLKDRV6                                                      |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| RCLKDRV7                                                      |          |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| Enhanced PLL5 outputs                                         |          |          |          |          |          |          |          |          |          |          |          |          |          |

| c0                                                            | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| c1                                                            | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

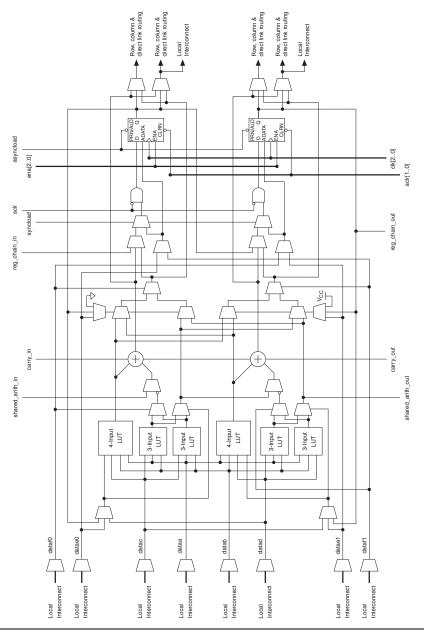

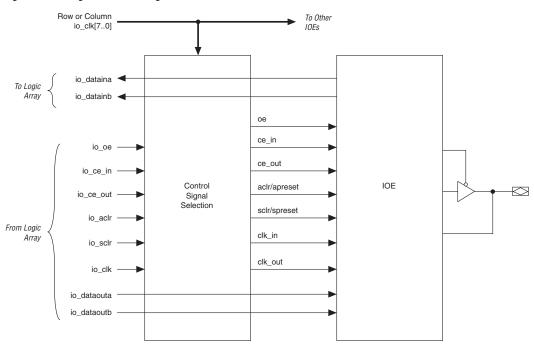

There are 32 control and data signals that feed each row or column I/O block. These control and data signals are driven from the logic array. The row or column IOE clocks, io\_clk [7..0], provide a dedicated routing resource for low-skew, high-speed clocks. I/O clocks are generated from global or regional clocks. Refer to "PLLs and Clock Networks" on page 2–89 for more information.

Figure 2–79 illustrates the signal paths through the I/O block.

Figure 2-79. Signal Path Through the I/O Block

Each IOE contains its own control signal selection for the following control signals: oe, ce\_in, ce\_out, aclr/apreset, sclr/spreset, clk\_in, and clk\_out. Figure 2–80 illustrates the control signal selection.

A path in which a pin directly drives a register can require the delay to ensure zero hold time, whereas a path in which a pin drives a register through combinational logic may not require the delay. Programmable delays exist for decreasing input-pin-to-logic-array and IOE input register delays. The Quartus II Compiler can program these delays to automatically minimize setup time while providing a zero hold time. Programmable delays can increase the register-to-pin delays for output and/or output enable registers. Programmable delays are no longer required to ensure zero hold times for logic array register-to-IOE register transfers. The Quartus II Compiler can create the zero hold time for these transfers. Table 2–30 shows the programmable delays for Stratix II GX devices.

| Table 2–30. Stratix II GX Programma          | ble Delay Chain                          |

|----------------------------------------------|------------------------------------------|

| Programmable Delays                          | Quartus II Logic Option                  |

| Input pin to logic array delay               | Input delay from pin to internal cells   |

| Input pin to input register delay            | Input delay from pin to input register   |

| Output pin delay                             | Delay from output register to output pin |

| Output enable register t <sub>CO</sub> delay | Delay to output enable pin               |

The IOE registers in Stratix II GX devices share the same source for clear or preset. You can program preset or clear for each individual IOE. You can also program the registers to power up high or low after configuration is complete. If programmed to power up low, an asynchronous clear can control the registers. If programmed to power up high, an asynchronous preset can control the registers. This feature prevents the inadvertent activation of another device's active-low input upon power-up. If one register in an IOE uses a preset or clear signal, all registers in the IOE must use that same signal if they require preset or clear. Additionally, a synchronous reset signal is available for the IOE registers.

#### Double Data Rate I/O Pins

Stratix II GX devices have six registers in the IOE, which support DDR interfacing by clocking data on both positive and negative clock edges. The IOEs in Stratix II GX devices support DDR inputs, DDR outputs, and bidirectional DDR modes. When using the IOE for DDR inputs, the two input registers clock double rate input data on alternating edges. An input latch is also used in the IOE for DDR input acquisition. The latch holds the data that is present during the clock high times, allowing both bits of data to be synchronous with the same clock edge (either rising or falling). Figure 2–82 shows an IOE configured for DDR input. Figure 2–83 shows the DDR input timing diagram.

| Table 2-42. Docu                                        | ment Revision History (Part 5 of 6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                     |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| Date and<br>Document<br>Version                         | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Summary of Changes                                                                  |

| Previous Chapter<br>02 changes:<br>June 2006, v1.2      | <ul> <li>Updated notes 1 and 2 in Figure 2–1.</li> <li>Updated "Byte Serializer" section.</li> <li>Updated Tables 2–4, 2–7, and 2–16.</li> <li>Updated "Programmable Output Driver" section.</li> <li>Updated Figure 2–12.</li> <li>Updated "Programmable Pre-Emphasis" section.</li> <li>Added Table 2–11.</li> <li>Added "Dynamic Reconfiguration" section.</li> <li>Added "Calibration Block" section.</li> <li>Updated "Programmable Equalizer" section, including addition of Figure 2–18.</li> </ul> | Updated input frequency range in Table 2–4.                                         |

| Previous Chapter<br>02 changes:<br>April 2006, v1.1     | <ul> <li>Updated Figure 2–3.</li> <li>Updated Figure 2–7.</li> <li>Updated Table 2–4.</li> <li>Updated "Transmit Buffer" section.</li> </ul>                                                                                                                                                                                                                                                                                                                                                               | Updated input frequency range in Table 2–4.                                         |

| Previous Chapter<br>02 changes:<br>October 2005<br>v1.0 | Added chapter to the Stratix II GX Device Handbook.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                     |

| Previous Chapter<br>03 changes:<br>August 2006, v1.4    | Updated Table 3–18 with note.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                     |

| Previous Chapter<br>03 changes:<br>June 2006, v1.3      | <ul> <li>Updated note 2 in Figure 3–41.</li> <li>Updated column title in Table 3–21.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                     |

| Previous Chapter<br>03 changes:<br>April 2006, v1.2     | <ul> <li>Updated note 1 in Table 3–9.</li> <li>Updated note 1 in Figure 3–40.</li> <li>Updated note 2 in Figure 3–41.</li> <li>Updated Table 3–16.</li> <li>Updated Figure 3–56.</li> <li>Updated Tables 3–19 through 3–22.</li> <li>Updated Tables 3–25 and 3–26.</li> <li>Updated "Fast PLL &amp; Channel Layout" section.</li> </ul>                                                                                                                                                                    | Added 1,152-pin FineLine BGA package information for EP2SGX60 device in Table 3–16. |

| Table 4-6. Stra                                           | atix II GX Trans                  | ceiver Blo          | ck AC S            | pecificati          | ion (Part           | 2 of 6)                     |                     |                     |                    |                     |      |

|-----------------------------------------------------------|-----------------------------------|---------------------|--------------------|---------------------|---------------------|-----------------------------|---------------------|---------------------|--------------------|---------------------|------|

| Symbol /<br>Description                                   | Conditions                        | -3 Spee<br>Spe      | d Comm<br>eed Grad |                     | -4 Spee<br>and Inc  | d Comr<br>Iustrial<br>Grade |                     |                     | ed Com<br>leed Gra |                     | Unit |

|                                                           |                                   | Min                 | Тур                | Max                 | Min                 | Тур                         | Max                 | Min                 | Тур                | Max                 |      |

| Absolute V <sub>MIN</sub> for a REFCLK pin (12)           |                                   | -0.3                | -                  | -                   | -0.3                | -                           | -                   | -0.3                | -                  | -                   | V    |

| Rise/fall time                                            |                                   | =                   | 0.2                | -                   | -                   | 0.2                         | -                   | -                   | 0.2                | -                   | UI   |

| Duty cycle                                                |                                   | 40                  | -                  | 60                  | 40                  | -                           | 60                  | 40                  | -                  | 60                  | %    |

| Peak-to-peak<br>differential<br>input voltage             |                                   | 200                 | ı                  | 2000                | 200                 | -                           | 2000                | 200                 | ı                  | 2000                | mV   |

| Spread-<br>spectrum<br>clocking                           |                                   | 30<br>0 to<br>-0.5% | 1                  | 33<br>0 to<br>-0.5% | 30<br>0 to<br>-0.5% | -                           | 33<br>0 to<br>-0.5% | 30<br>0 to<br>-0.5% | 1                  | 33<br>0 to<br>-0.5% | kHz  |

| On-chip<br>termination<br>resistors                       |                                   | 115 ±20%            |                    |                     | 1                   | 15 ±20%                     | 6                   | 1                   | 15 ±20°            | %                   | Ω    |

| V <sub>ICM</sub> (AC coupled) (12)                        |                                   | 1200 ±5%            |                    |                     | 1:                  | 200 ±5%                     | 6                   | 1                   | 1200 ±5°           | %                   | mV   |

| V <sub>ICM</sub> (DC coupled) (4)                         |                                   | 0.25                | -                  | 0.55                | 0.25                | -                           | 0.55                | 0.25                | -                  | 0.55                | V    |

| Rref                                                      |                                   | 20                  | 000 ±1%            | ,                   | 20                  | 000 ±1%                     | 6                   | 2                   | 2000 ±1°           | %                   | Ω    |

| Transceiver Cle                                           | ocks                              |                     |                    |                     |                     |                             |                     |                     |                    |                     |      |

| Calibration<br>block clock<br>frequency                   |                                   | 10                  | -                  | 125                 | 10                  | -                           | 125                 | 10                  | -                  | 125                 | MHz  |

| Calibration<br>block minimum<br>power-down<br>pulse width |                                   | 30                  | -                  | -                   | 30                  | -                           | -                   | 30                  | -                  | -                   | ns   |

| Time taken for one-time calibration                       |                                   | -                   | -                  | 8                   | -                   | -                           | 8                   | -                   | -                  | 8                   | ms   |

| fixedclk<br>clock<br>frequency                            | PCI Express<br>Receiver<br>Detect | -                   | 125                | -                   | -                   | 125                         | -                   | -                   | 125                | -                   | MHz  |

|                                                           | Adaptive<br>Equalization<br>(AEQ) | 2.5                 | -                  | 125                 | 2.5                 | -                           | 125                 | -                   | -                  | -                   | MHz  |

| Table 4–6. Stra                                                   | atix II GX Trans | ceiver Blo | ck AC S                                                                                                                                                                                                                                                                                                   | pecificat | ion (Part | 4 of 6)                         |         |        |                    |      |      |

|-------------------------------------------------------------------|------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|---------------------------------|---------|--------|--------------------|------|------|

| Symbol /<br>Description                                           | Conditions       |            | ed Comn<br>eed Grad                                                                                                                                                                                                                                                                                       |           |           | ed Comr<br>Iustrial<br>Grade    |         |        | ed Com<br>beed Gra |      | Unit |

|                                                                   |                  | Min        | Тур                                                                                                                                                                                                                                                                                                       | Max       | Min       | Тур                             | Max     | Min    | Тур                | Max  |      |

| Bandwidth at                                                      | BW = Low         | -          | 30                                                                                                                                                                                                                                                                                                        | -         | ı         | 30                              | -       | -      | 30                 | -    | MHz  |

| 3.125 Gbps                                                        | BW = Med         | -          | 40                                                                                                                                                                                                                                                                                                        | -         | ı         | 40                              | -       | -      | 40                 | -    | MHz  |

|                                                                   | BW = High        | -          | 50                                                                                                                                                                                                                                                                                                        | -         | ı         | 50                              | -       | -      | 50                 | -    | MHz  |

| Bandwidth at                                                      | BW = Low         | -          | 35                                                                                                                                                                                                                                                                                                        | -         | -         | 35                              | -       | -      | 35                 | -    | MHz  |

| 2.5 Gbps                                                          | BW = Med         | -          | 50                                                                                                                                                                                                                                                                                                        | -         | -         | 50                              | -       | -      | 50                 | -    | MHz  |

|                                                                   | BW = High        | -          | 60                                                                                                                                                                                                                                                                                                        | -         | -         | 60                              | -       | -      | 60                 | -    | MHz  |

| Return loss<br>differential<br>mode<br>Return loss<br>common mode |                  |            | 50 MHz to 1.25 GHz (PCI-E): -10 dB<br>100 MHz to 4.875 GHz (OIF/CEI): -8dB<br>4.875 GHz to 10 GHz (OIF/CEI): 16.6 dB/decade slope<br>100 MHz to 2.5 GHz (XAUI): -6 dB<br>50 MHz to 1.25 GHz (PCI-E): -6 dB<br>100 MHz to 4.875 GHz (OIF/CEI): -6dB<br>4.875 GHz to 10 GHz (OIF/CEI): 16.6 dB/decade slope |           |           |                                 |         |        |                    |      |      |

| Programmable<br>PPM detector<br>(2)                               |                  | 2          | 100, 125<br>50, 300,<br>00, 1000                                                                                                                                                                                                                                                                          | 5, 200,   | ±62.5,    | 100, 129<br>250, 300<br>00, 100 | 5, 200, | ±62.5, | 5, 200,<br>),<br>0 | ppm  |      |

| Run length (3), (9)                                               |                  |            | 80                                                                                                                                                                                                                                                                                                        |           |           | 80                              |         |        |                    | UI   |      |

| Programmable equalization                                         |                  | -          | -                                                                                                                                                                                                                                                                                                         | 16        | 16        |                                 |         | -      | -                  | 16   | dB   |

| Signal detect/loss threshold (4)                                  |                  | 65         | -                                                                                                                                                                                                                                                                                                         | 175       | 65        | -                               | 175     | 65     | -                  | 175  | mV   |

| CDR LTR TIme (5), (9)                                             |                  | -          | -                                                                                                                                                                                                                                                                                                         | 75        | -         | -                               | 75      | -      | -                  | 75   | us   |

| CDR Minimum<br>T1b (6), (9)                                       |                  | 15         | -                                                                                                                                                                                                                                                                                                         | -         | 15        | -                               | -       | 15     | -                  | -    | us   |

| LTD lock time (7), (9)                                            |                  | 0          | 100                                                                                                                                                                                                                                                                                                       | 4000      | 0         | 100                             | 4000    | 0      | 100                | 4000 | ns   |

| Data lock time from rx_freqloc ked (8), (9)                       |                  | -          | -                                                                                                                                                                                                                                                                                                         | 4         | -         | -                               | 4       | -      | -                  | 4    | us   |

| Programmable DC gain                                              |                  | 0, 3, 6    |                                                                                                                                                                                                                                                                                                           |           |           |                                 |         |        |                    | dB   |      |

| Transmitter                                                       |                  | •          |                                                                                                                                                                                                                                                                                                           |           |           |                                 |         | •      |                    |      |      |

| Symbol/<br>Description                 | Conditions                                                                                                                 | -3 Speed<br>Commercial Speed<br>Grade |       |       | -4 Speed<br>Commercial and<br>Industrial Speed<br>Grade |       |           | -5 Speed<br>Commercial Speed<br>Grade |       |      | Unit |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------|-------|---------------------------------------------------------|-------|-----------|---------------------------------------|-------|------|------|

|                                        |                                                                                                                            | Min                                   | Тур   | Max   | Min                                                     | Тур   | Max       | Min                                   | Тур   | Max  |      |

| Peak-to-peak jitter                    | Jitter frequency = 22.1 KHz                                                                                                | > 8.5                                 |       | > 8.5 |                                                         |       | 8.5 > 8.5 |                                       |       |      |      |

| Peak-to-peak jitter                    | Jitter frequency = 1.875 MHz                                                                                               |                                       | > 0.1 |       |                                                         | > 0.1 |           |                                       | > 0.1 |      | UI   |

| Peak-to-peak jitter                    | Jitter frequency = 20<br>MHz                                                                                               | > 0.1                                 |       |       | > 0.1                                                   |       |           |                                       | > 0.1 |      | UI   |

| PCI Express Trans                      | smit Jitter Generation                                                                                                     | 1 <i>(10)</i>                         |       |       |                                                         |       |           |                                       |       |      |      |

| Total jitter at 2.5<br>Gbps            | Compliance pattern $V_{OD} = 800 \text{ mV}$ Pre-emphasis (1st post-tap) = Setting 5                                       | -                                     | -     | 0.25  | -                                                       | -     | 0.25      | -                                     | -     | 0.25 | UI   |

| PCI Express Rece                       | iver Jitter Tolerance                                                                                                      | (10)                                  |       |       |                                                         |       |           |                                       |       |      |      |

| Total jitter at 2.5<br>Gbps            | Compliance pattern<br>No Equalization<br>DC gain = 3 dB                                                                    | > 0.6 > 0.6 > 0.6                     |       |       |                                                         | 3     | UI        |                                       |       |      |      |

| Serial RapidIO Tra                     | nsmit Jitter Generati                                                                                                      | on (11,                               | )     |       | ı                                                       |       |           |                                       |       |      |      |

| Deterministic Jitter<br>(peak-to-peak) | Data Rate = 1.25,<br>2.5, 3.125 Gbps<br>REFCLK = 125 MHz<br>Pattern = CJPAT<br>V <sub>OD</sub> = 800 mV<br>No Pre-emphasis | -                                     | -     | 0.17  | -                                                       | -     | 0.17      | -                                     | -     | 0.17 | UI   |

| Total Jitter<br>(peak-to-peak)         | Data Rate = 1.25,<br>2.5, 3.125 Gbps<br>REFCLK = 125 MHz<br>Pattern = CJPAT<br>V <sub>OD</sub> = 800 mV<br>No Pre-emphasis | -                                     | -     | 0.35  | -                                                       | -     | 0.35      | -                                     | -     | 0.35 | UI   |

| Table 4–19. Strat                                | ix II GX Transceiver Bl                                                                                                                                                                                                                                  | ock AC | Specif                     | ication | Notes (                                                 | 1), (2), | (3) <b>(P</b> | art 7 o | f 19)                      |       |      |

|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------------------|---------|---------------------------------------------------------|----------|---------------|---------|----------------------------|-------|------|

| Symbol/<br>Description                           | Conditions                                                                                                                                                                                                                                               |        | 3 Spee<br>nercial<br>Grade | Speed   | -4 Speed<br>Commercial and<br>Industrial Speed<br>Grade |          |               |         | -5 Spe<br>nercial<br>Grade | Speed | Unit |

|                                                  |                                                                                                                                                                                                                                                          | Min    | Тур                        | Max     | Min                                                     | Тур      | Max           | Min     | Тур                        | Max   |      |

|                                                  | Jitter Frequency = 22.1 KHz Data Rate = 1.25, 2.5, 3.125 Gbps REFCLK = 125 MHz Pattern = CJPAT Equalizer Setting = 0 for 1.25 Gbps Equalizer Setting = 6 for 2.5 Gbps Equalizer Setting = 6 for 3.125 Gbps                                               |        | > 8.5                      |         |                                                         | > 8.5    |               |         | > 8.5                      |       | UI   |

| Sinusoidal Jitter<br>Tolerance<br>(peak-to-peak) | oidal Jitter nce to-peak)  6 for 3.125 Gbps  Jitter Frequency = 1.875 MHz Data Rate = 1.25, 2.5, 3.125 Gbps  REFCLK = 125 MH Pattern = CJPAT Equalizer Setting = 0 for 1.25 Gbps Equalizer Setting = 6 for 2.5 Gbps Equalizer Setting = 6 for 3.125 Gbps |        | > 0.1                      |         |                                                         | > 0.1    |               |         | > 0.1                      |       | UI   |

|                                                  | Jitter Frequency = 20 MHz Data Rate = 1.25, 2.5, 3.125 Gbps REFCLK = 125 MHz Pattern = CJPAT Equalizer Setting = 0 for 1.25 Gbps Equalizer Setting = 6 for 2.5 Gbps Equalizer Setting = 6 for 3.125 Gbps                                                 |        | > 0.1                      |         |                                                         | > 0.1    |               |         | > 0.1                      |       | UI   |

| Symbol/<br>Description         | Conditions                                                                                                                                                                                                              | -3 Speed<br>Commercial Speed<br>Grade |       |     | -4 Speed<br>Commercial and<br>Industrial Speed<br>Grade |       |     | -5 Speed<br>Commercial Speed<br>Grade |     |     | Unit |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------|-----|---------------------------------------------------------|-------|-----|---------------------------------------|-----|-----|------|

|                                |                                                                                                                                                                                                                         | Min                                   | Тур   | Max | Min                                                     | Тур   | Max | Min                                   | Тур | Max |      |

| Sinusoidal Jitter<br>Tolerance | Jitter Frequency = 22.1 KHz Data Rate = 614.4 Mbps, 1.2288 Gbps, 2.4576 Gbps REFCLK = 61.44 MHz for 614.4 Mbps REFCLK = 122.88 MHz for 1.2288 Gbps and 2.4576 Gbps Pattern = CJPAT Equalizer Setting = 6 DC Gain = 0 dB |                                       | > 8.5 |     |                                                         | > 8.5 |     |                                       | N/A |     | UI   |

| (peak-to-peak) (6)             | Jitter Frequency = 1.875MHz Data Rate = 614.4 Mbps, 1.2288 Gbps, 2.4576 Gbps REFCLK = 61.44 MHz for 614.4 Mbps REFCLK = 122.88 MHz for 1.2288 Gbps and 2.4576 Gbps Pattern = CJPAT Equalizer Setting = 6 DC Gain = 0 dB |                                       | > 0.1 |     |                                                         | > 0.1 |     |                                       | N/A |     | UI   |

| Table 4-2         | Table 4–29. 2.5-V LVDS I/O Specifications                                               |                    |         |         |         |      |  |  |  |

|-------------------|-----------------------------------------------------------------------------------------|--------------------|---------|---------|---------|------|--|--|--|

| Symbol            | Parameter                                                                               | Conditions         | Minimum | Typical | Maximum | Unit |  |  |  |

| V <sub>CCIO</sub> | I/O supply voltage for left and right I/O banks (1, 2, 5, and 6)                        |                    | 2.375   | 2.5     | 2.625   | V    |  |  |  |

| V <sub>ID</sub>   | Input differential voltage swing (single-ended)                                         |                    | 100     | 350     | 900     | mV   |  |  |  |

| V <sub>ICM</sub>  | Input common mode voltage                                                               |                    | 200     | 1,250   | 1,800   | mV   |  |  |  |

| V <sub>OD</sub>   | Output differential voltage (single-ended)                                              | $R_L = 100 \Omega$ | 250     |         | 450     | mV   |  |  |  |

| V <sub>OCM</sub>  | Output common mode voltage                                                              | $R_L = 100 \Omega$ | 1.125   |         | 1.375   | V    |  |  |  |

| R <sub>L</sub>    | Receiver differential input<br>discrete resistor (external to<br>Stratix II GX devices) |                    | 90      | 100     | 110     | Ω    |  |  |  |

| Table 4–30. 3.3-V LVDS I/O Specifications |                                                                                         |                    |         |         |         |      |  |  |

|-------------------------------------------|-----------------------------------------------------------------------------------------|--------------------|---------|---------|---------|------|--|--|

| Symbol                                    | Parameter                                                                               | Conditions         | Minimum | Typical | Maximum | Unit |  |  |

| V <sub>CCIO</sub> (1)                     | I/O supply voltage for top and<br>bottom PLL banks (9, 10, 11,<br>and 12)               |                    | 3.135   | 3.3     | 3.465   | ٧    |  |  |

| V <sub>ID</sub>                           | Input differential voltage swing (single-ended)                                         |                    | 100     | 350     | 900     | mV   |  |  |

| V <sub>ICM</sub>                          | Input common mode voltage                                                               |                    | 200     | 1,250   | 1,800   | mV   |  |  |

| V <sub>OD</sub>                           | Output differential voltage (single-ended)                                              | $R_L = 100 \Omega$ | 250     |         | 710     | mV   |  |  |

| V <sub>OCM</sub>                          | Output common mode voltage                                                              | $R_L = 100 \Omega$ | 840     |         | 1,570   | mV   |  |  |

| R <sub>L</sub>                            | Receiver differential input<br>discrete resistor (external to<br>Stratix II GX devices) |                    | 90      | 100     | 110     | Ω    |  |  |

## Note to Table 4–30:

<sup>(1)</sup> The top and bottom clock input differential buffers in I/O banks 3, 4, 7, and 8 are powered by  $V_{CCINT}$ , not  $V_{CCIO}$ . The PLL clock output/feedback differential buffers are powered by VCC\_PLL\_OUT. For differential clock output/feedback operation, connect VCC\_PLL\_OUT to 3.3 V.

| Table 4–35. SSTL-18 Class I Specifications |                             |                                 |                          |           |                          |      |  |  |  |

|--------------------------------------------|-----------------------------|---------------------------------|--------------------------|-----------|--------------------------|------|--|--|--|

| Symbol                                     | Parameter                   | Conditions                      | Minimum                  | Typical   | Maximum                  | Unit |  |  |  |

| V <sub>CCIO</sub>                          | Output supply voltage       |                                 | 1.71                     | 1.8       | 1.89                     | V    |  |  |  |

| V <sub>REF</sub>                           | Reference voltage           |                                 | 0.855                    | 0.9       | 0.945                    | ٧    |  |  |  |

| V <sub>TT</sub>                            | Termination voltage         |                                 | V <sub>REF</sub> - 0.04  | $V_{REF}$ | V <sub>REF</sub> + 0.04  | ٧    |  |  |  |

| V <sub>IH</sub> (DC)                       | High-level DC input voltage |                                 | V <sub>REF</sub> + 0.125 |           |                          | ٧    |  |  |  |

| V <sub>IL</sub> (DC)                       | Low-level DC input voltage  |                                 |                          |           | V <sub>REF</sub> - 0.125 | ٧    |  |  |  |

| V <sub>IH</sub> (AC)                       | High-level AC input voltage |                                 | V <sub>REF</sub> + 0.25  |           |                          | ٧    |  |  |  |

| V <sub>IL</sub> (AC)                       | Low-level AC input voltage  |                                 |                          |           | V <sub>REF</sub> - 0.25  | ٧    |  |  |  |

| V <sub>OH</sub>                            | High-level output voltage   | $I_{OH} = -6.7 \text{ mA } (1)$ | V <sub>TT</sub> + 0.475  |           |                          | ٧    |  |  |  |

| V <sub>OL</sub>                            | Low-level output voltage    | I <sub>OL</sub> = 6.7 mA (1)    |                          |           | V <sub>TT</sub> – 0.475  | ٧    |  |  |  |

#### Note to Table 4-35:

(1) This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II GX Architecture* chapter in volume 1 of the *Stratix II GX Device Handbook*.

| Table 4-             | Table 4–36. SSTL-18 Class II Specifications |                                  |                          |           |                          |      |  |  |  |  |

|----------------------|---------------------------------------------|----------------------------------|--------------------------|-----------|--------------------------|------|--|--|--|--|

| Symbol               | Parameter                                   | Conditions                       | Minimum                  | Typical   | Maximum                  | Unit |  |  |  |  |

| $V_{\text{CCIO}}$    | Output supply voltage                       |                                  | 1.71                     | 1.8       | 1.89                     | V    |  |  |  |  |

| $V_{REF}$            | Reference voltage                           |                                  | 0.855                    | 0.9       | 0.945                    | V    |  |  |  |  |

| $V_{TT}$             | Termination voltage                         |                                  | V <sub>REF</sub> - 0.04  | $V_{REF}$ | V <sub>REF</sub> + 0.04  | V    |  |  |  |  |

| V <sub>IH</sub> (DC) | High-level DC input voltage                 |                                  | V <sub>REF</sub> + 0.125 |           |                          | V    |  |  |  |  |

| V <sub>IL</sub> (DC) | Low-level DC input voltage                  |                                  |                          |           | V <sub>REF</sub> - 0.125 | V    |  |  |  |  |

| V <sub>IH</sub> (AC) | High-level AC input voltage                 |                                  | V <sub>REF</sub> + 0.25  |           |                          | V    |  |  |  |  |

| V <sub>IL</sub> (AC) | Low-level AC input voltage                  |                                  |                          |           | V <sub>REF</sub> - 0.25  | V    |  |  |  |  |

| V <sub>OH</sub>      | High-level output voltage                   | $I_{OH} = -13.4 \text{ mA } (1)$ | V <sub>CCIO</sub> - 0.28 |           |                          | V    |  |  |  |  |

| $V_{OL}$             | Low-level output voltage                    | I <sub>OL</sub> = 13.4 mA (1)    |                          |           | 0.28                     | V    |  |  |  |  |

#### Note to Table 4-36:

(1) This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II GX Architecture* chapter in volume 1 of the *Stratix II GX Device Handbook*.

| Table 4-4             | Table 4–44. 1.5-V HSTL Class I and II Differential Specifications |            |         |         |         |      |  |  |  |

|-----------------------|-------------------------------------------------------------------|------------|---------|---------|---------|------|--|--|--|

| Symbol                | Parameter                                                         | Conditions | Minimum | Typical | Maximum | Unit |  |  |  |

| V <sub>CCIO</sub>     | I/O supply voltage                                                |            | 1.425   | 1.5     | 1.575   | V    |  |  |  |

| V <sub>DIF</sub> (DC) | DC input differential voltage                                     |            | 0.2     |         |         | V    |  |  |  |

| V <sub>CM</sub> (DC)  | DC common mode input voltage                                      |            | 0.68    |         | 0.9     | V    |  |  |  |

| V <sub>DIF</sub> (AC) | AC differential input voltage                                     |            | 0.4     |         |         | V    |  |  |  |

| V <sub>OX</sub> (AC)  | AC differential cross point voltage                               |            | 0.68    |         | 0.9     | ٧    |  |  |  |

| Table 4-4            | Table 4–45. 1.8-V HSTL Class I Specifications |                             |                         |         |                        |      |  |  |  |  |

|----------------------|-----------------------------------------------|-----------------------------|-------------------------|---------|------------------------|------|--|--|--|--|

| Symbol               | Parameter                                     | Conditions                  | Minimum                 | Typical | Maximum                | Unit |  |  |  |  |

| V <sub>CCIO</sub>    | Output supply voltage                         |                             | 1.71                    | 1.80    | 1.89                   | V    |  |  |  |  |

| $V_{REF}$            | Input reference voltage                       |                             | 0.85                    | 0.90    | 0.95                   | V    |  |  |  |  |

| V <sub>TT</sub>      | Termination voltage                           |                             | 0.85                    | 0.90    | 0.95                   | V    |  |  |  |  |

| V <sub>IH</sub> (DC) | DC high-level input voltage                   |                             | V <sub>REF</sub> + 0.1  |         |                        | ٧    |  |  |  |  |

| V <sub>IL</sub> (DC) | DC low-level input voltage                    |                             | -0.3                    |         | V <sub>REF</sub> - 0.1 | V    |  |  |  |  |

| V <sub>IH</sub> (AC) | AC high-level input voltage                   |                             | V <sub>REF</sub> + 0.2  |         |                        | ٧    |  |  |  |  |

| V <sub>IL</sub> (AC) | AC low-level input voltage                    |                             |                         |         | V <sub>REF</sub> - 0.2 | V    |  |  |  |  |

| V <sub>OH</sub>      | High-level output voltage                     | I <sub>OH</sub> = 8 mA (1)  | V <sub>CCIO</sub> - 0.4 |         |                        | ٧    |  |  |  |  |

| V <sub>OL</sub>      | Low-level output voltage                      | I <sub>OH</sub> = -8 mA (1) |                         |         | 0.4                    | V    |  |  |  |  |

#### Note to Table 4-45:

<sup>(1)</sup> This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II GX Architecture* chapter in volume 1 of the *Stratix II GX Device Handbook*.

|                          | M512 Block Intern                                       |                              |      | 1              | •    | <b>,</b>       |      |                |      |      |

|--------------------------|---------------------------------------------------------|------------------------------|------|----------------|------|----------------|------|----------------|------|------|

| Symbol                   | Parameter                                               | -3 Speed<br>Grade <i>(2)</i> |      | -3 Speed Grade |      | -4 Speed Grade |      | -5 Speed Grade |      | Unit |

| •                        |                                                         | Min                          | Max  | Min            | Max  | Min            | Max  | Min            | Max  |      |

| t <sub>M512RC</sub>      | Synchronous read cycle time                             | 2089                         | 2318 | 2089           | 2433 | 2089           | 2587 | 2089           | 3104 | ps   |

| t <sub>M512</sub> WERESU | Write or read<br>enable setup<br>time before clock      | 22                           |      | 23             |      | 24             |      | 29             |      | ps   |

| t <sub>M512WEREH</sub>   | Write or read<br>enable hold time<br>after clock        | 203                          |      | 213            |      | 226            |      | 272            |      | ps   |

| t <sub>M512DATASU</sub>  | Data setup time before clock                            | 22                           |      | 23             |      | 24             |      | 29             |      | ps   |

| t <sub>M512DATAH</sub>   | Data hold time after clock                              | 203                          |      | 213            |      | 226            |      | 272            |      | ps   |

| t <sub>M512WADDRSU</sub> | Write address<br>setup time before<br>clock             | 22                           |      | 23             |      | 24             |      | 29             |      | ps   |

| t <sub>M512WADDRH</sub>  | Write address<br>hold time after<br>clock               | 203                          |      | 213            |      | 226            |      | 272            |      | ps   |

| t <sub>M512RADDRSU</sub> | Read address<br>setup time before<br>clock              | 22                           |      | 23             |      | 24             |      | 29             |      | ps   |

| t <sub>M512RADDRH</sub>  | Read address<br>hold time after<br>clock                | 203                          |      | 213            |      | 226            |      | 272            |      | ps   |

| t <sub>M512DATACO1</sub> | Clock-to-output<br>delay when using<br>output registers | 298                          | 478  | 298            | 501  | 298            | 533  | 298            | 640  | ps   |

| t <sub>M512DATACO2</sub> | Clock-to-output<br>delay without<br>output registers    | 2102                         | 2345 | 2102           | 2461 | 2102           | 2616 | 2102           | 3141 | ps   |

| t <sub>M512CLKL</sub>    | Minimum clock low time                                  | 1315                         |      | 1380           |      | 1468           |      | 1762           |      | ps   |

| t <sub>M512CLKH</sub>    | Minimum clock high time                                 | 1315                         |      | 1380           |      | 1468           |      | 1762           |      | ps   |

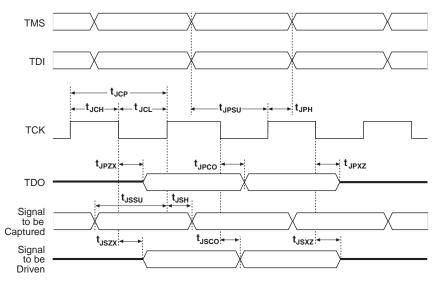

Figure 4-14. Stratix II GX JTAG Waveforms.

Table 4–117 shows the JTAG timing parameters and values for Stratix II GX devices.

| Table 4–117. Stratix II GX JTAG Timing Parameters and Values |                                                |     |     |      |  |  |  |  |

|--------------------------------------------------------------|------------------------------------------------|-----|-----|------|--|--|--|--|

| Symbol                                                       | Parameter                                      | Min | Max | Unit |  |  |  |  |

| t <sub>JCP</sub>                                             | TCK clock period                               | 30  |     | ns   |  |  |  |  |

| t <sub>JCH</sub>                                             | TCK clock high time                            | 12  |     | ns   |  |  |  |  |

| t <sub>JCL</sub>                                             | TCK clock low time                             | 12  |     | ns   |  |  |  |  |

| t <sub>JPSU</sub>                                            | JTAG port setup time                           | 4   |     | ns   |  |  |  |  |

| t <sub>JPH</sub>                                             | JTAG port hold time                            | 5   |     | ns   |  |  |  |  |

| t <sub>JPCO</sub>                                            | JTAG port clock to output                      |     | 9   | ns   |  |  |  |  |

| t <sub>JPZX</sub>                                            | JTAG port high impedance to valid output       |     | 9   | ns   |  |  |  |  |

| t <sub>JPXZ</sub>                                            | JTAG port valid output to high impedance       |     | 9   | ns   |  |  |  |  |

| t <sub>JSSU</sub>                                            | Capture register setup time                    | 4   |     | ns   |  |  |  |  |

| t <sub>JSH</sub>                                             | Capture register hold time                     | 5   |     | ns   |  |  |  |  |

| t <sub>JSCO</sub>                                            | Update register clock to output                |     | 12  | ns   |  |  |  |  |

| t <sub>JSZX</sub>                                            | Update register high impedance to valid output |     | 12  | ns   |  |  |  |  |

| t <sub>JSXZ</sub>                                            | Update register valid output to high impedance |     | 12  | ns   |  |  |  |  |