Welcome to **E-XFL.COM**

### Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 3022                                                        |

| Number of Logic Elements/Cells | 60440                                                       |

| Total RAM Bits                 | 2544192                                                     |

| Number of I/O                  | 364                                                         |

| Number of Gates                | -                                                           |

| Voltage - Supply               | 1.15V ~ 1.25V                                               |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 780-BBGA                                                    |

| Supplier Device Package        | 780-FBGA (29x29)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2sgx60df780c5n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

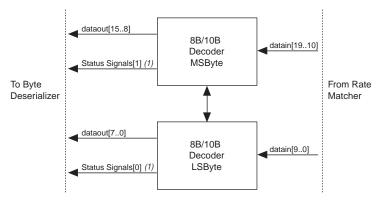

Figure 2-21. 8B/10B Decoder

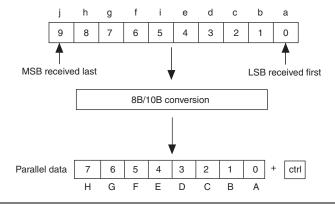

The 8B/10B decoder in single-width mode translates the 10-bit encoded data into the 8-bit equivalent data or control code. The 10-bit code received must be from the supported Dx.y or Kx.y list with the proper disparity or error flags asserted. All 8B/10B control signals, such as disparity error or control detect, are pipelined with the data and edge-aligned with the data. Figure 2–22 shows how the 10-bit symbol is decoded in the 8-bit data + 1-bit control indicator.

Figure 2-22. 8B/10B Decoder Conversion

The 8B/10B decoder in double-width mode translates the 20-bit (2  $\times$  10-bits) encoded code into the 16-bit (2  $\times$  8-bits) equivalent data or control code. The 20-bit upper and lower symbols received must be from the supported Dx.y or Kx.y list with the proper disparity or error flags

| Transmitter Ph. Transmitter Se Transmitter An. Transmitter An. Transmitter An. Transmitter An. Transmitter An. Transmitter An. BIST Generator Receiver Deske Receiver BA10 Receiver Phase Receiver PLL / Receiver PLL / Receiver PLL / Receiver AUII | Table 2–16. Reset Signal | Transmitter Phase Compensation FIFO Module/ Byte Serializer | Transmitter 8B/10B Encoder | Transmitter Serializer | Transmitter Analog Circuits | Transmitter PLL XX | Transmitter XAUI State Machine | BIST Generators | Receiver Deserializer | Receiver Word Aligner | Receiver Deskew FIFO Module | Receiver Rate Matcher | Receiver 8B/10B Decoder | Receiver Phase Comp FIFO Module/ Byte Deserializer | Receiver PLL / CRU | Receiver XAUI State Machine | ifiers   | Receiver Analog Circuits |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------------------------|----------------------------|------------------------|-----------------------------|--------------------|--------------------------------|-----------------|-----------------------|-----------------------|-----------------------------|-----------------------|-------------------------|----------------------------------------------------|--------------------|-----------------------------|----------|--------------------------|

|                                                                                                                                                                                                                                                      | rx_digitalreset          |                                                             |                            |                        |                             |                    |                                |                 |                       | <b>✓</b>              | <b>✓</b>                    | <b>✓</b>              | <b>✓</b>                | <b>✓</b>                                           |                    | <b>✓</b>                    | <b>✓</b> |                          |

| In_digitalioned                                                                                                                                                                                                                                      | rx_analogreset           |                                                             |                            |                        |                             |                    |                                |                 | <b>\</b>              |                       |                             |                       |                         |                                                    | <b>✓</b>           |                             |          | <b>✓</b>                 |

|                                                                                                                                                                                                                                                      | tx_digitalreset          | <b>~</b>                                                    | <b>~</b>                   |                        |                             |                    | <b>✓</b>                       | <b>~</b>        |                       |                       |                             |                       |                         |                                                    |                    |                             |          |                          |

| rx_analogreset                                                                                                                                                                                                                                       | gxb_powerdown            | <b>✓</b>                                                    | <b>✓</b>                   | <b>✓</b>               | <b>✓</b>                    | <b>✓</b>           | <b>✓</b>                       | <b>✓</b>        | <b>✓</b>              | <b>✓</b>              | <b>✓</b>                    | <b>✓</b>              | <b>✓</b>                | <b>✓</b>                                           | <b>✓</b>           | <b>✓</b>                    | <b>✓</b> | <b>✓</b>                 |

| rx_analogreset                                                                                                                                                                                                                                       | gxb_enable               | <b>✓</b>                                                    | <b>✓</b>                   | <b>✓</b>               | <b>✓</b>                    | <b>✓</b>           | <b>✓</b>                       | <b>✓</b>        | <b>✓</b>              | <b>✓</b>              | <b>✓</b>                    | <b>✓</b>              | <b>✓</b>                | <b>✓</b>                                           | <b>✓</b>           | <b>✓</b>                    | <b>✓</b> | <b>✓</b>                 |

#### Voltage Reference Capabilities

Stratix II GX transceivers provide voltage reference and bias circuitry. To set up internal bias for controlling the transmitter output driver voltage swings, as well as to provide voltage and current biasing for other analog circuitry, the device uses an internal bandgap voltage reference of 0.7 V. An external 2-K $\Omega$  resistor connected to ground generates a constant bias current (independent of power supply drift, process changes, or temperature variation). An on-chip resistor generates a tracking current that tracks on-chip resistor variation. These currents are mirrored and distributed to the analog circuitry in each channel.

For more information, refer to the *DC and Switching Characteristics* chapter in volume 1 of the *Stratix II GX Handbook*.

Table 2–20 shows the input and output data signal connections along with the address and control signal input connections to the row unit interfaces (L0 to L5 and R0 to R5).

| Table 2–20. M-RAM    | Row Interface Unit Signals                                              |                 |

|----------------------|-------------------------------------------------------------------------|-----------------|

| Unit Interface Block | Input Signals                                                           | Output Signals  |

| L0                   | datain_a[140]<br>byteena_a[10]                                          | dataout_a[110]  |

| L1                   | datain_a[2915]<br>byteena_a[32]                                         | dataout_a[2312] |

| L2                   | datain_a[3530] addressa[40] addr_ena_a clock_a clocken_a renwe_a aclr_a | dataout_a[3524] |

| L3                   | addressa[155]<br>datain_a[4136]                                         | dataout_a[4736] |

| L4                   | datain_a[5642]<br>byteena_a[54]                                         | dataout_a[5948] |

| L5                   | datain_a[7157]<br>byteena_a[76]                                         | dataout_a[7160] |

| R0                   | datain_b[140]<br>byteena_b[10]                                          | dataout_b[110]  |

| R1                   | datain_b[2915]<br>byteena_b[32]                                         | dataout_b[2312] |

| R2                   | datain_b[3530] addressb[40] addr_ena_b clock_b clocken_b renwe_b aclr_b | dataout_b[3524] |

| R3                   | addressb[155]<br>datain_b[4136]                                         | dataout_b[4736] |

| R4                   | datain_b[5642]<br>byteena_b[54]                                         | dataout_b[5948] |

| R5                   | datain_b[7157]<br>byteena_b[76]                                         | dataout_b[7160] |

Refer to the *TriMatrix Embedded Memory Blocks in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II GX Device Handbook* for more information on TriMatrix memory.

# Digital Signal Processing (DSP) Block

The most commonly used DSP functions are finite impulse response (FIR) filters, complex FIR filters, infinite impulse response (IIR) filters, fast Fourier transform (FFT) functions, direct cosine transform (DCT) functions, and correlators. All of these use the multiplier as the fundamental building block. Additionally, some applications need specialized operations such as multiply-add and multiply-accumulate operations. Stratix II GX devices provide DSP blocks to meet the arithmetic requirements of these functions.

Each Stratix II GX device has two to four columns of DSP blocks to efficiently implement DSP functions faster than ALM-based implementations. Stratix II GX devices have up to 24 DSP blocks per column (see Table 2–21). Each DSP block can be configured to support up to:

- Eight 9 × 9-bit multipliers

- Four 18 × 18-bit multipliers

- One 36 × 36-bit multiplier

As indicated, the Stratix II GX DSP block can support one  $36 \times 36$ -bit multiplier in a single DSP block, and is true for any combination of signed, unsigned, or mixed sign multiplications.

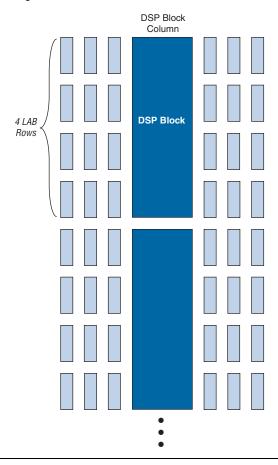

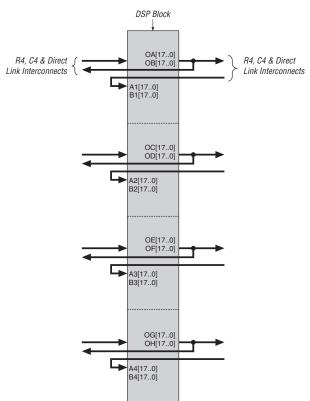

Figures 2–57 shows one of the columns with surrounding LAB rows.

Figure 2-57. DSP Blocks Arranged in Columns

The DSP block is divided into four block units that interface with four LAB rows on the left and right. Each block unit can be considered one complete  $18 \times 18$ -bit multiplier with 36 inputs and 36 outputs. A local interconnect region is associated with each DSP block. Like a LAB, this interconnect region can be fed with 16 direct link interconnects from the LAB to the left or right of the DSP block in the same row. R4 and C4 routing resources can access the DSP block's local interconnect region. The outputs also work similarly to LAB outputs. Eighteen outputs from the DSP block can drive to the left LAB through direct link interconnects and 18 can drive to the right LAB through direct link interconnects. All 36 outputs can drive to R4 and C4 routing interconnects. Outputs can drive right- or left-column routing.

Figures 2–59 and 2–60 show the DSP block interfaces to LAB rows.

Figure 2-59. DSP Block Interconnect Interface

The Stratix II GX clock networks can be disabled (powered down) by both static and dynamic approaches. When a clock net is powered down, all the logic fed by the clock net is in an off-state, thereby reducing the overall power consumption of the device. The global and regional clock networks can be powered down statically through a setting in the configuration file (.sof or .pof). Clock networks that are not used are automatically powered down through configuration bit settings in the configuration file generated by the Quartus II software. The dynamic clock enable and disable feature allows the internal logic to control power up and down synchronously on GCLK and RCLK nets and PLL\_OUT pins. This function is independent of the PLL and is applied directly on the clock network or PLL\_OUT pin, as shown in Figures 2–67 through 2–69.

#### **Enhanced and Fast PLLs**

Stratix II GX devices provide robust clock management and synthesis using up to four enhanced PLLs and four fast PLLs. These PLLs increase performance and provide advanced clock interfacing and clock frequency synthesis. With features such as clock switchover, spread spectrum clocking, reconfigurable bandwidth, phase control, and reconfigurable phase shifting, the Stratix II GX device's enhanced PLLs provide you with complete control of clocks and system timing. The fast PLLs provide general purpose clocking with multiplication and phase shifting as well as high-speed outputs for high-speed differential I/O support. Enhanced and fast PLLs work together with the Stratix II GX high-speed I/O and advanced clock architecture to provide significant improvements in system performance and bandwidth.

| Table 2–27. Global and Region<br>(Part 3 of 3)              |          |          |          |          |       |       |       |       |          |          |          |          |  |

|-------------------------------------------------------------|----------|----------|----------|----------|-------|-------|-------|-------|----------|----------|----------|----------|--|

| Left Side Global and Regional<br>Clock Network Connectivity | CLKO     | CLK1     | CLK2     | ССКЗ     | RCLKO | RCLK1 | RCLK2 | RCLK3 | RCLK4    | RCLK5    | RCLK6    | RCLK7    |  |

| PLL 8 outputs                                               |          |          |          |          |       |       |       |       |          |          |          |          |  |

| c0                                                          |          |          | <b>\</b> | <b>\</b> |       |       |       |       | <b>\</b> |          | <b>✓</b> |          |  |

| c1                                                          |          |          | <b>✓</b> | <b>✓</b> |       |       |       |       |          | <b>✓</b> |          | <b>✓</b> |  |

| c2                                                          | <b>✓</b> | <b>✓</b> |          |          |       |       |       |       | <b>✓</b> |          | <b>✓</b> |          |  |

|                                                             |          |          |          |          |       |       |       |       |          |          |          |          |  |

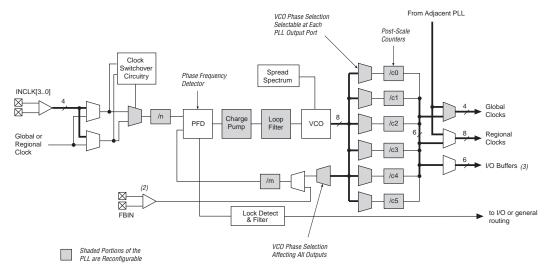

#### **Enhanced PLLs**

Stratix II GX devices contain up to four enhanced PLLs with advanced clock management features. These features include support for external clock feedback mode, spread-spectrum clocking, and counter cascading. Figure 2–74 shows a diagram of the enhanced PLL.

Figure 2–74. Stratix II GX Enhanced PLL Note (1)

#### *Notes to Figure 2–74:*

- Each clock source can come from any of the four clock pins that are physically located on the same side of the device

as the PLL.

- (2) If the feedback input is used, you will lose one (or two, if FBIN is differential) external clock output pin.

- (3) Each enhanced PLL has three differential external clock outputs or six single-ended external clock outputs.

- (4) The global or regional clock input can be driven by an output from another PLL, a pin-driven dedicated global or regional clock, or through a clock control block provided the clock control block is fed by an output from another PLL or a pin-driven dedicated global or regional clock. An internally generated global signal cannot drive the PLL.

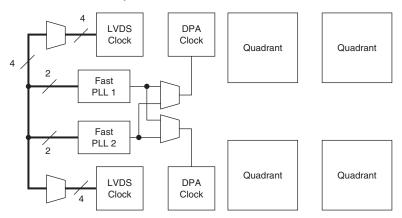

#### **Fast PLLs**

Stratix II GX devices contain up to four fast PLLs with high-speed serial interfacing ability. The fast PLLs offer high-speed outputs to manage the high-speed differential I/O interfaces. Figure 2–75 shows a diagram of the fast PLL.

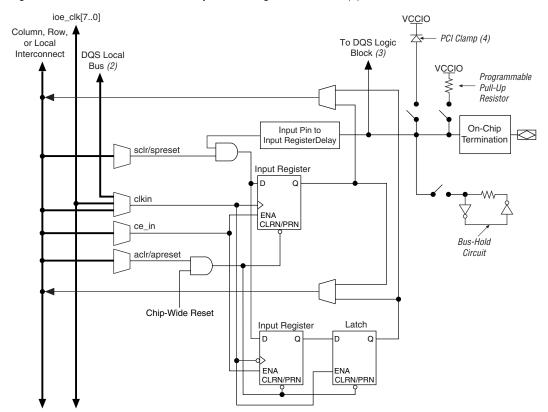

Figure 2–82. Stratix II GX IOE in DDR Input I/O Configuration Note (1)

Notes to Figure 2-82:

- (1) All input signals to the IOE can be inverted at the IOE.

- (2) This signal connection is only allowed on dedicated DQ function pins.

- (3) This signal is for dedicated DQS function pins only.

- (4) The optional PCI clamp is only available on column I/O pins.

For high-speed source synchronous interfaces such as POS-PHY 4 and the Parallel RapidIO standard, the source synchronous clock rate is not a byte- or SERDES-rate multiple of the data rate. Byte alignment is necessary for these protocols because the source synchronous clock does not provide a byte or word boundary since the clock is one half the data rate, not one eighth. The Stratix II GX device's high-speed differential I/O circuitry provides dedicated data realignment circuitry for user-controlled byte boundary shifting. This simplifies designs while saving ALM resources. You can use an ALM-based state machine to signal the shift of receiver byte boundaries until a specified pattern is detected to indicate byte alignment.

#### Fast PLL and Channel Layout

The receiver and transmitter channels are interleaved such that each I/O bank on the left side of the device has one receiver channel and one transmitter channel per LAB row. Figure 2–90 shows the fast PLL and channel layout in the EP2SGX30C/D and EP2SGX60C/D devices. Figure 2–91 shows the fast PLL and channel layout in EP2SGX60E, EP2SGX90E/F, and EP2SGX130G devices.

Figure 2–90. Fast PLL and Channel Layout in the EP2SGX30C/D and EP2SGX60C/D Devices Note (1)

Note to Figure 2-90:

(1) See Table 2–38 for the number of channels each device supports.

(AS), passive serial (PS), passive parallel asynchronous (PPA), and JTAG configuration schemes. The Stratix II GX device's optimized interface allows microprocessors to configure it serially or in parallel and synchronously or asynchronously. The interface also enables microprocessors to treat Stratix II GX devices as memory and configure them by writing to a virtual memory location, making reconfiguration easy.

In addition to the number of configuration methods supported, Stratix II GX devices also offer the design security, decompression, and remote system upgrade features. The design security feature, using configuration bitstream encryption and advanced encryption standard (AES) technology, provides a mechanism to protect designs. The decompression feature allows Stratix II GX FPGAs to receive a compressed configuration bitstream and decompress this data in real-time, reducing storage requirements and configuration time. The remote system upgrade feature allows real-time system upgrades from remote locations of Stratix II GX designs. For more information, refer to the "Configuration Schemes" on page 3–6.

#### **Operating Modes**

The Stratix II GX architecture uses SRAM configuration elements that require configuration data to be loaded each time the circuit powers up. The process of physically loading the SRAM data into the device is called configuration. During initialization, which occurs immediately after configuration, the device resets registers, enables I/O pins, and begins to operate as a logic device. The I/O pins are tri-stated during power-up, and before and during configuration. Together, the configuration and initialization processes are called command mode. Normal device operation is called user mode.

SRAM configuration elements allow you to reconfigure Stratix II GX devices in-circuit by loading new configuration data into the device. With real-time reconfiguration, the device is forced into command mode with a device pin. The configuration process loads different configuration data, re-initializes the device, and resumes user-mode operation. You can perform in-field upgrades by distributing new configuration files either within the system or remotely.

The PORSEL pin is a dedicated input used to select power-on reset (POR) delay times of 12 ms or 100 ms during power up. When the PORSEL pin is connected to ground, the POR time is 100 ms. When the PORSEL pin is connected to  $V_{CC}$ , the POR time is 12 ms.

## 4. DC and Switching Characteristics

SIIGX51006-4.6

### Operating Conditions

Stratix<sup>®</sup> II GX devices are offered in both commercial and industrial grades. Industrial devices are offered in -4 speed grade and commercial devices are offered in -3 (fastest), -4, and -5 speed grades.

Tables 4–1 through 4–51 provide information on absolute maximum ratings, recommended operating conditions, DC electrical characteristics, and other specifications for Stratix II GX devices.

#### **Absolute Maximum Ratings**

Table 4–1 contains the absolute maximum ratings for the Stratix II GX device family.

| Table 4–1          | . Stratix II GX Device Absolut | te Maximum Ratings Notes | (1), (2),(3) |         |      |

|--------------------|--------------------------------|--------------------------|--------------|---------|------|

| Symbol             | Parameter                      | Conditions               | Minimum      | Maximum | Unit |

| V <sub>CCINT</sub> | Supply voltage                 | With respect to ground   | -0.5         | 1.8     | V    |

| V <sub>CCIO</sub>  | Supply voltage                 | With respect to ground   | -0.5         | 4.6     | V    |

| V <sub>CCPD</sub>  | Supply voltage                 | With respect to ground   | -0.5         | 4.6     | V    |

| VI                 | DC input voltage (4)           |                          | -0.5         | 4.6     | V    |

| I <sub>OUT</sub>   | DC output current, per pin     |                          | -25          | 40      | mA   |

| T <sub>STG</sub>   | Storage temperature            | No bias                  | -65          | 150     | С    |

| T <sub>J</sub>     | Junction temperature           | BGA packages under bias  | <b>-</b> 55  | 125     | С    |

#### Notes to Table 4-1:

- (1) See the Operating Requirements for Altera Devices Data Sheet for more information.

- (2) Conditions beyond those listed in Table 4–1 may cause permanent damage to a device. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse affects on the device.

- (3) Supply voltage specifications apply to voltage readings taken at the device pins, not at the power supply.

- (4) During transitions, the inputs may overshoot to the voltage shown in Table 4–2 based upon the input duty cycle. The DC case is equivalent to 100% duty cycle. During transitions, the inputs may undershoot to –2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

| Table 4-                           | -13. Typi | -13. Typical Pre-Emphasis (First Post-Tap), Note (1) (Part 2 of 2) |   |     |           |           |         |           |     |     |     |     |  |  |

|------------------------------------|-----------|--------------------------------------------------------------------|---|-----|-----------|-----------|---------|-----------|-----|-----|-----|-----|--|--|

| V <sub>CCH</sub> TX<br>= 1.5 V     |           |                                                                    |   | 1   | First Pos | t Tap Pre | e-Empha | sis Level |     |     |     |     |  |  |

| V <sub>OD</sub><br>Setting<br>(mV) | 1         | 2                                                                  | 3 | 4   | 5         | 6         | 7       | 8         | 9   | 10  | 11  | 12  |  |  |

| 1400                               |           |                                                                    |   | 20% | 26%       | 33%       | 41%     | 51%       | 58% | 67% | 77% | 86% |  |  |

Note to Table 4–13:

$(1) \quad \text{Applicable to data rates from } 600 \text{ Mbps to } 6.375 \text{ Gbps. Specification is for measurement at the package ball.}$

| Table 4-                           | -14. Typi | cal Pre-E | mphasis | (First Pa | ost-Tap), | Note (1)  |                |           |      |      |      |      |

|------------------------------------|-----------|-----------|---------|-----------|-----------|-----------|----------------|-----------|------|------|------|------|

| V <sub>CCH</sub> TX<br>= 1.5 V     |           |           |         |           | First Pos | t Tap Pre | e-Empha        | sis Level |      |      |      |      |

| V <sub>OD</sub><br>Setting<br>(mV) | 1         | 2         | 3       | 4         | 5         | 6         | 7              | 8         | 9    | 10   | 11   | 12   |

|                                    |           |           |         |           |           | TX Term   | <b>= 120</b> Ω | 2         |      |      |      |      |

| 240                                | 45%       |           |         |           |           |           |                |           |      |      |      |      |

| 480                                |           | 41%       | 76%     | 114%      | 166%      | 257%      | 355%           |           |      |      |      |      |

| 720                                |           | 23%       | 38%     | 55%       | 84%       | 108%      | 137%           | 179%      | 226% | 280% | 405% | 477% |

| 960                                |           | 15%       | 24%     | 36%       | 47%       | 64%       | 80%            | 97%       | 122% | 140% | 170% | 196% |

|                                    |           |           | 18%     | 22%       | 30%       | 41%       | 51%            | 63%       | 77%  | 86%  | 98%  | 116% |

Note to Table 4–14:

| Table 4-                           | -15. Typi | cal Pre-E | mphasis | (First Po | ost-Tap), | Note (1)  | (Part 1 | of 2)     |   |    |    |    |

|------------------------------------|-----------|-----------|---------|-----------|-----------|-----------|---------|-----------|---|----|----|----|

| V <sub>CCH</sub> TX<br>= 1.5 V     |           |           |         |           | First Pos | t Tap Pre | e-Empha | sis Level |   |    |    |    |

| V <sub>OD</sub><br>Setting<br>(mV) | 1         | 2         | 3       | 4         | 5         | 6         | 7       | 8         | 9 | 10 | 11 | 12 |

|                                    |           |           |         |           | ,         | TX Term   | = 150 Ω | 2         |   |    |    |    |

| 300                                | 32%       | 85%       |         |           |           |           |         |           |   |    |    |    |

<sup>(1)</sup> Applicable to data rates from 600 Mbps to 6.375 Gbps. Specification is for measurement at the package ball.

| Table 4–19. Strati     | ix II GX Transceiver B | lock AC | Specia                                | fication | Notes ( | (1), (2)                                 | , (3) <b>(P</b> | art 19 | of 19)                   |         |      |

|------------------------|------------------------|---------|---------------------------------------|----------|---------|------------------------------------------|-----------------|--------|--------------------------|---------|------|

| Symbol/<br>Description | Conditions             |         | -3 Speed<br>Commercial Speed<br>Grade |          |         | -4 Spec<br>imercial<br>strial S<br>Grade | al and<br>Speed |        | -5 Spe<br>nercia<br>Grad | l Speed | Unit |

|                        |                        | Min     | Тур                                   | Max      | Min     | Тур                                      | Max             | Min    | Тур                      | Max     |      |

#### Notes to Table 4-19:

- (1) Dedicated REFCLK pins were used to drive the input reference clocks.

- (2) Jitter numbers specified are valid for the stated conditions only.

- (3) Refer to the protocol characterization documents for detailed information.

- (4) HiGig configuration is available in a -3 speed grade only. For more information, refer to the *Stratix II GX Transceiver Architecture Overview* chapter in volume 2 of the *Stratix II GX Device Handbook*.

- (5) Stratix II GX transceivers meet CEI jitter generation specification of 0.3 UI for a V<sub>OD</sub> range of 400 mV to 1000 mV.

- (6) The Sinusoidal Jitter Tolerance Mask is defined only for low voltage (LV) variant of CPRI.

- (7) The jitter numbers for SONET/SDH are compliant to the GR-253-CORE Issue 3 Specification.

- (8) The jitter numbers for Fibre Channel are compliant to the FC-PI-4 Specification revision 6.10.

- (9) The jitter numbers for XAUI are compliant to the IEEE802.3ae-2002 Specification.

- (10) The jitter numbers for PCI Express are compliant to the PCIe Base Specification 2.0.

- (11) The jitter numbers for Serial RapidIO are compliant to the RapidIO Specification 1.3.

- (12) The jitter numbers for GIGE are compliant to the IEEE802.3-2002 Specification.

- (13) The jitter numbers for HiGig are compliant to the IEEE802.3ae-2002 Specification.

- (14) The jitter numbers for (OIF) CEI are compliant to the OIF-CEI-02.0 Specification.

- (15) The jitter numbers for CPRI are compliant to the CPRI Specification V2.1.

- (16) The HD-SDI and 3G-SDI jitter numbers are compliant to the SMPTE292M and SMPTE424M Specifications.

- (17) The Fibre Channel transmitter jitter generation numbers are compliant to the specification at  $\beta_T$  interoperability point.

- (18) The Fibre Channel receiver jitter tolerance numbers are compliant to the specification at  $\beta_R$  interoperability point.

Table 4–20 provides information on recommended input clock jitter for each mode.

| Table 4–20. R | Table 4–20. Recommended Input Clock Jitter (Part 1 of 2) |                                    |                          |                                          |                                         |                                      |  |  |  |  |  |  |  |  |

|---------------|----------------------------------------------------------|------------------------------------|--------------------------|------------------------------------------|-----------------------------------------|--------------------------------------|--|--|--|--|--|--|--|--|

| Mode          | Reference<br>Clock (MHz)                                 | Vectron<br>LVPECL XO<br>Type/Model | Frequency<br>Range (MHz) | RMS Jitter<br>(12 kHz to 20<br>MHz) (ps) | Period Jitter<br>(Peak to<br>Peak) (ps) | Phase Noise<br>at 1 MHz<br>(dB c/Hz) |  |  |  |  |  |  |  |  |

| PCI-E         | 100                                                      | VCC6-Q/R                           | 10 to 270                | 0.3                                      | 23                                      | -149.9957                            |  |  |  |  |  |  |  |  |

| (OIF) CEI     | 156.25                                                   | VCC6-Q/R                           | 10 to 270                | 0.3                                      | 23                                      | -146.2169                            |  |  |  |  |  |  |  |  |

| PHY           | 622.08                                                   | VCC6-Q                             | 270 to 800               | 2                                        | 30                                      | Not available                        |  |  |  |  |  |  |  |  |

| GIGE          | 62.5                                                     | VCC6-Q/R                           | 10 to 270                | 0.3                                      | 23                                      | -149.9957                            |  |  |  |  |  |  |  |  |

|               | 125                                                      | VCC6-Q/R                           | 10 to 270                | 0.3                                      | 23                                      | -146.9957                            |  |  |  |  |  |  |  |  |

| XAUI          | 156.25                                                   | VCC6-Q/R                           | 10 to 270                | 0.3                                      | 23                                      | -146.2169                            |  |  |  |  |  |  |  |  |

| Table 4-20. R      | Recommended II           | nput Clock Jitte                   | r (Part 2 of 2)          |                                          |                                         |                                      |

|--------------------|--------------------------|------------------------------------|--------------------------|------------------------------------------|-----------------------------------------|--------------------------------------|

| Mode               | Reference<br>Clock (MHz) | Vectron<br>LVPECL XO<br>Type/Model | Frequency<br>Range (MHz) | RMS Jitter<br>(12 kHz to 20<br>MHz) (ps) | Period Jitter<br>(Peak to<br>Peak) (ps) | Phase Noise<br>at 1 MHz<br>(dB c/Hz) |

|                    | 77.76                    | VCC6-Q/R                           | 10 to 270                | 0.3                                      | 23                                      | -149.5476                            |

| SONET/SDH          | 155.52                   | VCC6-Q/R                           | 10 to 270                | 0.3                                      | 23                                      | -149.1903                            |

| OC-48              | 311.04                   | VCC6-Q                             | 270 to 800               | 2                                        | 30                                      | Not available                        |

|                    | 622.08                   | VCC6-Q                             | 270 to 800               | 2                                        | 30                                      | Not available                        |

|                    | 62.2                     | VCC6-Q/R                           | 10 to 270                | 0.3                                      | 23                                      | -149.6289                            |

|                    | 311                      | VCC6-Q                             | 270 to 800               | 2                                        | 30                                      | Not available                        |

| SONET/SDH<br>OC-12 | 77.76                    | VCC6-Q/R                           | 10 to 270                | 0.3                                      | 23                                      | -149.5476                            |

|                    | 155.52                   | VCC6-Q/R                           | 10 to 270                | 0.3                                      | 23                                      | -149.1903                            |

|                    | 622.08                   | VCC6-Q                             | 270 to 800               | 2                                        | 30                                      | Not available                        |

Tables 4–21 and 4–22 show the transmitter and receiver PCS latency for each mode, respectively.

| Table 4–21. PCS L | atency (Part 1 d                      | o <b>f 2)</b> Note ( | (1)                         |                    |                     |                   |                |

|-------------------|---------------------------------------|----------------------|-----------------------------|--------------------|---------------------|-------------------|----------------|

|                   |                                       |                      |                             | Transmitte         | r PCS Laten         | ıcy               |                |

| Functional Mode   | Configuration                         | TX PIPE              | TX<br>Phase<br>Comp<br>FIFO | Byte<br>Serializer | TX State<br>Machine | 8B/10B<br>Encoder | <b>Sum</b> (2) |

| XAUI              |                                       | -                    | 2-3                         | 1                  | 0.5                 | 0.5               | 4-5            |

| PIPF              | ×1, ×4, ×8<br>8-bit channel<br>width  | 1                    | 3-4                         | 1                  | -                   | 1                 | 6-7            |

| FIFE              | ×1, ×4, ×8<br>16-bit channel<br>width | 1                    | 3-4                         | 1                  | -                   | 0.5               | 6-7            |

| GIGE              |                                       | -                    | 2-3                         | 1                  | -                   | 1                 | 4-5            |

|                   | OC-12                                 | -                    | 2-3                         | 1                  | -                   | 1                 | 4-5            |

| SONET/SDH         | OC-48                                 | -                    | 2-3                         | 1                  | -                   | 0.5               | 4-5            |

|                   | OC-96                                 | -                    | 2-3                         | 1                  | -                   | 0.5               | 4-5            |

| (OIF) CEI PHY     |                                       | -                    | 2-3                         | 1                  | -                   | 0.5               | 4-5            |

| CPRI (3)          | 614 Mbps,<br>1.228 Gbps               | -                    | 2                           | 1                  | =                   | 1                 | 4              |

|                   | 2.456 Gbps                            | -                    | 2-3                         | 1                  | -                   | 1                 | 4-5            |

| Table 4–29. 2.5-V LVDS I/O Specifications |                                                                                         |                    |         |         |         |      |  |  |

|-------------------------------------------|-----------------------------------------------------------------------------------------|--------------------|---------|---------|---------|------|--|--|

| Symbol                                    | Parameter                                                                               | Conditions         | Minimum | Typical | Maximum | Unit |  |  |

| V <sub>CCIO</sub>                         | I/O supply voltage for left and right I/O banks (1, 2, 5, and 6)                        |                    | 2.375   | 2.5     | 2.625   | V    |  |  |

| V <sub>ID</sub>                           | Input differential voltage swing (single-ended)                                         |                    | 100     | 350     | 900     | mV   |  |  |

| V <sub>ICM</sub>                          | Input common mode voltage                                                               |                    | 200     | 1,250   | 1,800   | mV   |  |  |

| V <sub>OD</sub>                           | Output differential voltage (single-ended)                                              | $R_L = 100 \Omega$ | 250     |         | 450     | mV   |  |  |

| V <sub>OCM</sub>                          | Output common mode voltage                                                              | $R_L = 100 \Omega$ | 1.125   |         | 1.375   | V    |  |  |

| R <sub>L</sub>                            | Receiver differential input<br>discrete resistor (external to<br>Stratix II GX devices) |                    | 90      | 100     | 110     | Ω    |  |  |

| Table 4–30. 3.3-V LVDS I/O Specifications |                                                                                         |                    |         |         |         |      |  |  |

|-------------------------------------------|-----------------------------------------------------------------------------------------|--------------------|---------|---------|---------|------|--|--|

| Symbol                                    | Parameter                                                                               | Conditions         | Minimum | Typical | Maximum | Unit |  |  |

| V <sub>CCIO</sub> (1)                     | I/O supply voltage for top and<br>bottom PLL banks (9, 10, 11,<br>and 12)               |                    | 3.135   | 3.3     | 3.465   | ٧    |  |  |

| V <sub>ID</sub>                           | Input differential voltage swing (single-ended)                                         |                    | 100     | 350     | 900     | mV   |  |  |

| V <sub>ICM</sub>                          | Input common mode voltage                                                               |                    | 200     | 1,250   | 1,800   | mV   |  |  |

| V <sub>OD</sub>                           | Output differential voltage (single-ended)                                              | $R_L = 100 \Omega$ | 250     |         | 710     | mV   |  |  |

| V <sub>OCM</sub>                          | Output common mode voltage                                                              | $R_L = 100 \Omega$ | 840     |         | 1,570   | mV   |  |  |

| R <sub>L</sub>                            | Receiver differential input<br>discrete resistor (external to<br>Stratix II GX devices) |                    | 90      | 100     | 110     | Ω    |  |  |

#### Note to Table 4–30:

<sup>(1)</sup> The top and bottom clock input differential buffers in I/O banks 3, 4, 7, and 8 are powered by  $V_{CCINT}$ , not  $V_{CCIO}$ . The PLL clock output/feedback differential buffers are powered by VCC\_PLL\_OUT. For differential clock output/feedback operation, connect VCC\_PLL\_OUT to 3.3 V.

### **Duty Cycle Distortion**

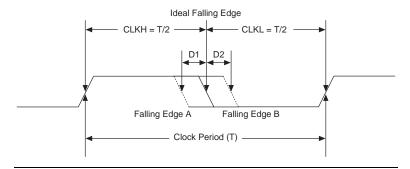

Duty cycle distortion (DCD) describes how much the falling edge of a clock is off from its ideal position. The ideal position is when both the clock high time (CLKH) and the clock low time (CLKL) equal half of the clock period (T), as shown in Figure 4–11. DCD is the deviation of the non-ideal falling edge from the ideal falling edge, such as D1 for the falling edge A and D2 for the falling edge B (see Figure 4–11). The maximum DCD for a clock is the larger value of D1 and D2.

Figure 4-11. Duty Cycle Distortion

DCD expressed in absolution derivation, for example, D1 or D2 in Figure 4–11, is clock-period independent. DCD can also be expressed as a percentage, and the percentage number is clock-period dependent. DCD as a percentage is defined as:

(T/2 - D1) / T (the low percentage boundary)

(T/2 + D2) / T (the high percentage boundary)

#### **DCD Measurement Techniques**

DCD is measured at an FPGA output pin driven by registers inside the corresponding I/O element (IOE) block. When the output is a single data rate signal (non-DDIO), only one edge of the register input clock (positive or negative) triggers output transitions (Figure 4–12). Therefore, any DCD present on the input clock signal or caused by the clock input buffer or different input I/O standard does not transfer to the output signal.

Table 4–102. Maximum DCD for DDIO Output on Column I/O Pins Without PLL in the Clock Path for -3 Devices (Part 2 of 2) Note (1)

| Maximum DCD (ps) for   | Input IO Standard (No PLL in the Clock Path) |          |        |           |        |      |

|------------------------|----------------------------------------------|----------|--------|-----------|--------|------|

| DDIO Column Output I/O | TTL/CMOS                                     |          | SSTL-2 | SSTL/HSTL | HSTL12 | Unit |

| Standard               | 3.3/2.5V                                     | 1.8/1.5V | 2.5V   | 1.8/1.5V  | 1.2V   |      |

| SSTL-18 Class II       | 140                                          | 260      | 70     | 70        | 70     | ps   |

| 1.8-V HSTL Class I     | 150                                          | 270      | 60     | 60        | 60     | ps   |

| 1.8-V HSTL Class II    | 150                                          | 270      | 60     | 60        | 60     | ps   |

| 1.5-V HSTL Class I     | 150                                          | 270      | 55     | 55        | 55     | ps   |

| 1.5-V HSTL Class II    | 125                                          | 240      | 85     | 85        | 85     | ps   |

| 1.2-V HSTL             | 240                                          | 360      | 155    | 155       | 155    | ps   |

| LVPECL                 | 180                                          | 180      | 180    | 180       | 180    | ps   |

(1) Table 4–102 assumes the input clock has zero DCD.

Table 4–103. Maximum DCD for DDIO Output on Column I/O Pins Without PLL in the Clock Path for -4 and -5 Devices Note (1)

| Maximum DCD (ps) for   | Input IO Standard (No PLL in the Clock Path) |          |        |           |      |  |

|------------------------|----------------------------------------------|----------|--------|-----------|------|--|

| DDIO Column Output I/O | TTL/0                                        | смоѕ     | SSTL-2 | SSTL/HSTL | Unit |  |

| Standard               | 3.3/2.5V                                     | 1.8/1.5V | 2.5V   | 1.8/1.5V  |      |  |

| 3.3-V LVTTL            | 440                                          | 495      | 170    | 160       | ps   |  |

| 3.3-V LVCMOS           | 390                                          | 450      | 120    | 110       | ps   |  |

| 2.5 V                  | 375                                          | 430      | 105    | 95        | ps   |  |

| 1.8 V                  | 325                                          | 385      | 90     | 100       | ps   |  |

| 1.5-V LVCMOS           | 430                                          | 490      | 160    | 155       | ps   |  |

| SSTL-2 Class I         | 355                                          | 410      | 85     | 75        | ps   |  |

| SSTL-2 Class II        | 350                                          | 405      | 80     | 70        | ps   |  |

| SSTL-18 Class I        | 335                                          | 390      | 65     | 65        | ps   |  |

| SSTL-18 Class II       | 320                                          | 375      | 70     | 80        | ps   |  |

| 1.8-V HSTL Class I     | 330                                          | 385      | 60     | 70        | ps   |  |

| 1.8-V HSTL Class II    | 330                                          | 385      | 60     | 70        | ps   |  |

| 1.5-V HSTL Class I     | 330                                          | 390      | 60     | 70        | ps   |  |

| 1.5-V HSTL Class II    | 330                                          | 360      | 90     | 100       | ps   |  |

| LVPECL                 | 180                                          | 180      | 180    | 180       | ps   |  |

<sup>(1)</sup> Table 4–103 assumes the input clock has zero DCD.

| Table 4–110. Enhanced PLL Specifications (Part 2 of 2) |                                                                                                                  |         |     |       |      |  |  |

|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|---------|-----|-------|------|--|--|

| Name                                                   | Description                                                                                                      | ion Min |     | Max   | Unit |  |  |

| $f_{VCO}$                                              | PLL VCO operating range for –3 and –4 speed grade devices                                                        | 300     |     | 1,040 | MHz  |  |  |

|                                                        | PLL VCO operating range for –5 speed grade devices                                                               | 300     |     | 840   | MHz  |  |  |

| f <sub>SS</sub>                                        | Spread-spectrum modulation frequency                                                                             | 100     |     | 500   | kHz  |  |  |

| % spread                                               | Percent down spread for a given clock frequency                                                                  | 0.4     | 0.5 | 0.6   | %    |  |  |

| t <sub>PLL_PSERR</sub>                                 | Accuracy of PLL phase shift                                                                                      |         |     | ±30   | ps   |  |  |

| t <sub>ARESET</sub>                                    | Minimum pulse width on areset signal.                                                                            | 10      |     |       | ns   |  |  |

| tareset_reconfig                                       | Minimum pulse width on the areset signal when using PLL reconfiguration. Reset the PLL after scandone goes high. | 500     |     |       | ns   |  |  |

| t <sub>RECONFIGWAIT</sub>                              | The time required for the wait after the reconfiguration is done and the areset is applied.                      |         |     | 2     | us   |  |  |

- (1) This is limited by the I/O  $f_{\mbox{\scriptsize MAX}}.$  See Tables 4–91 through 4–95 for the maximum.

- (2) If the counter cascading feature of the PLL is utilized, there is no minimum output clock frequency.

| Table 4–111. Fast PLL Specifications (Part 1 of 2) |                                                                             |    |     |     |          |  |  |  |

|----------------------------------------------------|-----------------------------------------------------------------------------|----|-----|-----|----------|--|--|--|

| Name                                               | Name Description                                                            |    | Тур | Max | Unit     |  |  |  |

| f <sub>IN</sub>                                    | Input clock frequency (for -3 and -4 speed grade devices)                   | 16 |     | 717 | MHz      |  |  |  |

|                                                    | Input clock frequency (for -5 speed grade devices)                          | 16 |     | 640 | MHz      |  |  |  |

| f <sub>INPFD</sub>                                 | Input frequency to the PFD                                                  | 16 |     | 500 | MHz      |  |  |  |

| f <sub>INDUTY</sub>                                | Input clock duty cycle                                                      | 40 |     | 60  | %        |  |  |  |

| t <sub>INJITTER</sub>                              | Input clock jitter tolerance in terms of period jitter. Bandwidth ⊴ MHz     |    | 0.5 |     | ns (p-p) |  |  |  |

|                                                    | Input clock jitter tolerance in terms of period jitter. Bandwidth > 0.2 MHz |    | 1.0 |     | ns (p-p) |  |  |  |