Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 3022                                                       |

| Number of Logic Elements/Cells | 60440                                                      |

| Total RAM Bits                 | 2544192                                                    |

| Number of I/O                  | 364                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.15V ~ 1.25V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                         |

| Package / Case                 | 780-BBGA                                                   |

| Supplier Device Package        | 780-FBGA (29x29)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2sgx60df780i4 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

There are up to 20 transceiver channels available on a single Stratix II GX device. Table 2–1 shows the number of transceiver channels and their serial bandwidth for each Stratix II GX device.

| Table 2–1. Stratix | Table 2–1. Stratix II GX Transceiver Channels |                                   |  |  |  |  |  |  |  |

|--------------------|-----------------------------------------------|-----------------------------------|--|--|--|--|--|--|--|

| Device             | Number of Transceiver<br>Channels             | Serial Bandwidth<br>(Full Duplex) |  |  |  |  |  |  |  |

| EP2SGX30C          | 4                                             | 51 Gbps                           |  |  |  |  |  |  |  |

| EP2SGX60C          | 4                                             | 51 Gbps                           |  |  |  |  |  |  |  |

| EP2SGX30D          | 8                                             | 102 Gbps                          |  |  |  |  |  |  |  |

| EP2SGX60D          | 8                                             | 102 Gbps                          |  |  |  |  |  |  |  |

| EP2SGX60E          | 12                                            | 153 Gbps                          |  |  |  |  |  |  |  |

| EP2SGX90E          | 12                                            | 153 Gbps                          |  |  |  |  |  |  |  |

| EP2SGX90F          | 16                                            | 204 Gbps                          |  |  |  |  |  |  |  |

| EP2SGX130G         | 20                                            | 255 Gbps                          |  |  |  |  |  |  |  |

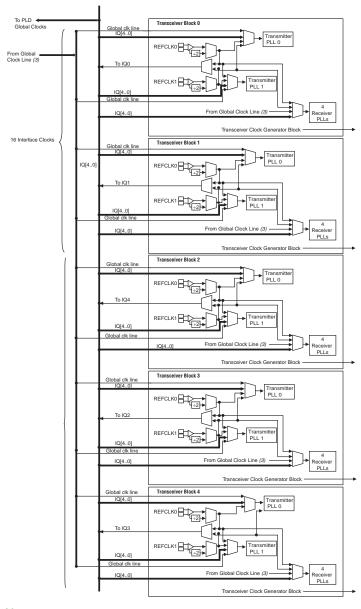

Figure 2–2 shows the elements of the transceiver block, including the four transceiver channels, supporting logic, and I/O buffers. Each transceiver channel consists of a receiver and transmitter. The supporting logic contains two transmitter PLLs to generate the high-speed clock(s) used by the four transmitters within that block. Each of the four transmitter channels has its own individual clock divider. The four receiver PLLs within each transceiver block generate four recovered clocks. The transceiver channels can be configured in one of the following functional modes:

- PCI Express (PIPE)

- OIF CEI PHY Interface

- SONET/SDH

- Gigabit Ethernet (GIGE)

- XAII

- Basic (600 Mbps to 3.125 Gbps single-width mode and 1 Gbps to 6.375 Gbps double-width mode)

- SDI (HD, 3G)

- CPRI (614 Mbps, 1228 Mbps, 2456 Mbps)

- Serial RapidIO (1.25 Gbps, 2.5 Gbps, 3.125 Gbps)

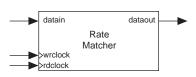

#### Rate Matcher

Rate matcher is available in Basic, PCI Express, XAUI, and GIGE modes and consists of a 20-word deep FIFO buffer and a FIFO controller. Figure 2–20 shows the implementation of the rate matcher in the Stratix II GX device.

Figure 2-20. Rate Matcher

In a multi-crystal environment, the rate matcher compensates for up to a  $\pm$  300-PPM difference between the source and receiver clocks. Table 2–8 shows the standards supported and the PPM for the rate matcher tolerance.

| Table 2–8. Rate Matcher PPM Support Note (1) |       |  |  |  |  |  |

|----------------------------------------------|-------|--|--|--|--|--|

| Standard                                     | PPM   |  |  |  |  |  |

| XAUI                                         | ± 100 |  |  |  |  |  |

| PCI Express (PIPE)                           | ± 300 |  |  |  |  |  |

| GIGE                                         | ± 100 |  |  |  |  |  |

| Basic Double-Width                           | ± 300 |  |  |  |  |  |

Note to Table 2–8:

(1) Refer to the Stratix II GX Transceiver User Guide for the Altera®-defined scheme.

#### **Basic Mode**

In Basic mode, you can program the skip and control pattern for rate matching. In single-width Basic mode, there is no restriction on the deletion of a skip character in a cluster. The rate matcher deletes the skip characters as long as they are available. For insertion, the rate matcher inserts skip characters such that the number of skip characters at the output of rate matcher does not exceed five. In double-width mode, the rate matcher deletes skip character when they appear as pairs in the upper and lower bytes. There are no restrictions on the number of skip characters that are deleted. The rate matcher inserts skip characters as pairs.

Figure 2-29. EP2SGX130 Device Inter-Transceiver and Global Clock Connections

#### *Notes to Figure 2–29:*

- (1) There are two transmitter PLLs in each transceiver block.

- (2) There are four receiver PLLs in each transceiver block.

- (3) The Global Clock line must be driven by an input pin.

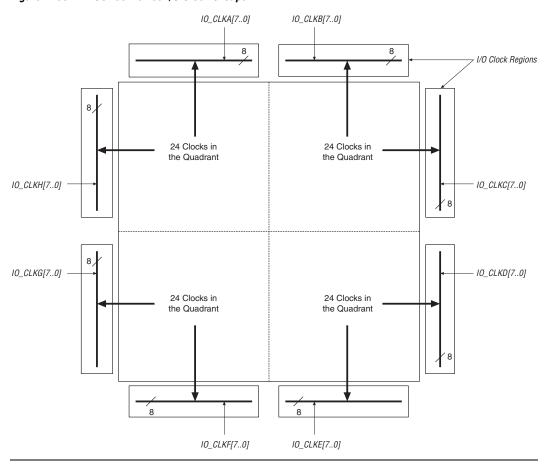

IOE clocks have row and column block regions that are clocked by  $8\,\mathrm{I/O}$  clock signals chosen from the 24 quadrant clock resources. Figures 2–65 and 2–66 show the quadrant relationship to the I/O clock regions.

Figure 2-65. EP2SGX30 Device I/O Clock Groups

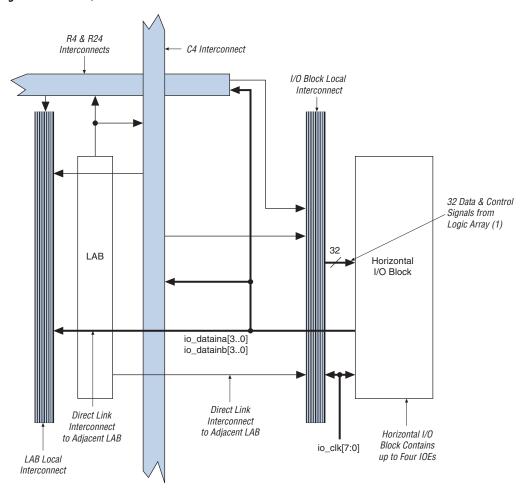

Figure 2–77 shows how a row I/O block connects to the logic array.

Figure 2-77. Row I/O Block Connection to the Interconnect

#### *Note to Figure 2–77:*

(1) The 32 data and control signals consist of eight data out lines: four lines each for DDR applications io\_dataouta[3..0] and io\_dataoutb[3..0], four output enables io\_oe[3..0], four input clock enables io\_ce\_in[3..0], four output clock enables io\_ce\_out[3..0], four clocks io\_clk[3..0], four asynchronous clear and preset signals io\_aclr/apreset[3..0], and four synchronous clear and preset signals io\_sclr/spreset[3..0].

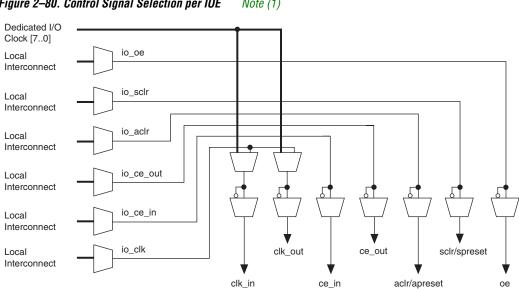

Figure 2-80. Control Signal Selection per IOE Note (1)

#### Note to Figure 2-80:

Control signals ce\_in, ce\_out, aclr/apreset, sclr/spreset, and oe can be global signals even though their control selection multiplexers are not directly fed by the ioe clk [7..0] signals. The ioe clk signals can drive the I/O local interconnect, which then drives the control selection multiplexers.

> In normal bidirectional operation, you can use the input register for input data requiring fast setup times. The input register can have its own clock input and clock enable separate from the OE and output registers. The output register can be used for data requiring fast clock-to-output performance. You can use the OE register for fast clock-to-output enable timing. The OE and output register share the same clock source and the same clock enable source from local interconnect in the associated LAB, dedicated I/O clocks, and the column and row interconnects. Figure 2-81 shows the IOE in bidirectional configuration.

| Table 2-37.           | Table 2–37. Supported TDO/TDI Voltage Combinations (Part 2 of 2) |                           |                           |                            |                           |                           |  |  |  |  |  |  |

|-----------------------|------------------------------------------------------------------|---------------------------|---------------------------|----------------------------|---------------------------|---------------------------|--|--|--|--|--|--|

| Device                | TDI Input                                                        | Sti                       | ratix II GX TDO V         | <sub>CCIO</sub> Voltage Le | vel in I/O Bank           | 4                         |  |  |  |  |  |  |

| Device                | Buffer Power                                                     | V <sub>CC10</sub> = 3.3 V | V <sub>CC10</sub> = 2.5 V | V <sub>CCIO</sub> = 1.8 V  | V <sub>CC10</sub> = 1.5 V | V <sub>CC10</sub> = 1.2 V |  |  |  |  |  |  |

| Non-<br>Stratix II GX | VCC = 3.3 V                                                      | <b>√</b> (1)              | <b>√</b> (2)              | <b>√</b> (3)               | Level shifter required    | Level shifter required    |  |  |  |  |  |  |

|                       | VCC = 2.5 V                                                      | <b>✓</b> (1), (4)         | <b>√</b> (2)              | <b>√</b> (3)               | Level shifter required    | Level shifter required    |  |  |  |  |  |  |

|                       | VCC = 1.8 V                                                      | <b>✓</b> (1), (4)         | <b>√</b> (2), (5)         | <b>✓</b>                   | Level shifter required    | Level shifter required    |  |  |  |  |  |  |

|                       | VCC = 1.5 V                                                      | <b>√</b> (1), (4)         | <b>√</b> (2), (5)         | <b>√</b> (6)               | <b>✓</b>                  | ✓                         |  |  |  |  |  |  |

Notes to Table 2-37:

- (1) The TDO output buffer meets  $V_{OH}(MIN) = 2.4 \text{ V}$ .

- (2) The TDO output buffer meets  $V_{OH}$  (MIN) = 2.0 V.

- (3) An external 250-Ω pull-up resistor is not required, but recommended if signal levels on the board are not optimal.

- (4) Input buffer must be 3.3-V tolerant.

- (5) Input buffer must be 2.5-V tolerant.

- (6) Input buffer must be 1.8-V tolerant.

# High-Speed Differential I/O with DPA Support

Stratix II GX devices contain dedicated circuitry for supporting differential standards at speeds up to 1 Gbps. The LVDS differential I/O standards are supported in the Stratix II GX device. In addition, the LVPECL I/O standard is supported on input and output clock pins on the top and bottom I/O banks.

The high-speed differential I/O circuitry supports the following high-speed I/O interconnect standards and applications:

- SPI-4 Phase 2 (POS-PHY Level 4)

- SFI-4

- Parallel RapidIO standard

There are two dedicated high-speed PLLs in the EP2SGX30 device and four dedicated high-speed PLLs in the EP2SGX60, EP2SGX90, and EP2SGX130 devices to multiply reference clocks and drive high-speed differential SERDES channels.

Tables 2–38 through 2–41 show the number of channels that each Fast PLL can clock in each of the Stratix II GX devices. In Tables 2–38 through 2–41, the first row for each transmitter or receiver provides the number of channels driven directly by the PLL. The second row below it shows the maximum channels a Fast PLL can drive if cross bank channels are used from the adjacent center Fast PLL. For example, in the 780-pin FineLine BGA EP2SGX30 device, PLL 1 can drive a maximum of

| Table 2–41. EP2SGX130 Device Differential Channels   Note (1) |                      |          |          |          |                  |      |  |  |  |  |

|---------------------------------------------------------------|----------------------|----------|----------|----------|------------------|------|--|--|--|--|

| Bookogo                                                       | Transmitter/Passiver | Total    | Center F | ast PLLs | Corner Fast PLLs |      |  |  |  |  |

| Package                                                       | Transmitter/Receiver | Channels | PLL1     | PLL2     | PLL7             | PLL8 |  |  |  |  |

| 1508-pin FineLine BGA                                         | Transmitter          | 71       | 37       | 41       | 37               | 41   |  |  |  |  |

| 1506-pill FilleLille BGA                                      | Receiver             | 73       | 37       | 41       | 37               | 41   |  |  |  |  |

Note to Tables 2-38 through 2-41:

Therefore, the total number of channels is not the addition of the number of channels accessible by PLLs 1 and 2 with the number of channels accessible by PLLs 7 and 8.

## **Dedicated Circuitry with DPA Support**

Stratix II GX devices support source-synchronous interfacing with LVDS signaling at up to 1 Gbps. Stratix II GX devices can transmit or receive serial channels along with a low-speed or high-speed clock.

The receiving device PLL multiplies the clock by an integer factor W=1 through 32. The SERDES factor J determines the parallel data width to deserialize from receivers or to serialize for transmitters. The SERDES factor J can be set to 4, 5, 6, 7, 8, 9, or 10 and does not have to equal the PLL clock-multiplication W value. A design using the dynamic phase aligner also supports all of these J factor values. For a J factor of 1, the Stratix II GX device bypasses the SERDES block. For a J factor of 2, the Stratix II GX device bypasses the SERDES block, and the DDR input and output registers are used in the IOE. Figure 2–88 shows the block diagram of the Stratix II GX transmitter channel.

The total number of receiver channels includes the four non-dedicated clock channels that can be optionally used as data channels.

| Table 2–42. Docu                                         | Table 2–42. Document Revision History (Part 6 of 6) |                    |  |  |  |  |  |  |

|----------------------------------------------------------|-----------------------------------------------------|--------------------|--|--|--|--|--|--|

| Date and<br>Document<br>Version                          | Changes Made                                        | Summary of Changes |  |  |  |  |  |  |

| Previous Chapter<br>03 changes:<br>December 2005<br>v1.1 | Updated Figure 3–56.                                |                    |  |  |  |  |  |  |

| Previous Chapter<br>03 changes:<br>October 2005<br>v1.0  | Added chapter to the Stratix II GX Device Handbook. |                    |  |  |  |  |  |  |

memory, and transmit this compressed bitstream to Stratix II GX FPGAs. During configuration, the Stratix II GX FPGA decompresses the bitstream in real time and programs its SRAM cells. Stratix II GX FPGAs support decompression in the FPP (when using a MAX II device or microprocessor and flash memory), AS, and PS configuration schemes. Decompression is not supported in the PPA configuration scheme nor in JTAG-based configuration.

## **Remote System Upgrades**

Shortened design cycles, evolving standards, and system deployments in remote locations are difficult challenges faced by system designers. Stratix II GX devices can help effectively deal with these challenges with their inherent re programmability and dedicated circuitry to perform remote system updates. Remote system updates help deliver feature enhancements and bug fixes without costly recalls, reducing time to market, and extending product life.

Stratix II GX FPGAs feature dedicated remote system upgrade circuitry to facilitate remote system updates. Soft logic (Nios processor or user logic) implemented in the Stratix II GX device can download a new configuration image from a remote location, store it in configuration memory, and direct the dedicated remote system upgrade circuitry to initiate a reconfiguration cycle. The dedicated circuitry performs error detection during and after the configuration process, recovers from any error condition by reverting back to a safe configuration image, and provides error status information. This dedicated remote system upgrade circuitry avoids system downtime and is the critical component for successful remote system upgrades.

Remote system configuration is supported in the following Stratix II GX configuration schemes: FPP, AS, PS, and PPA. Remote system configuration can also be implemented in conjunction with Stratix II GX features such as real-time decompression of configuration data and design security using AES for secure and efficient field upgrades.

Refer to the *Remote System Upgrades with Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II GX Device Handbook* for more information about remote configuration in Stratix II GX devices.

# Configuring Stratix II GX FPGAs with JRunner

The JRunner<sup>TM</sup> software driver configures Altera FPGAs, including Stratix II GX FPGAs, through the ByteBlaster II or ByteBlasterMV cables in JTAG mode. The programming input file supported is in Raw Binary File (.rbf) format. JRunner also requires a Chain Description File (.cdf)

| Table 4–19. Strat                                | ix II GX Transceiver Bl                                                                                                                                                                                     | ock AC | Specif                                | ication | Notes (                                                 | 1), (2), | (3) <b>(P</b> | art 7 o                               | f 19) |     |      |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------------------------------|---------|---------------------------------------------------------|----------|---------------|---------------------------------------|-------|-----|------|

| Symbol/<br>Description                           | Conditions                                                                                                                                                                                                  |        | -3 Speed<br>Commercial Speed<br>Grade |         | -4 Speed<br>Commercial and<br>Industrial Speed<br>Grade |          |               | -5 Speed<br>Commercial Speed<br>Grade |       |     | Unit |

|                                                  |                                                                                                                                                                                                             | Min    | Тур                                   | Max     | Min                                                     | Тур      | Max           | Min                                   | Тур   | Max |      |

| Sinusoidal Jitter<br>Tolerance<br>(peak-to-peak) | Jitter Frequency = 22.1 KHz Data Rate = 1.25, 2.5, 3.125 Gbps REFCLK = 125 MHz Pattern = CJPAT Equalizer Setting = 0 for 1.25 Gbps Equalizer Setting = 6 for 2.5 Gbps Equalizer Setting = 6 for 3.125 Gbps  |        | > 8.5                                 |         |                                                         | > 8.5    |               |                                       | > 8.5 |     | UI   |

|                                                  | Jitter Frequency = 1.875 MHz Data Rate = 1.25, 2.5, 3.125 Gbps REFCLK = 125 MHz Pattern = CJPAT Equalizer Setting = 0 for 1.25 Gbps Equalizer Setting = 6 for 2.5 Gbps Equalizer Setting = 6 for 3.125 Gbps |        | > 0.1                                 |         |                                                         | > 0.1    |               |                                       | > 0.1 |     | UI   |

|                                                  | Jitter Frequency = 20 MHz Data Rate = 1.25, 2.5, 3.125 Gbps REFCLK = 125 MHz Pattern = CJPAT Equalizer Setting = 0 for 1.25 Gbps Equalizer Setting = 6 for 2.5 Gbps Equalizer Setting = 6 for 3.125 Gbps    |        | > 0.1                                 |         |                                                         | > 0.1    |               |                                       | > 0.1 |     | UI   |

| Table 4–19. Strati                                                | ix II GX Transceiver Bi                                                                                             | lock AC                               | Specif | ication                                                 | Notes ( | (1), (2) | , (3) <b>(P</b>                       | art 9 o | f 19) |      |    |

|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------|---------------------------------------------------------|---------|----------|---------------------------------------|---------|-------|------|----|

| Symbol/<br>Description                                            | Conditions                                                                                                          | -3 Speed<br>Commercial Speed<br>Grade |        | -4 Speed<br>Commercial and<br>Industrial Speed<br>Grade |         |          | -5 Speed<br>Commercial Speed<br>Grade |         |       | Unit |    |

|                                                                   |                                                                                                                     | Min                                   | Тур    | Max                                                     | Min     | Тур      | Max                                   | Min     | Тур   | Max  |    |

| HiGig Receiver Jit                                                | ter Tolerance (13)                                                                                                  |                                       |        |                                                         |         |          |                                       |         |       |      |    |

| Deterministic Jitter<br>Tolerance<br>(peak-to-peak)               | Data Rate = 3.75 Gbps REFCLK = 187.5 MHz Pattern = CJPAT No Equalization DC Gain = 3 dB                             |                                       | > 0.37 | ,                                                       |         | -        |                                       |         | -     |      | U  |

| Combined                                                          | Data Rate = 3.75 Gbps REFCLK = 187.5 MHz Pattern = CJPAT No Equalization DC Gain = 3 dB                             |                                       | > 0.65 | ,                                                       |         | -        |                                       |         | -     |      | UI |

| Deterministic and<br>Random Jitter<br>Tolerance<br>(peak-to-peak) | Jitter Frequency = 22.1 KHz Data Rate = 3.75 Gbps REFCLK = 187.5 MHz Pattern = CJPAT No Equalization DC Gain = 3 dB |                                       | > 8.5  |                                                         |         | -        |                                       |         | -     |      | UI |

| Table 4-3            | Table 4–39. SSTL-2 Class II Specifications |                                  |                         |         |                         |      |  |  |  |  |  |

|----------------------|--------------------------------------------|----------------------------------|-------------------------|---------|-------------------------|------|--|--|--|--|--|

| Symbol               | Parameter                                  | Conditions                       | Minimum                 | Typical | Maximum                 | Unit |  |  |  |  |  |

| V <sub>IH</sub> (DC) | High-level DC input voltage                |                                  | V <sub>REF</sub> + 0.18 |         | V <sub>CCIO</sub> + 0.3 | V    |  |  |  |  |  |

| V <sub>IL</sub> (DC) | Low-level DC input voltage                 |                                  | -0.3                    |         | V <sub>REF</sub> – 0.18 | V    |  |  |  |  |  |

| V <sub>IH</sub> (AC) | High-level AC input voltage                |                                  | V <sub>REF</sub> + 0.35 |         |                         | V    |  |  |  |  |  |

| V <sub>IL</sub> (AC) | Low-level AC input voltage                 |                                  |                         |         | V <sub>REF</sub> - 0.35 | V    |  |  |  |  |  |

| V <sub>OH</sub>      | High-level output voltage                  | $I_{OH} = -16.4 \text{ mA } (1)$ | V <sub>TT</sub> + 0.76  |         |                         | V    |  |  |  |  |  |

| V <sub>OL</sub>      | Low-level output voltage                   | I <sub>OL</sub> = 16.4 mA (1)    |                         |         | V <sub>TT</sub> – 0.76  | V    |  |  |  |  |  |

#### Note to Table 4-39:

(1) This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II GX Architecture* chapter in volume 1 of the *Stratix II GX Device Handbook*.

| Table 4-40.             | Table 4–40. SSTL-2 Class I and II Differential Specifications |            |                              |                       |                      |      |  |  |  |  |  |

|-------------------------|---------------------------------------------------------------|------------|------------------------------|-----------------------|----------------------|------|--|--|--|--|--|

| Symbol                  | Parameter                                                     | Conditions | Minimum                      | Typical               | Maximum              | Unit |  |  |  |  |  |

| $V_{\text{CCIO}}$       | Output supply voltage                                         |            | 2.375                        | 2.5                   | 2.625                | V    |  |  |  |  |  |

| V <sub>SWING</sub> (DC) | DC differential input voltage                                 |            | 0.36                         |                       |                      | V    |  |  |  |  |  |

| V <sub>X</sub> (AC)     | AC differential input cross point voltage                     |            | (V <sub>CCIO</sub> /2) - 0.2 |                       | $(V_{CCIO}/2) + 0.2$ | V    |  |  |  |  |  |

| V <sub>SWING</sub> (AC) | AC differential input voltage                                 |            | 0.7                          |                       |                      | V    |  |  |  |  |  |

| V <sub>ISO</sub>        | Input clock signal offset voltage                             |            |                              | 0.5 V <sub>CCIO</sub> |                      | V    |  |  |  |  |  |

| $\Delta V_{ISO}$        | Input clock signal offset voltage variation                   |            |                              | 200                   |                      | mV   |  |  |  |  |  |

| V <sub>OX</sub> (AC)    | AC differential output cross point voltage                    |            | (V <sub>CCIO</sub> /2) - 0.2 |                       | $(V_{CCIO}/2) + 0.2$ | V    |  |  |  |  |  |

| Table 4-             | Table 4–41. 1.2-V HSTL Specifications |            |                         |                       |                          |      |  |  |  |  |

|----------------------|---------------------------------------|------------|-------------------------|-----------------------|--------------------------|------|--|--|--|--|

| Symbol               | Parameter                             | Conditions | Minimum                 | Typical               | Maximum                  | Unit |  |  |  |  |

| $V_{\text{CCIO}}$    | Output supply voltage                 |            | 1.14                    | 1.2                   | 1.26                     | V    |  |  |  |  |

| $V_{REF}$            | Reference voltage                     |            | 0.48 V <sub>CCIO</sub>  | 0.5 V <sub>CCIO</sub> | 0.52 V <sub>CCIO</sub>   | ٧    |  |  |  |  |

| V <sub>IH</sub> (DC) | High-level DC input voltage           |            | V <sub>REF</sub> + 0.08 |                       | V <sub>CCIO</sub> + 0.15 | ٧    |  |  |  |  |

| V <sub>IL</sub> (DC) | Low-level DC input voltage            |            | -0.15                   |                       | V <sub>REF</sub> - 0.08  | ٧    |  |  |  |  |

| V <sub>IH</sub> (AC) | High-level AC input voltage           |            | V <sub>REF</sub> + 0.15 |                       | V <sub>CCIO</sub> + 0.24 | V    |  |  |  |  |

| V <sub>IL</sub> (AC) | Low-level AC input voltage            |            | -0.24                   |                       | V <sub>REF</sub> – 0.15  | V    |  |  |  |  |

| Table 4-4             | Table 4–44. 1.5-V HSTL Class I and II Differential Specifications |            |         |         |         |      |  |  |  |  |

|-----------------------|-------------------------------------------------------------------|------------|---------|---------|---------|------|--|--|--|--|

| Symbol                | Parameter                                                         | Conditions | Minimum | Typical | Maximum | Unit |  |  |  |  |

| V <sub>CCIO</sub>     | I/O supply voltage                                                |            | 1.425   | 1.5     | 1.575   | V    |  |  |  |  |

| V <sub>DIF</sub> (DC) | DC input differential voltage                                     |            | 0.2     |         |         | ٧    |  |  |  |  |

| V <sub>CM</sub> (DC)  | DC common mode input voltage                                      |            | 0.68    |         | 0.9     | ٧    |  |  |  |  |

| V <sub>DIF</sub> (AC) | AC differential input voltage                                     |            | 0.4     |         |         | V    |  |  |  |  |

| V <sub>OX</sub> (AC)  | AC differential cross point voltage                               |            | 0.68    |         | 0.9     | ٧    |  |  |  |  |

| Table 4-4            | 5. 1.8-V HSTL Class I Specifi | cations                     |                         |         |                        |      |

|----------------------|-------------------------------|-----------------------------|-------------------------|---------|------------------------|------|

| Symbol               | Parameter                     | Conditions                  | Minimum                 | Typical | Maximum                | Unit |

| V <sub>CCIO</sub>    | Output supply voltage         |                             | 1.71                    | 1.80    | 1.89                   | V    |

| $V_{REF}$            | Input reference voltage       |                             | 0.85                    | 0.90    | 0.95                   | V    |

| V <sub>TT</sub>      | Termination voltage           |                             | 0.85                    | 0.90    | 0.95                   | V    |

| V <sub>IH</sub> (DC) | DC high-level input voltage   |                             | V <sub>REF</sub> + 0.1  |         |                        | ٧    |

| V <sub>IL</sub> (DC) | DC low-level input voltage    |                             | -0.3                    |         | V <sub>REF</sub> - 0.1 | V    |

| V <sub>IH</sub> (AC) | AC high-level input voltage   |                             | V <sub>REF</sub> + 0.2  |         |                        | ٧    |

| V <sub>IL</sub> (AC) | AC low-level input voltage    |                             |                         |         | V <sub>REF</sub> - 0.2 | V    |

| V <sub>OH</sub>      | High-level output voltage     | I <sub>OH</sub> = 8 mA (1)  | V <sub>CCIO</sub> - 0.4 |         |                        | ٧    |

| V <sub>OL</sub>      | Low-level output voltage      | I <sub>OH</sub> = -8 mA (1) |                         |         | 0.4                    | V    |

#### Note to Table 4-45:

<sup>(1)</sup> This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II GX Architecture* chapter in volume 1 of the *Stratix II GX Device Handbook*.

# **Bus Hold Specifications**

Table 4–48 shows the Stratix II GX device family bus hold specifications.

| Table 4-48.                  | Table 4–48. Bus Hold Parameters                |       |                         |     |      |      |      |     |      |     |      |      |

|------------------------------|------------------------------------------------|-------|-------------------------|-----|------|------|------|-----|------|-----|------|------|

|                              |                                                |       | V <sub>CCIO</sub> Level |     |      |      |      |     |      |     |      |      |

| Parameter                    | Conditions                                     | 1.2   | 2 V                     | 1.  | .5 V | 1.8  | 8 V  | 2.  | 5 V  | 3.3 | 3 V  | Unit |

|                              |                                                | Min   | Max                     | Min | Max  | Min  | Max  | Min | Max  | Min | Max  |      |

| Low<br>sustaining<br>current | V <sub>IN</sub> > V <sub>IL</sub><br>(maximum) | 22.5  |                         | 25  |      | 30   |      | 50  |      | 70  |      | μΑ   |

| High sustaining current      | V <sub>IN</sub> < V <sub>IH</sub><br>(minimum) | -22.5 |                         | -25 |      | -30  |      | -50 |      | -70 |      | μΑ   |

| Low<br>overdrive<br>current  | 0 V < V <sub>IN</sub> < V <sub>CCIO</sub>      |       | 120                     |     | 160  |      | 200  |     | 300  |     | 500  | μА   |

| High overdrive current       | 0 V < V <sub>IN</sub> < V <sub>CCIO</sub>      |       | -120                    |     | -160 |      | -200 |     | -300 |     | -500 | μА   |

| Bus-hold<br>trip point       |                                                | 0.45  | 0.95                    | 0.5 | 1.0  | 0.68 | 1.07 | 0.7 | 1.7  | 0.8 | 2.0  | ٧    |

# **On-Chip Termination Specifications**

Tables 4–49 and 4–50 define the specification for internal termination resistance tolerance when using series or differential on-chip termination.

| Table 4-4                      | Table 4–49. On-Chip Termination Specification for Top and Bottom I/O Banks (Part 1 of 2)       Notes (1), (2) |                                |        |                      |      |  |  |  |  |  |

|--------------------------------|---------------------------------------------------------------------------------------------------------------|--------------------------------|--------|----------------------|------|--|--|--|--|--|

|                                |                                                                                                               |                                | Resist | Resistance Tolerance |      |  |  |  |  |  |

| Symbol                         | Description                                                                                                   | Conditions Commerc<br>Max      |        | Industrial<br>Max    | Unit |  |  |  |  |  |

| 25-Ω R <sub>S</sub><br>3.3/2.5 | Internal series termination with calibration (25- $\Omega$ setting)                                           | $V_{CCIO} = 3.3/2.5 \text{ V}$ | ±5     | ±10                  | %    |  |  |  |  |  |

|                                | Internal series termination without calibration (25- $\Omega$ setting)                                        | V <sub>CCIO</sub> = 3.3/2.5 V  | ±30    | ±30                  | %    |  |  |  |  |  |

| 50-ΩR <sub>S</sub><br>3.3/2.5  | Internal series termination with calibration (50-Ω setting)                                                   | V <sub>CCIO</sub> = 3.3/2.5 V  | ±5     | ±10                  | %    |  |  |  |  |  |

|                                | Internal series termination without calibration (50- $\Omega$ setting)                                        | V <sub>CCIO</sub> = 3.3/2.5 V  | ±30    | ± 30                 | %    |  |  |  |  |  |

| Table 4-77. E        | Table 4–77. EP2SGX130 Column Pins Regional Clock Timing Parameters |            |          |          |          |        |  |  |  |  |  |

|----------------------|--------------------------------------------------------------------|------------|----------|----------|----------|--------|--|--|--|--|--|

| Parameter            | Fast Corner                                                        |            | -3 Speed | -4 Speed | -5 Speed | Units  |  |  |  |  |  |

|                      | Industrial                                                         | Commercial | Grade    | Grade    | Grade    | UIIIIS |  |  |  |  |  |

| t <sub>CIN</sub>     | 1.815                                                              | 1.834      | 3.218    | 3.417    | 4.087    | ns     |  |  |  |  |  |

| t <sub>COUT</sub>    | 1.650                                                              | 1.669      | 3.218    | 3.417    | 4.087    | ns     |  |  |  |  |  |

| t <sub>PLLCIN</sub>  | 0.116                                                              | 0.134      | 0.349    | 0.364    | 0.426    | ns     |  |  |  |  |  |

| t <sub>PLLCOUT</sub> | -0.049                                                             | -0.031     | 0.361    | 0.378    | 0.444    | ns     |  |  |  |  |  |

| Table 4–78. EP2SGX130 Row Pins Regional Clock Timing Parameters |             |            |          |          |          |        |  |  |  |  |

|-----------------------------------------------------------------|-------------|------------|----------|----------|----------|--------|--|--|--|--|

| Parameter                                                       | Fast Corner |            | -3 Speed | -4 Speed | -5 Speed | Units  |  |  |  |  |

|                                                                 | Industrial  | Commercial | Grade    | Grade    | Grade    | UIIIIS |  |  |  |  |

| t <sub>CIN</sub>                                                | 1.544       | 1.560      | 3.195    | 3.395    | 4.060    | ns     |  |  |  |  |

| t <sub>COUT</sub>                                               | 1.549       | 1.565      | 3.195    | 3.395    | 4.060    | ns     |  |  |  |  |

| t <sub>PLLCIN</sub>                                             | -0.149      | -0.132     | 0.34     | 0.356    | 0.417    | ns     |  |  |  |  |

| t <sub>PLLCOUT</sub>                                            | -0.144      | -0.127     | 0.342    | 0.356    | 0.417    | ns     |  |  |  |  |

# **Clock Network Skew Adders**

The Quartus II software models skew within dedicated clock networks such as global and regional clocks. Therefore, the intra-clock network skew adder is not specified. Table 4–79 specifies the intra-clock skew between any two clock networks driving any registers in the Stratix II GX device.

| Table 4–79. Clock Network Specifications (Part 1 of 2) |                                  |      |  |      |    |  |  |  |

|--------------------------------------------------------|----------------------------------|------|--|------|----|--|--|--|

| Name                                                   | Max                              | Unit |  |      |    |  |  |  |

| Clock skew adder                                       | Inter-clock network, same side   |      |  | ±50  | ps |  |  |  |

| EP2SGX30 (1)                                           | Inter-clock network, entire chip |      |  | ±100 | ps |  |  |  |

| Clock skew adder                                       | Inter-clock network, same side   |      |  | ±50  | ps |  |  |  |

| EP2SGX60 (1)                                           | Inter-clock network, entire chip |      |  | ±100 | ps |  |  |  |

| Clock skew adder                                       | Inter-clock network, same side   |      |  | ±55  | ps |  |  |  |

| EP2SGX90 (1)                                           | Inter-clock network, entire chip |      |  | ±110 | ps |  |  |  |

Table 4–85. Stratix II GX I/O Input Delay for Row Pins (Part 2 of 3)

| I/O Standard        | Parameter          | Fast Corner<br>Industrial/<br>Commercial | -3 Speed<br>Grade (2) | -3 Speed<br>Grade (3) | -4 Speed<br>Grade | -5 Speed<br>Grade | Unit |

|---------------------|--------------------|------------------------------------------|-----------------------|-----------------------|-------------------|-------------------|------|

| LVCMOS              | t <sub>Pl</sub>    | 749                                      | 1287                  | 1350                  | 1435              | 1723              | ps   |

|                     | t <sub>PCOUT</sub> | 410                                      | 760                   | 798                   | 848               | 1018              | ps   |

| SSTL-2 Class I      | t <sub>Pl</sub>    | 573                                      | 879                   | 921                   | 980               | 1176              | ps   |

|                     | t <sub>PCOUT</sub> | 234                                      | 352                   | 369                   | 393               | 471               | ps   |

| SSTL-2 Class II     | t <sub>PI</sub>    | 573                                      | 879                   | 921                   | 980               | 1176              | ps   |

|                     | t <sub>PCOUT</sub> | 234                                      | 352                   | 369                   | 393               | 471               | ps   |

| SSTL-18 Class I     | t <sub>PI</sub>    | 605                                      | 960                   | 1006                  | 1070              | 1285              | ps   |

|                     | t <sub>PCOUT</sub> | 266                                      | 433                   | 454                   | 483               | 580               | ps   |

| SSTL-18 Class II    | t <sub>Pl</sub>    | 605                                      | 960                   | 1006                  | 1070              | 1285              | ps   |

|                     | t <sub>PCOUT</sub> | 266                                      | 433                   | 454                   | 483               | 580               | ps   |

| 1.5-V HSTL Class I  | t <sub>PI</sub>    | 631                                      | 1056                  | 1107                  | 1177              | 1413              | ps   |

|                     | t <sub>PCOUT</sub> | 292                                      | 529                   | 555                   | 590               | 708               | ps   |

| 1.5-V HSTL Class II | t <sub>Pl</sub>    | 631                                      | 1056                  | 1107                  | 1177              | 1413              | ps   |

|                     | t <sub>PCOUT</sub> | 292                                      | 529                   | 555                   | 590               | 708               | ps   |

| 1.8-V HSTL Class I  | t <sub>Pl</sub>    | 605                                      | 960                   | 1006                  | 1070              | 1285              | ps   |

|                     | t <sub>PCOUT</sub> | 266                                      | 433                   | 454                   | 483               | 580               | ps   |

| 1.8-V HSTL Class II | t <sub>Pl</sub>    | 605                                      | 960                   | 1006                  | 1070              | 1285              | ps   |

|                     | t <sub>PCOUT</sub> | 266                                      | 433                   | 454                   | 483               | 580               | ps   |

| PCI                 | t <sub>Pl</sub>    | 830                                      | 1498                  | 1571                  | 1671              | 2006              | ps   |

|                     | t <sub>PCOUT</sub> | 491                                      | 971                   | 1019                  | 1084              | 1301              | ps   |

| PCI-X               | t <sub>Pl</sub>    | 830                                      | 1498                  | 1571                  | 1671              | 2006              | ps   |

|                     | t <sub>PCOUT</sub> | 491                                      | 971                   | 1019                  | 1084              | 1301              | ps   |

| LVDS (1)            | t <sub>PI</sub>    | 540                                      | 948                   | 994                   | 1057              | 1269              | ps   |

|                     | t <sub>PCOUT</sub> | 201                                      | 421                   | 442                   | 470               | 564               | ps   |

| HyperTransport      | t <sub>PI</sub>    | 540                                      | 948                   | 994                   | 1057              | 1269              | ps   |

|                     | t <sub>PCOUT</sub> | 201                                      | 421                   | 442                   | 470               | 564               | ps   |

| Differential SSTL-2 | t <sub>Pl</sub>    | 573                                      | 879                   | 921                   | 980               | 1176              | ps   |

| Class I             | t <sub>PCOUT</sub> | 234                                      | 352                   | 369                   | 393               | 471               | ps   |

| Differential SSTL-2 | t <sub>Pl</sub>    | 573                                      | 879                   | 921                   | 980               | 1176              | ps   |

| Class II            | t <sub>PCOUT</sub> | 234                                      | 352                   | 369                   | 393               | 471               | ps   |

Therefore, the DCD percentage for the output clock is from 48.4% to 51.6%.

Table 4–101. Maximum DCD for DDIO Output on Row I/O Pins Without PLL in the Clock Path for -4 and -5 Devices Note (1)

| Maximum DCD (ps) for |          | Input I/O Star | ndard (No PL | L in the Clock | Path) |      |

|----------------------|----------|----------------|--------------|----------------|-------|------|

| Row DDIO Output I/O  | TTL/0    | CMOS           | SSTL-2       | SSTL/HSTL      | LVDS  | Unit |

| Standard             | 3.3/2.5V | 1.8/1.5V       | 2.5V         | 1.8/1.5V       | 3.3V  |      |

| 3.3-V LVTTL          | 440      | 495            | 170          | 160            | 105   | ps   |

| 3.3-V LVCMOS         | 390      | 450            | 120          | 110            | 75    | ps   |

| 2.5 V                | 375      | 430            | 105          | 95             | 90    | ps   |

| 1.8 V                | 325      | 385            | 90           | 100            | 135   | ps   |

| 1.5-V LVCMOS         | 430      | 490            | 160          | 155            | 100   | ps   |

| SSTL-2 Class I       | 355      | 410            | 85           | 75             | 85    | ps   |

| SSTL-2 Class II      | 350      | 405            | 80           | 70             | 90    | ps   |

| SSTL-18 Class I      | 335      | 390            | 65           | 65             | 105   | ps   |

| 1.8-V HSTL Class I   | 330      | 385            | 60           | 70             | 110   | ps   |

| 1.5-V HSTL Class I   | 330      | 390            | 60           | 70             | 105   | ps   |

| LVDS                 | 180      | 180            | 180          | 180            | 180   | ps   |

(1) Table 4–101 assumes the input clock has zero DCD.

Table 4–102. Maximum DCD for DDIO Output on Column I/O Pins Without PLL in the Clock Path for -3

Devices (Part 1 of 2) Note (1)

| Maximum DCD (ps) for   | In       | )        |        |           |        |      |

|------------------------|----------|----------|--------|-----------|--------|------|

| DDIO Column Output I/O | TTL/0    | CMOS     | SSTL-2 | SSTL/HSTL | HSTL12 | Unit |

| Standard               | 3.3/2.5V | 1.8/1.5V | 2.5V   | 1.8/1.5V  | 1.2V   |      |

| 3.3-V LVTTL            | 260      | 380      | 145    | 145       | 145    | ps   |

| 3.3-V LVCMOS           | 210      | 330      | 100    | 100       | 100    | ps   |

| 2.5 V                  | 195      | 315      | 85     | 85        | 85     | ps   |

| 1.8 V                  | 150      | 265      | 85     | 85        | 85     | ps   |

| 1.5-V LVCMOS           | 255      | 370      | 140    | 140       | 140    | ps   |

| SSTL-2 Class I         | 175      | 295      | 65     | 65        | 65     | ps   |

| SSTL-2 Class II        | 170      | 290      | 60     | 60        | 60     | ps   |

| SSTL-18 Class I        | 155      | 275      | 55     | 50        | 50     | ps   |

Table 4–108 shows the high-speed I/O timing specifications for -4 speed grade Stratix II GX devices.

| •                                    |                                         |                                               |             | -4 S |      |       |                       |  |

|--------------------------------------|-----------------------------------------|-----------------------------------------------|-------------|------|------|-------|-----------------------|--|

| Symbol                               | Conditions                              |                                               |             |      | Тур  | Max   | Unit                  |  |

| $f_{IN} = f_{HSDR} / W$              | W = 2 to 32 (LVDS, I                    | HyperTransport                                | technology) | 16   |      | 520   | MHz                   |  |

|                                      | W = 1 (SERDES by                        | pass, LVDS only                               | /)          | 16   |      | 500   | MHz                   |  |

|                                      | W = 1 (SERDES us                        | ed, LVDS only)                                |             | 150  |      | 717   | MHz                   |  |

| f <sub>HSDR</sub> (data rate)        | J = 4 to 10 (LVDS, F                    | lyperTransport t                              | technology) | 150  |      | 1,040 | Mbps                  |  |

|                                      | J = 2 (LVDS, HyperTransport technology) |                                               |             |      |      | 760   | Mbps                  |  |

|                                      | J = 1 (LVDS only)                       | (4)                                           |             | 500  | Mbps |       |                       |  |

| f <sub>HSDRDPA</sub> (DPA data rate) | J = 4 to 10 (LVDS, F                    | J = 4 to 10 (LVDS, HyperTransport technology) |             |      |      |       | Mbps                  |  |

| TCCS                                 | All differential stand                  | ards                                          |             | -    |      | 200   | ps                    |  |

| SW                                   | All differential stand                  | ards                                          |             | 330  |      | -     | ps                    |  |

| Output jitter                        |                                         |                                               |             |      |      | 190   | ps                    |  |

| Output t <sub>RISE</sub>             | All differential I/O sta                | andards                                       |             |      |      | 160   | ps                    |  |

| Output t <sub>FALL</sub>             | All differential I/O sta                | andards                                       |             |      |      | 180   | ps                    |  |

| t <sub>DUTY</sub>                    |                                         |                                               |             | 45   | 50   | 55    | %                     |  |

| DPA run length                       |                                         |                                               |             |      |      | 6,400 | UI                    |  |

| DPA jitter tolerance                 | Data channel peak-                      | to-peak jitter                                |             | 0.44 |      |       | UI                    |  |

| DPA lock time                        |                                         |                                               |             |      |      |       | Number of repetitions |  |

|                                      | SPI-4                                   | 000000000<br>1111111111                       | 10%         | 256  |      |       |                       |  |

|                                      | Parallel Rapid I/O                      |                                               | 25%         | 256  |      |       | 1                     |  |

|                                      |                                         | 10010000                                      | 50%         | 256  |      |       | 1                     |  |

|                                      | Miscellaneous                           | 10101010                                      | 100%        | 256  |      |       | 1                     |  |

|                                      |                                         | 01010101                                      |             | 256  |      |       | 1                     |  |

<sup>(1)</sup> When J = 4 to 10, the SERDES block is used.

<sup>(2)</sup> When J = 1 or 2, the SERDES block is bypassed.

<sup>(3)</sup> The input clock frequency and the W factor must satisfy the following fast PLL VCO specification: 150 ≤nput clock frequency × W ≤1,040.

<sup>(4)</sup> The minimum specification is dependent on the clock source (fast PLL, enhanced PLL, clock pin, and so on) and the clock routing resource (global, regional, or local) utilized. The I/O differential buffer and input register do not have a minimum toggle rate.

# PLL Timing Specifications

Tables 4–110 and 4–111 describe the Stratix II GX PLL specifications when operating in both the commercial junction temperature range (0 to 85 C) and the industrial junction temperature range (–40 to 100 C), except for the clock switchover and phase-shift stepping features. These two features are only supported from the 0 to 100 C junction temperature range.

| Name                    | Description                                                                                                                     | Min     | Тур                      | Max                                                              | Unit                  |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------|---------|--------------------------|------------------------------------------------------------------|-----------------------|

| $f_{IN}$                | Input clock frequency                                                                                                           | 4       |                          | 500                                                              | MHz                   |

| f <sub>INPFD</sub>      | Input frequency to the PFD                                                                                                      | 4       |                          | 420                                                              | MHz                   |

| f <sub>INDUTY</sub>     | Input clock duty cycle                                                                                                          | 40      |                          | 60                                                               | %                     |

| f <sub>ENDUTY</sub>     | External feedback input clock duty cycle                                                                                        | 40      |                          | 60                                                               | %                     |

| t <sub>INJITTER</sub>   | Input or external feedback clock input jitter tolerance in terms of period jitter. Bandwidth ⊴0.85 MHz                          |         | 0.5                      |                                                                  | ns (peak-<br>to-peak) |

|                         | Input or external feedback clock input jitter tolerance in terms of period jitter. Bandwidth > 0.85 MHz                         |         | 1.0                      |                                                                  | ns (peak-<br>to-peak) |

| toutjitter              | Dedicated clock output period jitter                                                                                            |         |                          | 250 ps for ≥<br>100 MHz outclk<br>25 mUl for <<br>100 MHz outclk | ps or mUI<br>(p-p)    |

| t <sub>FCOMP</sub>      | External feedback compensation time                                                                                             |         |                          | 10                                                               | ns                    |

| f <sub>OUT</sub>        | Output frequency for internal global or regional clock                                                                          | 1.5 (2) |                          | 550                                                              | MHz                   |

| f <sub>OUTDUTY</sub>    | Duty cycle for external clock output                                                                                            | 45      | 50                       | 55                                                               | %                     |

| f <sub>SCANCLK</sub>    | Scanclk frequency                                                                                                               |         |                          | 100                                                              | MHz                   |

| t <sub>CONFIGEPLL</sub> | Time required to reconfigure scan chains for EPLLs                                                                              |         | 174/f <sub>SCANCLK</sub> |                                                                  | ns                    |

| f <sub>OUT_EXT</sub>    | PLL external clock output frequency                                                                                             | 1.5 (2) |                          | (1)                                                              | MHz                   |

| t <sub>LOCK</sub>       | Time required for the PLL to lock from the time it is enabled or the end of device configuration                                |         | 0.03                     | 1                                                                | ms                    |

| t <sub>DLOCK</sub>      | Time required for the PLL to lock<br>dynamically after automatic clock<br>switchover between two identical clock<br>frequencies |         |                          | 1                                                                | ms                    |

| f <sub>SWITCHOVER</sub> | Frequency range where the clock switchover performs properly                                                                    | 1.5     | 1                        | 500                                                              | MHz                   |

| f <sub>CLBW</sub>       | PLL closed-loop bandwidth                                                                                                       | 0.13    | 1.2                      | 16.9                                                             | MHz                   |