Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | 3022                                                         |

| Number of Logic Elements/Cells | 60440                                                        |

| Total RAM Bits                 | 2544192                                                      |

| Number of I/O                  | 534                                                          |

| Number of Gates                | -                                                            |

| Voltage - Supply               | 1.15V ~ 1.25V                                                |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                           |

| Package / Case                 | 1152-BBGA                                                    |

| Supplier Device Package        | 1152-FBGA (35x35)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2sgx60ef1152i4n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The CRU has a built-in switchover circuit to select whether the PLL VCO is aligned by the reference clock or the data. The optional port rx freqlocked monitors when the CRU is in locked-to-data mode.

In the automatic mode, the CRU PLL must be within the prescribed PPM frequency threshold setting of the CRU reference clock for the CRU to switch from locked-to-reference to locked-to-data mode.

The automatic switchover circuit can be overridden by using the optional ports rx\_locktorefclk and rx\_locktodata. Table 2–6 shows the possible combinations of these two signals.

| Table 2–6. Receiver Lock Combinations |                              |                 |  |  |  |  |

|---------------------------------------|------------------------------|-----------------|--|--|--|--|

| rx_locktodata                         | rx_locktorefk VCO (Lock to N |                 |  |  |  |  |

| 0                                     | 0                            | Auto            |  |  |  |  |

| 0                                     | 1                            | Reference clock |  |  |  |  |

| 1                                     | х                            | Data            |  |  |  |  |

If the rx\_locktorefclk and rx\_locktodata ports are not used, the default is auto mode.

### Deserializer (Serial-to-Parallel Converter)

The deserializer converts a serial bitstream into 8, 10, 16, or 20 bits of parallel data. The deserializer receives the LSB first. Figure 2–17 shows the deserializer.

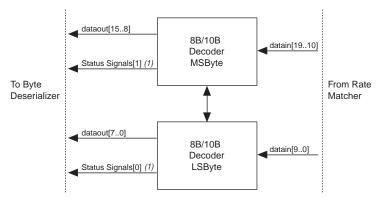

Figure 2-21. 8B/10B Decoder

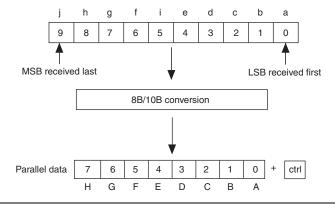

The 8B/10B decoder in single-width mode translates the 10-bit encoded data into the 8-bit equivalent data or control code. The 10-bit code received must be from the supported Dx.y or Kx.y list with the proper disparity or error flags asserted. All 8B/10B control signals, such as disparity error or control detect, are pipelined with the data and edge-aligned with the data. Figure 2–22 shows how the 10-bit symbol is decoded in the 8-bit data + 1-bit control indicator.

Figure 2-22. 8B/10B Decoder Conversion

The 8B/10B decoder in double-width mode translates the 20-bit (2  $\times$  10-bits) encoded code into the 16-bit (2  $\times$  8-bits) equivalent data or control code. The 20-bit upper and lower symbols received must be from the supported Dx.y or Kx.y list with the proper disparity or error flags

The dynamic reconfiguration block can dynamically reconfigure the following PMA settings:

- Pre-emphasis settings

- Equalizer and DC gain settings

- Voltage Output Differential (V<sub>OD</sub>) settings

The channel reconfiguration allows you to dynamically modify the data rate, local dividers, and the functional mode of the transceiver channel.

Refer to the *Stratix II GX Device Handbook*, volume 2, for more information.

The dynamic reconfiguration block requires an input clock between 2.5 MHz and 50 MHz. The clock for the dynamic reconfiguration block is derived from a high-speed clock and divided down using a counter.

#### Individual Power Down and Reset for the Transmitter and Receiver

Stratix II GX transceivers offer a power saving advantage with their ability to shut off functions that are not needed. The device can individually reset the receiver and transmitter blocks and the PLLs. The Stratix II GX device can either globally or individually power down and reset the transceiver. Table  $2{\text -}16$  shows the connectivity between the reset signals and the Stratix II GX transceiver blocks. These reset signals can be controlled from the FPGA or pins.

| Table 2–18. Stratix II GX Device Routing Scheme (Part 2 of 2) |                         |             |                |                    |                          |                 |                  |                 |                  |     |                |               |             |            |            |         |

|---------------------------------------------------------------|-------------------------|-------------|----------------|--------------------|--------------------------|-----------------|------------------|-----------------|------------------|-----|----------------|---------------|-------------|------------|------------|---------|

| Destination                                                   |                         |             |                |                    |                          |                 |                  |                 |                  |     |                |               |             |            |            |         |

| Source                                                        | Shared Arithmetic Chair | Carry Chain | Register Chain | Local Interconnect | Direct Link Interconnect | R4 Interconnect | R24 Interconnect | C4 Interconnect | C16 Interconnect | ALM | M512 RAM Block | M4K RAM Block | M-RAM Block | DSP Blocks | Column IOE | Row IOE |

| Column IOE                                                    |                         |             |                |                    | <b>✓</b>                 |                 |                  | <b>✓</b>        | <b>✓</b>         |     |                |               |             |            |            |         |

| Row IOE                                                       |                         |             |                |                    | <b>✓</b>                 | <b>✓</b>        | <b>✓</b>         | <b>✓</b>        |                  |     |                |               |             |            |            |         |

# TriMatrix Memory

TriMatrix memory consists of three types of RAM blocks: M512, M4K, and M-RAM. Although these memory blocks are different, they can all implement various types of memory with or without parity, including true dual-port, simple dual-port, and single-port RAM, ROM, and FIFO buffers. Table 2–19 shows the size and features of the different RAM blocks.

| Table 2–19. TriMatrix Memory Features (Part 1 of 2) |                                  |                                  |                                |  |  |  |

|-----------------------------------------------------|----------------------------------|----------------------------------|--------------------------------|--|--|--|

| Memory Feature                                      | M512 RAM Block<br>(32 x 18 Bits) | M4K RAM Block<br>(128 × 36 Bits) | M-RAM Block<br>(4K × 144 Bits) |  |  |  |

| Maximum performance                                 | 500 MHz                          | 550 MHz                          | 420 MHz                        |  |  |  |

| True dual-port memory                               |                                  | ✓                                | ✓                              |  |  |  |

| Simple dual-port memory                             | ✓                                | ✓                                | ✓                              |  |  |  |

| Single-port memory                                  | ✓                                | ✓                                | ✓                              |  |  |  |

| Shift register                                      | ✓                                | ✓                                |                                |  |  |  |

| ROM                                                 | ✓                                | ✓                                | (1)                            |  |  |  |

| FIFO buffer                                         | ✓                                | ✓                                | ✓                              |  |  |  |

| Pack mode                                           |                                  | ✓                                | ✓                              |  |  |  |

| Byte enable                                         | ✓                                | ✓                                | ✓                              |  |  |  |

| Address clock enable                                |                                  | ✓                                | ✓                              |  |  |  |

| Parity bits                                         | ✓                                | ✓                                | ✓                              |  |  |  |

| Mixed clock mode                                    | ✓                                | ✓                                | ✓                              |  |  |  |

| Memory initialization (.mif)                        | ✓                                | ✓                                |                                |  |  |  |

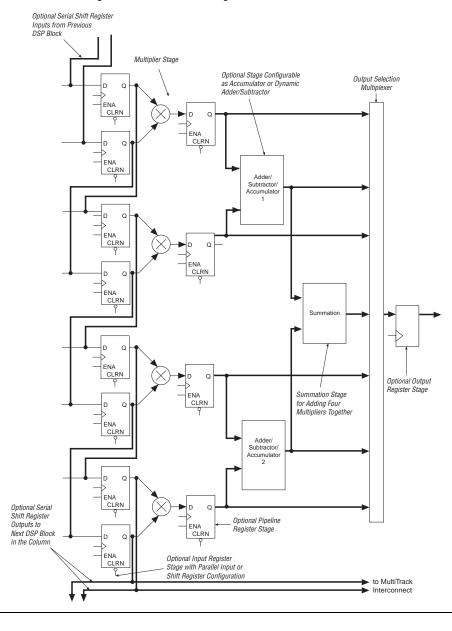

Figure 2-58. DSP Block Diagram for 18 x 18-Bit Configuration

## PLLs and Clock Networks

Stratix II GX devices provide a hierarchical clock structure and multiple phase-locked loops (PLLs) with advanced features. The large number of clocking resources in combination with the clock synthesis precision provided by enhanced and fast PLLs provides a complete clock management solution.

### Global and Hierarchical Clocking

Stratix II GX devices provide 16 dedicated global clock networks and 32 regional clock networks (eight per device quadrant). These clocks are organized into a hierarchical clock structure that allows for up to 24 clocks per device region with low skew and delay. This hierarchical clocking scheme provides up to 48 unique clock domains in Stratix II GX devices.

There are 12 dedicated clock pins to dive either the global or regional clock networks. Four clock pins drive each side of the device, as shown in Figures 2–61 and 2–62 Internal logic and enhanced and fast PLL outputs can also drive the global and regional clock networks. Each global and regional clock has a clock control block, which controls the selection of the clock source and dynamically enables or disables the clock to reduce power consumption. Table 2–24 shows global and regional clock features.

| Table 2 24. Global and Regional Clock Features |                                                                        |                                                                        |  |  |  |  |

|------------------------------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------|--|--|--|--|

| Feature                                        | Global Clocks                                                          | Regional Clocks                                                        |  |  |  |  |

| Number per device                              | 16                                                                     | 32                                                                     |  |  |  |  |

| Number available per quadrant                  | 16                                                                     | 8                                                                      |  |  |  |  |

| Sources                                        | Clock pins, PLL outputs,<br>core routings,<br>inter-transceiver clocks | Clock pins, PLL outputs,<br>core routings,<br>inter-transceiver clocks |  |  |  |  |

| Dynamic clock source selection                 | V                                                                      | _                                                                      |  |  |  |  |

| Dynamic enable/disable                         | V                                                                      | V                                                                      |  |  |  |  |

#### Global Clock Network

These clocks drive throughout the entire device, feeding all device quadrants. The global clock networks can be used as clock sources for all resources in the device IOEs, ALMs, DSP blocks, and all memory blocks. These resources can also be used for control signals, such as clock enables and synchronous or asynchronous clears fed from the external pin. The global clock networks can also be driven by internal logic for internally

Table 3–5shows the specifications for bias voltage and current of the Stratix II GX temperature sensing diode.

| Table 3 5. Temperature-Sensingdlei Electrical Characteristics |         |         |        |       |  |  |  |

|---------------------------------------------------------------|---------|---------|--------|-------|--|--|--|

| Parameter                                                     | Minimum | Typical | Maximu | ım Un |  |  |  |

| IBIAS high                                                    | 80      | 100     | 120    | А     |  |  |  |

| IBIAS low                                                     | 8       | 10      | 12     | Α     |  |  |  |

| VBP - VBN                                                     | 0.3     |         | 0.9    | V     |  |  |  |

| VBN                                                           |         | 0.7     |        | V     |  |  |  |

| Series resistance                                             |         |         | 3      |       |  |  |  |

The temperature-sensing diode works for the entire operating range shown in Figure 3–2.

Figure 3 2. Temperature Versums plerature-Sensing Diode Voltage