Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Obsolete                                                      |

| Number of LABs/CLBs            | 4548                                                          |

| Number of Logic Elements/Cells | 90960                                                         |

| Total RAM Bits                 | 4520448                                                       |

| Number of I/O                  | 558                                                           |

| Number of Gates                | -                                                             |

| Voltage - Supply               | 1.15V ~ 1.25V                                                 |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                               |

| Package / Case                 | 1152-BBGA                                                     |

| Supplier Device Package        | 1152-FBGA (35x35)                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2sgx90ef1152c3es |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Transmit State Machine

The transmit state machine operates in either PCI Express mode, XAUI mode, or GIGE mode, depending on the protocol used. The state machine is not utilized for certain protocols, such as SONET.

#### GIGE Mode

In GIGE mode, the transmit state machine converts all idle ordered sets (/K28.5/, /Dx.y/) to either /I1/ or /I2/ ordered sets. /I1/ consists of a negative-ending disparity /K28.5/ (denoted by /K28.5/-) followed by a neutral /D5.6/. /I2/ consists of a positive-ending disparity /K28.5/ (denoted by /K28.5/+) and a negative-ending disparity /D16.2/ (denoted by /D16.2/-). The transmit state machines do not convert any of the ordered sets to match /C1/ or /C2/, which are the configuration ordered sets. (/C1/ and /C2/ are defined by [/K28.5/, /D21.5/] and [/K28.5/, /D2.2/], respectively). Both the /I1/ and /I2/ ordered sets guarantee a negative-ending disparity after each ordered set.

#### XAUI Mode

The transmit state machine translates the XAUI XGMII code group to the XAUI PCS code group. Table 2–5 shows the code conversion.

| Table 2–5. | Table 2–5. Code Conversion                |                                        |                         |  |  |  |  |  |  |

|------------|-------------------------------------------|----------------------------------------|-------------------------|--|--|--|--|--|--|

| XGMII TXC  | XGMII TXD                                 | PCS Code-Group                         | Description             |  |  |  |  |  |  |

| 0          | 00 through FF                             | Dxx.y                                  | Normal data             |  |  |  |  |  |  |

| 1          | 07                                        | K28.0 or K28.3 or<br>K28.5             | Idle in    <b>I</b>     |  |  |  |  |  |  |

| 1          | 07                                        | K28.5                                  | Idle in   T             |  |  |  |  |  |  |

| 1          | 9C                                        | K28.4                                  | Sequence                |  |  |  |  |  |  |

| 1          | FB                                        | K27.7                                  | Start                   |  |  |  |  |  |  |

| 1          | FD                                        | K29.7                                  | Terminate               |  |  |  |  |  |  |

| 1          | FE                                        | K30.7                                  | Error                   |  |  |  |  |  |  |

| 1          | See IEEE 802.3<br>reserved code<br>groups | See IEEE 802.3<br>reserved code groups | Reserved code groups    |  |  |  |  |  |  |

| 1          | Other value                               | K30.7                                  | Invalid XGMII character |  |  |  |  |  |  |

The XAUI PCS idle code groups, /K28.0/ (/R/) and /K28.5/ (/K/), are automatically randomized based on a PRBS7 pattern with an  $x^7 + x^6 + 1$  polynomial. The /K28.3/ (/A/) code group is automatically generated between 16 and 31 idle code groups. The idle randomization on the /A/, /K/, and /R/ code groups is done automatically by the transmit state machine.

Refer to the *Stratix II GX Transceiver Architecture Overview* chapter in volume 2 of the *Stratix II GX Handbook*.

The output buffer, as shown in Figure 2–8, is directly driven by the high-speed data serializer and consists of a programmable output driver, a programmable pre-emphasis circuit, a programmable termination, and a programmable  $V_{\text{CM}}$ .

Serializer

Output Buffer

Programmable

Pre-Emphasis

Programmable

Termination

Output

Pins

Output

Driver

Figure 2-8. Output Buffer

### **Programmable Output Driver**

The programmable output driver can be set to drive out differentially 200 to 1,400 mV. The differential output voltage ( $V_{OD}$ ) can be changed dynamically, or statically set by using the ALT2GXB megafunction or through I/O pins.

The output driver may be programmed with four different differential termination values:

- 100 Ω

- 120 Ω

- 150 Ω

- External termination

The rx syncstatus signal is not available in bit-slipping mode.

### Channel Aligner

The channel aligner is available only in XAUI mode and aligns the signals of all four channels within a transceiver. The channel aligner follows the IEEE 802.3ae, clause 48 specification for channel bonding.

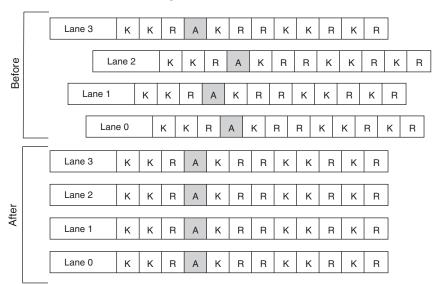

The channel aligner is a 16-word FIFO buffer with a state machine controlling the channel bonding process. The state machine looks for an /A/(K28.3/) in each channel, and aligns all the /A/ code groups in the transceiver. When four columns of /A/ (denoted by //A//) are detected, the <code>rx\_channelaligned</code> signal goes high, signifying that all the channels in the transceiver have been aligned. The reception of four consecutive misaligned /A/ code groups restarts the channel alignment sequence and sends the <code>rx\_channelaligned</code> signal low.

Figure 2–19 shows misaligned channels before the channel aligner and the aligned channels after the channel aligner.

Figure 2-19. Before and After the Channel Aligner

| Clo                     |                 | Resource          | Transceiver            |                        |                        |                        |                        |  |  |

|-------------------------|-----------------|-------------------|------------------------|------------------------|------------------------|------------------------|------------------------|--|--|

| Region                  | Global<br>Clock | Regional<br>Clock | Bank 13<br>8 Clock I/O | Bank 14<br>8 Clock I/O | Bank 15<br>8 clock I/O | Bank 16<br>8 Clock I/O | Bank 17<br>8 Clock I/O |  |  |

| Region0<br>8 LRIO clock | <b>✓</b>        | RCLK 20-27        | <b>✓</b>               |                        |                        |                        |                        |  |  |

| Region1<br>8 LRIO clock | ~               | RCLK 20-27        |                        | <b>✓</b>               |                        |                        |                        |  |  |

| Region2<br>8 LRIO clock | ~               | RCLK 12-19        |                        |                        | ✓                      | ~                      |                        |  |  |

| Region3<br>8 LRIO clock | ~               | RCLK 12-19        |                        |                        |                        | ~                      | <b>✓</b>               |  |  |

### **Other Transceiver Features**

Other important features of the Stratix II GX transceivers are the power down and reset capabilities, external voltage reference and bias circuitry, and hot swapping.

#### Calibration Block

The Stratix II GX device uses the calibration block to calibrate the on-chip termination for the PLLs and their associated output buffers and the terminating resistors on the transceivers. The calibration block counters the effects of process, voltage, and temperature (PVT). The calibration block references a derived voltage across an external reference resistor to calibrate the on-chip termination resistors on the Stratix II GX device. The calibration block can be powered down. However, powering down the calibration block during operations may yield transmit and receive data errors.

## Dynamic Reconfiguration

This feature allows you to dynamically reconfigure the PMA portion and the channel parameters, such as data rate and functional mode, of the Stratix II GX transceiver. The PMA reconfiguration allows you to quickly optimize the settings for the transceiver's PMA to achieve the intended bit error rate (BER).

The dynamic reconfiguration block can dynamically reconfigure the following PMA settings:

- Pre-emphasis settings

- Equalizer and DC gain settings

- Voltage Output Differential (V<sub>OD</sub>) settings

The channel reconfiguration allows you to dynamically modify the data rate, local dividers, and the functional mode of the transceiver channel.

Refer to the *Stratix II GX Device Handbook*, volume 2, for more information.

The dynamic reconfiguration block requires an input clock between 2.5 MHz and 50 MHz. The clock for the dynamic reconfiguration block is derived from a high-speed clock and divided down using a counter.

#### Individual Power Down and Reset for the Transmitter and Receiver

Stratix II GX transceivers offer a power saving advantage with their ability to shut off functions that are not needed. The device can individually reset the receiver and transmitter blocks and the PLLs. The Stratix II GX device can either globally or individually power down and reset the transceiver. Table  $2{\text -}16$  shows the connectivity between the reset signals and the Stratix II GX transceiver blocks. These reset signals can be controlled from the FPGA or pins.

Figure 2-33. Direct Link Connection Direct link interconnect from Direct link interconnect from left LAB, TriMatrix™ memory right LAB, TriMatrix memory block, DSP block, or block, DSP block, or IOE output input/output element (IOE) ALMs Direct link Direct link interconnect < interconnect to left to right Local Interconnect LAB

Figure 2–33 shows the direct link connection.

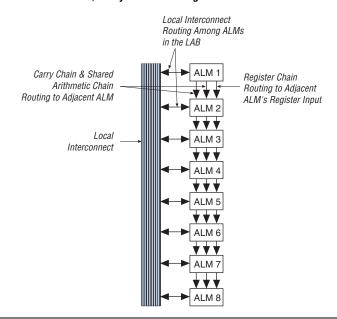

## **LAB Control Signals**

Each LAB contains dedicated logic for driving control signals to its ALMs. The control signals include three clocks, three clock enables, two asynchronous clears, synchronous clear, asynchronous preset/load, and synchronous load control signals, providing a maximum of 11 control signals at a time. Although synchronous load and clear signals are generally used when implementing counters, they can also be used with other functions.

Each LAB can use three clocks and three clock enable signals. However, there can only be up to two unique clocks per LAB, as shown in the LAB control signal generation circuit in Figure 2–34. Each LAB's clock and clock enable signals are linked. For example, any ALM in a particular LAB using the labclk1 signal also uses labclkena1. If the LAB uses both the rising and falling edges of a clock, it also uses two LAB-wide clock signals. De-asserting the clock enable signal turns off the corresponding LAB-wide clock. Each LAB can use two asynchronous clear signals and an asynchronous load/preset signal. The asynchronous

Figure 2-42. Conditional Operation Example

The arithmetic mode also offers clock enable, counter enable, synchronous up and down control, add and subtract control, synchronous clear, synchronous load. The LAB local interconnect data inputs generate the clock enable, counter enable, synchronous up and down and add and subtract control signals. These control signals may be used for the inputs that are shared between the four LUTs in the ALM. The synchronous clear and synchronous load options are LAB-wide signals that affect all registers in the LAB. The Quartus II software automatically places any registers that are not used by the counter into other LABs.

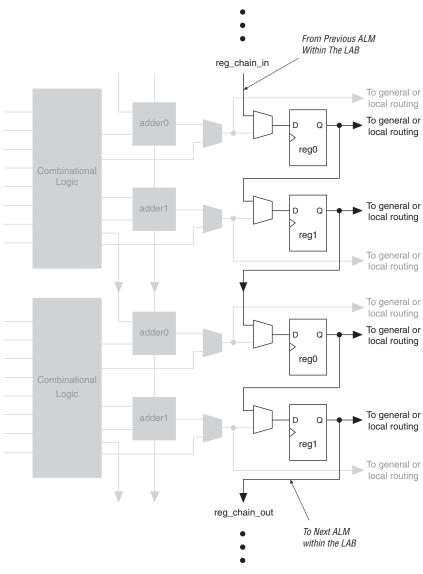

Figure 2–45. Register Chain within a LAB Note (1)

Note to Figure 2-45:

(1) The combinational or adder logic can be utilized to implement an unrelated, un-registered function.

## **Clear and Preset Logic Control**

LAB-wide signals control the logic for the register's clear and load/preset signals. The ALM directly supports an asynchronous clear and preset function. The register preset is achieved through the asynchronous load of a logic high. The direct asynchronous preset does not require a NOT gate push-back technique. Stratix II GX devices support simultaneous asynchronous load/preset and clear signals. An asynchronous clear signal takes precedence if both signals are asserted simultaneously. Each LAB supports up to two clears and one load/preset signal.

In addition to the clear and load/preset ports, Stratix II GX devices provide a device-wide reset pin (DEV\_CLRn) that resets all registers in the device. An option set before compilation in the Quartus II software controls this pin. This device-wide reset overrides all other control signals.

## MultiTrack Interconnect

In the Stratix II GX architecture, the MultiTrack interconnect structure with DirectDrive technology provides connections between ALMs, TriMatrix memory, DSP blocks, and device I/O pins. The MultiTrack interconnect consists of continuous, performance-optimized routing lines of different lengths and speeds used for inter- and intra-design block connectivity. The Quartus II Compiler automatically places critical design paths on faster interconnects to improve design performance.

DirectDrive technology is a deterministic routing technology that ensures identical routing resource usage for any function regardless of placement in the device. The MultiTrack interconnect and DirectDrive technology simplify the integration stage of block-based designing by eliminating the re-optimization cycles that typically follow design changes and additions.

The MultiTrack interconnect consists of row and column interconnects that span fixed distances. A routing structure with fixed length resources for all devices allows predictable and repeatable performance when migrating through different device densities. Dedicated row interconnects route signals to and from LABs, DSP blocks, and TriMatrix memory in the same row.

These row resources include:

- Direct link interconnects between LABs and adjacent blocks

- R4 interconnects traversing four blocks to the right or left

- R24 row interconnects for high-speed access across the length of the device

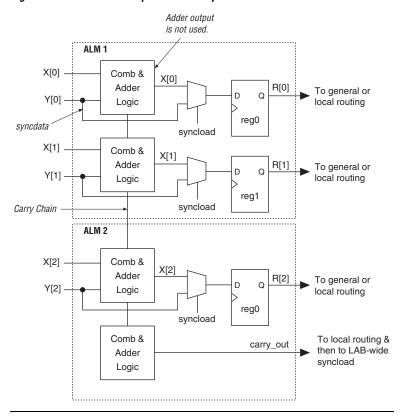

Figure 2-47. Shared Arithmetic Chain, Carry Chain and Register Chain Interconnects

The C4 interconnects span four LABs, M512, or M4K blocks up or down from a source LAB. Every LAB has its own set of C4 interconnects to drive either up or down. Figure 2–48 shows the C4 interconnect connections from a LAB in a column. The C4 interconnects can drive and be driven by all types of architecture blocks, including DSP blocks, TriMatrix memory blocks, and column and row IOEs. For LAB interconnection, a primary LAB or its LAB neighbor can drive a given C4 interconnect. C4 interconnects can drive each other to extend their range as well as drive row interconnects for column-to-column connections.

## **Modes of Operation**

The adder, subtractor, and accumulate functions of a DSP block have four modes of operation:

- Simple multiplier

- Multiply-accumulator

- Two-multipliers adder

- Four-multipliers adder

Table 2–22 shows the different number of multipliers possible in each DSP block mode according to size. These modes allow the DSP blocks to implement numerous applications for DSP including FFTs, complex FIR, FIR, 2D FIR filters, equalizers, IIR, correlators, matrix multiplication, and many other functions. The DSP blocks also support mixed modes and mixed multiplier sizes in the same block. For example, half of one DSP block can implement one  $18 \times 18$ -bit multiplier in multiply-accumulator mode, while the other half of the DSP block implements four  $9 \times 9$ -bit multipliers in simple multiplier mode.

| Table 2–22. Multiplier Size and Configurations per DSP Block |                                                        |                                                         |                                        |  |  |  |  |  |

|--------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------|----------------------------------------|--|--|--|--|--|

| DSP Block Mode                                               | 9 × 9                                                  | 18 × 18                                                 | 36 × 36                                |  |  |  |  |  |

| Multiplier                                                   | Eight multipliers with eight product outputs           | Four multipliers with four product outputs              | One multiplier with one product output |  |  |  |  |  |

| Multiply-accumulator                                         | _                                                      | Two 52-bit multiply-<br>accumulate blocks               | _                                      |  |  |  |  |  |

| Two-multipliers adder                                        | Four two-multiplier adder (two 9 × 9 complex multiply) | Two two-multiplier adder (one 18 × 18 complex multiply) | _                                      |  |  |  |  |  |

| Four-multipliers adder                                       | Two four-multiplier adder                              | One four-multiplier adder                               | _                                      |  |  |  |  |  |

#### **DSP Block Interface**

The Stratix II GX device DSP block input registers can generate a shift register that can cascade down in the same DSP block column. Dedicated connections between DSP blocks provide fast connections between the shift register inputs to cascade the shift register chains. You can cascade registers within multiple DSP blocks for 9  $\times$  9- or 18  $\times$  18-bit FIR filters larger than four taps, with additional adder stages implemented in ALMs. If the DSP block is configured as 36  $\times$  36 bits, the adder, subtractor, or accumulator stages are implemented in ALMs. Each DSP block can route the shift register chain out of the block to cascade multiple columns of DSP blocks.

| Table 2-42. Docu                                        | ment Revision History (Part 5 of 6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                     |  |  |  |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--|--|--|

| Date and<br>Document<br>Version                         | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Summary of Changes                                                                  |  |  |  |

| Previous Chapter<br>02 changes:<br>June 2006, v1.2      | <ul> <li>Updated notes 1 and 2 in Figure 2–1.</li> <li>Updated "Byte Serializer" section.</li> <li>Updated Tables 2–4, 2–7, and 2–16.</li> <li>Updated "Programmable Output Driver" section.</li> <li>Updated Figure 2–12.</li> <li>Updated "Programmable Pre-Emphasis" section.</li> <li>Added Table 2–11.</li> <li>Added "Dynamic Reconfiguration" section.</li> <li>Added "Calibration Block" section.</li> <li>Updated "Programmable Equalizer" section, including addition of Figure 2–18.</li> </ul> | Updated input frequency range in Table 2–4.                                         |  |  |  |

| Previous Chapter<br>02 changes:<br>April 2006, v1.1     | <ul> <li>Updated Figure 2–3.</li> <li>Updated Figure 2–7.</li> <li>Updated Table 2–4.</li> <li>Updated "Transmit Buffer" section.</li> </ul>                                                                                                                                                                                                                                                                                                                                                               | Updated input frequency range in Table 2–4.                                         |  |  |  |

| Previous Chapter<br>02 changes:<br>October 2005<br>v1.0 | Added chapter to the Stratix II GX Device Handbook.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                     |  |  |  |

| Previous Chapter<br>03 changes:<br>August 2006, v1.4    | Updated Table 3–18 with note.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                     |  |  |  |

| Previous Chapter<br>03 changes:<br>June 2006, v1.3      | <ul> <li>Updated note 2 in Figure 3–41.</li> <li>Updated column title in Table 3–21.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                     |  |  |  |

| Previous Chapter<br>03 changes:<br>April 2006, v1.2     | <ul> <li>Updated note 1 in Table 3–9.</li> <li>Updated note 1 in Figure 3–40.</li> <li>Updated note 2 in Figure 3–41.</li> <li>Updated Table 3–16.</li> <li>Updated Figure 3–56.</li> <li>Updated Tables 3–19 through 3–22.</li> <li>Updated Tables 3–25 and 3–26.</li> <li>Updated "Fast PLL &amp; Channel Layout" section.</li> </ul>                                                                                                                                                                    | Added 1,152-pin FineLine BGA package information for EP2SGX60 device in Table 3–16. |  |  |  |

## 3. Configuration & Testing

SIIGX51005-1.4

## IEEE Std. 1149.1 JTAG Boundary-Scan Support

All Stratix<sup>®</sup> II GX devices provide Joint Test Action Group (JTAG) boundary-scan test (BST) circuitry that complies with the IEEE Std. 1149.1. You can perform JTAG boundary-scan testing either before or after, but not during configuration. Stratix II GX devices can also use the JTAG port for configuration with the Quartus<sup>®</sup> II software or hardware using either Jam Files (.jam) or Jam Byte-Code Files (.jbc).

Stratix II GX devices support IOE I/O standard setting reconfiguration through the JTAG BST chain. The JTAG chain can update the I/O standard for all input and output pins any time before or during user mode through the CONFIG\_IO instruction. You can use this capability for JTAG testing before configuration when some of the Stratix II GX pins drive or receive from other devices on the board using voltage-referenced standards. Since the Stratix II GX device may not be configured before JTAG testing, the I/O pins may not be configured for appropriate electrical standards for chip-to-chip communication. Programming these I/O standards via JTAG allows you to fully test I/O connections to other devices.

A device operating in JTAG mode uses four required pins, TDI, TDO, TMS, and TCK, and one optional pin, TRST. The TCK pin has an internal weak pull-down resistor, while the TDI, TMS, and TRST pins have weak internal pull-up resistors. The JTAG input pins are powered by the 3.3-V VCCPD pins. The TDO output pin is powered by the VCCIO power supply in I/O bank 4.

Stratix II GX devices also use the JTAG port to monitor the logic operation of the device with the SignalTap<sup>®</sup> II embedded logic analyzer. Stratix II GX devices support the JTAG instructions shown in Table 3–1.

Stratix II GX devices must be within the first eight devices in a JTAG chain. All of these devices have the same JTAG controller. If any of the Stratix II GX devices appear after the eighth device in the JTAG chain, they will fail configuration. This does not affect SignalTap II embedded logic analysis.

| Table 4–11. Typical $V_{0D}$ Setting, TX Term = 120 $\Omega$ Note (1) |     |                              |     |     |     |  |  |  |

|-----------------------------------------------------------------------|-----|------------------------------|-----|-----|-----|--|--|--|

| V <sub>CCH</sub> TX = 1.2 V                                           |     | V <sub>OD</sub> Setting (mV) |     |     |     |  |  |  |

|                                                                       | 192 | 192 384 576 768 960          |     |     |     |  |  |  |

| V <sub>OD</sub> Typical (mV)                                          | 210 | 410                          | 600 | 780 | 960 |  |  |  |

Note to Table 4–11:

Applicable to data rates from 600 Mbps to 3.125 Gbps. Specification is for measurement at the package ball.

| Table 4–12. Typical $V_{OD}$ Setting, TX Term = 150 $\Omega$ Note (1) |                 |                              |     |     |  |  |  |

|-----------------------------------------------------------------------|-----------------|------------------------------|-----|-----|--|--|--|

| V <sub>CCH</sub> TX = 1.2 V                                           |                 | V <sub>OD</sub> Setting (mV) |     |     |  |  |  |

|                                                                       | 240 480 720 960 |                              |     |     |  |  |  |

| V <sub>OD</sub> Typical (mV)                                          | 260             | 500                          | 730 | 960 |  |  |  |

Note to Table 4–12:

Applicable to data rates from 600 Mbps to 3.125 Gbps. Specification is for measurement at the package ball.

Tables 4–13 through 4–18 show the typical first post-tap pre-emphasis.

| Table 4-                           | -13. Typi | cal Pre-E                         | mphasis    | (First Po  | ost-Tap),  | Note (1)   | (Part 1     | of 2)       |              |              |              |              |

|------------------------------------|-----------|-----------------------------------|------------|------------|------------|------------|-------------|-------------|--------------|--------------|--------------|--------------|

| V <sub>CCH</sub> TX<br>= 1.5 V     |           | First Post Tap Pre-Emphasis Level |            |            |            |            |             |             |              |              |              |              |

| V <sub>OD</sub><br>Setting<br>(mV) | 1         | 1 2 3 4 5 6 7 8 9 10 11 12        |            |            |            |            |             |             |              |              | 12           |              |

|                                    |           |                                   |            |            |            | TX Term    | = 100 Ω     | !           |              |              |              |              |

| 400                                | 24%       | 62%                               | 112%       | 184%       |            |            |             |             |              |              |              |              |

| 600                                |           | 31%                               | 56%        | 86%        | 122%       | 168%       | 230%        | 329%        | 457%         |              |              |              |

|                                    |           |                                   |            |            |            |            |             |             |              |              |              |              |

| 800                                |           | 20%                               | 35%        | 53%        | 73%        | 96%        | 123%        | 156%        | 196%         | 237%         | 312%         | 387%         |

| 800<br>1000                        |           | 20%                               | 35%<br>23% | 53%<br>36% | 73%<br>49% | 96%<br>64% | 123%<br>79% | 156%<br>97% | 196%<br>118% | 237%<br>141% | 312%<br>165% | 387%<br>200% |

| Symbol/<br>Description                                                 | Conditions                                                                                                                                                                                                            | -3 Speed<br>Commercial Speed<br>Conditions Grade |       | -4 Speed<br>Commercial and<br>Industrial Speed<br>Grade |     |       | -5 Speed<br>Commercial Speed<br>Grade |     |     | Unit |    |

|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-------|---------------------------------------------------------|-----|-------|---------------------------------------|-----|-----|------|----|

|                                                                        |                                                                                                                                                                                                                       | Min                                              | Тур   | Max                                                     | Min | Тур   | Max                                   | Min | Тур | Max  |    |

| Sinusoidal Jitter<br>Tolerance<br>(peak-to-peak) <i>(6)</i><br>(cont.) | Jitter Frequency = 20 MHz Data Rate = 614.4 Mbps, 1.2288 Gbps, 2.4576 Gbps REFCLK = 61.44 MHz for 614.4 Mbps REFCLK = 122.88 MHz for 1.2288 Gbps and 2.4576 Gbps Pattern = CJPAT Equalizer Setting = 6 DC Gain = 0 dB |                                                  | > 0.1 |                                                         |     | > 0.1 |                                       |     | N/A |      | UI |

| Table 4-74. E        | Table 4–74. EP2SGX90 Row Pins Regional Clock Timing Parameters |             |       |          |          |       |  |  |  |  |

|----------------------|----------------------------------------------------------------|-------------|-------|----------|----------|-------|--|--|--|--|

| Daramatar            | Fast                                                           | Fast Corner |       | -4 Speed | -5 Speed | Unito |  |  |  |  |

| Parameter            | Industrial                                                     | Commercial  | Grade | Grade    | Grade    | Units |  |  |  |  |

| t <sub>CIN</sub>     | 1.444                                                          | 1.461       | 2.792 | 3.108    | 3.716    | ns    |  |  |  |  |

| t <sub>COUT</sub>    | 1.449                                                          | 1.466       | 2.792 | 3.108    | 3.716    | ns    |  |  |  |  |

| t <sub>PLLCIN</sub>  | -0.348                                                         | -0.333      | 0.204 | 0.217    | 0.243    | ns    |  |  |  |  |

| t <sub>PLLCOUT</sub> | -0.343                                                         | -0.328      | 0.212 | 0.217    | 0.254    | ns    |  |  |  |  |

## EP2SGX130 Clock Timing Parameters

Tables 4–75 through 4–78 show the maximum clock timing parameters for EP2SGX130 devices.

| Table 4–75. EP2SGX130 Column Pins Global Clock Timing Parameters |             |            |          |          |          |        |  |  |  |

|------------------------------------------------------------------|-------------|------------|----------|----------|----------|--------|--|--|--|

| Parameter                                                        | Fast Corner |            | -3 Speed | -4 Speed | -5 Speed | Units  |  |  |  |

| rarameter                                                        | Industrial  | Commercial | Grade    | Grade    | Grade    | UIIIIS |  |  |  |

| t <sub>CIN</sub>                                                 | 1.980       | 1.998      | 3.491    | 3.706    | 4.434    | ns     |  |  |  |

| t <sub>COUT</sub>                                                | 1.815       | 1.833      | 3.237    | 3.436    | 4.110    | ns     |  |  |  |

| t <sub>PLLCIN</sub>                                              | -0.027      | -0.009     | 0.307    | 0.322    | 0.376    | ns     |  |  |  |

| t <sub>PLLCOUT</sub>                                             | -0.192      | -0.174     | 0.053    | 0.052    | 0.052    | ns     |  |  |  |

| Table 4–76. EP2SGX130 Row Pins Global Clock Timing Parameters |            |            |          |          |          |        |  |  |  |

|---------------------------------------------------------------|------------|------------|----------|----------|----------|--------|--|--|--|

| Davamatav                                                     | Fast       | Corner     | -3 Speed | -4 Speed | -5 Speed | lluite |  |  |  |

| Parameter                                                     | Industrial | Commercial | Grade    | Grade    | Grade    | Units  |  |  |  |

| t <sub>CIN</sub>                                              | 1.741      | 1.759      | 3.112    | 3.303    | 3.950    | ns     |  |  |  |

| t <sub>cout</sub>                                             | 1.746      | 1.764      | 3.108    | 3.299    | 3.945    | ns     |  |  |  |

| t <sub>PLLCIN</sub>                                           | -0.261     | -0.243     | -0.089   | -0.099   | -0.129   | ns     |  |  |  |

| t <sub>PLLCOUT</sub>                                          | -0.256     | -0.238     | -0.093   | -0.103   | -0.134   | ns     |  |  |  |

Table 4–91 shows the maximum output clock toggle rates for Stratix II GX device column pins.

| I/O Standard    | Drive Strength | -3 Speed Grade | -4 Speed Grade | -5 Speed Grade | Unit |

|-----------------|----------------|----------------|----------------|----------------|------|

| LVTTL           | 4 mA           | 270            | 225            | 210            | MHz  |

|                 | 8 mA           | 435            | 355            | 325            | MHz  |

|                 | 12 mA          | 580            | 475            | 420            | MHz  |

|                 | 16 mA          | 720            | 594            | 520            | MHz  |

|                 | 20 mA          | 875            | 700            | 610            | MHz  |

|                 | 24 mA (1)      | 1030           | 794            | 670            | MHz  |

| LVCMOS          | 4 mA           | 290            | 250            | 230            | MHz  |

|                 | 8 mA           | 565            | 480            | 440            | MHz  |

|                 | 12 mA          | 790            | 710            | 670            | MHz  |

|                 | 16 mA          | 1020           | 925            | 875            | MHz  |

|                 | 20 mA          | 1066           | 985            | 935            | MHz  |

|                 | 24 mA (1)      | 1100           | 1040           | 1000           | MHz  |

| 2.5 V           | 4 mA           | 230            | 194            | 180            | MHz  |

|                 | 8 mA           | 430            | 380            | 380            | MHz  |

|                 | 12 mA          | 630            | 575            | 550            | MHz  |

|                 | 16 mA (1)      | 930            | 845            | 820            | MHz  |

| 1.8 V           | 2 mA           | 120            | 109            | 104            | MHz  |

|                 | 4 mA           | 285            | 250            | 230            | MHz  |

|                 | 6 mA           | 450            | 390            | 360            | MHz  |

|                 | 8 mA           | 660            | 570            | 520            | MHz  |

|                 | 10 mA          | 905            | 805            | 755            | MHz  |

|                 | 12 mA (1)      | 1131           | 1040           | 990            | MHz  |

| 1.5 V           | 2 mA           | 244            | 200            | 180            | MHz  |

|                 | 4 mA           | 470            | 370            | 325            | MHz  |

|                 | 6 mA           | 550            | 430            | 375            | MHz  |

|                 | 8 mA (1)       | 625            | 495            | 420            | MHz  |

| SSTL-2 Class I  | 8 mA           | 400            | 300            | 300            | MHz  |

|                 | 12 mA (1)      | 400            | 400            | 350            | MHz  |

| SSTL-2 Class II | 16 mA          | 350            | 350            | 300            | MHz  |

|                 | 20 mA          | 400            | 350            | 350            | MHz  |

|                 | 24 mA (1)      | 400            | 400            | 350            | MHz  |

Table 4–94. Stratix II GX Maximum Output Clock Rate for Column Pins (Series Termination) (Part 2 of 2)

| I/O Standard                        | Drive Strength | -3 Speed Grade | -4 Speed Grade | -5 Speed Grade | Unit |

|-------------------------------------|----------------|----------------|----------------|----------------|------|

| SSTL-18 Class I                     | OCT_50_OHMS    | 560            | 400            | 350            | MHz  |

| SSTL-18 Class II                    | OCT_25_OHMS    | 550            | 500            | 450            | MHz  |

| 1.5-V HSTL<br>Class I               | OCT_50_OHMS    | 600            | 550            | 500            | MHz  |

| 1.8-V HSTL<br>Class I               | OCT_50_OHMS    | 650            | 600            | 600            | MHz  |

| 1.8-V HSTL<br>Class II              | OCT_25_OHMS    | 500            | 500            | 450            | MHz  |

| Differential<br>SSTL-2 Class I      | OCT_50_OHMS    | 600            | 500            | 500            | MHz  |

| Differential<br>SSTL-2 Class II     | OCT_25_OHMS    | 600            | 550            | 500            | MHz  |

| Differential<br>SSTL-18 Class I     | OCT_50_OHMS    | 560            | 400            | 350            | MHz  |

| Differential<br>SSTL-18 Class II    | OCT_25_OHMS    | 550            | 500            | 450            | MHz  |

| 1.8-V differential<br>HSTL Class I  | OCT_50_OHMS    | 650            | 600            | 600            | MHz  |

| 1.8-V differential<br>HSTL Class II | OCT_25_OHMS    | 500            | 500            | 450            | MHz  |

| 1.5-V differential<br>HSTL Class I  | OCT_50_OHMS    | 600            | 550            | 500            | MHz  |

Table 4–95 shows the maximum output clock toggle rate for Stratix II GX device series-terminated row pins.

| Table 4–95. Stratix II GX Maximum Output Clock Rate for Row Pins (Series Termination) (Part 1 of 2) |                |                |                |                |      |  |  |  |

|-----------------------------------------------------------------------------------------------------|----------------|----------------|----------------|----------------|------|--|--|--|

| I/O Standard                                                                                        | Drive Strength | -3 Speed Grade | -4 Speed Grade | -5 Speed Grade | Unit |  |  |  |

| LVTTL                                                                                               | OCT_25_OHMS    | 400            | 400            | 350            | MHz  |  |  |  |

|                                                                                                     | OCT_50_OHMS    | 400            | 400            | 350            | MHz  |  |  |  |

| LVCMOS                                                                                              | OCT_25_OHMS    | 350            | 350            | 300            | MHz  |  |  |  |

|                                                                                                     | OCT_50_OHMS    | 350            | 350            | 300            | MHz  |  |  |  |

| 2.5 V                                                                                               | OCT_25_OHMS    | 350            | 350            | 300            | MHz  |  |  |  |

|                                                                                                     | OCT_50_OHMS    | 350            | 350            | 300            | MHz  |  |  |  |

| 1.8 V                                                                                               | OCT_50_OHMS    | 700            | 550            | 450            | MHz  |  |  |  |

| 1.5 V                                                                                               | OCT_50_OHMS    | 550            | 450            | 400            | MHz  |  |  |  |

| Table 4–97. Maximum Output Clock Toggle Rate Derating Factors (Part 4 of 5) |                                                           |                 |     |              |    |    |                            |     |     |     |

|-----------------------------------------------------------------------------|-----------------------------------------------------------|-----------------|-----|--------------|----|----|----------------------------|-----|-----|-----|

|                                                                             | Maximum Output Clock Toggle Rate Derating Factors (ps/pF) |                 |     |              |    |    |                            | )   |     |     |

| I/O Standard                                                                | Drive<br>Strength                                         | Column I/O Pins |     | Row I/O Pins |    |    | Dedicated Clock<br>Outputs |     |     |     |

|                                                                             |                                                           | -3              | -4  | -5           | -3 | -4 | -5                         | -3  | -4  | -5  |

| 1.5-V HSTL                                                                  | 16 mA                                                     | 95              | 101 | 101          | -  | -  | -                          | 96  | 101 | 101 |

| Class II                                                                    | 18 mA                                                     | 95              | 100 | 100          | -  | -  | -                          | 101 | 100 | 100 |

|                                                                             | 20 mA                                                     | 94              | 101 | 101          | -  | -  | -                          | 104 | 101 | 101 |

| 2.5-V differential                                                          | 8 mA                                                      | 364             | 680 | 680          | -  | -  | -                          | 350 | 680 | 680 |

| SSTL Class II (3)                                                           | 12 mA                                                     | 163             | 207 | 207          | -  | -  | -                          | 188 | 207 | 207 |

|                                                                             | 16 mA                                                     | 118             | 147 | 147          | -  | -  | ı                          | 94  | 147 | 147 |

|                                                                             | 20 mA                                                     | 99              | 122 | 122          | -  | -  | -                          | 87  | 122 | 122 |

|                                                                             | 24 mA                                                     | 91              | 116 | 116          | -  | -  | ı                          | 85  | 116 | 116 |

| 1.8-V differential                                                          | 4 mA                                                      | 458             | 570 | 570          | -  | -  | ·                          | 505 | 570 | 570 |

| SSTL Class I (3)                                                            | 6 mA                                                      | 305             | 380 | 380          | -  | -  | -                          | 336 | 380 | 380 |

|                                                                             | 8 mA                                                      | 225             | 282 | 282          | -  | -  | -                          | 248 | 282 | 282 |

|                                                                             | 10 mA                                                     | 167             | 220 | 220          | -  | -  | -                          | 190 | 220 | 220 |

|                                                                             | 12 mA                                                     | 129             | 175 | 175          | -  | -  | -                          | 148 | 175 | 175 |

| 1.8-V differential                                                          | 8 mA                                                      | 173             | 206 | 206          | -  | -  | ·                          | 155 | 206 | 206 |

| SSTL Class II (3)                                                           | 16 mA                                                     | 150             | 160 | 160          | -  | -  | ·                          | 140 | 160 | 160 |

|                                                                             | 18 mA                                                     | 120             | 130 | 130          | -  | -  | -                          | 110 | 130 | 130 |

|                                                                             | 20 mA                                                     | 109             | 127 | 127          | -  | -  | -                          | 94  | 127 | 127 |

| 1.8-V differential                                                          | 4 mA                                                      | 245             | 282 | 282          | -  | -  | -                          | 229 | 282 | 282 |

| HSTL Class I (3)                                                            | 6 mA                                                      | 164             | 188 | 188          | -  | -  | -                          | 153 | 188 | 188 |

|                                                                             | 8 mA                                                      | 123             | 140 | 140          | -  | -  | -                          | 114 | 140 | 140 |

|                                                                             | 10 mA                                                     | 110             | 124 | 124          | -  | -  | -                          | 108 | 124 | 124 |

|                                                                             | 12 mA                                                     | 97              | 110 | 110          | -  | -  | -                          | 104 | 110 | 110 |

| 1.8-V differential                                                          | 16 mA                                                     | 101             | 104 | 104          | -  | -  | -                          | 99  | 104 | 104 |

| HSTL Class II (3)                                                           | 18 mA                                                     | 98              | 102 | 102          | -  | -  | -                          | 93  | 102 | 102 |

|                                                                             | 20 mA                                                     | 93              | 99  | 99           | -  | -  | -                          | 88  | 99  | 99  |

| 1.5-V differential                                                          | 4 mA                                                      | 168             | 196 | 196          | -  | -  | -                          | 188 | 196 | 196 |

| HSTL Class I (3)                                                            | 6 mA                                                      | 112             | 131 | 131          | -  | -  | -                          | 125 | 131 | 131 |

|                                                                             | 8 mA                                                      | 84              | 99  | 99           | -  | -  | -                          | 95  | 99  | 99  |

|                                                                             | 10 mA                                                     | 87              | 98  | 98           | -  | -  | -                          | 90  | 98  | 98  |

|                                                                             | 12 mA                                                     | 86              | 98  | 98           | -  | -  | -                          | 87  | 98  | 98  |

г

Table 4–108 shows the high-speed I/O timing specifications for -4 speed grade Stratix II GX devices.

| Table 4–108. High-Speed I/O Specifications for -4 Speed Grade Notes (1), (2) |                                |                         |             |      |       |       |                       |  |  |

|------------------------------------------------------------------------------|--------------------------------|-------------------------|-------------|------|-------|-------|-----------------------|--|--|

| Comple at                                                                    |                                | -4 Speed Grade          |             |      | T     |       |                       |  |  |

| Symbol                                                                       | Conditions                     |                         |             |      | Тур   | Max   | Unit                  |  |  |

| $f_{IN} = f_{HSDR} / W$                                                      | W = 2 to 32 (LVDS, I           | 16                      |             | 520  | MHz   |       |                       |  |  |

|                                                                              | W = 1 (SERDES by               | pass, LVDS only         | y)          | 16   |       | 500   | MHz                   |  |  |

|                                                                              | W = 1 (SERDES used, LVDS only) |                         |             |      |       | 717   | MHz                   |  |  |

| f <sub>HSDR</sub> (data rate)                                                | J = 4 to 10 (LVDS, F           | lyperTransport t        | technology) | 150  |       | 1,040 | Mbps                  |  |  |

|                                                                              | J = 2 (LVDS, Hyper             | (4)                     |             | 760  | Mbps  |       |                       |  |  |

|                                                                              | J = 1 (LVDS only)              | (4)                     |             | 500  | Mbps  |       |                       |  |  |

| f <sub>HSDRDPA</sub> (DPA data rate)                                         | J = 4 to 10 (LVDS, F           | lyperTransport t        | 150         |      | 1,040 | Mbps  |                       |  |  |

| TCCS                                                                         | All differential stand         | ards                    | -           |      | 200   | ps    |                       |  |  |

| SW                                                                           | All differential stand         |                         | 330         |      | -     | ps    |                       |  |  |

| Output jitter                                                                |                                |                         |             |      |       | 190   | ps                    |  |  |

| Output t <sub>RISE</sub>                                                     | All differential I/O sta       | andards                 |             |      |       | 160   | ps                    |  |  |

| Output t <sub>FALL</sub>                                                     | All differential I/O sta       | andards                 |             |      |       | 180   | ps                    |  |  |

| t <sub>DUTY</sub>                                                            |                                |                         | 45          | 50   | 55    | %     |                       |  |  |

| DPA run length                                                               |                                |                         |             |      |       | 6,400 | UI                    |  |  |

| DPA jitter tolerance                                                         | Data channel peak-             | to-peak jitter          |             | 0.44 |       |       | UI                    |  |  |

| DPA lock time                                                                |                                |                         |             |      |       |       | Number of repetitions |  |  |

|                                                                              | SPI-4                          | 000000000<br>1111111111 | 10%         | 256  |       |       |                       |  |  |

|                                                                              | Parallel Rapid I/O             | 00001111                | 25%         | 256  |       |       | 1                     |  |  |

|                                                                              |                                | 10010000                | 50%         | 256  |       |       | 1                     |  |  |

|                                                                              | Miscellaneous                  | 10101010                | 100%        | 256  |       |       | 1                     |  |  |

|                                                                              |                                | 01010101                |             | 256  |       |       | 1                     |  |  |

<sup>(1)</sup> When J = 4 to 10, the SERDES block is used.

<sup>(2)</sup> When J = 1 or 2, the SERDES block is bypassed.

<sup>(3)</sup> The input clock frequency and the W factor must satisfy the following fast PLL VCO specification: 150 ≤nput clock frequency × W ≤1,040.

<sup>(4)</sup> The minimum specification is dependent on the clock source (fast PLL, enhanced PLL, clock pin, and so on) and the clock routing resource (global, regional, or local) utilized. The I/O differential buffer and input register do not have a minimum toggle rate.