Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | 4548                                                         |

| Number of Logic Elements/Cells | 90960                                                        |

| Total RAM Bits                 | 4520448                                                      |

| Number of I/O                  | 558                                                          |

| Number of Gates                | -                                                            |

| Voltage - Supply               | 1.15V ~ 1.25V                                                |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                              |

| Package / Case                 | 1152-BBGA                                                    |

| Supplier Device Package        | 1152-FBGA (35x35)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2sgx90ef1152c4n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

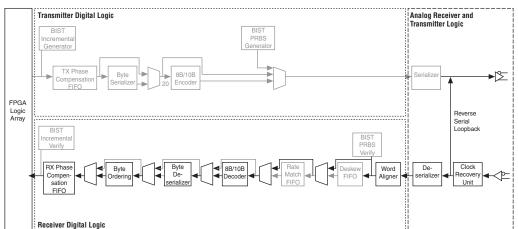

capable of built-in self test (BIST) generation and verification. The ALT2GXB megafunction in the Quartus II software provides a step-by-step menu selection to configure the transceiver.

Figure 2–1 shows the block diagram for the Stratix II GX transceiver channel. Stratix II GX transceivers provide PCS and PMA implementations for all supported protocols. The PCS portion of the transceiver consists of the word aligner, lane deskew FIFO buffer, rate matcher FIFO buffer, 8B/10B encoder and decoder, byte serializer and deserializer, byte ordering, and phase compensation FIFO buffers.

Each Stratix II GX transceiver channel is also capable of BIST generation and verification in addition to various loopback modes. The PMA portion of the transceiver consists of the serializer and deserializer, the CRU, and the high-speed differential transceiver buffers that contain pre-emphasis, programmable on-chip termination (OCT), programmable voltage output differential ( $V_{\rm OD}$ ), and equalization.

### **Transmitter Path**

This section describes the data path through the Stratix II GX transmitter. The Stratix II GX transmitter contains the following modules:

- Transmitter PLLs

- Access to one of two PLLs

- Transmitter logic array interface

- Transmitter phase compensation FIFO buffer

- Byte serializer

- 8B/10B encoder

- Serializer (parallel-to-serial converter)

- Transmitter differential output buffer

#### Transmitter PLLs

Each transceiver block has two transmitter PLLs which receive two reference clocks to generate timing and the following clocks:

- High-speed clock used by the serializer to transmit the high-speed differential transmitter data

- Low-speed clock to load the parallel transmitter data of the serializer

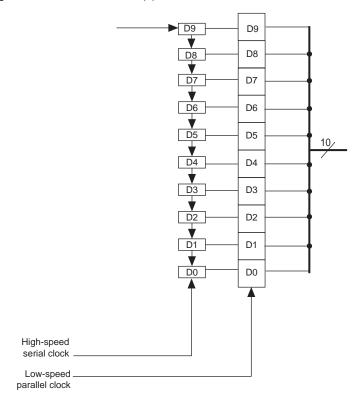

The serializer uses high-speed clocks to transmit data. The serializer is also referred to as parallel in serial out (PISO). The high-speed clock is fed to the local clock generation buffer. The local clock generation buffers divide the high-speed clock on the transmitter to a desired frequency on a per-channel basis. Figure 2–3 is a block diagram of the transmitter clocks.

Figure 2–17. Deserializer Note (1)

Note to Figure 2-17:

1) This is a 10-bit deserializer. The deserializer can also convert 8, 16, or 20 bits of data.

# Word Aligner

The deserializer block creates 8-, 10-, 16-, or 20-bit parallel data. The deserializer ignores protocol symbol boundaries when converting this data. Therefore, the boundaries of the transferred words are arbitrary. The word aligner aligns the incoming data based on specific byte or word boundaries. The word alignment module is clocked by the local receiver recovered clock during normal operation. All the data and programmed patterns are defined as big-endian (most significant word followed by least significant word). Most-significant-bit-first protocols such as SONET/SDH should reverse the bit order of word align patterns programmed.

Figure 2–26 shows the data path in reverse serial loopback mode.

Figure 2–26. Stratix II GX Block in Reverse Serial Loopback Mode

# Reverse Serial Pre-CDR Loopback

The reverse serial pre-CDR loopback mode uses the analog portion of the transceiver. An external source (pattern generator or transceiver) generates the source data. The high-speed serial source data arrives at the high-speed differential receiver input buffer, loops back before the CRU unit, and is transmitted though the high-speed differential transmitter output buffer. It is for test or verification use only to verify the signal being received after the gain and equalization improvements of the input buffer. The signal at the output is not exactly what is received since the signal goes through the output buffer and the VOD is changed to the VOD setting level. The pre-emphasis settings have no effect.

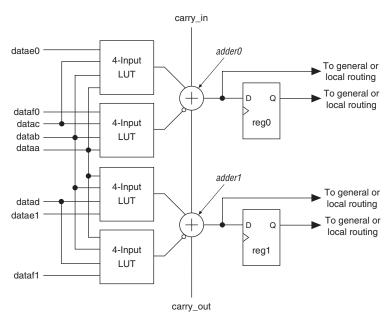

using the bottom set of output drivers. The Quartus II Compiler automatically selects the inputs to the LUT. Asynchronous load data for the register comes from the datae or dataf input of the ALM. ALMs in normal mode support register packing.

Figure 2-39. 6-Input Function in Normal Mode Notes (1), (2) To general or dataf0 local routing datae0 6-Input dataa To general or LUT datab Q local routing datac datad reg0 datae1 dataf1 To general or D Q (2) local routing These inputs are available for register packing. reg1

#### Notes to Figure 2–39:

- If datae1 and dataf1 are used as inputs to the six-input function, datae0 and dataf0 are available for register packing.

- (2) The dataf1 input is available for register packing only if the six-input function is un-registered.

#### Extended LUT Mode

The extended LUT mode is used to implement a specific set of seven-input functions. The set must be a 2-to-1 multiplexer fed by two arbitrary five-input functions sharing four inputs. Figure 2–40 shows the template of supported seven-input functions utilizing extended LUT mode. In this mode, if the seven-input function is unregistered, the unused eighth input is available for register packing. Functions that fit into the template shown in Figure 2–40 occur naturally in designs. These functions often appear in designs as "if-else" statements in Verilog HDL or VHDL code.

Figure 2-41. ALM in Arithmetic Mode

While operating in arithmetic mode, the ALM can support simultaneous use of the adder's carry output along with combinational logic outputs. In this operation, the adder output is ignored. This usage of the adder with the combinational logic output provides resource savings of up to 50% for functions that can use this ability. An example of such functionality is a conditional operation, such as the one shown in Figure 2–42. The equation for this example is:

$$R = (X < Y) ? Y : X$$

To implement this function, the adder is used to subtract 'Y' from 'X'. If 'X' is less than 'Y', the carry\_out signal will be '1'. The carry\_out signal is fed to an adder where it drives out to the LAB local interconnect. It then feeds to the LAB-wide syncload signal. When asserted, syncload selects the syncdata input. In this case, the data 'Y' drives the syncdata inputs to the registers. If 'X' is greater than or equal to 'Y', the syncload signal is de-asserted and 'X' drives the data port of the registers.

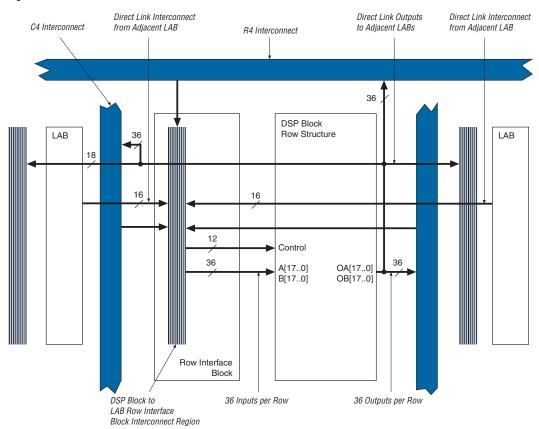

Table 2–21 shows the number of DSP blocks in each Stratix II GX device. DSP block multipliers can optionally feed an adder/subtractor or accumulator in the block, depending on the configuration, which makes routing to ALMs easier, saves ALM routing resources, and increases performance because all connections and blocks are in the DSP block.

| Table 2–21. DSP Blocks in Stratix II GX Devices Note (1) |                                     |     |     |    |  |  |  |  |  |  |  |

|----------------------------------------------------------|-------------------------------------|-----|-----|----|--|--|--|--|--|--|--|

| Device                                                   | Multipliers Multipliers Multipliers |     |     |    |  |  |  |  |  |  |  |

| EP2SGX30                                                 | 16                                  | 128 | 64  | 16 |  |  |  |  |  |  |  |

| EP2SGX60                                                 | 36                                  | 288 | 144 | 36 |  |  |  |  |  |  |  |

| EP2SGX90                                                 | 48                                  | 384 | 192 | 48 |  |  |  |  |  |  |  |

| EP2SGX130                                                | 63                                  | 504 | 252 | 63 |  |  |  |  |  |  |  |

*Note to Table 2–21:*

Additionally, the DSP block input registers can efficiently implement shift registers for FIR filter applications, and DSP blocks support Q1.15 format rounding and saturation. Figure 2–58 shows the top-level diagram of the DSP block configured for  $18 \times 18$ -bit multiplier mode.

This list only shows functions that can fit into a single DSP block. Multiple DSP blocks can support larger multiplication functions.

Figure 2-60. DSP Block Interface to Interconnect

A bus of 44 control signals feeds the entire DSP block. These signals include clocks, asynchronous clears, clock enables, signed and unsigned control signals, addition and subtraction control signals, rounding and saturation control signals, and accumulator synchronous loads. The clock signals are routed from LAB row clocks and are generated from specific LAB rows at the DSP block interface. The LAB row source for control signals, data inputs, and outputs is shown in Table 2–23.

Refer to the *DSP Blocks in Stratix II GX Devices* chapter in volume 2 of the *Stratix II GX Device Handbook* for more information on DSP blocks.

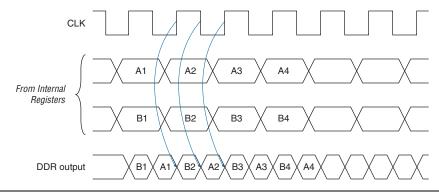

Figure 2-85. Output Timing Diagram in DDR Mode

The Stratix II GX IOE operates in bidirectional DDR mode by combining the DDR input and DDR output configurations. The negative-edge-clocked OE register holds the OE signal inactive until the falling edge of the clock to meet DDR SDRAM timing requirements.

# **External RAM Interfacing**

In addition to the six I/O registers in each IOE, Stratix II GX devices also have dedicated phase-shift circuitry for interfacing with external memory interfaces, including DDR and DDR2 SDRAM, QDR II SRAM, RLDRAM II, and SDR SDRAM. In every Stratix II GX device, the I/O banks at the top (banks 3 and 4) and bottom (banks 7 and 8) of the device support DQ and DQS signals with DQ bus modes of  $\times 4$ ,  $\times 8/\times 9$ ,  $\times 16/\times 18$ , or  $\times 32/\times 36$ . Table 2–31 shows the number of DQ and DQS buses that are supported per device.

| Table 2–31. DQS and DQ Bus Mode Support |                        |                        |                        |                                |                                |  |  |  |  |  |  |

|-----------------------------------------|------------------------|------------------------|------------------------|--------------------------------|--------------------------------|--|--|--|--|--|--|

| Device                                  | Package                | Number of<br>×4 Groups | Number of ×8/×9 Groups | Number of<br>×16/×18<br>Groups | Number of<br>×32/×36<br>Groups |  |  |  |  |  |  |

| EP2SGX30                                | 780-pin FineLine BGA   | 18                     | 8                      | 4                              | 0                              |  |  |  |  |  |  |

| EP2SGX60                                | 780-pin FineLine BGA   | 18                     | 8                      | 4                              | 0                              |  |  |  |  |  |  |

|                                         | 1,152-pin FineLine BGA | 36                     | 18                     | 8                              | 4                              |  |  |  |  |  |  |

| EP2SGX90                                | 1,152-pin FineLine BGA | 36                     | 18                     | 8                              | 4                              |  |  |  |  |  |  |

|                                         | 1,508-pin FineLine BGA | 36                     | 18                     | 8                              | 4                              |  |  |  |  |  |  |

| EP2SGX130                               | 1,508-pin FineLine BGA | 36                     | 18                     | 8                              | 4                              |  |  |  |  |  |  |

# **On-Chip Termination**

Stratix II GX devices provide differential (for the LVDS technology I/O standard) and series on-chip termination to reduce reflections and maintain signal integrity. On-chip termination simplifies board design by minimizing the number of external termination resistors required. Termination can be placed inside the package, eliminating small stubs that can still lead to reflections.

Stratix II GX devices provide four types of termination:

- Differential termination (R<sub>D</sub>)

- Series termination (R<sub>S</sub>) without calibration

- Series termination (R<sub>S</sub>) with calibration

- Parallel termination (R<sub>T</sub>) with calibration

Table 2–34 shows the Stratix II GX on-chip termination support per I/O bank.

| Table 2–34. On-Chip Terminati          | on Support by I/O Banks (P | art 1 of 2)                          |                  |

|----------------------------------------|----------------------------|--------------------------------------|------------------|

| On-Chip Termination Support            | I/O Standard Support       | Top and Bottom Banks<br>(3, 4, 7, 8) | Left Bank (1, 2) |

|                                        | 3.3-V LVTTL                | ✓                                    | <b>✓</b>         |

|                                        | 3.3-V LVCMOS               | ✓                                    | ✓                |

|                                        | 2.5-V LVTTL                | ✓                                    | ✓                |

|                                        | 2.5-V LVCMOS               | ✓                                    | <b>✓</b>         |

|                                        | 1.8-V LVTTL                | ✓                                    | ✓                |

|                                        | 1.8-V LVCMOS               | ✓                                    | ✓                |

|                                        | 1.5-V LVTTL                | ✓                                    | <b>✓</b>         |

| Series termination without calibration | 1.5-V LVCMOS               | ✓                                    | <b>✓</b>         |

|                                        | SSTL-2 class I and II      | ✓                                    | ✓                |

|                                        | SSTL-18 class I            | ✓                                    | ✓                |

|                                        | SSTL-18 class II           | ✓                                    | _                |

|                                        | 1.8-V HSTL class I         | ✓                                    | ✓                |

|                                        | 1.8-V HSTL class II        | ✓                                    | _                |

|                                        | 1.5-V HSTL class I         | ✓                                    | ✓                |

|                                        | 1.2-V HSTL                 | ✓                                    | _                |

## On-Chip Parallel Termination with Calibration

Stratix II GX devices support on-chip parallel termination with calibration for column I/O pins only. There is one calibration circuit for the top I/O banks and one circuit for the bottom I/O banks. Each on-chip parallel termination calibration circuit compares the total impedance of each I/O buffer to the external 50- $\Omega$  resistors connected to the RUP and RDN pins and dynamically enables or disables the transistors until they match. Calibration occurs at the end of device configuration. Once the calibration circuit finds the correct impedance, it powers down and stops changing the characteristics of the drivers.

On-chip parallel termination with calibration is only supported for input pins.

For more information about on-chip termination supported by Stratix II devices, refer to the *Selectable I/O Standards in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II GX Device Handbook*.

For more information about tolerance specifications for on-chip termination with calibration, refer to the *DC & Switching Characteristics* chapter in volume 1 of the *Stratix II GX Device Handbook*.

# MultiVolt I/O Interface

The Stratix II GX architecture supports the MultiVolt I/O interface feature that allows Stratix II GX devices in all packages to interface with systems of different supply voltages. The Stratix II GX VCCINT pins must always be connected to a 1.2-V power supply. With a 1.2-V V<sub>CCINT</sub> level, input pins are 1.2-, 1.5-, 1.8-, 2.5-, and 3.3-V tolerant. The VCCIO pins can be connected to either a 1.2-, 1.5-, 1.8-, 2.5-, or 3.3-V power supply, depending on the output requirements. The output levels are compatible with systems of the same voltage as the power supply (for example, when VCCIO pins are connected to a 1.5-V power supply, the output levels are compatible with 1.5-V systems). The Stratix II GX VCCPD power pins must be connected to a 3.3-V power supply. These power pins are used to supply the pre-driver power to the output buffers, which increases the performance of the output pins. The VCCPD pins also power configuration input pins and JTAG input pins.

# 3. Configuration & Testing

SIIGX51005-1.4

# IEEE Std. 1149.1 JTAG Boundary-Scan Support

All Stratix<sup>®</sup> II GX devices provide Joint Test Action Group (JTAG) boundary-scan test (BST) circuitry that complies with the IEEE Std. 1149.1. You can perform JTAG boundary-scan testing either before or after, but not during configuration. Stratix II GX devices can also use the JTAG port for configuration with the Quartus<sup>®</sup> II software or hardware using either Jam Files (.jam) or Jam Byte-Code Files (.jbc).

Stratix II GX devices support IOE I/O standard setting reconfiguration through the JTAG BST chain. The JTAG chain can update the I/O standard for all input and output pins any time before or during user mode through the CONFIG\_IO instruction. You can use this capability for JTAG testing before configuration when some of the Stratix II GX pins drive or receive from other devices on the board using voltage-referenced standards. Since the Stratix II GX device may not be configured before JTAG testing, the I/O pins may not be configured for appropriate electrical standards for chip-to-chip communication. Programming these I/O standards via JTAG allows you to fully test I/O connections to other devices.

A device operating in JTAG mode uses four required pins, TDI, TDO, TMS, and TCK, and one optional pin, TRST. The TCK pin has an internal weak pull-down resistor, while the TDI, TMS, and TRST pins have weak internal pull-up resistors. The JTAG input pins are powered by the 3.3-V VCCPD pins. The TDO output pin is powered by the VCCIO power supply in I/O bank 4.

Stratix II GX devices also use the JTAG port to monitor the logic operation of the device with the SignalTap<sup>®</sup> II embedded logic analyzer. Stratix II GX devices support the JTAG instructions shown in Table 3–1.

Stratix II GX devices must be within the first eight devices in a JTAG chain. All of these devices have the same JTAG controller. If any of the Stratix II GX devices appear after the eighth device in the JTAG chain, they will fail configuration. This does not affect SignalTap II embedded logic analysis.

| Table 4-3 | 3. Stratix II GX Device Recomme | nded Operating Conditions (Part           | 2 of 2) A | lote (1) |   |  |  |  |  |  |  |  |  |

|-----------|---------------------------------|-------------------------------------------|-----------|----------|---|--|--|--|--|--|--|--|--|

| Symbol    | Parameter                       | Parameter Conditions Minimum Maximum Unit |           |          |   |  |  |  |  |  |  |  |  |

| $T_J$     | Operating junction temperature  | For commercial use                        | 0         | 85       | С |  |  |  |  |  |  |  |  |

|           |                                 | For industrial use                        | -40       | 100      | С |  |  |  |  |  |  |  |  |

#### Notes to Table 4-3:

- (1) Supply voltage specifications apply to voltage readings taken at the device pins, not at the power supply.

- (2) During transitions, the inputs may overshoot to the voltage shown in Table 4–2 based upon the input duty cycle. The DC case is equivalent to 100% duty cycle. During transitions, the inputs may undershoot to –2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

- (3) Maximum  $V_{CC}$  rise time is 100 ms, and  $V_{CC}$  must rise monotonically from ground to  $V_{CC}$ .

- (4) V<sub>CCPD</sub> must ramp-up from 0 V to 3.3 V within 100 µs to 100 ms. If V<sub>CCPD</sub> is not ramped up within this specified time, the Stratix II GX device will not configure successfully. If the system does not allow for a V<sub>CCPD</sub> ramp-up time of 100 ms or less, hold nCONFIG low until all power supplies are reliable.

- (5) All pins, including dedicated inputs, clock, I/O, and JTAG pins, may be driven before V<sub>CCINT</sub>, V<sub>CCPD</sub>, and V<sub>CCIO</sub> are powered.

- (6) V<sub>CCIO</sub> maximum and minimum conditions for PCI and PCI-X are shown in parentheses.

## **Transceiver Block Characteristics**

Tables 4–4 through 4–6 contain transceiver block specifications.

| Table 4–4. Stratix | II GX Transceiver Block Ab       | solute Maximum Ratings    | Note (1) |         |       |

|--------------------|----------------------------------|---------------------------|----------|---------|-------|

| Symbol             | Parameter                        | Conditions                | Minimum  | Maximum | Units |

| V <sub>CCA</sub>   | Transceiver block supply voltage | Commercial and industrial | -0.5     | 4.6     | V     |

| V <sub>CCP</sub>   | Transceiver block supply voltage | Commercial and industrial | -0.5     | 1.8     | V     |

| V <sub>CCR</sub>   | Transceiver block supply Voltage | Commercial and industrial | -0.5     | 1.8     | V     |

| V <sub>CCT</sub>   | Transceiver block supply voltage | Commercial and industrial | -0.5     | 1.8     | V     |

| V <sub>CCT_B</sub> | Transceiver block supply voltage | Commercial and industrial | -0.5     | 1.8     | V     |

| V <sub>CCL</sub>   | Transceiver block supply voltage | Commercial and industrial | -0.5     | 1.8     | V     |

| V <sub>CCH_B</sub> | Transceiver block supply voltage | Commercial and industrial | -0.5     | 2.4     | V     |

#### Note to Table 4-4:

(1) The device can tolerate prolonged operation at this absolute maximum, as long as the maximum specification is not violated.

| Table 4-                           | Table 4–13. Typical Pre-Emphasis (First Post-Tap), Note (1) (Part 2 of 2) |                                     |  |  |  |  |  |  |  |  |  |  |  |

|------------------------------------|---------------------------------------------------------------------------|-------------------------------------|--|--|--|--|--|--|--|--|--|--|--|

| V <sub>CCH</sub> TX<br>= 1.5 V     | First Post Tap Pre-Emphasis Level                                         |                                     |  |  |  |  |  |  |  |  |  |  |  |

| V <sub>OD</sub><br>Setting<br>(mV) | 1                                                                         | 1 2 3 4 5 6 7 8 9 10 11 12          |  |  |  |  |  |  |  |  |  |  |  |

| 1400                               |                                                                           | 20% 26% 33% 41% 51% 58% 67% 77% 86% |  |  |  |  |  |  |  |  |  |  |  |

Note to Table 4–13:

$(1) \quad \text{Applicable to data rates from } 600 \text{ Mbps to } 6.375 \text{ Gbps. Specification is for measurement at the package ball.}$

| Table 4-                           | -14. Typi                         | cal Pre-E                  | mphasis | (First Pa | ost-Tap), | Note (1) |                |      |      |      |      |      |  |

|------------------------------------|-----------------------------------|----------------------------|---------|-----------|-----------|----------|----------------|------|------|------|------|------|--|

| V <sub>CCH</sub> TX<br>= 1.5 V     | First Post Tap Pre-Emphasis Level |                            |         |           |           |          |                |      |      |      |      |      |  |

| V <sub>OD</sub><br>Setting<br>(mV) | 1                                 | 1 2 3 4 5 6 7 8 9 10 11 12 |         |           |           |          |                |      |      |      |      |      |  |

|                                    |                                   |                            |         |           |           | TX Term  | <b>= 120</b> Ω | 2    |      |      |      |      |  |

| 240                                | 45%                               |                            |         |           |           |          |                |      |      |      |      |      |  |

| 480                                |                                   | 41%                        | 76%     | 114%      | 166%      | 257%     | 355%           |      |      |      |      |      |  |

| 720                                |                                   | 23%                        | 38%     | 55%       | 84%       | 108%     | 137%           | 179% | 226% | 280% | 405% | 477% |  |

| 960                                |                                   | 15%                        | 24%     | 36%       | 47%       | 64%      | 80%            | 97%  | 122% | 140% | 170% | 196% |  |

|                                    |                                   |                            | 18%     | 22%       | 30%       | 41%      | 51%            | 63%  | 77%  | 86%  | 98%  | 116% |  |

Note to Table 4–14:

| Table 4-                           | Table 4–15. Typical Pre-Emphasis (First Post-Tap), Note (1) (Part 1 of 2) |     |  |  |  |  |  |  |  |  |  |  |  |

|------------------------------------|---------------------------------------------------------------------------|-----|--|--|--|--|--|--|--|--|--|--|--|

| V <sub>CCH</sub> TX<br>= 1.5 V     | First Post Tap Pre-Emphasis Level                                         |     |  |  |  |  |  |  |  |  |  |  |  |

| V <sub>OD</sub><br>Setting<br>(mV) | 1 2 3 4 5 6 7 8 9 10 11 12                                                |     |  |  |  |  |  |  |  |  |  |  |  |

|                                    | TX Term = 150 $\Omega$                                                    |     |  |  |  |  |  |  |  |  |  |  |  |

| 300                                | 32%                                                                       | 85% |  |  |  |  |  |  |  |  |  |  |  |

<sup>(1)</sup> Applicable to data rates from 600 Mbps to 6.375 Gbps. Specification is for measurement at the package ball.

| Table 4-                           | Table 4–15. Typical Pre-Emphasis (First Post-Tap), Note (1) (Part 2 of 2) |                            |     |     |      |      |      |      |      |      |      |      |  |

|------------------------------------|---------------------------------------------------------------------------|----------------------------|-----|-----|------|------|------|------|------|------|------|------|--|

| V <sub>CCH</sub> TX<br>= 1.5 V     | First Post Tap Pre-Emphasis Level                                         |                            |     |     |      |      |      |      |      |      |      |      |  |

| V <sub>OD</sub><br>Setting<br>(mV) | 1                                                                         | 1 2 3 4 5 6 7 8 9 10 11 12 |     |     |      |      |      |      |      |      |      |      |  |

| 600                                |                                                                           | 33%                        | 53% | 80% | 115% | 157% | 195% | 294% | 386% |      |      |      |  |

| 900                                |                                                                           | 19%                        | 28% | 38% | 56%  | 70%  | 86%  | 113% | 133% | 168% | 196% | 242% |  |

| 1200                               |                                                                           |                            | 17% | 22% | 31%  | 40%  | 52%  | 62%  | 75%  | 86%  | 96%  | 112% |  |

Note to Table 4-15:

| Table 4-                           | -16. Typi | cal Pre-E                         | mphasis | (First Po | ost-Tap), | Note (1) |         |      |      |      |      |      |  |  |

|------------------------------------|-----------|-----------------------------------|---------|-----------|-----------|----------|---------|------|------|------|------|------|--|--|

| V <sub>CCH</sub> TX<br>= 1.2 V     |           | First Post Tap Pre-Emphasis Level |         |           |           |          |         |      |      |      |      |      |  |  |

| V <sub>OD</sub><br>Setting<br>(mV) | 1         | 1 2 3 4 5 6 7 8 9 10 11 12        |         |           |           |          |         |      |      |      |      |      |  |  |

|                                    |           |                                   |         |           |           | TX Term  | = 100 Ω | 2    |      |      |      |      |  |  |

| 320                                | 24%       | 61%                               | 114%    |           |           |          |         |      |      |      |      |      |  |  |

| 480                                |           | 31%                               | 55%     | 86%       | 121%      | 170%     | 232%    | 333% |      |      |      |      |  |  |

| 640                                |           | 20%                               | 35%     | 54%       | 72%       | 95%      | 124%    | 157% | 195% | 233% | 307% | 373% |  |  |

| 800                                |           |                                   | 23%     | 36%       | 49%       | 64%      | 81%     | 97%  | 117% | 140% | 161% | 195% |  |  |

| 960                                |           |                                   | 18%     | 25%       | 35%       | 44%      | 57%     | 69%  | 82%  | 94%  | 108% | 127% |  |  |

*Note to Table 4–16:*

<sup>(1)</sup> Applicable to data rates from 600 Mbps to 6.375 Gbps. Specification is for measurement at the package ball.

<sup>(1)</sup> Applicable to data rates from 600 Mbps to 3.125 Gbps. Specification is for measurement at the package ball.

| Table 4–19. Strati     | ix II GX Transceiver B | lock AC                | Specia | fication | Notes (                                  | (1), (2)        | , (3) <b>(P</b> | art 19                   | of 19)  |      |      |

|------------------------|------------------------|------------------------|--------|----------|------------------------------------------|-----------------|-----------------|--------------------------|---------|------|------|

| Symbol/<br>Description | Conditions             | 3 Speenercial<br>Grade | Speed  | Com      | -4 Spec<br>imercial<br>strial S<br>Grade | al and<br>Speed |                 | -5 Spe<br>nercia<br>Grad | l Speed | Unit |      |

|                        |                        | Min                    | Тур    | Max      | Min                                      | Тур             | Max             | Min                      | Тур     | Max  | Unit |

#### Notes to Table 4-19:

- (1) Dedicated REFCLK pins were used to drive the input reference clocks.

- (2) Jitter numbers specified are valid for the stated conditions only.

- (3) Refer to the protocol characterization documents for detailed information.

- (4) HiGig configuration is available in a -3 speed grade only. For more information, refer to the *Stratix II GX Transceiver Architecture Overview* chapter in volume 2 of the *Stratix II GX Device Handbook*.

- (5) Stratix II GX transceivers meet CEI jitter generation specification of 0.3 UI for a V<sub>OD</sub> range of 400 mV to 1000 mV.

- (6) The Sinusoidal Jitter Tolerance Mask is defined only for low voltage (LV) variant of CPRI.

- (7) The jitter numbers for SONET/SDH are compliant to the GR-253-CORE Issue 3 Specification.

- (8) The jitter numbers for Fibre Channel are compliant to the FC-PI-4 Specification revision 6.10.

- (9) The jitter numbers for XAUI are compliant to the IEEE802.3ae-2002 Specification.

- (10) The jitter numbers for PCI Express are compliant to the PCIe Base Specification 2.0.

- (11) The jitter numbers for Serial RapidIO are compliant to the RapidIO Specification 1.3.

- (12) The jitter numbers for GIGE are compliant to the IEEE802.3-2002 Specification.

- (13) The jitter numbers for HiGig are compliant to the IEEE802.3ae-2002 Specification.

- (14) The jitter numbers for (OIF) CEI are compliant to the OIF-CEI-02.0 Specification.

- (15) The jitter numbers for CPRI are compliant to the CPRI Specification V2.1.

- (16) The HD-SDI and 3G-SDI jitter numbers are compliant to the SMPTE292M and SMPTE424M Specifications.

- (17) The Fibre Channel transmitter jitter generation numbers are compliant to the specification at  $\beta_T$  interoperability point.

- (18) The Fibre Channel receiver jitter tolerance numbers are compliant to the specification at  $\beta_R$  interoperability point.

Table 4–20 provides information on recommended input clock jitter for each mode.

| Table 4–20. Recommended Input Clock Jitter (Part 1 of 2) |                          |                                    |                          |                                          |                                         |                                      |

|----------------------------------------------------------|--------------------------|------------------------------------|--------------------------|------------------------------------------|-----------------------------------------|--------------------------------------|

| Mode                                                     | Reference<br>Clock (MHz) | Vectron<br>LVPECL XO<br>Type/Model | Frequency<br>Range (MHz) | RMS Jitter<br>(12 kHz to 20<br>MHz) (ps) | Period Jitter<br>(Peak to<br>Peak) (ps) | Phase Noise<br>at 1 MHz<br>(dB c/Hz) |

| PCI-E                                                    | 100                      | VCC6-Q/R                           | 10 to 270                | 0.3                                      | 23                                      | -149.9957                            |

| (OIF) CEI                                                | 156.25                   | VCC6-Q/R                           | 10 to 270                | 0.3                                      | 23                                      | -146.2169                            |

| PHY                                                      | 622.08                   | VCC6-Q                             | 270 to 800               | 2                                        | 30                                      | Not available                        |

| GIGE                                                     | 62.5                     | VCC6-Q/R                           | 10 to 270                | 0.3                                      | 23                                      | -149.9957                            |

|                                                          | 125                      | VCC6-Q/R                           | 10 to 270                | 0.3                                      | 23                                      | -146.9957                            |

| XAUI                                                     | 156.25                   | VCC6-Q/R                           | 10 to 270                | 0.3                                      | 23                                      | -146.2169                            |

| Table 4–21. PCS Latency (Part 2 of 2) Note (1) |                                       |                         |                             |                    |                     |                   |                |  |

|------------------------------------------------|---------------------------------------|-------------------------|-----------------------------|--------------------|---------------------|-------------------|----------------|--|

|                                                |                                       | Transmitter PCS Latency |                             |                    |                     |                   |                |  |

| Functional Mode                                | Configuration                         | TX PIPE                 | TX<br>Phase<br>Comp<br>FIFO | Byte<br>Serializer | TX State<br>Machine | 8B/10B<br>Encoder | <b>Sum</b> (2) |  |

| Serial RapidIO                                 | 1.25 Gbps,<br>2.5 Gbps,<br>3.125 Gbps | -                       | 2-3                         | 1                  | -                   | 0.5               | 4-5            |  |

| SDI                                            | HD<br>10-bit channel<br>width         | -                       | 2-3                         | 1                  | -                   | 1                 | 4-5            |  |

|                                                | HD, 3G<br>20-bit channel<br>width     | -                       | 2-3                         | 1                  | -                   | 0.5               | 4-5            |  |

| BASIC Single                                   | 8-bit/10-bit<br>channel width         | -                       | 2-3                         | 1                  | -                   | 1                 | 4-5            |  |

| Width                                          | 16-bit/20-bit<br>channel width        | -                       | 2-3                         | 1                  | -                   | 0.5               | 4-5            |  |

|                                                | 16-bit/20-bit<br>channel width        | -                       | 2-3                         | 1                  | -                   | 1                 | 4-5            |  |

| BASIC Double<br>Width                          | 32-bit/40-bit<br>channel width        | -                       | 2-3                         | 1                  | -                   | 0.5               | 4-5            |  |

|                                                | Parallel<br>Loopback/<br>BIST         | -                       | 2-3                         | 1                  | -                   | 1                 | 4-5            |  |

#### *Notes to Table 4–21:*

- (1) The latency numbers are with respect to the PLD-transceiver interface clock cycles.

- (2) The total latency number is rounded off in the Sum column.

- (3) For CPRI 614 Mbps and 1.228 Gbps data rates, the Quartus II software customizes the PLD-transceiver interface clocking to achieve zero clock cycle uncertainty in the transmitter phase compensation FIFO latency. For more details, refer to the CPRI Mode section in the Stratix II GX Transceiver Architecture Overview chapter in volume 2 of the Stratix II GX Device Handbook.

|                    |                                                              | Receiver PCS Latency |                |                 |                   |                              |                           |               |                                   |                  |                |

|--------------------|--------------------------------------------------------------|----------------------|----------------|-----------------|-------------------|------------------------------|---------------------------|---------------|-----------------------------------|------------------|----------------|

| Functional<br>Mode | Configuration                                                | Word<br>Aligner      | Deskew<br>FIFO | Rate<br>Matcher | 8B/10B<br>Decoder | Receiver<br>State<br>Machine | Byte<br>De-<br>serializer | Byte<br>Order | Receiver<br>Phase<br>Comp<br>FIFO | Receiver<br>PIPE | <b>Sum</b> (2) |

|                    | 16/20-bit<br>channel<br>width; with<br>Rate<br>Matcher       | 4-5                  | -              | 11-13           | 1                 | -                            | 1                         | 1             | 1-2                               | -                | 19-23          |

| BASIC              | 16/20-bit<br>channel<br>width;<br>without<br>Rate<br>Matcher | 4-5                  | -              | -               | 1                 | -                            | 1                         | 1             | 1-2                               | -                | 8-10           |

| Double<br>Width    | 32/40-bit<br>channel<br>width; with<br>Rate<br>Matcher       | 2-2.5                | -              | 5.5-6.5         | 0.5               | -                            | 1                         | 1             | 1-2                               | -                | 11-14          |

|                    | 32/40-bit<br>channel<br>width;<br>without<br>Rate<br>Matcher | 2-2.5                | -              | -               | 0.5               | -                            | 1                         | 1-3           | 1-2                               | -                | 6-9            |

#### Notes to Table 4–21:

- (1) The latency numbers are with respect to the PLD-transceiver interface clock cycles.

- (2) The total latency number is rounded off in the Sum column.

- (3) The rate matcher latency shown is the steady state latency. Actual latency may vary depending on the skip ordered set gap allowed by the protocol, actual PPM difference between the reference clocks, and so forth.

- (4) For CPRI 614 Mbps and 1.228 Gbps data rates, the Quartus II software customizes the PLD-transceiver interface clocking to achieve zero clock cycle uncertainty in the receiver phase compensation FIFO latency. For more details, refer to the CPRI Mode section in the Stratix II GX Transceiver Architecture Overview chapter in volume 2 of the Stratix II GX Device Handbook

Table 4–87. Stratix II GX I/O Output Delay for Row Pins (Part 2 of 4)

| I/O Standard    | Drive<br>Strength | Parameter        | Fast Corner<br>Industrial/<br>Commercial | -3 Speed<br>Grade (3) | -3 Speed<br>Grade (4) | -4 Speed<br>Grade | -5 Speed<br>Grade | Unit |

|-----------------|-------------------|------------------|------------------------------------------|-----------------------|-----------------------|-------------------|-------------------|------|

| LVCMOS          | 4 mA              | t <sub>OP</sub>  | 1200                                     | 2113                  | 2217                  | 2357              | 2549              | ps   |

|                 |                   | t <sub>DIP</sub> | 1157                                     | 2058                  | 2160                  | 2297              | 2476              | ps   |

|                 | 8 mA (1)          | t <sub>OP</sub>  | 1094                                     | 1853                  | 1944                  | 2067              | 2243              | ps   |

|                 |                   | t <sub>DIP</sub> | 1051                                     | 1798                  | 1887                  | 2007              | 2170              | ps   |

|                 | 12 mA (1)         | t <sub>OP</sub>  | 1061                                     | 1723                  | 1808                  | 1922              | 2089              | ps   |

|                 |                   | t <sub>DIP</sub> | 1018                                     | 1668                  | 1751                  | 1862              | 2016              | ps   |

| 2.5 V           | 4 mA              | t <sub>OP</sub>  | 1183                                     | 2091                  | 2194                  | 2332              | 2523              | ps   |

|                 |                   | t <sub>DIP</sub> | 1140                                     | 2036                  | 2137                  | 2272              | 2450              | ps   |

|                 | 8 mA              | t <sub>OP</sub>  | 1080                                     | 1872                  | 1964                  | 2088              | 2265              | ps   |

|                 |                   | t <sub>DIP</sub> | 1037                                     | 1817                  | 1907                  | 2028              | 2192              | ps   |

|                 | 12 mA (1)         | t <sub>OP</sub>  | 1061                                     | 1775                  | 1862                  | 1980              | 2151              | ps   |

|                 |                   | t <sub>DIP</sub> | 1018                                     | 1720                  | 1805                  | 1920              | 2078              | ps   |

| 1.8 V           | 2 mA              | t <sub>OP</sub>  | 1253                                     | 2954                  | 3100                  | 3296              | 3542              | ps   |

|                 |                   | t <sub>DIP</sub> | 1210                                     | 2899                  | 3043                  | 3236              | 3469              | ps   |

|                 | 4 mA              | t <sub>OP</sub>  | 1242                                     | 2294                  | 2407                  | 2559              | 2763              | ps   |

|                 |                   | t <sub>DIP</sub> | 1199                                     | 2239                  | 2350                  | 2499              | 2690              | ps   |

|                 | 6 mA              | t <sub>OP</sub>  | 1131                                     | 2039                  | 2140                  | 2274              | 2462              | ps   |

|                 |                   | t <sub>DIP</sub> | 1088                                     | 1984                  | 2083                  | 2214              | 2389              | ps   |

|                 | 8 mA (1)          | t <sub>OP</sub>  | 1100                                     | 1942                  | 2038                  | 2166              | 2348              | ps   |

|                 |                   | t <sub>DIP</sub> | 1057                                     | 1887                  | 1981                  | 2106              | 2275              | ps   |

| 1.5 V           | 2 mA              | t <sub>OP</sub>  | 1213                                     | 2530                  | 2655                  | 2823              | 3041              | ps   |

|                 |                   | t <sub>DIP</sub> | 1170                                     | 2475                  | 2598                  | 2763              | 2968              | ps   |

|                 | 4 mA (1)          | t <sub>OP</sub>  | 1106                                     | 2020                  | 2120                  | 2253              | 2440              | ps   |

|                 |                   | t <sub>DIP</sub> | 1063                                     | 1965                  | 2063                  | 2193              | 2367              | ps   |

| SSTL-2 Class I  | 8 mA              | t <sub>OP</sub>  | 1050                                     | 1759                  | 1846                  | 1962              | 2104              | ps   |

|                 |                   | t <sub>DIP</sub> | 1007                                     | 1704                  | 1789                  | 1902              | 2031              | ps   |

|                 | 12 mA (1)         | t <sub>OP</sub>  | 1026                                     | 1694                  | 1777                  | 1889              | 2028              | ps   |

|                 |                   | t <sub>DIP</sub> | 983                                      | 1639                  | 1720                  | 1829              | 1955              | ps   |

| SSTL-2 Class II | 16 mA (1)         | t <sub>OP</sub>  | 992                                      | 1581                  | 1659                  | 1763              | 1897              | ps   |

|                 |                   | t <sub>DIP</sub> | 949                                      | 1526                  | 1602                  | 1703              | 1824              | ps   |

| Table 4–91. Stratix II GX Maximum Output Clock Rate for Column Pins (Part 2 of 3) |                |                |                |                |      |  |

|-----------------------------------------------------------------------------------|----------------|----------------|----------------|----------------|------|--|

| I/O Standard                                                                      | Drive Strength | -3 Speed Grade | -4 Speed Grade | -5 Speed Grade | Unit |  |

| SSTL-18 Class I                                                                   | 4 mA           | 200            | 150            | 150            | MHz  |  |

|                                                                                   | 6 mA           | 350            | 250            | 200            | MHz  |  |

|                                                                                   | 8 mA           | 450            | 300            | 300            | MHz  |  |

|                                                                                   | 10 mA          | 500            | 400            | 400            | MHz  |  |

|                                                                                   | 12 mA (1)      | 700            | 550            | 400            | MHz  |  |

| SSTL-18 Class II                                                                  | 8 mA           | 200            | 200            | 150            | MHz  |  |

|                                                                                   | 16 mA          | 400            | 350            | 350            | MHz  |  |

|                                                                                   | 18 mA          | 450            | 400            | 400            | MHz  |  |

|                                                                                   | 20 mA (1)      | 550            | 500            | 450            | MHz  |  |

| 1.8-V HSTL                                                                        | 4 mA           | 300            | 300            | 300            | MHz  |  |

| Class I                                                                           | 6 mA           | 500            | 450            | 450            | MHz  |  |

|                                                                                   | 8 mA           | 650            | 600            | 600            | MHz  |  |

|                                                                                   | 10 mA          | 700            | 650            | 600            | MHz  |  |

|                                                                                   | 12 mA (1)      | 700            | 700            | 650            | MHz  |  |

| 1.8-V HSTL                                                                        | 16 mA          | 500            | 500            | 450            | MHz  |  |

| Class II                                                                          | 18 mA          | 550            | 500            | 500            | MHz  |  |

|                                                                                   | 20 mA (1)      | 650            | 550            | 550            | MHz  |  |

| 1.5-V HSTL                                                                        | 4 mA           | 350            | 300            | 300            | MHz  |  |

| Class I                                                                           | 6 mA           | 500            | 500            | 450            | MHz  |  |

|                                                                                   | 8 mA           | 700            | 650            | 600            | MHz  |  |

|                                                                                   | 10 mA          | 700            | 700            | 650            | MHz  |  |

|                                                                                   | 12 mA (1)      | 700            | 700            | 700            | MHz  |  |

| 1.5-V HSTL                                                                        | 16 mA          | 600            | 600            | 550            | MHz  |  |

| Class II                                                                          | 18 mA          | 650            | 600            | 600            | MHz  |  |

|                                                                                   | 20 mA (1)      | 700            | 650            | 600            | MHz  |  |

| PCI                                                                               | -              | 1000           | 790            | 670            | MHz  |  |

| PCI-X                                                                             | -              | 1000           | 790            | 670            | MHz  |  |

| Differential                                                                      | 8 mA           | 400            | 300            | 300            | MHz  |  |

| SSTL-2 Class I                                                                    | 12 mA          | 400            | 400            | 350            | MHz  |  |

| Differential                                                                      | 16 mA          | 350            | 350            | 300            | MHz  |  |

| SSTL-2 Class II                                                                   | 20 mA          | 400            | 350            | 350            | MHz  |  |

|                                                                                   | 24 mA          | 400            | 400            | 350            | MHz  |  |

| Table 4–105. Maximum DCD for DDIO Output on Column I/O Pins With PLL in the Clock Path (Part 2 of 2) |                                                 |                  |    |  |  |

|------------------------------------------------------------------------------------------------------|-------------------------------------------------|------------------|----|--|--|

| Maximum DCD (ps) for<br>Column DDIO Output I/O                                                       | Stratix II GX Devices (PLL Output Feeding DDIO) |                  |    |  |  |

| Standard                                                                                             | -3 Device                                       | -4 and -5 Device |    |  |  |

| 1.2-V HSTL                                                                                           | 155                                             | 155              | ps |  |  |

| LVPECL                                                                                               | 180                                             | 180              | ps |  |  |

# High-Speed I/O Specifications

Table 4–106 provides high-speed timing specifications definitions.

| Table 4–106. High-Speed Timing Specifications and Definitions |                                                                                                                                                                                                                    |  |  |  |  |

|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| High-Speed Timing Specifications                              | Definitions                                                                                                                                                                                                        |  |  |  |  |

| t <sub>C</sub>                                                | High-speed receiver/transmitter input and output clock period.                                                                                                                                                     |  |  |  |  |

| f <sub>HSCLK</sub>                                            | High-speed receiver/transmitter input and output clock frequency.                                                                                                                                                  |  |  |  |  |

| J                                                             | Deserialization factor (width of parallel data bus).                                                                                                                                                               |  |  |  |  |

| W                                                             | PLL multiplication factor.                                                                                                                                                                                         |  |  |  |  |

| t <sub>RISE</sub>                                             | Low-to-high transmission time.                                                                                                                                                                                     |  |  |  |  |

| t <sub>FALL</sub>                                             | High-to-low transmission time.                                                                                                                                                                                     |  |  |  |  |

| Timing unit interval (TUI)                                    | The timing budget allowed for skew, propagation delays, and data sampling window. (TUI = $1/(\text{Receiver Input Clock Frequency} \times \text{Multiplication Factor}) = t_{\text{C}}/w$ ).                       |  |  |  |  |

| f <sub>IN</sub>                                               | Fast PLL input clock frequency                                                                                                                                                                                     |  |  |  |  |

| f <sub>HSDR</sub>                                             | Maximum/minimum LVDS data transfer rate (f <sub>HSDR</sub> = 1/TUI), non-DPA.                                                                                                                                      |  |  |  |  |

| fhsdrdpa                                                      | Maximum/minimum LVDS data transfer rate (f <sub>HSDRDPA</sub> = 1/TUI), DPA.                                                                                                                                       |  |  |  |  |

| Channel-to-channel skew (TCCS)                                | The timing difference between the fastest and the slowest output edges including $t_{\rm CO}$ variation and clock skew across channels driven by the same fast PLL. The clock is included in the TCCS measurement. |  |  |  |  |

| Sampling window (SW)                                          | The period of time during which the data must be valid in order to capture it correctly. The setup and hold times determine the ideal strobe position within the sampling window.                                  |  |  |  |  |

| Input jitter                                                  | Peak-to-peak input jitter on high-speed PLLs.                                                                                                                                                                      |  |  |  |  |

| Output jitter                                                 | Peak-to-peak output jitter on high-speed PLLs.                                                                                                                                                                     |  |  |  |  |

| t <sub>DUTY</sub>                                             | Duty cycle on high-speed transmitter output clock.                                                                                                                                                                 |  |  |  |  |

| t <sub>LOCK</sub>                                             | Lock time for high-speed transmitter and receiver PLLs.                                                                                                                                                            |  |  |  |  |