Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Obsolete                                                      |

| Number of LABs/CLBs            | 4548                                                          |

| Number of Logic Elements/Cells | 90960                                                         |

| Total RAM Bits                 | 4520448                                                       |

| Number of I/O                  | 558                                                           |

| Number of Gates                | -                                                             |

| Voltage - Supply               | 1.15V ~ 1.25V                                                 |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                               |

| Package / Case                 | 1152-BBGA                                                     |

| Supplier Device Package        | 1152-FBGA (35x35)                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2sgx90ef1152c5es |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Section I–2 Altera Corporation

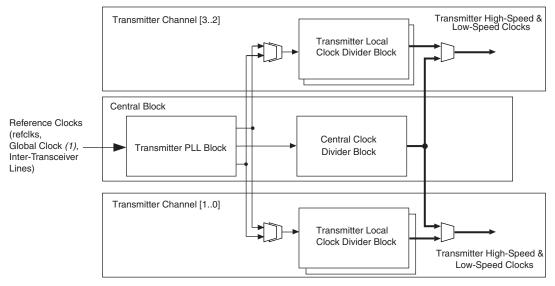

Figure 2–3. Clock Distribution for the Transmitters Note (1)

*Note to Figure 2–3:*

(1) The global clock line must be driven by an input pin.

The transmitter PLLs in each transceiver block clock the PMA and PCS circuitry in the transmit path. The Quartus II software automatically powers down the transmitter PLLs that are not used in the design. Figure 2–4 is a block diagram of the transmitter PLL.

The transmitter phase/frequency detector references the clock from one of the following sources:

- Reference clocks

- Reference clock from the adjacent transceiver block

- Inter-transceiver block clock lines

- Global clock line driven by input pin

Two reference clocks, REFCLK0 and REFCLK1, are available per transceiver block. The inter-transceiver block bus allows multiple transceivers to use the same reference clocks. Each transceiver block has one outgoing reference clock which connects to one inter-transceiver block line. The incoming reference clock can be selected from five inter-transceiver block lines IQ[4..0] or from the global clock line that is driven by an input pin.

#### Transmit State Machine

The transmit state machine operates in either PCI Express mode, XAUI mode, or GIGE mode, depending on the protocol used. The state machine is not utilized for certain protocols, such as SONET.

#### GIGE Mode

In GIGE mode, the transmit state machine converts all idle ordered sets (/K28.5/, /Dx.y/) to either /I1/ or /I2/ ordered sets. /I1/ consists of a negative-ending disparity /K28.5/ (denoted by /K28.5/-) followed by a neutral /D5.6/. /I2/ consists of a positive-ending disparity /K28.5/ (denoted by /K28.5/+) and a negative-ending disparity /D16.2/ (denoted by /D16.2/-). The transmit state machines do not convert any of the ordered sets to match /C1/ or /C2/, which are the configuration ordered sets. (/C1/ and /C2/ are defined by [/K28.5/, /D21.5/] and [/K28.5/, /D2.2/], respectively). Both the /I1/ and /I2/ ordered sets guarantee a negative-ending disparity after each ordered set.

#### XAUI Mode

The transmit state machine translates the XAUI XGMII code group to the XAUI PCS code group. Table 2–5 shows the code conversion.

| Table 2–5. | Code Conversion                           |                                        |                         |

|------------|-------------------------------------------|----------------------------------------|-------------------------|

| XGMII TXC  | XGMII TXD                                 | PCS Code-Group                         | Description             |

| 0          | 00 through FF                             | Dxx.y                                  | Normal data             |

| 1          | 07                                        | K28.0 or K28.3 or<br>K28.5             | Idle in    <b>I</b>     |

| 1          | 07                                        | K28.5                                  | Idle in   T             |

| 1          | 9C                                        | K28.4                                  | Sequence                |

| 1          | FB                                        | K27.7                                  | Start                   |

| 1          | FD                                        | K29.7                                  | Terminate               |

| 1          | FE                                        | K30.7                                  | Error                   |

| 1          | See IEEE 802.3<br>reserved code<br>groups | See IEEE 802.3<br>reserved code groups | Reserved code groups    |

| 1          | Other value                               | K30.7                                  | Invalid XGMII character |

The XAUI PCS idle code groups, /K28.0/ (/R/) and /K28.5/ (/K/), are automatically randomized based on a PRBS7 pattern with an  $x^7 + x^6 + 1$  polynomial. The /K28.3/ (/A/) code group is automatically generated between 16 and 31 idle code groups. The idle randomization on the /A/, /K/, and /R/ code groups is done automatically by the transmit state machine.

The CRU has a built-in switchover circuit to select whether the PLL VCO is aligned by the reference clock or the data. The optional port rx\_freqlocked monitors when the CRU is in locked-to-data mode.

In the automatic mode, the CRU PLL must be within the prescribed PPM frequency threshold setting of the CRU reference clock for the CRU to switch from locked-to-reference to locked-to-data mode.

The automatic switchover circuit can be overridden by using the optional ports rx\_locktorefclk and rx\_locktodata. Table 2–6 shows the possible combinations of these two signals.

| Table 2–6. Receiver Lock Combinations            |   |                 |  |  |  |  |  |  |  |  |

|--------------------------------------------------|---|-----------------|--|--|--|--|--|--|--|--|

| rx_locktodata rx_locktorefclk VCO (Lock to Mode) |   |                 |  |  |  |  |  |  |  |  |

| 0                                                | 0 | Auto            |  |  |  |  |  |  |  |  |

| 0                                                | 1 | Reference clock |  |  |  |  |  |  |  |  |

| 1                                                | х | Data            |  |  |  |  |  |  |  |  |

If the rx\_locktorefclk and rx\_locktodata ports are not used, the default is auto mode.

### Deserializer (Serial-to-Parallel Converter)

The deserializer converts a serial bitstream into 8, 10, 16, or 20 bits of parallel data. The deserializer receives the LSB first. Figure 2–17 shows the deserializer.

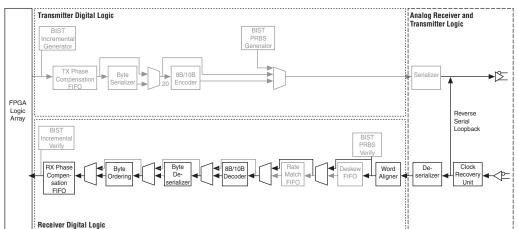

Figure 2–26 shows the data path in reverse serial loopback mode.

Figure 2–26. Stratix II GX Block in Reverse Serial Loopback Mode

#### Reverse Serial Pre-CDR Loopback

The reverse serial pre-CDR loopback mode uses the analog portion of the transceiver. An external source (pattern generator or transceiver) generates the source data. The high-speed serial source data arrives at the high-speed differential receiver input buffer, loops back before the CRU unit, and is transmitted though the high-speed differential transmitter output buffer. It is for test or verification use only to verify the signal being received after the gain and equalization improvements of the input buffer. The signal at the output is not exactly what is received since the signal goes through the output buffer and the VOD is changed to the VOD setting level. The pre-emphasis settings have no effect.

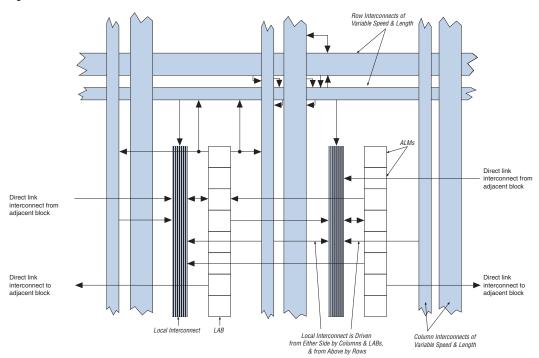

Figure 2-32. Stratix II GX LAB Structure

#### LAB Interconnects

The LAB local interconnect can drive all eight ALMs in the same LAB. It is driven by column and row interconnects and ALM outputs in the same LAB. Neighboring LABs, M512 RAM blocks, M4K RAM blocks, M-RAM blocks, or digital signal processing (DSP) blocks from the left and right can also drive a LAB's local interconnect through the direct link connection. The direct link connection feature minimizes the use of row and column interconnects, providing higher performance and flexibility. Each ALM can drive 24 ALMs through fast local and direct link interconnects.

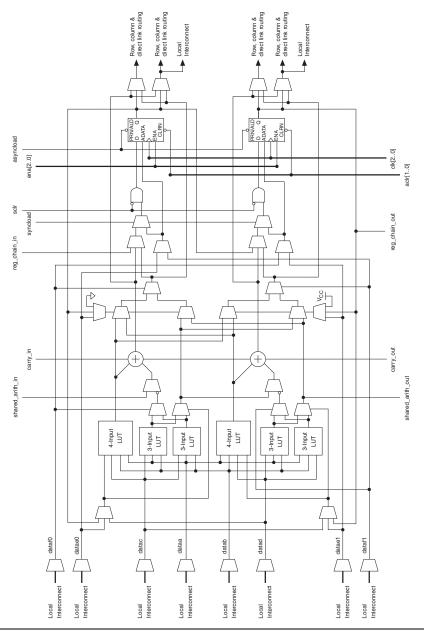

Figure 2-36. Stratix II GX ALM Details

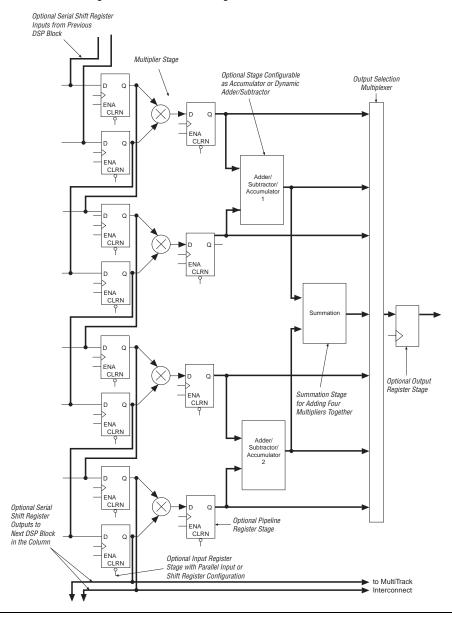

Figure 2-58. DSP Block Diagram for 18 x 18-Bit Configuration

The connections to the global and regional clocks from the top clock pins and enhanced PLL outputs are shown in Table 2–28. The connections to the clocks from the bottom clock pins are shown in Table 2–29.

| Table 2–28. Global and Reg<br>(Part 1 of 2)                   | ional (  | Clock (  | Connec   | ctions   | from T   | Top Clo  | ock Pi   | ns and   | l Enha   | nced F   | PLL Ou   | ıtputs   |          |

|---------------------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Top Side Global and<br>Regional Clock Network<br>Connectivity | DLLCLK   | CLK12    | CLK13    | CLK14    | CLK15    | RCLK24   | RCLK25   | RCLK26   | RCLK27   | RCLK28   | RCLK29   | RCLK30   | RCLK31   |

| Clock pins                                                    | •        |          |          |          |          |          |          |          | •        |          |          | •        |          |

| CLK12p                                                        | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| CLK13p                                                        | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| CLK14p                                                        | <b>✓</b> |          |          | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| CLK15p                                                        | <b>✓</b> |          |          | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| CLK12n                                                        |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| CLK13n                                                        |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| CLK14n                                                        |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| CLK15n                                                        |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| Drivers from internal logic                                   |          |          |          |          |          |          |          |          | •        |          |          |          |          |

| GCLKDRV0                                                      |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |          |          |

| GCLKDRV1                                                      |          |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |          |

| GCLKDRV2                                                      |          |          |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |

| GCLKDRV3                                                      |          |          |          |          | <b>✓</b> |          |          |          |          |          |          |          |          |

| RCLKDRV0                                                      |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| RCLKDRV1                                                      |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| RCLKDRV2                                                      |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| RCLKDRV3                                                      |          |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| RCLKDRV4                                                      |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| RCLKDRV5                                                      |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| RCLKDRV6                                                      |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| RCLKDRV7                                                      |          |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| Enhanced PLL5 outputs                                         | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        |          | 1        | 1        | 1        |          |

| c0                                                            | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| c1                                                            | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| Top Side Global and                    | DLLCLK   | CLK12    | CLK13    | 14       | (15      | RCLK24   | RCLK25   | RCLK26   | RCLK27   | RCLK28   | RCLK29   | RCLK30   | K31      |

|----------------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Regional Clock Network<br>Connectivity | DLL      | CE       | Ę.       | CLK14    | CLK15    | RCL      | RCLK31   |

| c2                                     | <b>✓</b> |          |          | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| с3                                     | ~        |          |          | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| c4                                     | <b>✓</b> |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          |

| c5                                     | <b>✓</b> |          |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |

| Enhanced PLL 11 outputs                | •        |          |          |          |          |          |          |          |          |          |          |          |          |

| c0                                     |          | <b>✓</b> | <b>~</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| c1                                     |          | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| c2                                     |          |          |          | <b>✓</b> | <b>✓</b> |          |          | <b>\</b> |          |          |          | <b>\</b> |          |

| c3                                     |          |          |          | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| c4                                     |          |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          |

| c5                                     |          |          |          |          |          |          | _        |          | /        |          | /        |          | _        |

| Table 2–29. Global and Regional Clock Connections from Bottom Clock Pins and Enhanced PLL<br>Outputs (Part 1 of 2) |          |          |          |          |          |          |          |          |          |          |          |          |          |

|--------------------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Bottom Side Global and<br>Regional Clock Network<br>Connectivity                                                   | DLLCLK   | CLK4     | CLK5     | CLK6     | CLK7     | RCLK8    | RCLK9    | RCLK10   | RCLK11   | RCLK12   | RCLK13   | RCLK14   | RCLK15   |

| Clock pins                                                                                                         |          |          |          |          |          |          |          |          |          |          |          |          |          |

| CLK4p                                                                                                              | <b>~</b> | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>~</b> |          |          |          |

| CLK5p                                                                                                              | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| CLK6p                                                                                                              | <b>✓</b> |          |          | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| CLK7p                                                                                                              | <b>✓</b> |          |          | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>\</b> |

| CLK4n                                                                                                              |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| CLK5n                                                                                                              |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| CLK6n                                                                                                              |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| CLK7n                                                                                                              |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| Drivers from internal logic                                                                                        |          |          |          |          | •        | •        |          |          |          |          | •        |          |          |

| GCLKDRV0                                                                                                           |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |          |          |

| GCLKDRV1                                                                                                           |          |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |          |

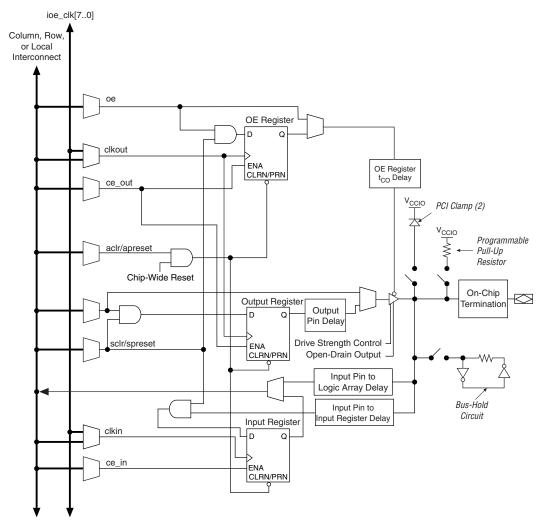

Figure 2–81. Stratix II GX IOE in Bidirectional I/O Configuration Note (1)

Notes to Figure 2-81:

- (1) All input signals to the IOE can be inverted at the IOE.

- (2) The optional PCI clamp is only available on column I/O pins.

The Stratix II GX device IOE includes programmable delays that can be activated to ensure input IOE register-to-logic array register transfers, input pin-to-logic array register transfers, or output IOE register-to-pin transfers.

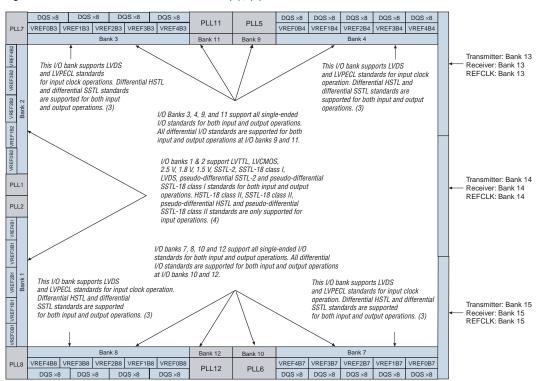

**Figure 2–87. Stratix II GX I/O Banks** Notes (1), (2)

#### Notes to Figure 2-87:

- Figure 2–87 is a top view of the silicon die that corresponds to a reverse view for flip-chip packages. It is a graphical representation only.

- (2) Depending on the size of the device, different device members have different numbers of  $V_{REF}$  groups. Refer to the pin list and the Quartus II software for exact locations.

- (3) Banks 9 through 12 are enhanced PLL external clock output banks.

- (4) Horizontal I/O banks feature SERDES and DPA circuitry for high-speed differential I/O standards. See the High-Speed Differential I/O Interfaces with DPA in Stratix II & Stratix II GX Devices chapter in volume 2 of the Stratix II Device Handbook 2 for more information on differential I/O standards.

Each I/O bank has its own VCCIO pins. A single device can support 1.5-, 1.8-, 2.5-, and 3.3-V interfaces; each bank can support a different  $V_{\rm CCIO}$  level independently. Each bank also has dedicated VREF pins to support the voltage-referenced standards (such as SSTL-2).

Each I/O bank can support multiple standards with the same  $V_{\text{CCIO}}$  for input and output pins. Each bank can support one  $V_{\text{REF}}$  voltage level. For example, when  $V_{\text{CCIO}}$  is 3.3 V, a bank can support LVTTL, LVCMOS, and 3.3-V PCI for inputs and outputs.

The temperature sensing diode is a very sensitive circuit which can be influenced by noise coupled from other traces on the board, and possibly within the device package itself, depending on device usage. The interfacing device registers temperature based on millivolts of difference as seen at the TSD. Switching I/O near the TSD pins can affect the temperature reading. Altera recommends you take temperature readings during periods of no activity in the device (for example, standby mode where no clocks are toggling in the device), such as when the nearby I/Os are at a DC state, and disable clock networks in the device.

# Automated Single Event Upset (SEU) Detection

Stratix II GX devices offer on-chip circuitry for automated checking of single event upset (SEU) detection. Some applications that require the device to operate error free at high elevations or in close proximity to Earth's North or South Pole will require periodic checks to ensure continued data integrity. The error detection cyclic redundancy check (CRC) feature controlled by the **Device & Pin Options** dialog box in the Quartus II software uses a 32-bit CRC circuit to ensure data reliability and is one of the best options for mitigating SEU.

You can implement the error detection CRC feature with existing circuitry in Stratix II GX devices, eliminating the need for external logic. Stratix II GX devices compute CRC during configuration and checks the computed-CRC against an automatically computed CRC during normal operation. The CRC\_ERROR pin reports a soft error when configuration SRAM data is corrupted, triggering device reconfiguration.

# **Custom-Built Circuitry**

Dedicated circuitry is built into Stratix II GX devices to automatically perform error detection. This circuitry constantly checks for errors in the configuration SRAM cells while the device is in user mode. You can monitor one external pin for the error and use it to trigger a reconfiguration cycle. You can select the desired time between checks by adjusting a built-in clock divider.

#### Software Interface

Beginning with version 4.1 of the Quartus II software, you can turn on the automated error detection CRC feature in the **Device & Pin Options** dialog box. This dialog box allows you to enable the feature and set the internal frequency of the CRC between 400 kHz to 50 MHz. This controls the rate that the CRC circuitry verifies the internal configuration SRAM bits in the Stratix II GX FPGA.

For more information on CRC, refer to AN 357: Error Detection Using CRC in Altera FPGA Devices.

| Table 4-2. | Table 4–2. Maximum Duty Cycles in Voltage Transitions |                         |                             |  |  |  |  |  |  |  |  |

|------------|-------------------------------------------------------|-------------------------|-----------------------------|--|--|--|--|--|--|--|--|

| Symbol     | Parameter                                             | Condition               | Maximum Duty Cycles (%) (1) |  |  |  |  |  |  |  |  |

| $V_{I}$    | Maximum duty cycles                                   | $V_{I} = 4.0 \text{ V}$ | 100                         |  |  |  |  |  |  |  |  |

|            | in voltage transitions                                | V <sub>I</sub> = 4.1 V  | 90                          |  |  |  |  |  |  |  |  |

|            |                                                       | V <sub>I</sub> = 4.2 V  | 50                          |  |  |  |  |  |  |  |  |

|            |                                                       | V <sub>I</sub> = 4.3 V  | 30                          |  |  |  |  |  |  |  |  |

|            |                                                       | V <sub>I</sub> = 4.4 V  | 17                          |  |  |  |  |  |  |  |  |

|            |                                                       | V <sub>I</sub> = 4.5 V  | 10                          |  |  |  |  |  |  |  |  |

Note to Table 4-2:

# **Recommended Operating Conditions**

Table 4–3 contains the Stratix II GX device family recommended operating conditions.

| Table 4-           | 3. Stratix II GX Device Recomme                                               | nded Operating Conditions (Part   | 1 of 2) \(\Lambda\) | lote (1)          |      |

|--------------------|-------------------------------------------------------------------------------|-----------------------------------|---------------------|-------------------|------|

| Symbol             | Parameter                                                                     | Conditions                        | Minimum             | Maximum           | Unit |

| V <sub>CCINT</sub> | Supply voltage for internal logic and input buffers                           | 100 μs ≤rise time ≤100 ms (3)     | 1.15                | 1.25              | V    |

| V <sub>CCIO</sub>  | Supply voltage for output buffers, 3.3-V operation                            | 100 μs ⊴ise time ≤100 ms (3), (6) | 3.135<br>(3.00)     | 3.465<br>(3.60)   | ٧    |

|                    | Supply voltage for output buffers, 2.5-V operation                            | 100 μs ≤rise time ≤100 ms (3)     | 2.375               | 2.625             | ٧    |

|                    | Supply voltage for output buffers, 1.8-V operation                            | 100 μs ≤rise time ≤100 ms (3)     | 1.71                | 1.89              | ٧    |

|                    | Supply voltage for output buffers, 1.5-V operation                            | 100 μs ≤rise time ≤100 ms (3)     | 1.425               | 1.575             | ٧    |

|                    | Supply voltage for output buffers, 1.2-V operation                            | 100 μs ≤rise time ≤100 ms (3)     | 1.15                | 1.25              | ٧    |

| V <sub>CCPD</sub>  | Supply voltage for pre-drivers as well as configuration and JTAG I/O buffers. | 100 μs ⊴rise time ≤100 ms (4)     | 3.135               | 3.465             | V    |

| Vı                 | Input voltage (see Table 4–2)                                                 | (2), (5)                          | -0.5                | 4.0               | V    |

| Vo                 | Output voltage                                                                |                                   | 0                   | V <sub>CCIO</sub> | V    |

<sup>(1)</sup> During transition, the inputs may overshoot to the voltages shown based on the input duty cycle. The duty cycle case is equivalent to 100% duty cycle.

| 10010 7 13. Ollali                                                            | ix II GX Transceiver B                                                                                                                                                                      | look AU                               | ороон | ivativii |                                                         |        |     | 11110                                 | . 13) |     |      |

|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------|----------|---------------------------------------------------------|--------|-----|---------------------------------------|-------|-----|------|

| Symbol/<br>Description Conditions                                             |                                                                                                                                                                                             | -3 Speed<br>Commercial Speed<br>Grade |       |          | -4 Speed<br>Commercial and<br>Industrial Speed<br>Grade |        |     | -5 Speed<br>Commercial Speed<br>Grade |       |     | Unit |

|                                                                               |                                                                                                                                                                                             | Min                                   | Тур   | Max      | Min                                                     | Тур    | Max | Min                                   | Тур   | Max |      |

| <b>CPRI Receiver Jitt</b>                                                     | ter Tolerance (15)                                                                                                                                                                          |                                       |       |          |                                                         |        |     |                                       |       |     |      |

| Deterministic Jitter<br>Tolerance<br>(peak-to-peak)                           | Data Rate = 614.4 Mbps, 1.2288 Gbps, 2.4576 Gbps REFCLK = 61.44 MHz for 614.4 Mbps REFCLK = 122.88 MHz for 1.2288 Gbps and 2.4576 Gbps Pattern = CJPAT Equalizer Setting = 6 DC Gain = 0 dB | > 0.4                                 |       | > 0.4    |                                                         |        | N/A |                                       |       | UI  |      |

| Combined<br>Deterministic and<br>Random Jitter<br>Tolerance<br>(peak-to-peak) | Data Rate = 614.4 Mbps, 1.2288 Gbps, 2.4576 Gbps REFCLK = 61.44 MHz for 614.4 Mbps REFCLK = 122.88 MHz for 1.2288 Gbps and 2.4576 Gbps Pattern = CJPAT Equalizer Setting = 6 DC Gain = 0 dB | > 0.66                                |       | > 0.66   |                                                         | > 0.66 |     |                                       |       | UI  |      |

| Symbol/<br>Description                                                                                                          | Conditions                                                                                                                     | Comm | -3 Speed<br>Commercial Speed<br>Grade |     |     | -4 Speed<br>Commercial and<br>Industrial Speed<br>Grade |     |     | Commercial and Industrial Speed Commercial S |     | Speed | Unit |

|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------|---------------------------------------|-----|-----|---------------------------------------------------------|-----|-----|----------------------------------------------|-----|-------|------|

|                                                                                                                                 |                                                                                                                                | Min  | Тур                                   | Max | Min | Тур                                                     | Max | Min | Тур                                          | Max |       |      |

| Data Rate = 1.485 Gbps (HD) REFCLK = 74.25 MHz Pattern = ColorBar Vod = 800 mV No Pre-emphasis Low-Frequency Roll-Off = 100 KHz |                                                                                                                                |      | 0.2                                   |     |     | 0.2                                                     |     |     | 0.2                                          |     | UI    |      |

| Alignment Jitter<br>(peak-to-peak)                                                                                              | Data Rate = 2.97 Gbps (3G) REFCLK = 148.5 MHz Pattern = ColorBar Vod = 800 mV No Pre-emphasis Low-Frequency Roll-Off = 100 KHz |      | 0.3                                   |     |     | 0.3                                                     |     |     | 0.3                                          |     | UI    |      |

| (F                                                                                                                              |                                                                                                                                |      |                                       |     |     |                                                         |     |     |                                              |     |       |      |

|                                                                                                                                 |                                                                                                                                |      |                                       |     |     |                                                         |     |     |                                              |     |       |      |

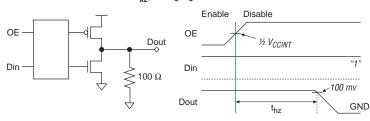

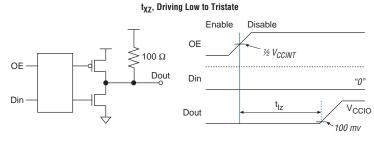

Figures 4–9 and 4–10 show the measurement setup for output disable and output enable timing.

Figure 4–9. Measurement Setup for  $t_{xz}$  Note (1)  $t_{XZ}$ , Driving High to Tristate

*Note to Figure 4–9:*

(1)  $V_{CCINT}$  is 1.12 V for this measurement.

| Table 4-65. E        | Table 4–65. EP2SGX30 Column Pins Regional Clock Timing Parameters |            |          |          |          |        |  |  |  |  |  |  |  |

|----------------------|-------------------------------------------------------------------|------------|----------|----------|----------|--------|--|--|--|--|--|--|--|

| Parameter            | Fast                                                              | Corner     | -3 Speed | -4 Speed | -5 Speed | Units  |  |  |  |  |  |  |  |

| raiailletei          | Industrial                                                        | Commercial | Grade    | Grade    | Grade    | UIIIIS |  |  |  |  |  |  |  |

| t <sub>CIN</sub>     | 1.493                                                             | 1.507      | 2.522    | 2.806    | 3.364    | ns     |  |  |  |  |  |  |  |

| t <sub>COUT</sub>    | 1.353                                                             | 1.372      | 2.525    | 2.809    | 3.364    | ns     |  |  |  |  |  |  |  |

| t <sub>PLLCIN</sub>  | 0.087                                                             | 0.104      | 0.237    | 0.253    | 0.292    | ns     |  |  |  |  |  |  |  |

| t <sub>PLLCOUT</sub> | -0.078                                                            | -0.061     | 0.237    | 0.253    | 0.29     | ns     |  |  |  |  |  |  |  |

| Table 4–66. E        | Table 4–66. EP2SGX30 Row Pins Regional Clock Timing Parameters |            |          |          |          |        |  |  |  |  |  |  |  |

|----------------------|----------------------------------------------------------------|------------|----------|----------|----------|--------|--|--|--|--|--|--|--|

| Parameter            | Fast                                                           | Corner     | -3 Speed | -4 Speed | -5 Speed | Units  |  |  |  |  |  |  |  |

| Parameter            | Industrial                                                     | Commercial | Grade    | Grade    | Grade    | UIIIIS |  |  |  |  |  |  |  |

| t <sub>CIN</sub>     | 1.246                                                          | 1.262      | 2.437    | 2.712    | 3.246    | ns     |  |  |  |  |  |  |  |

| t <sub>COUT</sub>    | 1.251                                                          | 1.267      | 2.437    | 2.712    | 3.246    | ns     |  |  |  |  |  |  |  |

| t <sub>PLLCIN</sub>  | -0.18                                                          | -0.167     | 0.215    | 0.229    | 0.263    | ns     |  |  |  |  |  |  |  |

| t <sub>PLLCOUT</sub> | -0.175                                                         | -0.162     | 0.215    | 0.229    | 0.263    | ns     |  |  |  |  |  |  |  |

# EP2SGX60 Clock Timing Parameters

Tables 4–67 through 4–70 show the maximum clock timing parameters for EP2SGX60 devices.

| Table 4–67. EP2SGX60 Column Pins Global Clock Timing Parameters |             |            |          |          |          |       |  |  |

|-----------------------------------------------------------------|-------------|------------|----------|----------|----------|-------|--|--|

| Parameter                                                       | Fast Corner |            | -3 Speed | -4 Speed | -5 Speed | Unito |  |  |

|                                                                 | Industrial  | Commercial | Grade    | Grade    | Grade    | Units |  |  |

| t <sub>CIN</sub>                                                | 1.722       | 1.736      | 2.940    | 3.275    | 3.919    | ns    |  |  |

| t <sub>COUT</sub>                                               | 1.557       | 1.571      | 2.698    | 3.005    | 3.595    | ns    |  |  |

| t <sub>PLLCIN</sub>                                             | 0.037       | 0.051      | 0.474    | 0.521    | 0.613    | ns    |  |  |

| t <sub>PLLCOUT</sub>                                            | -0.128      | -0.114     | 0.232    | 0.251    | 0.289    | ns    |  |  |

Table 4–85. Stratix II GX I/O Input Delay for Row Pins (Part 2 of 3)

| I/O Standard        | Parameter          | Fast Corner<br>Industrial/<br>Commercial | -3 Speed<br>Grade (2) | -3 Speed<br>Grade (3) | -4 Speed<br>Grade | -5 Speed<br>Grade | Unit |

|---------------------|--------------------|------------------------------------------|-----------------------|-----------------------|-------------------|-------------------|------|

| LVCMOS              | t <sub>Pl</sub>    | 749                                      | 1287                  | 1350                  | 1435              | 1723              | ps   |

|                     | t <sub>PCOUT</sub> | 410                                      | 760                   | 798                   | 848               | 1018              | ps   |

| SSTL-2 Class I      | t <sub>Pl</sub>    | 573                                      | 879                   | 921                   | 980               | 1176              | ps   |

|                     | t <sub>PCOUT</sub> | 234                                      | 352                   | 369                   | 393               | 471               | ps   |

| SSTL-2 Class II     | t <sub>PI</sub>    | 573                                      | 879                   | 921                   | 980               | 1176              | ps   |

|                     | t <sub>PCOUT</sub> | 234                                      | 352                   | 369                   | 393               | 471               | ps   |

| SSTL-18 Class I     | t <sub>PI</sub>    | 605                                      | 960                   | 1006                  | 1070              | 1285              | ps   |

|                     | t <sub>PCOUT</sub> | 266                                      | 433                   | 454                   | 483               | 580               | ps   |

| SSTL-18 Class II    | t <sub>Pl</sub>    | 605                                      | 960                   | 1006                  | 1070              | 1285              | ps   |

|                     | t <sub>PCOUT</sub> | 266                                      | 433                   | 454                   | 483               | 580               | ps   |

| 1.5-V HSTL Class I  | t <sub>PI</sub>    | 631                                      | 1056                  | 1107                  | 1177              | 1413              | ps   |

|                     | t <sub>PCOUT</sub> | 292                                      | 529                   | 555                   | 590               | 708               | ps   |

| 1.5-V HSTL Class II | t <sub>Pl</sub>    | 631                                      | 1056                  | 1107                  | 1177              | 1413              | ps   |

|                     | t <sub>PCOUT</sub> | 292                                      | 529                   | 555                   | 590               | 708               | ps   |

| 1.8-V HSTL Class I  | t <sub>Pl</sub>    | 605                                      | 960                   | 1006                  | 1070              | 1285              | ps   |

|                     | t <sub>PCOUT</sub> | 266                                      | 433                   | 454                   | 483               | 580               | ps   |

| 1.8-V HSTL Class II | t <sub>Pl</sub>    | 605                                      | 960                   | 1006                  | 1070              | 1285              | ps   |

|                     | t <sub>PCOUT</sub> | 266                                      | 433                   | 454                   | 483               | 580               | ps   |

| PCI                 | t <sub>Pl</sub>    | 830                                      | 1498                  | 1571                  | 1671              | 2006              | ps   |

|                     | t <sub>PCOUT</sub> | 491                                      | 971                   | 1019                  | 1084              | 1301              | ps   |

| PCI-X               | t <sub>Pl</sub>    | 830                                      | 1498                  | 1571                  | 1671              | 2006              | ps   |

|                     | t <sub>PCOUT</sub> | 491                                      | 971                   | 1019                  | 1084              | 1301              | ps   |

| LVDS (1)            | t <sub>PI</sub>    | 540                                      | 948                   | 994                   | 1057              | 1269              | ps   |

|                     | t <sub>PCOUT</sub> | 201                                      | 421                   | 442                   | 470               | 564               | ps   |

| HyperTransport      | t <sub>PI</sub>    | 540                                      | 948                   | 994                   | 1057              | 1269              | ps   |

|                     | t <sub>PCOUT</sub> | 201                                      | 421                   | 442                   | 470               | 564               | ps   |

| Differential SSTL-2 | t <sub>Pl</sub>    | 573                                      | 879                   | 921                   | 980               | 1176              | ps   |

| Class I             | t <sub>PCOUT</sub> | 234                                      | 352                   | 369                   | 393               | 471               | ps   |

| Differential SSTL-2 | t <sub>Pl</sub>    | 573                                      | 879                   | 921                   | 980               | 1176              | ps   |

| Class II            | t <sub>PCOUT</sub> | 234                                      | 352                   | 369                   | 393               | 471               | ps   |

| Table 4–85. Stratix II GX I/O Input Delay for Row Pins (Part 3 of 3) |                    |                                          |                       |                       |                   |                   |      |  |  |

|----------------------------------------------------------------------|--------------------|------------------------------------------|-----------------------|-----------------------|-------------------|-------------------|------|--|--|

| I/O Standard                                                         | Parameter          | Fast Corner<br>Industrial/<br>Commercial | -3 Speed<br>Grade (2) | -3 Speed<br>Grade (3) | -4 Speed<br>Grade | -5 Speed<br>Grade | Unit |  |  |

| Differential SSTL-18                                                 | t <sub>Pl</sub>    | 605                                      | 960                   | 1006                  | 1070              | 1285              | ps   |  |  |

| Class I                                                              | t <sub>PCOUT</sub> | 266                                      | 433                   | 454                   | 483               | 580               | ps   |  |  |

| Differential SSTL-18                                                 | t <sub>Pl</sub>    | 605                                      | 960                   | 1006                  | 1070              | 1285              | ps   |  |  |

| Class II                                                             | t <sub>PCOUT</sub> | 266                                      | 433                   | 454                   | 483               | 580               | ps   |  |  |

| 1.8-V differential HSTL                                              | t <sub>Pl</sub>    | 605                                      | 960                   | 1006                  | 1070              | 1285              | ps   |  |  |

| Class I                                                              | t <sub>PCOUT</sub> | 266                                      | 433                   | 454                   | 483               | 580               | ps   |  |  |

| 1.8-V differential HSTL                                              | t <sub>Pl</sub>    | 605                                      | 960                   | 1006                  | 1070              | 1285              | ps   |  |  |

| Class II                                                             | t <sub>PCOUT</sub> | 266                                      | 433                   | 454                   | 483               | 580               | ps   |  |  |

| 1.5-V differential HSTL                                              | t <sub>Pl</sub>    | 631                                      | 1056                  | 1107                  | 1177              | 1413              | ps   |  |  |

| Class I                                                              | t <sub>PCOUT</sub> | 292                                      | 529                   | 555                   | 590               | 708               | ps   |  |  |

| 1.5-V differential HSTL                                              | t <sub>Pl</sub>    | 631                                      | 1056                  | 1107                  | 1177              | 1413              | ps   |  |  |

| Class II                                                             | t <sub>PCOUT</sub> | 292                                      | 529                   | 555                   | 590               | 708               | ps   |  |  |

<sup>(1)</sup> The parameters are only available on the left side of the device.

(2) This column refers to -3 speed grades for EP2SGX30, EP2SGX60, and EP2SGX90 devices.

(3) This column refers to -3 speed grades for EP2SGX130 devices.