Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | 4548                                                         |

| Number of Logic Elements/Cells | 90960                                                        |

| Total RAM Bits                 | 4520448                                                      |

| Number of I/O                  | 558                                                          |

| Number of Gates                | -                                                            |

| Voltage - Supply               | 1.15V ~ 1.25V                                                |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                              |

| Package / Case                 | 1152-BBGA                                                    |

| Supplier Device Package        | 1152-FBGA (35x35)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2sgx90ef1152c5n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Transmitter Phase Compensation FIFO Buffer

The transmitter phase compensation FIFO buffer resides in the transceiver block at the PCS/FPGA boundary and cannot be bypassed. This FIFO buffer compensates for phase differences between the transmitter PLL clock and the clock from the PLD. After the transmitter PLL has locked to the frequency and phase of the reference clock, the transmitter FIFO buffer must be reset to initialize the read and write pointers. After FIFO pointer initialization, the PLL must remain phase locked to the reference clock.

## Byte Serializer

The FPGA and transceiver block must maintain the same throughput. If the FPGA interface cannot meet the timing margin to support the throughput of the transceiver, the byte serializer is used on the transmitter and the byte deserializer is used on the receiver.

The byte serializer takes words from the FPGA interface and converts them into smaller words for use in the transceiver. The transmit data path after the byte serializer is 8, 10, 16, or 20 bits. Refer to Table 2–3 for the transmitter data with the byte serializer enabled. The byte serializer can be bypassed when the data width is 8, 10, 16, or 20 bits at the FPGA interface.

| Table 2–3. Transmitter Data with the | Table 2–3. Transmitter Data with the Byte Serializer Enabled |  |  |  |  |  |  |  |

|--------------------------------------|--------------------------------------------------------------|--|--|--|--|--|--|--|

| Input Data Width                     | Output Data Width                                            |  |  |  |  |  |  |  |

| 16 bits                              | 8 bits                                                       |  |  |  |  |  |  |  |

| 20 bits                              | 10 bits                                                      |  |  |  |  |  |  |  |

| 32 bits                              | 16 bits                                                      |  |  |  |  |  |  |  |

| 40 bits                              | 20 bits                                                      |  |  |  |  |  |  |  |

If the byte serializer is disabled, the FPGA transmit data is passed without data width conversion.

Table 2–4 shows the data path configurations for the Stratix II GX device in single-width and double-width modes.

Refer to the section "8B/10B Encoder" on page 2–8 for a description of the single- and double-width modes.

| Table 2–4. Data Path Configuration   | s Note (1)                                        |                                                |                                                   |                                                |  |  |

|--------------------------------------|---------------------------------------------------|------------------------------------------------|---------------------------------------------------|------------------------------------------------|--|--|

|                                      | Single-Wi                                         | idth Mode                                      | Double-Width Mode                                 |                                                |  |  |

| Parameter                            | Without Byte<br>Serialization/<br>Deserialization | With Byte<br>Serialization/<br>Deserialization | Without Byte<br>Serialization/<br>Deserialization | With Byte<br>Serialization/<br>Deserialization |  |  |

| Fabric to PCS data path width (bits) | 8 or 10                                           | 16 or 20                                       | 16 or 20                                          | 32 or 40                                       |  |  |

| Data rate range (Gbps)               | 0.6 to 2.5                                        | 0.6 to 3.125                                   | 1 to 5.0                                          | 1 to 6.375                                     |  |  |

| PCS to PMA data path width (bits)    | 8 or 10                                           | 8 or 10                                        | 16 or 20                                          | 16 or 20                                       |  |  |

| Byte ordering (1)                    |                                                   | ✓                                              |                                                   | <b>✓</b>                                       |  |  |

| Data symbol A (MSB)                  |                                                   |                                                |                                                   | ✓                                              |  |  |

| Data symbol B                        |                                                   | ✓                                              |                                                   | ✓                                              |  |  |

| Data symbol C                        |                                                   |                                                | ✓                                                 | <b>✓</b>                                       |  |  |

| Data symbol D (LSB)                  | ✓                                                 | ✓                                              | ✓                                                 | ✓                                              |  |  |

#### Note to Table 2-4:

(1) Designs can use byte ordering when byte serialization and deserialization are used.

## 8B/10B Encoder

There are two different modes of operation for 8B/10B encoding. Single-width (8-bit) mode supports natural data rates from 622 Mbps to 3.125 Gbps. Double-width (16-bit cascaded) mode supports data rates above 3.125 Gbps. The encoded data has a maximum run length of five. The 8B/10B encoder can be bypassed. Figure 2–5 diagrams the 10-bit encoding process.

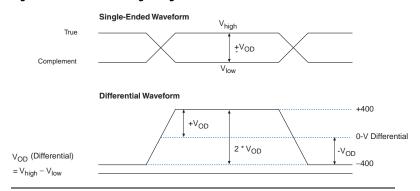

Differential signaling conventions are shown in Figure 2–9. The differential amplitude represents the value of the voltage between the true and complement signals. Peak-to-peak differential voltage is defined as 2 × (V<sub>HIGH</sub> – V<sub>LOW</sub>) = 2 × single-ended voltage swing. The common mode voltage is the average of V<sub>high</sub> and V<sub>low</sub>.

Figure 2-9. Differential Signaling

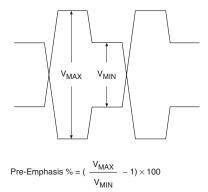

## **Programmable Pre-Emphasis**

The programmable pre-emphasis module controls the output driver to boost the high frequency components, and compensate for losses in the transmission medium, as shown in Figure 2–10. The pre-emphasis is set statically using the ALT2GXB megafunction or dynamically through the dynamic reconfiguration controller.

Figure 2-10. Pre-Emphasis Signaling

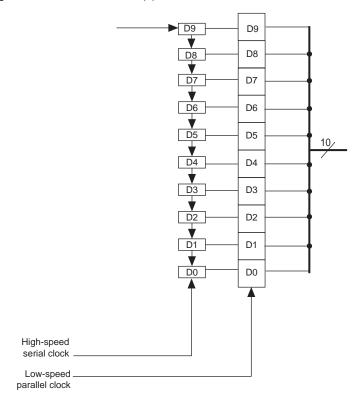

Figure 2–17. Deserializer Note (1)

Note to Figure 2-17:

1) This is a 10-bit deserializer. The deserializer can also convert 8, 16, or 20 bits of data.

## Word Aligner

The deserializer block creates 8-, 10-, 16-, or 20-bit parallel data. The deserializer ignores protocol symbol boundaries when converting this data. Therefore, the boundaries of the transferred words are arbitrary. The word aligner aligns the incoming data based on specific byte or word boundaries. The word alignment module is clocked by the local receiver recovered clock during normal operation. All the data and programmed patterns are defined as big-endian (most significant word followed by least significant word). Most-significant-bit-first protocols such as SONET/SDH should reverse the bit order of word align patterns programmed.

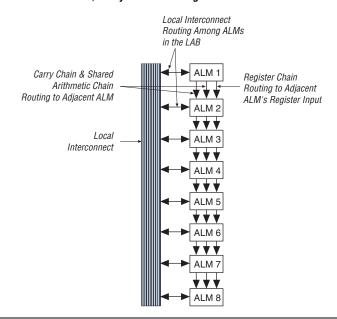

Figure 2-47. Shared Arithmetic Chain, Carry Chain and Register Chain Interconnects

The C4 interconnects span four LABs, M512, or M4K blocks up or down from a source LAB. Every LAB has its own set of C4 interconnects to drive either up or down. Figure 2–48 shows the C4 interconnect connections from a LAB in a column. The C4 interconnects can drive and be driven by all types of architecture blocks, including DSP blocks, TriMatrix memory blocks, and column and row IOEs. For LAB interconnection, a primary LAB or its LAB neighbor can drive a given C4 interconnect. C4 interconnects can drive each other to extend their range as well as drive row interconnects for column-to-column connections.

M-RAM blocks interface to LABs on right and left sides for easy access to horizontal I/O pins M-RAM M-RAM Block Block M-RAM M-RAM Block Block M-RAM M-RAM Block Block

Figure 2–54. EP2SGX130 Device with M-RAM Interface Locations Note (1)

Note to Figure 2-54:

M4K

**Blocks**

M512

Blocks

(1) The device shown is an EP2SGX130 device. The number and position of M-RAM blocks varies in other devices.

DSP

Blocks

LABs

DSP

**Blocks**

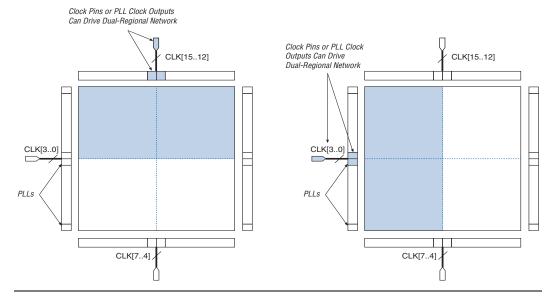

Figure 2-63. Dual-Regional Clocks

## Combined Resources

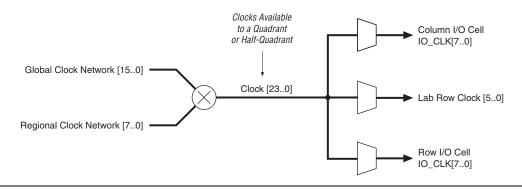

Within each quadrant, there are 24 distinct dedicated clocking resources consisting of 16 global clock lines and 8 regional clock lines. Multiplexers are used with these clocks to form buses to drive LAB row clocks, column IOE clocks, or row IOE clocks. Another multiplexer is used at the LAB level to select three of the six row clocks to feed the ALM registers in the LAB (see Figure 2–64).

Figure 2-64. Hierarchical Clock Networks per Quadrant

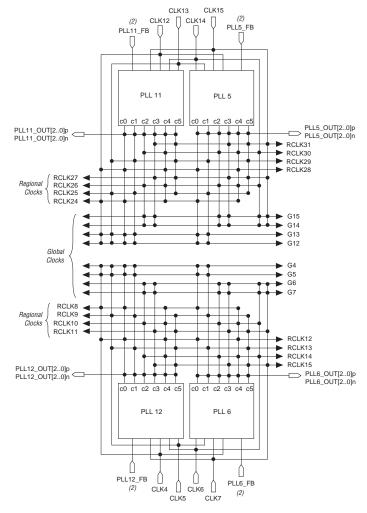

Figure 2–73 shows the global and regional clocking from enhanced PLL outputs and top and bottom CLK pins.

Figure 2–73. Global and Regional Clock Connections from Top and Bottom Clock Pins and Enhanced PLL Outputs Notes (1), (2)

#### *Notes to Figure 2–73:*

- (1) EP2SGX30C/D and EP2SGX60C/D devices only have two enhanced PLLs (5 and 6), but the connectivity from these two PLLs to the global and regional clock networks remains the same as shown.

- (2) If the design uses the feedback input, you will lose one (or two, if FBIN is differential) external clock output pin.

The connections to the global and regional clocks from the top clock pins and enhanced PLL outputs are shown in Table 2–28. The connections to the clocks from the bottom clock pins are shown in Table 2–29.

| Table 2–28. Global and Reg<br>(Part 1 of 2)                   | ional (  | Clock (  | Connec   | ctions   | from T   | Top Clo  | ock Pi   | ns and   | l Enha   | nced F   | PLL Ou   | ıtputs   |          |

|---------------------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Top Side Global and<br>Regional Clock Network<br>Connectivity | DLLCLK   | CLK12    | CLK13    | CLK14    | CLK15    | RCLK24   | RCLK25   | RCLK26   | RCLK27   | RCLK28   | RCLK29   | RCLK30   | RCLK31   |

| Clock pins                                                    | •        |          |          |          |          |          |          |          | •        |          |          | •        |          |

| CLK12p                                                        | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| CLK13p                                                        | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| CLK14p                                                        | <b>✓</b> |          |          | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| CLK15p                                                        | <b>✓</b> |          |          | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| CLK12n                                                        |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| CLK13n                                                        |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| CLK14n                                                        |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| CLK15n                                                        |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| Drivers from internal logic                                   |          |          |          |          |          |          |          |          | •        |          |          |          |          |

| GCLKDRV0                                                      |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |          |          |

| GCLKDRV1                                                      |          |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |          |

| GCLKDRV2                                                      |          |          |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |

| GCLKDRV3                                                      |          |          |          |          | <b>✓</b> |          |          |          |          |          |          |          |          |

| RCLKDRV0                                                      |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| RCLKDRV1                                                      |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| RCLKDRV2                                                      |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| RCLKDRV3                                                      |          |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| RCLKDRV4                                                      |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| RCLKDRV5                                                      |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| RCLKDRV6                                                      |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| RCLKDRV7                                                      |          |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| Enhanced PLL5 outputs                                         | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        |          | 1        | 1        | 1        |          |

| c0                                                            | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| c1                                                            | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| JTAG Instruction          | Instruction Code | Description                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SAMPLE/PRELOAD            | 00 0000 0101     | Allows a snapshot of signals at the device pins to be captured and examined during normal device operation and permits an initial data pattern to be output at the device pins. Also used by the SignalTap II embedded logic analyzer.                                                                                                                                                                                               |

| EXTEST(1)                 | 00 0000 1111     | Allows the external circuitry and board-level interconnects to be tested by forcing a test pattern at the output pins and capturing test results at the input pins.                                                                                                                                                                                                                                                                  |

| BYPASS                    | 11 1111 1111     | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation.                                                                                                                                                                                                                                          |

| USERCODE                  | 00 0000 0111     | Selects the 32-bit USERCODE register and places it between the TDI and TDO pins, allowing the USERCODE to be serially shifted out of TDO.                                                                                                                                                                                                                                                                                            |

| IDCODE                    | 00 0000 0110     | Selects the IDCODE register and places it between TDI and TDO, allowing the IDCODE to be serially shifted out of TDO.                                                                                                                                                                                                                                                                                                                |

| HIGHZ (1)                 | 00 0000 1011     | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation, while tri-stating all of the I/O pins.                                                                                                                                                                                                   |

| CLAMP (1)                 | 00 0000 1010     | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation while holding the I/O pins to a state defined by the data in the boundary-scan register.                                                                                                                                                  |

| ICR instructions          |                  | Used when configuring a Stratix II GX device via the JTAG port with a USB-Blaster™, MasterBlaster™, ByteBlasterMV™, or ByteBlaster II download cable, or when using a .jam or .jbc via an embedded processor or JRunner.                                                                                                                                                                                                             |

| PULSE_NCONFIG             | 00 0000 0001     | Emulates pulsing the ${\tt nCONFIG}$ pin low to trigger reconfiguration even though the physical pin is unaffected.                                                                                                                                                                                                                                                                                                                  |

| CONFIG_IO (2)             | 00 0000 1101     | Allows configuration of I/O standards through the JTAG chain for JTAG testing. Can be executed before, during, or after configuration. Stops configuration if executed during configuration. Once issued, the CONFIG_IO instruction holds nSTATUS low to reset the configuration device. nSTATUS is held low until the IOE configuration register is loaded and the TAP controller state machine transitions to the UPDATE_DR state. |

| SignalTap II instructions |                  | Monitors internal device operation with the SignalTap II embedded logic analyzer.                                                                                                                                                                                                                                                                                                                                                    |

#### *Notes to Table 3–1:*

- (1) Bus hold and weak pull-up resistor features override the high-impedance state of HIGHZ, CLAMP, and EXTEST.

- (2) For more information on using the CONFIG\_IO instruction, refer to the *MorphIO: An I/O Reconfiguration Solution* for Altera Devices White Paper.

The nIO\_PULLUP pin is a dedicated input that chooses whether the internal pull-up resistors on the user I/O pins and dual-purpose configuration I/O pins (nCSO, ASDO, DATA [7..0], nWS, nRS, RDYnBSY, nCS, CS, RUnLU, PGM [2..0], CLKUSR, INIT\_DONE, DEV\_OE, DEV\_CLR) are on or off before and during configuration. A logic high (1.5, 1.8, 2.5, 3.3 V) turns off the weak internal pull-up resistors, while a logic low turns them on.

Stratix II GX devices also offer a new power supply, V<sub>CCPD</sub>, which must be connected to 3.3 V in order to power the 3.3-V/2.5-V buffer available on the configuration input pins and JTAG pins. V<sub>CCPD</sub> applies to all the JTAG input pins (TCK, TMS, TDI, and TRST) and the following configuration pins: nCONFIG, DCLK (when used as an input), nio Pullup, Data [7..0], Runlu, nce, nws, nrs, cs, ncs, and CLKUSR. The VCCSEL pin allows the V<sub>CCIO</sub> setting (of the banks where the configuration inputs reside) to be independent of the voltage required by the configuration inputs. Therefore, when selecting the  $V_{CCIO}$  voltage, you do not have to take the  $V_{II}$  and  $V_{IH}$  levels driven to the configuration inputs into consideration. The configuration input pins, nCONFIG, DCLK (when used as an input), nIO PULLUP, RUNLU, nCE, nWS, nRS, CS, nCS, and CLKUSR, have a dual buffer design: a 3.3-V/2.5-V input buffer and a 1.8-V/1.5-V input buffer. The V<sub>CCSEL</sub> input pin selects which input buffer is used. The 3.3-V/2.5-V input buffer is powered by  $V_{CCPD}$ , while the 1.8-V/1.5-V input buffer is powered by  $V_{CCIO}$ .

$V_{CCSEL}$  is sampled during power-up. Therefore, the  $V_{CCSEL}$  setting cannot change on-the-fly or during a reconfiguration. The  $V_{CCSEL}$  input buffer is powered by  $V_{CCINT}$  and must be hardwired to  $V_{CCPD}$  or ground. A logic high  $V_{CCSEL}$  connection selects the 1.8-V/1.5-V input buffer; a logic low selects the 3.3-V/2.5-V input buffer.  $V_{CCSEL}$  should be set to comply with the logic levels driven out of the configuration device or the MAX II microprocessor.

If the design must support configuration input voltages of 3.3 V/2.5 V, set  $V_{CCSEL}$  to a logic low. You can set the  $V_{CCIO}$  voltage of the I/O bank that contains the configuration inputs to any supported voltage. If the design must support configuration input voltages of 1.8 V/1.5 V, set  $V_{CCSEL}$  to a logic high and the  $V_{CCIO}$  of the bank that contains the configuration inputs to 1.8 V/1.5 V.

For more information on multi-volt support, including information on using TDO and nCEO in multi-volt systems, refer to the *Stratix II GX Architecture* chapter in volume 1 of the *Stratix II GX Device Handbook*.

| Symbol/<br>Description                                                        | Conditions                                                                                                                                                                                                | -3 Speed<br>Commercial Speed<br>Grade |        |     | -4 Speed<br>Commercial and<br>Industrial Speed<br>Grade |        |     | -5 Speed<br>Commercial Speed<br>Grade |        |     | Unit |

|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------|-----|---------------------------------------------------------|--------|-----|---------------------------------------|--------|-----|------|

|                                                                               |                                                                                                                                                                                                           | Min                                   | Тур    | Max | Min                                                     | Тур    | Max | Min                                   | Тур    | Max |      |

| Serial RapidIO Re                                                             |                                                                                                                                                                                                           |                                       |        |     |                                                         |        |     |                                       |        |     |      |

| Deterministic Jitter<br>Tolerance<br>(peak-to-peak)                           | Data Rate = 1.25,<br>2.5, 3.125 Gbps<br>REFCLK = 125 MHz<br>Pattern = CJPAT<br>Equalizer Setting =<br>0 for 1.25 Gbps<br>Equalizer Setting =<br>6 for 2.5 Gbps<br>Equalizer Setting =<br>6 for 3.125 Gbps |                                       | > 0.37 | •   |                                                         | > 0.37 | •   |                                       | > 0.3  | 7   | UI   |

| Combined<br>Deterministic and<br>Random Jitter<br>Tolerance<br>(peak-to-peak) | Data Rate = 1.25,<br>2.5, 3.125 Gbps<br>REFCLK = 125 MHz<br>Pattern = CJPAT<br>Equalizer Setting =<br>0 for 1.25 Gbps<br>Equalizer Setting =<br>6 for 2.5 Gbps<br>Equalizer Setting =<br>6 for 3.125 Gbps |                                       | > 0.55 |     |                                                         | > 0.55 |     |                                       | > 0.55 | 5   | UI   |

| Table 4–19. Strati                                                | x II GX Transceiver Bl                                                                                          | ock AC | Specia                                | fication | Notes ( | 1), (2)                                                 | , (3) <b>(P</b> a | art 8 o | f 19)                    |         |      |

|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------|---------------------------------------|----------|---------|---------------------------------------------------------|-------------------|---------|--------------------------|---------|------|

| Symbol/<br>Description                                            | Conditions                                                                                                      |        | -3 Speed<br>Commercial Speed<br>Grade |          |         | -4 Speed<br>Commercial and<br>Industrial Speed<br>Grade |                   |         | -5 Spe<br>mercia<br>Grad | l Speed | Unit |

|                                                                   |                                                                                                                 | Min    | Тур                                   | Max      | Min     | Тур                                                     | Max               | Min     | Тур                      | Max     |      |

| GIGE Transmit Jit                                                 | ter Generation (12)                                                                                             |        |                                       |          |         |                                                         |                   |         |                          |         |      |

| Deterministic Jitter<br>(peak-to-peak)                            | Data Rate =<br>1.25 Gbps<br>REFCLK = 125 MHz<br>Pattern = CRPAT<br>V <sub>OD</sub> = 1400 mV<br>No Pre-emphasis | 1      | -                                     | 0.14     | 1       | ı                                                       | 0.14              | -       | -                        | 0.14    | U    |

| Total Jitter<br>(peak-to-peak)                                    | Data Rate = 1.25 Gbps REFCLK = 125 MHz Pattern = CRPAT V <sub>OD</sub> = 1400 mV No Pre-emphasis                | -      | -                                     | 0.279    | -       | -                                                       | 0.279             | -       | -                        | 0.279   | UI   |

| GIGE Receiver Jitt                                                | ter Tolerance (12)                                                                                              |        |                                       |          |         |                                                         |                   |         |                          |         |      |

| Deterministic Jitter<br>Tolerance<br>(peak-to-peak)               | Data Rate =<br>1.25 Gbps<br>REFCLK = 125 MHz<br>Pattern = CJPAT<br>No Equalization                              | > 0.4  |                                       | > 0.4    |         |                                                         | > 0.4             |         |                          | UI      |      |

| Combined Deterministic and Random Jitter Tolerance (peak-to-peak) | Data Rate =<br>1.25 Gbps<br>REFCLK = 125 MHz<br>Pattern = CJPAT<br>No Equalization                              |        | > 0.66                                | 6        | > 0.66  |                                                         | 6                 | > 0.66  |                          | 6       | UI   |

| HiGig Transmit Jit                                                | ter Generation (4), (1                                                                                          | 3)     |                                       |          |         |                                                         |                   |         |                          |         |      |

| Deterministic Jitter<br>(peak-to-peak)                            | Data Rate = 3.75 Gbps REFCLK = 187.5 MHz Pattern = CJPAT V <sub>OD</sub> = 1200 mV No Pre-emphasis              | -      | -                                     | 0.17     | -       |                                                         |                   | UI      |                          |         |      |

| Total Jitter<br>(peak-to-peak)                                    | Data Rate = 3.75 Gbps REFCLK = 187.5 MHz Pattern = CJPAT V <sub>OD</sub> = 1200 mV No Pre-emphasis              | 0.35   |                                       |          |         |                                                         | UI                |         |                          |         |      |

| Cumbal                | Davamatav                                                                                | Conditions                        | Davisa | Minimum | Tunical | Maximum | Unit  |

|-----------------------|------------------------------------------------------------------------------------------|-----------------------------------|--------|---------|---------|---------|-------|

| Symbol                | Parameter                                                                                | Conditions                        | Device | Minimum | Typical | Maximum | UIIIL |

| R <sub>CONF</sub> (4) | Value of I/O pin pull-up resistor before and                                             | Vi = 0, V <sub>CCIO</sub> = 3.3 V |        | 10      | 25      | 50      | KOhm  |

|                       | during configuration                                                                     | Vi = 0, V <sub>CCIO</sub> = 2.5 V |        | 15      | 35      | 70      | KOhm  |

|                       |                                                                                          | Vi = 0, V <sub>CCIO</sub> = 1.8 V |        | 30      | 50      | 100     | KOhm  |

|                       |                                                                                          | Vi = 0, V <sub>CCIO</sub> = 1.5 V |        | 40      | 75      | 150     | KOhm  |

|                       |                                                                                          | Vi = 0, V <sub>CCIO</sub> = 1.2 V |        | 50      | 90      | 170     | KOhm  |

|                       | Recommended value of I/O pin external pull-down resistor before and during configuration |                                   |        |         | 1       | 2       | KOhm  |

## Notes to Table 4-23:

- (1) Typical values are for  $T_A$  = 25 °C,  $V_{CCINT}$  = 1.2 V, and  $V_{CCIO}$  = 1.5 V, 1.8 V, 2.5 V, and 3.3 V.

- (2) This value is specified for normal device operation. The value may vary during power-up. This applies for all  $V_{CCIO}$  settings (3.3, 2.5, 1.8, and 1.5 V).

- (3) Maximum values depend on the actual TJ and design utilization. See *PowerPlay Early Power Estimator (EPE) and Power Analyzer* or the *Quartus II PowerPlay Power Analyzer and Optimization Technology* (available at www.altera.com) for maximum values. See the section "Power Consumption" on page 4–59 for more information.

- (4) Pin pull-up resistance values will lower if an external source drives the pin higher than V<sub>CCIO</sub>.

# I/O Standard Specifications

Tables 4–24 through 4–47 show the Stratix II GX device family I/O standard specifications.

| Table 4–24            | Table 4–24. LVTTL Specifications (Part 1 of 2) |                             |         |         |      |  |  |  |  |  |  |  |

|-----------------------|------------------------------------------------|-----------------------------|---------|---------|------|--|--|--|--|--|--|--|

| Symbol                | Parameter                                      | Conditions                  | Minimum | Maximum | Unit |  |  |  |  |  |  |  |

| V <sub>CCIO</sub> (1) | Output supply voltage                          |                             | 3.135   | 3.465   | V    |  |  |  |  |  |  |  |

| V <sub>IH</sub>       | High-level input voltage                       |                             | 1.7     | 4.0     | ٧    |  |  |  |  |  |  |  |

| V <sub>IL</sub>       | Low-level input voltage                        |                             | -0.3    | 0.8     | ٧    |  |  |  |  |  |  |  |

| V <sub>OH</sub>       | High-level output voltage                      | I <sub>OH</sub> = -4 mA (2) | 2.4     |         | ٧    |  |  |  |  |  |  |  |

Table 4–55 shows the Stratix II GX performance for some common designs. All performance values were obtained with the Quartus II software compilation of LPM or MegaCore functions for FIR and FFT designs.

| Table 4-55                       | 5. Stratix II GX Pe                     | rformance | Notes (Pa                     | rt 1 of 3)    | Note (1                  | )                           |                   |                      |       |  |

|----------------------------------|-----------------------------------------|-----------|-------------------------------|---------------|--------------------------|-----------------------------|-------------------|----------------------|-------|--|

|                                  |                                         | Re        | sources Us                    | ed            | Performance              |                             |                   |                      |       |  |

| Applications                     |                                         | ALUTs     | TriMatrix<br>Memory<br>Blocks | DSP<br>Blocks | -3 Speed<br>Grade<br>(2) | -3<br>Speed<br>Grade<br>(3) | -4 Speed<br>Grade | -5<br>Speed<br>Grade | Units |  |

| LE                               | 16-to-1<br>multiplexer (4)              | 21        | 0                             | 0             | 657.03                   | 620.73                      | 589.62            | 477.09               | MHz   |  |

|                                  | 32-to-1<br>multiplexer (4)              | 38        | 0                             | 0             | 534.75                   | 517.33                      | 472.81            | 369.27               | MHz   |  |

|                                  | 16-bit counter                          | 16        | 0                             | 0             | 568.18                   | 539.66                      | 507.61            | 422.47               | MHz   |  |

|                                  | 64-bit counter                          | 64        | 0                             | 0             | 242.54                   | 231.0                       | 217.77            | 180.31               | MHz   |  |

| TriMatrix<br>Memory<br>M512      | Simple<br>dual-port RAM<br>32 x 18bit   | 0         | 1                             | 0             | 500.0                    | 476.19                      | 447.22            | 373.13               | MHz   |  |

| block                            | FIFO 32 x 18 bit                        | 22        | 1                             | 0             | 500.00                   | 476.19                      | 460.82            | 373.13               | MHz   |  |

| TriMatrix<br>Memory<br>M4K block | Simple dual-<br>port RAM 128 x<br>36bit | 0         | 1                             | 0             | 540.54                   | 515.46                      | 483.09            | 401.6                | MHz   |  |

|                                  | True dual-port<br>RAM 128 x 18bit       | 0         | 1                             | 0             | 540.54                   | 515.46                      | 483.09            | 401.6                | MHz   |  |

|                                  | FIFO 128 x 36<br>bit                    | 22        | 1                             | 0             | 524.10                   | 500.25                      | 466.41            | 381.38               | MHz   |  |

| Table 4–84. Stratix II G                                  | X I/O Input De     | lay for Column                           | Pins (Part 3          | of 3)                 |                   |                   |      |

|-----------------------------------------------------------|--------------------|------------------------------------------|-----------------------|-----------------------|-------------------|-------------------|------|

| I/O Standard                                              | Parameter          | Fast Corner<br>Industrial/<br>Commercial | -3 Speed<br>Grade (2) | -3 Speed<br>Grade (3) | -4 Speed<br>Grade | -5 Speed<br>Grade | Unit |

| Differential SSTL-2                                       | t <sub>Pl</sub>    | 530                                      | 818                   | 857                   | 912               | 1094              | ps   |

| Class II (1)                                              | t <sub>PCOUT</sub> | 251                                      | 382                   | 400                   | 426               | 511               | ps   |

| Differential SSTL-18                                      | t <sub>Pl</sub>    | 569                                      | 898                   | 941                   | 1001              | 1201              | ps   |

| Class I (1)  Differential SSTL-18                         | t <sub>PCOUT</sub> | 290                                      | 462                   | 484                   | 515               | 618               | ps   |

| Differential SSTL-18 Class II (1)                         | t <sub>Pl</sub>    | 569                                      | 898                   | 941                   | 1001              | 1201              | ps   |

|                                                           | t <sub>PCOUT</sub> | 290                                      | 462                   | 484                   | 515               | 618               | ps   |

| Differential SSTL-18 Class II (1) 1.8-V differential HSTL | t <sub>Pl</sub>    | 569                                      | 898                   | 941                   | 1001              | 1201              | ps   |

| Class I (1)                                               | t <sub>PCOUT</sub> | 290                                      | 462                   | 484                   | 515               | 618               | ps   |

| 1.8-V differential HSTL                                   | t <sub>Pl</sub>    | 569                                      | 898                   | 941                   | 1001              | 1201              | ps   |

| Class II (1)                                              | t <sub>PCOUT</sub> | 290                                      | 462                   | 484                   | 515               | 618               | ps   |

| 1.5-V differential HSTL                                   | t <sub>Pl</sub>    | 587                                      | 993                   | 1041                  | 1107              | 1329              | ps   |

| Class I (1)                                               | t <sub>PCOUT</sub> | 308                                      | 557                   | 584                   | 621               | 746               | ps   |

| 1.5-V differential HSTL                                   | t <sub>Pl</sub>    | 587                                      | 993                   | 1041                  | 1107              | 1329              | ps   |

| Class II (1)                                              | t <sub>PCOUT</sub> | 308                                      | 557                   | 584                   | 621               | 746               | ps   |

- (1) These I/O standards are only supported on DQS pins.

(2) This column refers to -3 speed grades for EP2SGX30, EP2SGX60, and EP2SGX90 devices.

(3) This column refers to -3 speed grades for EP2SGX130 devices.

| Table 4–85. Stratix II | GX I/O Input I     | Delay for Row                            | Pins (Part 1 of       | 3)                    |                   |                   |      |

|------------------------|--------------------|------------------------------------------|-----------------------|-----------------------|-------------------|-------------------|------|

| I/O Standard           | Parameter          | Fast Corner<br>Industrial/<br>Commercial | -3 Speed<br>Grade (2) | -3 Speed<br>Grade (3) | -4 Speed<br>Grade | -5 Speed<br>Grade | Unit |

| LVTTL                  | t <sub>Pl</sub>    | 749                                      | 1287                  | 1350                  | 1435              | 1723              | ps   |

|                        | t <sub>PCOUT</sub> | 410                                      | 760                   | 798                   | 848               | 1018              | ps   |

| 2.5 V                  | t <sub>Pl</sub>    | 761                                      | 1273                  | 1335                  | 1419              | 1704              | ps   |

|                        | t <sub>PCOUT</sub> | 422                                      | 746                   | 783                   | 832               | 999               | ps   |

| 1.8 V                  | t <sub>Pl</sub>    | 827                                      | 1427                  | 1497                  | 1591              | 1911              | ps   |

|                        | t <sub>PCOUT</sub> | 488                                      | 900                   | 945                   | 1004              | 1206              | ps   |

| 1.5 V                  | t <sub>Pl</sub>    | 830                                      | 1498                  | 1571                  | 1671              | 2006              | ps   |

|                        | t <sub>PCOUT</sub> | 491                                      | 971                   | 1019                  | 1084              | 1301              | ps   |

| Table 4–97. Maximum Output Clock Toggle Rate Derating Factors (Part 3 of 5) |                   |                                                           |     |     |              |     |     |                            |     |     |

|-----------------------------------------------------------------------------|-------------------|-----------------------------------------------------------|-----|-----|--------------|-----|-----|----------------------------|-----|-----|

|                                                                             |                   | Maximum Output Clock Toggle Rate Derating Factors (ps/pF) |     |     |              |     |     |                            |     |     |

| I/O Standard                                                                | Drive<br>Strength | Column I/O Pins                                           |     |     | Row I/O Pins |     |     | Dedicated Clock<br>Outputs |     |     |

|                                                                             |                   | -3                                                        | -4  | -5  | -3           | -4  | -5  | -3                         | -4  | -5  |

| SSTL-18 Class II                                                            | 8 mA              | 173                                                       | 206 | 206 | -            | -   | -   | 155                        | 206 | 206 |

|                                                                             | 16 mA             | 150                                                       | 160 | 160 | -            | -   | -   | 140                        | 160 | 160 |

|                                                                             | 18 mA             | 120                                                       | 130 | 130 | -            | -   | -   | 110                        | 130 | 130 |

|                                                                             | 20 mA             | 109                                                       | 127 | 127 | -            | -   | -   | 94                         | 127 | 127 |

| 2.5-V SSTL-2                                                                | 8 mA              | 364                                                       | 680 | 680 | 364          | 680 | 680 | 350                        | 680 | 680 |

| Class I                                                                     | 12 mA             | 163                                                       | 207 | 207 | 163          | 207 | 207 | 188                        | 207 | 207 |

| 2.5-V SSTL-2<br>Class II                                                    | 16 mA             | 118                                                       | 147 | 147 | 118          | 147 | 147 | 94                         | 147 | 147 |

|                                                                             | 20 mA             | 99                                                        | 122 | 122 | -            | -   | -   | 87                         | 122 | 122 |

|                                                                             | 24 mA             | 91                                                        | 116 | 116 | -            | -   | -   | 85                         | 116 | 116 |

| 1.8-V SSTL-18<br>Class I                                                    | 4 mA              | 458                                                       | 570 | 570 | 458          | 570 | 570 | 505                        | 570 | 570 |

|                                                                             | 6 mA              | 305                                                       | 380 | 380 | 305          | 380 | 380 | 336                        | 380 | 380 |

|                                                                             | 8 mA              | 225                                                       | 282 | 282 | 225          | 282 | 282 | 248                        | 282 | 282 |

|                                                                             | 10 mA             | 167                                                       | 220 | 220 | 167          | 220 | 220 | 190                        | 220 | 220 |

|                                                                             | 12 mA             | 129                                                       | 175 | 175 | -            | -   | -   | 148                        | 175 | 175 |

| 1.8-V SSTL-18                                                               | 8 mA              | 173                                                       | 206 | 206 | -            | -   | -   | 155                        | 206 | 206 |

| Class II                                                                    | 16 mA             | 150                                                       | 160 | 160 | -            | -   | -   | 140                        | 160 | 160 |

|                                                                             | 18 mA             | 120                                                       | 130 | 130 | -            | -   | -   | 110                        | 130 | 130 |

|                                                                             | 20 mA             | 109                                                       | 127 | 127 | -            | -   | -   | 94                         | 127 | 127 |

| 1.8-V HSTL Class I                                                          | 4 mA              | 245                                                       | 282 | 282 | 245          | 282 | 282 | 229                        | 282 | 282 |

|                                                                             | 6 mA              | 164                                                       | 188 | 188 | 164          | 188 | 188 | 153                        | 188 | 188 |

|                                                                             | 8 mA              | 123                                                       | 140 | 140 | 123          | 140 | 140 | 114                        | 140 | 140 |

|                                                                             | 10 mA             | 110                                                       | 124 | 124 | 110          | 124 | 124 | 108                        | 124 | 124 |

|                                                                             | 12 mA             | 97                                                        | 110 | 110 | 97           | 110 | 110 | 104                        | 110 | 110 |

| 1.8-V HSTL<br>Class II                                                      | 16 mA             | 101                                                       | 104 | 104 | -            | -   | -   | 99                         | 104 | 104 |

|                                                                             | 18 mA             | 98                                                        | 102 | 102 | -            | -   | -   | 93                         | 102 | 102 |

|                                                                             | 20 mA             | 93                                                        | 99  | 99  | -            | -   | -   | 88                         | 99  | 99  |

| 1.5-V HSTL Class I                                                          | 4 mA              | 168                                                       | 196 | 196 | 168          | 196 | 196 | 188                        | 196 | 196 |

|                                                                             | 6 mA              | 112                                                       | 131 | 131 | 112          | 131 | 131 | 125                        | 131 | 131 |

|                                                                             | 8 mA              | 84                                                        | 99  | 99  | 84           | 99  | 99  | 95                         | 99  | 99  |

|                                                                             | 10 mA             | 87                                                        | 98  | 98  | -            | -   | -   | 90                         | 98  | 98  |

|                                                                             | 12 mA             | 86                                                        | 98  | 98  | -            | -   | -   | 87                         | 98  | 98  |

Table 4–107 shows the high-speed I/O timing specifications for -3 speed grade Stratix II GX devices.

|                                      | Conditions                                        |                          |      |     | peed G |       |                       |

|--------------------------------------|---------------------------------------------------|--------------------------|------|-----|--------|-------|-----------------------|

| Symbol                               |                                                   |                          |      |     | Тур    | Max   | Unit                  |

| $f_{IN} = f_{HSDR} / W$              | W = 2 to 32 (LVDS, HyperTransport technology) (3) |                          |      |     |        | 520   | MHz                   |

|                                      | W = 1 (SERDES bypass, LVDS only)                  |                          |      |     |        | 500   | MHz                   |

|                                      | W = 1 (SERDES used, LVDS only)                    |                          |      |     |        | 717   | MHz                   |

| f <sub>HSDR</sub> (data rate)        | J = 4 to 10 (LVDS, HyperTransport technology)     |                          |      |     |        | 1,040 | Mbps                  |

|                                      | J = 2 (LVDS, HyperTransport technology)           |                          |      |     |        | 760   | Mbps                  |

|                                      | J = 1 (LVDS only)                                 |                          |      |     |        | 500   | Mbps                  |

| f <sub>HSDRDPA</sub> (DPA data rate) | J = 4 to 10 (LVDS, HyperTransport technology)     |                          |      |     |        | 1,040 | Mbps                  |

| TCCS                                 | All differential standards                        |                          |      |     |        | 200   | ps                    |

| SW                                   | All differential standards                        |                          |      |     |        | -     | ps                    |

| Output jitter                        |                                                   |                          |      |     |        | 190   | ps                    |

| Output t <sub>RISE</sub>             | All differential I/O standards                    |                          |      |     |        | 160   | ps                    |

| Output t <sub>FALL</sub>             | All differential I/O standards                    |                          |      |     |        | 180   | ps                    |

| t <sub>DUTY</sub>                    |                                                   |                          |      |     | 50     | 55    | %                     |

| DPA run length                       | A run length                                      |                          |      |     |        | 6,400 | UI                    |

| DPA jitter tolerance (5)             | Data channel peak-                                | 0.44                     |      |     | UI     |       |                       |

| DPA lock time                        |                                                   |                          |      |     |        |       | Number of repetitions |

|                                      | SPI-4                                             | 0000000000<br>1111111111 | 10%  | 256 |        |       |                       |

|                                      | Parallel Rapid I/O                                | 00001111                 | 25%  | 256 |        |       | 1                     |

|                                      |                                                   | 10010000                 | 50%  | 256 |        |       | 1                     |

|                                      | Miscellaneous                                     | 10101010                 | 100% | 256 |        |       | 1                     |

|                                      |                                                   | 01010101                 |      | 256 |        |       | 1                     |

<sup>(1)</sup> When J = 4 to 10, the SERDES block is used.

<sup>(2)</sup> When J = 1 or 2, the SERDES block is bypassed.

<sup>(3)</sup> The input clock frequency and the W factor must satisfy the following fast PLL VCO specification: 150 ≤nput clock frequency × W ≤1,040.

<sup>(4)</sup> The minimum specification is dependent on the clock source (fast PLL, enhanced PLL, clock pin, and so on) and the clock routing resource (global, regional, or local) utilized. The I/O differential buffer and input register do not have a minimum toggle rate.

<sup>(5)</sup> For setup details, refer to the characterization report.

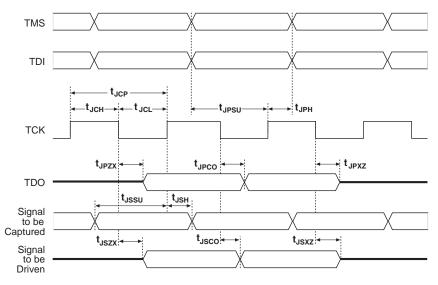

Figure 4-14. Stratix II GX JTAG Waveforms.

Table 4–117 shows the JTAG timing parameters and values for Stratix II GX devices.

| Table 4–117. Stratix II GX JTAG Timing Parameters and Values |                                                |     |     |      |  |  |  |

|--------------------------------------------------------------|------------------------------------------------|-----|-----|------|--|--|--|

| Symbol                                                       | Parameter                                      | Min | Max | Unit |  |  |  |

| t <sub>JCP</sub>                                             | TCK clock period                               | 30  |     | ns   |  |  |  |

| t <sub>JCH</sub>                                             | TCK clock high time                            | 12  |     | ns   |  |  |  |

| t <sub>JCL</sub>                                             | TCK clock low time                             | 12  |     | ns   |  |  |  |

| t <sub>JPSU</sub>                                            | JTAG port setup time                           | 4   |     | ns   |  |  |  |

| t <sub>JPH</sub>                                             | JTAG port hold time                            | 5   |     | ns   |  |  |  |

| t <sub>JPCO</sub>                                            | JTAG port clock to output                      |     | 9   | ns   |  |  |  |

| t <sub>JPZX</sub>                                            | JTAG port high impedance to valid output       |     | 9   | ns   |  |  |  |

| t <sub>JPXZ</sub>                                            | JTAG port valid output to high impedance       |     | 9   | ns   |  |  |  |

| t <sub>JSSU</sub>                                            | Capture register setup time                    | 4   |     | ns   |  |  |  |

| t <sub>JSH</sub>                                             | Capture register hold time                     | 5   |     | ns   |  |  |  |

| t <sub>JSCO</sub>                                            | Update register clock to output                |     | 12  | ns   |  |  |  |

| t <sub>JSZX</sub>                                            | Update register high impedance to valid output |     | 12  | ns   |  |  |  |

| t <sub>JSXZ</sub>                                            | Update register valid output to high impedance |     | 12  | ns   |  |  |  |