Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 4548                                                        |

| Number of Logic Elements/Cells | 90960                                                       |

| Total RAM Bits                 | 4520448                                                     |

| Number of I/O                  | 650                                                         |

| Number of Gates                | -                                                           |

| Voltage - Supply               | 1.15V ~ 1.25V                                               |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 1508-BBGA, FCBGA                                            |

| Supplier Device Package        | 1508-FBGA, FC (40x40)                                       |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2sgx90ff1508c3 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1. Introduction

SIIGX51001-1.6

The Stratix® II GX family of devices is Altera's third generation of FPGAs to combine high-speed serial transceivers with a scalable, high-performance logic array. Stratix II GX devices include 4 to 20 high-speed transceiver channels, each incorporating clock and data recovery unit (CRU) technology and embedded SERDES capability at data rates of up to 6.375 gigabits per second (Gbps). The transceivers are grouped into four-channel transceiver blocks and are designed for low power consumption and small die size. The Stratix II GX FPGA technology is built upon the Stratix II architecture and offers a 1.2-V logic array with unmatched performance, flexibility, and time-to-market capabilities. This scalable, high-performance architecture makes Stratix II GX devices ideal for high-speed backplane interface, chip-to-chip, and communications protocol-bridging applications.

# **Features**

This section lists the Stratix II GX device features.

### Main device features:

- TriMatrix memory consisting of three RAM block sizes to implement true dual-port memory and first-in first-out (FIFO) buffers with performance up to 550 MHz

- Up to 16 global clock networks with up to 32 regional clock networks per device region

- High-speed DSP blocks provide dedicated implementation of multipliers (at up to 450 MHz), multiply-accumulate functions, and finite impulse response (FIR) filters

- Up to four enhanced PLLs per device provide spread spectrum, programmable bandwidth, clock switch-over, real-time PLL reconfiguration, and advanced multiplication and phase shifting

- Support for numerous single-ended and differential I/O standards

- High-speed source-synchronous differential I/O support on up to 71 channels

- Support for source-synchronous bus standards, including SPI-4 Phase 2 (POS-PHY Level 4), SFI-4.1, XSBI, UTOPIA IV, NPSI, and CSIX-L1

- Support for high-speed external memory, including quad data rate (QDR and QDRII) SRAM, double data rate (DDR and DDR2) SDRAM, and single data rate (SDR) SDRAM

# 2. Stratix II GX Architecture

SIIGX51003-2.2

# **Transceivers**

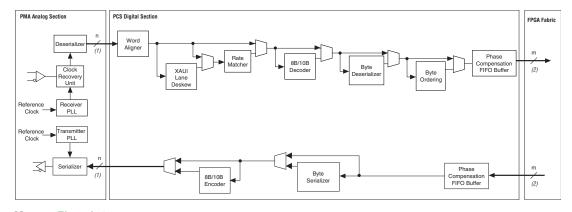

Stratix<sup>®</sup> II GX devices incorporate dedicated embedded circuitry on the right side of the device, which contains up to 20 high-speed 6.375-Gbps serial transceiver channels. Each Stratix II GX transceiver block contains four full-duplex channels and supporting logic to transmit and receive high-speed serial data streams. The transceivers deliver bidirectional point-to-point data transmissions, with up to 51 Gbps (6.375 Gbps per channel) of full-duplex data transmission per transceiver block. Figure 2–1 shows the function blocks that make up a transceiver channel within the Stratix II GX device.

Figure 2-1. Stratix II GX Transceiver Block Diagram

### *Notes to Figure 2–1:*

- (1) n represents the number of bits in each word that need to be serialized by the transmitter portion of the PMA or have been describing by the receiver portion of the PMA. n = 8, 10, 16, or 20.

- (2) m represents the number of bits in the word that pass between the FPGA logic and the PCS portion of the transceiver. m = 8, 10, 16, 20, 32, or 40.

Transceivers within each block are independent and have their own set of dividers. Therefore, each transceiver can operate at different frequencies. Each block can select from two reference clocks to provide two clock domains that each transceiver can select from.

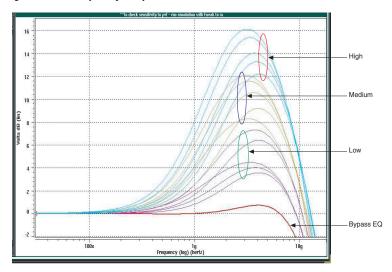

The Stratix II GX receivers also have adaptive equalization capability that adjusts the equalization levels to compensate for changing link characteristics. The adaptive equalization can be powered down dynamically after it selects the appropriate equalization levels.

The receiver equalization circuit is comprised of a programmable amplifier. Each stage is a peaking equalizer with a different center frequency and programmable gain. This allows varying amounts of gain to be applied, depending on the overall frequency response of the channel loss. Channel loss is defined as the summation of all losses through the PCB traces, vias, connectors, and cables present in the physical link. Figure 2–15 shows the frequency response for the 16 programmable settings allowed by the Quartus II software for Stratix II GX devices.

Figure 2-15. Frequency Response

### Receiver PLL and CRU

Each transceiver block has four receiver PLLs, lock detectors, signal detectors, run length checkers, and CRU units, each of which is dedicated to a receive channel. If the receive channel associated with a particular receiver PLL or CRU is not used, the receiver PLL and CRU are powered down for the channel. Figure 2–16 shows the receiver PLL and CRU circuits.

Table 2–11 summarizes the possible clocking connections for the transceivers.

| Table 2–11. Availa                            | Table 2–11. Available Clocking Connections for Transceivers |              |              |                   |                            |  |  |  |  |  |  |  |

|-----------------------------------------------|-------------------------------------------------------------|--------------|--------------|-------------------|----------------------------|--|--|--|--|--|--|--|

|                                               | Destination                                                 |              |              |                   |                            |  |  |  |  |  |  |  |

| Source                                        | Transmitter<br>PLL                                          | Receiver PLL | Global Clock | Regional<br>Clock | Inter-Transceiver<br>Lines |  |  |  |  |  |  |  |

| REFCLK[10]                                    | <b>✓</b>                                                    | <b>✓</b>     | <b>✓</b>     | <b>✓</b>          | <b>✓</b>                   |  |  |  |  |  |  |  |

| Transmitter PLL                               |                                                             |              | ✓            | <b>✓</b>          |                            |  |  |  |  |  |  |  |

| Receiver PLL                                  |                                                             |              | ✓            | <b>✓</b>          |                            |  |  |  |  |  |  |  |

| Global clock<br>(driven from an<br>input pin) | <b>✓</b>                                                    | ~            |              |                   |                            |  |  |  |  |  |  |  |

| Inter-transceiver lines                       | <b>✓</b>                                                    | ~            |              |                   |                            |  |  |  |  |  |  |  |

### Clock Resource for PLD-Transceiver Interface

For the regional or global clock network to route into the transceiver, a local route input output (LRIO) channel is required. Each LRIO clock region has up to eight clock paths and each transceiver block has a maximum of eight clock paths for connecting with LRIO clocks. These resources are limited and determine the number of clocks that can be used between the PLD and transceiver blocks. Table 2–12 shows the number of LRIO resources available for Stratix II GX devices with different numbers of transceiver blocks.

Tables 2–12 through 2–15 show the connection of the LRIO clock resource to the transceiver block.

| Table 2–12. Av          | ailable Clocki  | ing Connection    | s for Transcei         | vers in 2SGX30D        |  |  |

|-------------------------|-----------------|-------------------|------------------------|------------------------|--|--|

|                         | Clock R         | Transceiver       |                        |                        |  |  |

| Region                  | Global<br>Clock | Regional<br>Clock | Bank 13<br>8 Clock I/O | Bank 14<br>8 Clock I/O |  |  |

| Region0<br>8 LRIO clock | ✓               | RCLK 20-27        | ✓                      |                        |  |  |

| Region1<br>8 LRIO clock | ✓               | RCLK 12-19        |                        | <b>✓</b>               |  |  |

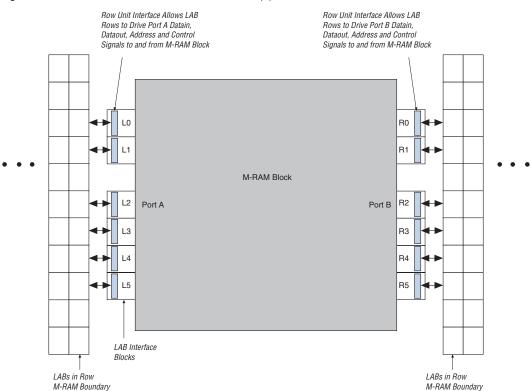

Figure 2–55. M-RAM Block LAB Row Interface Note (1)

*Note to Figure 2–55:*

(1) Only R24 and C16 interconnects cross the M-RAM block boundaries.

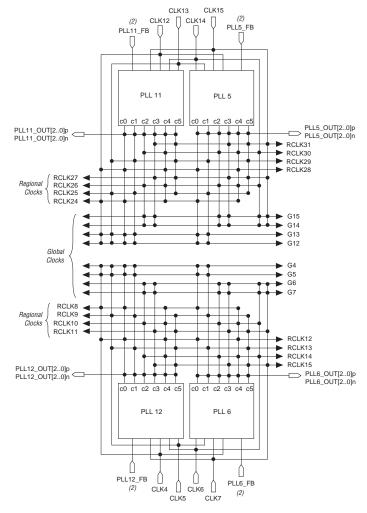

Figure 2–73 shows the global and regional clocking from enhanced PLL outputs and top and bottom CLK pins.

Figure 2–73. Global and Regional Clock Connections from Top and Bottom Clock Pins and Enhanced PLL Outputs Notes (1), (2)

### *Notes to Figure 2–73:*

- (1) EP2SGX30C/D and EP2SGX60C/D devices only have two enhanced PLLs (5 and 6), but the connectivity from these two PLLs to the global and regional clock networks remains the same as shown.

- (2) If the design uses the feedback input, you will lose one (or two, if FBIN is differential) external clock output pin.

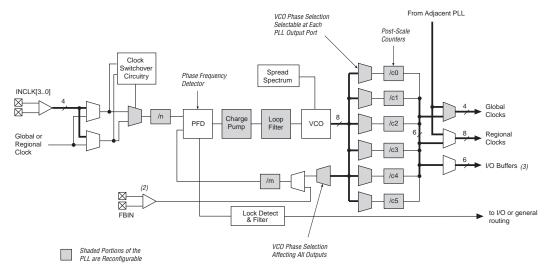

### **Enhanced PLLs**

Stratix II GX devices contain up to four enhanced PLLs with advanced clock management features. These features include support for external clock feedback mode, spread-spectrum clocking, and counter cascading. Figure 2–74 shows a diagram of the enhanced PLL.

Figure 2–74. Stratix II GX Enhanced PLL Note (1)

### *Notes to Figure 2–74:*

- Each clock source can come from any of the four clock pins that are physically located on the same side of the device

as the PLL.

- (2) If the feedback input is used, you will lose one (or two, if FBIN is differential) external clock output pin.

- (3) Each enhanced PLL has three differential external clock outputs or six single-ended external clock outputs.

- (4) The global or regional clock input can be driven by an output from another PLL, a pin-driven dedicated global or regional clock, or through a clock control block provided the clock control block is fed by an output from another PLL or a pin-driven dedicated global or regional clock. An internally generated global signal cannot drive the PLL.

### **Fast PLLs**

Stratix II GX devices contain up to four fast PLLs with high-speed serial interfacing ability. The fast PLLs offer high-speed outputs to manage the high-speed differential I/O interfaces. Figure 2–75 shows a diagram of the fast PLL.

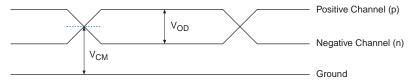

Figure 4-4. Transmitter Output Waveform

# Differential Waveform $V_{OD}$ (diff peak-peak) = 2 x $V_{OD}$ (single-ended) $V_{OD}$ p-n=0 $V_{OD}$

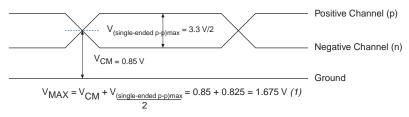

Figure 4-5. Maximum Receiver Input Pin Voltage

### Single-Ended Waveform

*Note to Figure 4–5:*

(1) The absolute  $V_{MAX}$  that the receiver input pins can tolerate is 2 V.

Tables 4–7 through 4–12 show the typical  $V_{OD}$  for data rates from 600 Mbps to 6.375 Gbps. The specification is for measurement at the package ball.

| Table 4–7. Typical                                       | Table 4–7. Typical $V_{OD}$ Setting, TX Term = 100 $\Omega$ Note (1) |                                |     |     |      |      |      |  |  |  |  |  |

|----------------------------------------------------------|----------------------------------------------------------------------|--------------------------------|-----|-----|------|------|------|--|--|--|--|--|

| V <sub>CCH</sub> TX = 1.5 V V <sub>OD</sub> Setting (mV) |                                                                      |                                |     |     |      |      |      |  |  |  |  |  |

|                                                          | 200                                                                  | 200 400 600 800 1000 1200 1400 |     |     |      |      |      |  |  |  |  |  |

| V <sub>OD</sub> Typical (mV)                             | 220                                                                  | 430                            | 625 | 830 | 1020 | 1200 | 1350 |  |  |  |  |  |

Note to Table 4-7:

(1) Applicable to data rates from 600 Mbps to 6.375 Gbps. Specification is for measurement at the package ball.

| Table 4–19. Strati                                                | ix II GX Transceiver Bi                                                                                             | lock AC                               | Specif | ication | Notes (                                                 | (1), (2) | , (3) <b>(P</b> | art 9 o                               | f 19) |     |      |

|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------|---------|---------------------------------------------------------|----------|-----------------|---------------------------------------|-------|-----|------|

| Symbol/<br>Description                                            | Conditions                                                                                                          | -3 Speed<br>Commercial Speed<br>Grade |        |         | -4 Speed<br>Commercial and<br>Industrial Speed<br>Grade |          |                 | -5 Speed<br>Commercial Speed<br>Grade |       |     | Unit |

|                                                                   |                                                                                                                     | Min                                   | Тур    | Max     | Min                                                     | Тур      | Max             | Min                                   | Тур   | Max |      |

| HiGig Receiver Jit                                                | ter Tolerance (13)                                                                                                  |                                       |        |         |                                                         |          |                 |                                       |       |     |      |

| Deterministic Jitter<br>Tolerance<br>(peak-to-peak)               | Data Rate = 3.75 Gbps REFCLK = 187.5 MHz Pattern = CJPAT No Equalization DC Gain = 3 dB                             |                                       | > 0.37 | ,       |                                                         | -        |                 |                                       | -     |     | U    |

| Combined                                                          | Data Rate = 3.75 Gbps REFCLK = 187.5 MHz Pattern = CJPAT No Equalization DC Gain = 3 dB                             |                                       | > 0.65 | ,       |                                                         | -        |                 |                                       | -     |     | UI   |

| Deterministic and<br>Random Jitter<br>Tolerance<br>(peak-to-peak) | Jitter Frequency = 22.1 KHz Data Rate = 3.75 Gbps REFCLK = 187.5 MHz Pattern = CJPAT No Equalization DC Gain = 3 dB |                                       | > 8.5  |         |                                                         | -        |                 |                                       | -     |     | UI   |

| Symbol/<br>Description                                                 | Conditions                                                                                                                                                                                                            | -3 Speed<br>Commercial Speed<br>Grade |       |     | -4 Speed<br>Commercial and<br>Industrial Speed<br>Grade |       |     | -5 Speed<br>Commercial Speed<br>Grade |     |     | Unit |

|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------|-----|---------------------------------------------------------|-------|-----|---------------------------------------|-----|-----|------|

|                                                                        |                                                                                                                                                                                                                       | Min                                   | Тур   | Max | Min                                                     | Тур   | Max | Min                                   | Тур | Max |      |

| Sinusoidal Jitter<br>Tolerance<br>(peak-to-peak) <i>(6)</i><br>(cont.) | Jitter Frequency = 20 MHz Data Rate = 614.4 Mbps, 1.2288 Gbps, 2.4576 Gbps REFCLK = 61.44 MHz for 614.4 Mbps REFCLK = 122.88 MHz for 1.2288 Gbps and 2.4576 Gbps Pattern = CJPAT Equalizer Setting = 6 DC Gain = 0 dB |                                       | > 0.1 |     |                                                         | > 0.1 |     |                                       | N/A |     | UI   |

# **Bus Hold Specifications**

Table 4–48 shows the Stratix II GX device family bus hold specifications.

| Table 4-48.                  | . Bus Hold Para                                | meters |                         |     |      |      |      |     |      |     |      |      |

|------------------------------|------------------------------------------------|--------|-------------------------|-----|------|------|------|-----|------|-----|------|------|

|                              |                                                |        | V <sub>CCIO</sub> Level |     |      |      |      |     |      |     |      |      |

| Parameter                    | Conditions                                     | 1.2    | 2 V                     | 1.  | .5 V | 1.8  | 8 V  | 2.  | 5 V  | 3.3 | 3 V  | Unit |

|                              |                                                | Min    | Max                     | Min | Max  | Min  | Max  | Min | Max  | Min | Max  |      |

| Low<br>sustaining<br>current | V <sub>IN</sub> > V <sub>IL</sub><br>(maximum) | 22.5   |                         | 25  |      | 30   |      | 50  |      | 70  |      | μΑ   |

| High sustaining current      | V <sub>IN</sub> < V <sub>IH</sub><br>(minimum) | -22.5  |                         | -25 |      | -30  |      | -50 |      | -70 |      | μΑ   |

| Low<br>overdrive<br>current  | 0 V < V <sub>IN</sub> < V <sub>CCIO</sub>      |        | 120                     |     | 160  |      | 200  |     | 300  |     | 500  | μА   |

| High overdrive current       | 0 V < V <sub>IN</sub> < V <sub>CCIO</sub>      |        | -120                    |     | -160 |      | -200 |     | -300 |     | -500 | μА   |

| Bus-hold<br>trip point       |                                                | 0.45   | 0.95                    | 0.5 | 1.0  | 0.68 | 1.07 | 0.7 | 1.7  | 0.8 | 2.0  | ٧    |

# **On-Chip Termination Specifications**

Tables 4–49 and 4–50 define the specification for internal termination resistance tolerance when using series or differential on-chip termination.

| Table 4-4                      | 49. On-Chip Termination Specificat                                     | ion for Top and Bottor         | m I/O Banks (Par  | t 1 of 2) Notes   | s (1) <b>,</b> (2) |

|--------------------------------|------------------------------------------------------------------------|--------------------------------|-------------------|-------------------|--------------------|

|                                |                                                                        |                                | Resist            | ance Tolerance    |                    |

| Symbol                         | Description                                                            | Conditions                     | Commercial<br>Max | Industrial<br>Max | Unit               |

| 25-Ω R <sub>S</sub><br>3.3/2.5 | Internal series termination with calibration (25- $\Omega$ setting)    | $V_{CCIO} = 3.3/2.5 \text{ V}$ | ±5                | ±10               | %                  |

|                                | Internal series termination without calibration (25- $\Omega$ setting) | V <sub>CCIO</sub> = 3.3/2.5 V  | ±30               | ±30               | %                  |

| 50-ΩR <sub>S</sub><br>3.3/2.5  | Internal series termination with calibration (50-Ω setting)            | V <sub>CCIO</sub> = 3.3/2.5 V  | ±5                | ±10               | %                  |

|                                | Internal series termination without calibration (50- $\Omega$ setting) | V <sub>CCIO</sub> = 3.3/2.5 V  | ±30               | ± 30              | %                  |

| Table 4-57. IC             | DE Internal Timing Micro                          | parame                | ters (Pa | rt 2 of 2             | <u>')</u> |                   |      |                   |      |      |

|----------------------------|---------------------------------------------------|-----------------------|----------|-----------------------|-----------|-------------------|------|-------------------|------|------|

| Symbol                     | Parameter                                         | -3 Speed<br>Grade (1) |          | -3 Speed<br>Grade (2) |           | -4 Speed<br>Grade |      | -5 Speed<br>Grade |      | Unit |

| ,                          |                                                   | Min                   | Max      | Min                   | Max       | Min               | Max  | Min               | Max  |      |

| t <sub>PIN2COMBOUT_R</sub> | Row input pin to IOE combinational output         | 410                   | 760      | 410                   | 798       | 410               | 848  | 410               | 1018 | ps   |

| t <sub>PIN2COMBOUT_C</sub> | Column input pin to IOE combinational output      | 428                   | 787      | 428                   | 825       | 428               | 878  | 428               | 1054 | ps   |

| t <sub>COMBIN2PIN_R</sub>  | Row IOE data input to combinational output pin    | 1101                  | 2026     | 1101                  | 2127      | 1101              | 2261 | 1101              | 2439 | ps   |

| t <sub>COMBIN2PIN_C</sub>  | Column IOE data input to combinational output pin | 991                   | 1854     | 991                   | 1946      | 991               | 2069 | 991               | 2246 | ps   |

| t <sub>CLR</sub>           | Minimum clear pulse width                         | 200                   |          | 210                   |           | 223               |      | 268               |      | ps   |

| t <sub>PRE</sub>           | Minimum preset pulse width                        | 200                   |          | 210                   |           | 223               |      | 268               |      | ps   |

| t <sub>CLKL</sub>          | Minimum clock low time                            | 600                   |          | 630                   |           | 669               |      | 804               |      | ps   |

| t <sub>CLKH</sub>          | Minimum clock high time                           | 600                   |          | 630                   |           | 669               |      | 804               |      | ps   |

<sup>(1)</sup> This column refers to -3 speed grades for EP2SGX30, EP2SGX60, and EP2SGX90 devices.

(2) This column refers to -3 speed grades for EP2SGX130 devices.

| Symbol          | Parameter                                                    | -3 Speed<br>Grade (1) |     | -3 Speed<br>Grade <i>(2)</i> |     | -4 Speed<br>Grade |     | -5 Speed<br>Grade |     | Unit |

|-----------------|--------------------------------------------------------------|-----------------------|-----|------------------------------|-----|-------------------|-----|-------------------|-----|------|

|                 |                                                              | Min                   | Max | Min                          | Max | Min               | Max | Min               | Max |      |

| t <sub>SU</sub> | Input, pipeline, and output register setup time before clock | 50                    |     | 52                           |     | 55                |     | 67                |     | ps   |

| t <sub>H</sub>  | Input, pipeline, and output register hold time after clock   | 180                   |     | 189                          |     | 200               |     | 241               |     | ps   |

| t <sub>CO</sub> | Input, pipeline, and output register clock-to-output delay   | 0                     | 0   | 0                            | 0   | 0                 | 0   | 0                 | 0   | ps   |

| Table 4-77. E        | Table 4–77. EP2SGX130 Column Pins Regional Clock Timing Parameters |            |          |          |          |        |  |  |  |  |  |  |

|----------------------|--------------------------------------------------------------------|------------|----------|----------|----------|--------|--|--|--|--|--|--|

| Parameter            | Fast                                                               | Corner     | -3 Speed | -4 Speed | -5 Speed | Units  |  |  |  |  |  |  |

| Parameter            | Industrial                                                         | Commercial | Grade    | Grade    | Grade    | UIIIIS |  |  |  |  |  |  |

| t <sub>CIN</sub>     | 1.815                                                              | 1.834      | 3.218    | 3.417    | 4.087    | ns     |  |  |  |  |  |  |

| t <sub>COUT</sub>    | 1.650                                                              | 1.669      | 3.218    | 3.417    | 4.087    | ns     |  |  |  |  |  |  |

| t <sub>PLLCIN</sub>  | 0.116                                                              | 0.134      | 0.349    | 0.364    | 0.426    | ns     |  |  |  |  |  |  |

| t <sub>PLLCOUT</sub> | -0.049                                                             | -0.031     | 0.361    | 0.378    | 0.444    | ns     |  |  |  |  |  |  |

| Table 4–78. E        | Table 4–78. EP2SGX130 Row Pins Regional Clock Timing Parameters |            |          |          |          |        |  |  |  |  |  |  |

|----------------------|-----------------------------------------------------------------|------------|----------|----------|----------|--------|--|--|--|--|--|--|

| Parameter            | Fast (                                                          | Corner     | -3 Speed | -4 Speed | -5 Speed | Units  |  |  |  |  |  |  |

| raiailletei          | Industrial                                                      | Commercial | Grade    | Grade    | Grade    | UIIIIS |  |  |  |  |  |  |

| t <sub>CIN</sub>     | 1.544                                                           | 1.560      | 3.195    | 3.395    | 4.060    | ns     |  |  |  |  |  |  |

| t <sub>COUT</sub>    | 1.549                                                           | 1.565      | 3.195    | 3.395    | 4.060    | ns     |  |  |  |  |  |  |

| t <sub>PLLCIN</sub>  | -0.149                                                          | -0.132     | 0.34     | 0.356    | 0.417    | ns     |  |  |  |  |  |  |

| t <sub>PLLCOUT</sub> | -0.144                                                          | -0.127     | 0.342    | 0.356    | 0.417    | ns     |  |  |  |  |  |  |

# **Clock Network Skew Adders**

The Quartus II software models skew within dedicated clock networks such as global and regional clocks. Therefore, the intra-clock network skew adder is not specified. Table 4–79 specifies the intra-clock skew between any two clock networks driving any registers in the Stratix II GX device.

| Table 4–79. Clock Network Specifications (Part 1 of 2) |                                  |     |     |      |      |  |

|--------------------------------------------------------|----------------------------------|-----|-----|------|------|--|

| Name                                                   | Description                      | Min | Тур | Max  | Unit |  |

| Clock skew adder                                       | Inter-clock network, same side   |     |     | ±50  | ps   |  |

| EP2SGX30 (1)                                           | Inter-clock network, entire chip |     |     | ±100 | ps   |  |

| Clock skew adder                                       | Inter-clock network, same side   |     |     | ±50  | ps   |  |

| EP2SGX60 (1)                                           | Inter-clock network, entire chip |     |     | ±100 | ps   |  |

| Clock skew adder                                       | Inter-clock network, same side   |     |     | ±55  | ps   |  |

| EP2SGX90 (1)                                           | Inter-clock network, entire chip |     |     | ±110 | ps   |  |

Table 4–82. Default Loading of Different I/O Standards for Stratix II GX Devices (Part 2 of 2)

| I/O Standard                     | Capacitive Load | Unit |

|----------------------------------|-----------------|------|

| SSTL-18 Class I                  | 0               | pF   |

| SSTL-18 Class II                 | 0               | pF   |

| 1.5-V HSTL Class I               | 0               | pF   |

| 1.5-V HSTL Class II              | 0               | pF   |

| 1.8-V HSTL Class I               | 0               | pF   |

| 1.8-V HSTL Class II              | 0               | pF   |

| Differential SSTL-2 Class I      | 0               | pF   |

| Differential SSTL-2 Class II     | 0               | pF   |

| Differential SSTL-18 Class I     | 0               | pF   |

| Differential SSTL-18 Class II    | 0               | pF   |

| 1.5-V differential HSTL Class I  | 0               | pF   |

| 1.5-V differential HSTL Class II | 0               | pF   |

| 1.8-V differential HSTL Class I  | 0               | pF   |

| 1.8-V differential HSTL Class II | 0               | pF   |

| LVDS                             | 0               | pF   |

# I/O Delays

See Tables 4–83 through 4–87 for I/O delays.

| Table 4–83. I/O Delay Parameters |                                              |  |  |  |

|----------------------------------|----------------------------------------------|--|--|--|

| Symbol                           | Parameter                                    |  |  |  |

| t <sub>DIP</sub>                 | Delay from I/O datain to output pad          |  |  |  |

| t <sub>OP</sub>                  | Delay from I/O output register to output pad |  |  |  |

| t <sub>PCOUT</sub>               | Delay from input pad to I/O dataout to core  |  |  |  |

| t <sub>Pl</sub>                  | Delay from input pad to I/O input register   |  |  |  |

| Table 4–84. Stratix II GX I/O Input Delay for Column Pins (Part 1 of 3) |                    |                                          |                       |                       |                   |                   |      |

|-------------------------------------------------------------------------|--------------------|------------------------------------------|-----------------------|-----------------------|-------------------|-------------------|------|

| I/O Standard                                                            | Parameter          | Fast Corner<br>Industrial/<br>Commercial | -3 Speed<br>Grade (2) | -3 Speed<br>Grade (3) | -4 Speed<br>Grade | -5 Speed<br>Grade | Unit |

| LVTTL                                                                   | t <sub>Pl</sub>    | 707                                      | 1223                  | 1282                  | 1364              | 1637              | ps   |

|                                                                         | t <sub>PCOUT</sub> | 428                                      | 787                   | 825                   | 878               | 1054              | ps   |

| I/O Standard | Drive<br>Strength | Parameter        | Fast Corner<br>Industrial/<br>Commercial | -3 Speed<br>Grade (3) | -3 Speed<br>Grade (4) | -4 Speed<br>Grade | -5 Speed<br>Grade | Unit |

|--------------|-------------------|------------------|------------------------------------------|-----------------------|-----------------------|-------------------|-------------------|------|

| 2.5 V        | 4 mA              | t <sub>OP</sub>  | 1053                                     | 2063                  | 2165                  | 2302              | 2480              | ps   |

|              |                   | t <sub>DIP</sub> | 1075                                     | 2129                  | 2235                  | 2376              | 2570              | ps   |

|              | 8 mA              | t <sub>OP</sub>  | 1001                                     | 1841                  | 1932                  | 2054              | 2218              | ps   |

|              |                   | t <sub>DIP</sub> | 1023                                     | 1907                  | 2002                  | 2128              | 2308              | ps   |

|              | 12 mA             | t <sub>OP</sub>  | 980                                      | 1742                  | 1828                  | 1944              | 2101              | ps   |

|              |                   | t <sub>DIP</sub> | 1002                                     | 1808                  | 1898                  | 2018              | 2191              | ps   |

|              | 16 mA (1)         | t <sub>OP</sub>  | 962                                      | 1679                  | 1762                  | 1873              | 2027              | ps   |

|              |                   | t <sub>DIP</sub> | 984                                      | 1745                  | 1832                  | 1947              | 2117              | ps   |

| 1.8 V        | 2 mA              | t <sub>OP</sub>  | 1093                                     | 2904                  | 3048                  | 3241              | 3472              | ps   |

|              |                   | t <sub>DIP</sub> | 1115                                     | 2970                  | 3118                  | 3315              | 3562              | ps   |

|              | 4 mA              | t <sub>OP</sub>  | 1098                                     | 2248                  | 2359                  | 2509              | 2698              | ps   |

|              |                   | t <sub>DIP</sub> | 1120                                     | 2314                  | 2429                  | 2583              | 2788              | ps   |

|              | 6 mA              | t <sub>OP</sub>  | 1022                                     | 2024                  | 2124                  | 2258              | 2434              | ps   |

|              |                   | t <sub>DIP</sub> | 1044                                     | 2090                  | 2194                  | 2332              | 2524              | ps   |

|              | 8 mA              | t <sub>OP</sub>  | 1024                                     | 1947                  | 2043                  | 2172              | 2343              | ps   |

|              |                   | t <sub>DIP</sub> | 1046                                     | 2013                  | 2113                  | 2246              | 2433              | ps   |

|              | 10 mA             | t <sub>OP</sub>  | 978                                      | 1882                  | 1975                  | 2100              | 2266              | ps   |

|              |                   | t <sub>DIP</sub> | 1000                                     | 1948                  | 2045                  | 2174              | 2356              | ps   |

|              | 12 mA (1)         | t <sub>OP</sub>  | 979                                      | 1833                  | 1923                  | 2045              | 2209              | ps   |

|              |                   | t <sub>DIP</sub> | 1001                                     | 1899                  | 1993                  | 2119              | 2299              | ps   |

| 1.5 V        | 2 mA              | t <sub>OP</sub>  | 1073                                     | 2505                  | 2629                  | 2795              | 3002              | ps   |

|              |                   | t <sub>DIP</sub> | 1095                                     | 2571                  | 2699                  | 2869              | 3092              | ps   |

|              | 4 mA              | t <sub>OP</sub>  | 1009                                     | 2023                  | 2123                  | 2257              | 2433              | ps   |

|              |                   | t <sub>DIP</sub> | 1031                                     | 2089                  | 2193                  | 2331              | 2523              | ps   |

|              | 6 mA              | t <sub>OP</sub>  | 1012                                     | 1923                  | 2018                  | 2146              | 2315              | ps   |

|              |                   | t <sub>DIP</sub> | 1034                                     | 1989                  | 2088                  | 2220              | 2405              | ps   |

|              | 8 mA (1)          | t <sub>OP</sub>  | 971                                      | 1878                  | 1970                  | 2095              | 2262              | ps   |

|              |                   | t <sub>DIP</sub> | 993                                      | 1944                  | 2040                  | 2169              | 2352              | ps   |

| Table 4–90. Stratix II GX Maximum Input Clock Rate for Dedicated Clock Pins (Part 2 of 2) |                |                |                |      |  |

|-------------------------------------------------------------------------------------------|----------------|----------------|----------------|------|--|

| I/O Standard                                                                              | -3 Speed Grade | -4 Speed Grade | -5 Speed Grade | Unit |  |

| 1.8-V HSTL CLass I                                                                        | 500            | 500            | 500            | MHz  |  |

| PCI                                                                                       | 500            | 500            | 400            | MHz  |  |

| PCI-X                                                                                     | 500            | 500            | 400            | MHz  |  |

| Differential SSTL-2<br>Class I                                                            | 500            | 500            | 500            | MHz  |  |

| Differential SSTL-2<br>Class II                                                           | 500            | 500            | 500            | MHz  |  |

| Differential SSTL-18<br>Class I                                                           | 500            | 500            | 500            | MHz  |  |

| Differential SSTL-18<br>Class II                                                          | 500            | 500            | 500            | MHz  |  |

| 1.8-V differential<br>HSTL Class I                                                        | 500            | 500            | 500            | MHz  |  |

| 1.8-V differential<br>HSTL Class II                                                       | 500            | 500            | 500            | MHz  |  |

| 1.5-V differential<br>HSTL Class I                                                        | 500            | 500            | 500            | MHz  |  |

| 1.5-V differential<br>HSTL Class I I                                                      | 500            | 500            | 500            | MHz  |  |

| HyperTransport (1)                                                                        | 717            | 717            | 640            | MHz  |  |

|                                                                                           | 450            | 450            | 400            | MHz  |  |

| LVPECL (1), (2)                                                                           | 717            | 717            | 640            | MHz  |  |

| Ī                                                                                         | 450            | 450            | 400            | MHz  |  |

| LVDS (1)                                                                                  | 717            | 717            | 640            | MHz  |  |

| Ī                                                                                         | 450            | 450            | 400            | MHz  |  |

$<sup>(1) \</sup>quad \text{The first set of numbers refers to the HIO dedicated clock pins. The second set of numbers refers to the VIO}$ dedicated clock pins.

(2) LVPECL is only supported on column clock pins.

| Table 4–91. Stratix II GX Maximum Output Clock Rate for Column Pins (Part 2 of 3) |                |                |                |                |      |  |

|-----------------------------------------------------------------------------------|----------------|----------------|----------------|----------------|------|--|

| I/O Standard                                                                      | Drive Strength | -3 Speed Grade | -4 Speed Grade | -5 Speed Grade | Unit |  |

| SSTL-18 Class I                                                                   | 4 mA           | 200            | 150            | 150            | MHz  |  |

|                                                                                   | 6 mA           | 350            | 250            | 200            | MHz  |  |

|                                                                                   | 8 mA           | 450            | 300            | 300            | MHz  |  |

|                                                                                   | 10 mA          | 500            | 400            | 400            | MHz  |  |

|                                                                                   | 12 mA (1)      | 700            | 550            | 400            | MHz  |  |

| SSTL-18 Class II                                                                  | 8 mA           | 200            | 200            | 150            | MHz  |  |

|                                                                                   | 16 mA          | 400            | 350            | 350            | MHz  |  |

|                                                                                   | 18 mA          | 450            | 400            | 400            | MHz  |  |

|                                                                                   | 20 mA (1)      | 550            | 500            | 450            | MHz  |  |

| 1.8-V HSTL                                                                        | 4 mA           | 300            | 300            | 300            | MHz  |  |

| Class I                                                                           | 6 mA           | 500            | 450            | 450            | MHz  |  |

|                                                                                   | 8 mA           | 650            | 600            | 600            | MHz  |  |

|                                                                                   | 10 mA          | 700            | 650            | 600            | MHz  |  |

|                                                                                   | 12 mA (1)      | 700            | 700            | 650            | MHz  |  |

| 1.8-V HSTL                                                                        | 16 mA          | 500            | 500            | 450            | MHz  |  |

| Class II                                                                          | 18 mA          | 550            | 500            | 500            | MHz  |  |

|                                                                                   | 20 mA (1)      | 650            | 550            | 550            | MHz  |  |

| 1.5-V HSTL                                                                        | 4 mA           | 350            | 300            | 300            | MHz  |  |

| Class I                                                                           | 6 mA           | 500            | 500            | 450            | MHz  |  |

|                                                                                   | 8 mA           | 700            | 650            | 600            | MHz  |  |

|                                                                                   | 10 mA          | 700            | 700            | 650            | MHz  |  |

|                                                                                   | 12 mA (1)      | 700            | 700            | 700            | MHz  |  |

| 1.5-V HSTL                                                                        | 16 mA          | 600            | 600            | 550            | MHz  |  |

| Class II                                                                          | 18 mA          | 650            | 600            | 600            | MHz  |  |

|                                                                                   | 20 mA (1)      | 700            | 650            | 600            | MHz  |  |

| PCI                                                                               | -              | 1000           | 790            | 670            | MHz  |  |

| PCI-X                                                                             | -              | 1000           | 790            | 670            | MHz  |  |

| Differential                                                                      | 8 mA           | 400            | 300            | 300            | MHz  |  |

| SSTL-2 Class I                                                                    | 12 mA          | 400            | 400            | 350            | MHz  |  |

| Differential                                                                      | 16 mA          | 350            | 350            | 300            | MHz  |  |

| SSTL-2 Class II                                                                   | 20 mA          | 400            | 350            | 350            | MHz  |  |

|                                                                                   | 24 mA          | 400            | 400            | 350            | MHz  |  |

| I/O Standard                    | <b>Drive Strength</b> | -3 Speed Grade | -4 Speed Grade | -5 Speed Grade | Unit |

|---------------------------------|-----------------------|----------------|----------------|----------------|------|

| Differential                    | 8 mA                  | 400            | 300            | 300            | MHz  |

| SSTL-2 Class I                  | 12 mA                 | 400            | 400            | 350            | MHz  |

| Differential<br>SSTL-2 Class II | 16 mA (1)             | 350            | 350            | 300            | MHz  |

| Differential                    | 4 mA                  | 200            | 150            | 150            | MHz  |

| SSTL-18 Class I                 | 6 mA                  | 350            | 250            | 200            | MHz  |

|                                 | 8 mA                  | 450            | 300            | 300            | MHz  |

|                                 | 10 mA (1)             | 500            | 400            | 400            | MHz  |

| LVDS                            | -                     | 717            | 717            | 640            | MHz  |

| HyperTransport                  | -                     | 717            | 717            | 640            | MHz  |

<sup>(1)</sup> This is the default setting in Quartus II software.

Table 4–93 shows the maximum output clock toggle rate for Stratix II GX device dedicated clock pins.

| Table 4–93. Stratix II GX Maximum Output Clock Rate for Dedicated Clock Pins (Part 1 of 4) |                |                   |                   |                   |      |

|--------------------------------------------------------------------------------------------|----------------|-------------------|-------------------|-------------------|------|

| I/O Standard                                                                               | Drive Strength | -3 Speed<br>Grade | -4 Speed<br>Grade | -5 Speed<br>Grade | Unit |

| LVTTL                                                                                      | 4 mA           | 270               | 225               | 210               | MHz  |

|                                                                                            | 8 mA           | 435               | 355               | 325               | MHz  |

|                                                                                            | 12 mA          | 580               | 475               | 420               | MHz  |

|                                                                                            | 16 mA          | 720               | 594               | 520               | MHz  |

|                                                                                            | 20 mA          | 875               | 700               | 610               | MHz  |

|                                                                                            | 24 mA (1)      | 1030              | 794               | 670               | MHz  |

| LVCMOS                                                                                     | 4 mA           | 290               | 250               | 230               | MHz  |

|                                                                                            | 8 mA           | 565               | 480               | 440               | MHz  |

|                                                                                            | 12 mA          | 790               | 710               | 670               | MHz  |

|                                                                                            | 16 mA          | 1020              | 925               | 875               | MHz  |

|                                                                                            | 20 mA          | 1066              | 985               | 935               | MHz  |

|                                                                                            | 24 mA (1)      | 1100              | 1040              | 1000              | MHz  |

Tables 4–98 through 4–105 show the maximum DCD in absolution derivation for different I/O standards on Stratix II GX devices. Examples are also provided that show how to calculate DCD as a percentage.

| Table 4–98. Maximum DCD for Non-DDIO Output on Row I/O Pins |                                      |                   |      |  |  |

|-------------------------------------------------------------|--------------------------------------|-------------------|------|--|--|

| Day I/O Output Standard                                     | Maximum DCD (ps) for Non-DDIO Output |                   |      |  |  |

| Row I/O Output Standard                                     | -3 Devices                           | -4 and -5 Devices | Unit |  |  |

| 3.3-V LVTTTL                                                | 245                                  | 275               | ps   |  |  |

| 3.3-V LVCMOS                                                | 125                                  | 155               | ps   |  |  |

| 2.5 V                                                       | 105                                  | 135               | ps   |  |  |

| 1.8 V                                                       | 180                                  | 180               | ps   |  |  |

| 1.5-V LVCMOS                                                | 165                                  | 195               | ps   |  |  |

| SSTL-2 Class I                                              | 115                                  | 145               | ps   |  |  |

| SSTL-2 Class II                                             | 95                                   | 125               | ps   |  |  |

| SSTL-18 Class I                                             | 55                                   | 85                | ps   |  |  |

| 1.8-V HSTL Class I                                          | 80                                   | 100               | ps   |  |  |

| 1.5-V HSTL Class I                                          | 85                                   | 115               | ps   |  |  |

| LVDS                                                        | 55                                   | 80                | ps   |  |  |

Here is an example for calculating the DCD as a percentage for a non-DDIO output on a row I/O on a -3 device:

If the non-DDIO output I/O standard is SSTL-2 Class II, the maximum DCD is 95 ps (see Table 4–99). If the clock frequency is 267 MHz, the clock period T is:

$$T = 1/f = 1/267 \text{ MHz} = 3.745 \text{ ns} = 3,745 \text{ ps}$$

To calculate the DCD as a percentage:

$$(T/2 - DCD) / T = (3,745 ps/2 - 95 ps) / 3,745 ps = 47.5\%$$

(for low boundary)

$$(T/2 + DCD) / T = (3,745 ps/2 + 95 ps) / 3,745 ps = 52.5\%$$

(for high boundary)

Table 4–104. Maximum DCD for DDIO Output on Row I/O Pins With PLL in the Clock Path

| Maximum DCD (ps) for<br>Row DDIO Output I/O | Stratix II GX Devices (PLL Output Feeding DDIO) |                  |    |

|---------------------------------------------|-------------------------------------------------|------------------|----|

| Standard                                    | -3 Device                                       | -4 and -5 Device |    |

| 3.3-V LVTTL                                 | 110                                             | 105              | ps |

| 3.3-V LVCMOS                                | 65                                              | 75               | ps |

| 2.5V                                        | 75                                              | 90               | ps |

| 1.8V                                        | 85                                              | 100              | ps |

| 1.5-V LVCMOS                                | 105                                             | 100              | ps |

| SSTL-2 Class I                              | 65                                              | 75               | ps |

| SSTL-2 Class II                             | 60                                              | 70               | ps |

| SSTL-18 Class I                             | 50                                              | 65               | ps |

| 1.8-V HSTL Class I                          | 50                                              | 70               | ps |

| 1.5-V HSTL Class I                          | 55                                              | 70               | ps |

| LVDS                                        | 180                                             | 180              | ps |

Table 4–105. Maximum DCD for DDIO Output on Column I/O Pins With PLL in the Clock Path  $\,$  (Part 1 of 2)

| Maximum DCD (ps) for<br>Column DDIO Output I/O | Stratix II GX Devices (PLL Output Feeding DDIO) |                  |    |  |

|------------------------------------------------|-------------------------------------------------|------------------|----|--|

| Standard                                       | -3 Device                                       | -4 and -5 Device |    |  |

| 3.3-V LVTTL                                    | 145                                             | 160              | ps |  |

| 3.3-V LVCMOS                                   | 100                                             | 110              | ps |  |

| 2.5V                                           | 85                                              | 95               | ps |  |

| 1.8V                                           | 85                                              | 100              | ps |  |

| 1.5-V LVCMOS                                   | 140                                             | 155              | ps |  |

| SSTL-2 Class I                                 | 65                                              | 75               | ps |  |

| SSTL-2 Class II                                | 60                                              | 70               | ps |  |

| SSTL-18 Class I                                | 50                                              | 65               | ps |  |

| SSTL-18 Class II                               | 70                                              | 80               | ps |  |

| 1.8-V HSTL Class I                             | 60                                              | 70               | ps |  |

| 1.8-V HSTL Class II                            | 60                                              | 70               | ps |  |

| 1.5-V HSTL Class I                             | 55                                              | 70               | ps |  |

| 1.5-V HSTL Class II                            | 85                                              | 100              | ps |  |