Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 4548                                                        |

| Number of Logic Elements/Cells | 90960                                                       |

| Total RAM Bits                 | 4520448                                                     |

| Number of I/O                  | 650                                                         |

| Number of Gates                | -                                                           |

| Voltage - Supply               | 1.15V ~ 1.25V                                               |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 1508-BBGA, FCBGA                                            |

| Supplier Device Package        | 1508-FBGA, FC (40x40)                                       |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2sgx90ff1508c4 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

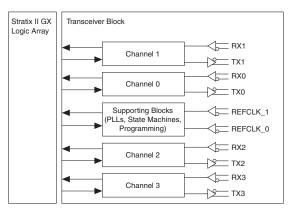

Figure 2-2. Elements of the Transceiver Block

Each Stratix II GX transceiver channel consists of a transmitter and receiver. The transceivers are grouped in four and share PLL resources. Each transmitter has access to one of two PLLs. The transmitter contains the following:

- Transmitter phase compensation first-in first-out (FIFO) buffer

- Byte serializer (optional)

- 8B/10B encoder (optional)

- Serializer (parallel-to-serial converter)

- Transmitter differential output buffer

The receiver contains the following:

- Receiver differential input buffer

- Receiver lock detector and run length checker

- Clock recovery unit (CRU)

- Deserializer

- Pattern detector

- Word aligner

- Lane deskew

- Rate matcher (optional)

- 8B/10B decoder (optional)

- Byte deserializer (optional)

- Byte ordering

- Receiver phase compensation FIFO buffer

Designers can preset Stratix II GX transceiver functions using the Quartus  $^{\otimes}$  II software. In addition, pre-emphasis, equalization, and differential output voltage ( $V_{OD}$ ) are dynamically programmable. Each Stratix II GX transceiver channel supports various loopback modes and is

#### Transmit State Machine

The transmit state machine operates in either PCI Express mode, XAUI mode, or GIGE mode, depending on the protocol used. The state machine is not utilized for certain protocols, such as SONET.

#### GIGE Mode

In GIGE mode, the transmit state machine converts all idle ordered sets (/K28.5/, /Dx.y/) to either /I1/ or /I2/ ordered sets. /I1/ consists of a negative-ending disparity /K28.5/ (denoted by /K28.5/-) followed by a neutral /D5.6/. /I2/ consists of a positive-ending disparity /K28.5/ (denoted by /K28.5/+) and a negative-ending disparity /D16.2/ (denoted by /D16.2/-). The transmit state machines do not convert any of the ordered sets to match /C1/ or /C2/, which are the configuration ordered sets. (/C1/ and /C2/ are defined by [/K28.5/, /D21.5/] and [/K28.5/, /D2.2/], respectively). Both the /I1/ and /I2/ ordered sets guarantee a negative-ending disparity after each ordered set.

#### XAUI Mode

The transmit state machine translates the XAUI XGMII code group to the XAUI PCS code group. Table 2–5 shows the code conversion.

| Table 2–5. | Code Conversion                           |                                        |                         |

|------------|-------------------------------------------|----------------------------------------|-------------------------|

| XGMII TXC  | XGMII TXD                                 | PCS Code-Group                         | Description             |

| 0          | 00 through FF                             | Dxx.y                                  | Normal data             |

| 1          | 07                                        | K28.0 or K28.3 or<br>K28.5             | Idle in    <b>I</b>     |

| 1          | 07                                        | K28.5                                  | Idle in   T             |

| 1          | 9C                                        | K28.4                                  | Sequence                |

| 1          | FB                                        | K27.7                                  | Start                   |

| 1          | FD                                        | K29.7                                  | Terminate               |

| 1          | FE                                        | K30.7                                  | Error                   |

| 1          | See IEEE 802.3<br>reserved code<br>groups | See IEEE 802.3<br>reserved code groups | Reserved code groups    |

| 1          | Other value                               | K30.7                                  | Invalid XGMII character |

The XAUI PCS idle code groups, /K28.0/ (/R/) and /K28.5/ (/K/), are automatically randomized based on a PRBS7 pattern with an  $x^7 + x^6 + 1$  polynomial. The /K28.3/ (/A/) code group is automatically generated between 16 and 31 idle code groups. The idle randomization on the /A/, /K/, and /R/ code groups is done automatically by the transmit state machine.

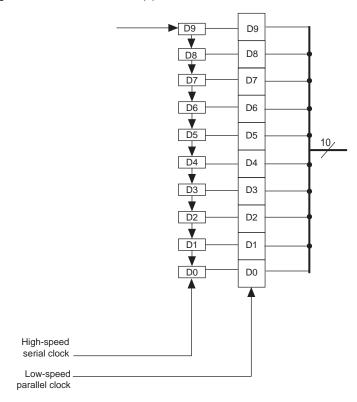

Figure 2–17. Deserializer Note (1)

Note to Figure 2-17:

1) This is a 10-bit deserializer. The deserializer can also convert 8, 16, or 20 bits of data.

## Word Aligner

The deserializer block creates 8-, 10-, 16-, or 20-bit parallel data. The deserializer ignores protocol symbol boundaries when converting this data. Therefore, the boundaries of the transferred words are arbitrary. The word aligner aligns the incoming data based on specific byte or word boundaries. The word alignment module is clocked by the local receiver recovered clock during normal operation. All the data and programmed patterns are defined as big-endian (most significant word followed by least significant word). Most-significant-bit-first protocols such as SONET/SDH should reverse the bit order of word align patterns programmed.

Figure 2–27 show the Stratix II GX block in reverse serial pre-CDR loopback mode.

Transmitter Digital Logic **Analog Receiver and** Transmitter Logic Generator Generato Byte Reverse Array Pre-CDR Loopback ncrementa Verify RX Phase Clock Word De-Compen-Recovery Ordering Aligner serialize Unit FIFO **Receiver Digital Logic**

Figure 2–27. Stratix II GX Block in Reverse Serial Pre-CDR Loopback Mode

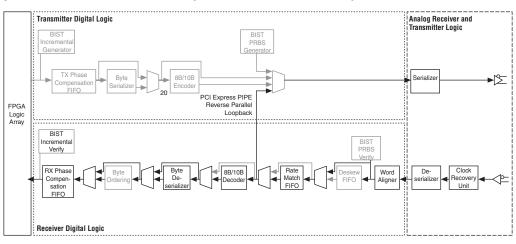

## PCI Express PIPE Reverse Parallel Loopback

This loopback mode, available only in PIPE mode, can be dynamically enabled by the tx\_detectrxloopback port of the PIPE interface. Figure 2–28 shows the datapath for this mode.

Figure 2–28. Stratix II GX Block in PCI Express PIPE Reverse Parallel Loopback Mode

Figure 2-33. Direct Link Connection Direct link interconnect from Direct link interconnect from left LAB, TriMatrix™ memory right LAB, TriMatrix memory block, DSP block, or block, DSP block, or IOE output input/output element (IOE) **ALMs** Direct link Direct link interconnect < interconnect to left to right Local Interconnect LAB

Figure 2–33 shows the direct link connection.

## **LAB Control Signals**

Each LAB contains dedicated logic for driving control signals to its ALMs. The control signals include three clocks, three clock enables, two asynchronous clears, synchronous clear, asynchronous preset/load, and synchronous load control signals, providing a maximum of 11 control signals at a time. Although synchronous load and clear signals are generally used when implementing counters, they can also be used with other functions.

Each LAB can use three clocks and three clock enable signals. However, there can only be up to two unique clocks per LAB, as shown in the LAB control signal generation circuit in Figure 2–34. Each LAB's clock and clock enable signals are linked. For example, any ALM in a particular LAB using the labclk1 signal also uses labclkena1. If the LAB uses both the rising and falling edges of a clock, it also uses two LAB-wide clock signals. De-asserting the clock enable signal turns off the corresponding LAB-wide clock. Each LAB can use two asynchronous clear signals and an asynchronous load/preset signal. The asynchronous

One ALM contains two programmable registers. Each register has data, clock, clock enable, synchronous and asynchronous clear, asynchronous load data, and synchronous and asynchronous load/preset inputs.

Global signals, general-purpose I/O pins, or any internal logic can drive the register's clock and clear control signals. Either general-purpose I/O pins or internal logic can drive the clock enable, preset, asynchronous load, and asynchronous load data. The asynchronous load data input comes from the datae or dataf input of the ALM, which are the same inputs that can be used for register packing. For combinational functions, the register is bypassed and the output of the LUT drives directly to the outputs of the ALM.

Each ALM has two sets of outputs that drive the local, row, and column routing resources. The LUT, adder, or register output can drive these output drivers independently (see Figure 2–36). For each set of output drivers, two ALM outputs can drive column, row, or direct link routing connections, and one of these ALM outputs can also drive local interconnect resources. This allows the LUT or adder to drive one output while the register drives another output. This feature, called register packing, improves device utilization because the device can use the register and the combinational logic for unrelated functions. Another special packing mode allows the register output to feed back into the LUT of the same ALM so that the register is packed with its own fan-out LUT. This feature provides another mechanism for improved fitting. The ALM can also drive out registered and unregistered versions of the LUT or adder output.

See the *Stratix II Performance and Logic Efficiency Analysis White Paper* for more information on the efficiencies of the Stratix II GX ALM and comparisons with previous architectures.

## **ALM Operating Modes**

The Stratix II GX ALM can operate in one of the following modes:

- Normal mode

- Extended LUT mode

- Arithmetic mode

- Shared arithmetic mode

Each mode uses ALM resources differently. Each mode has 11 available inputs to the ALM (see Figure 2–35)—the eight data inputs from the LAB local interconnect; carry-in from the previous ALM or LAB; the shared arithmetic chain connection from the previous ALM or LAB; and the register chain connection—are directed to different destinations to implement the desired logic function. LAB-wide signals provide clock,

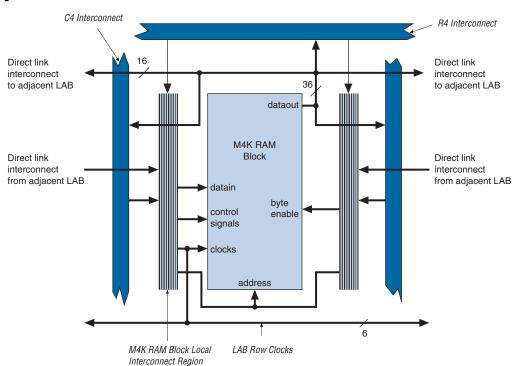

The RAM blocks in Stratix II GX devices have local interconnects to allow ALMs and interconnects to drive into RAM blocks. The M512 RAM block local interconnect is driven by the R4, C4, and direct link interconnects from adjacent LABs. The M512 RAM blocks can communicate with LABs on either the left or right side through these row interconnects or with LAB columns on the left or right side with the column interconnects. The M512 RAM block has up to 16 direct link input connections from the left adjacent LABs and another 16 from the right adjacent LAB. M512 RAM outputs can also connect to left and right LABs through direct link interconnect. The M512 RAM block has equal opportunity for access and performance to and from LABs on either its left or right side. Figure 2–50 shows the M512 RAM block to logic array interface.

Figure 2-50. M512 RAM Block LAB Row Interface

Similar to all RAM blocks, M-RAM blocks can have different clocks on their inputs and outputs. Either of the two clocks feeding the block can clock M-RAM block registers (renwe, address, byte enable, datain, and output registers). The output register can be bypassed. The six labclk signals or local interconnect can drive the control signals for the A and B ports of the M-RAM block. ALMs can also control the clock\_a, clock\_b, renwe\_a, renwe\_b, clr\_a, clr\_b, clocken\_a, and clocken\_b signals, as shown in Figure 2–53.

Dedicated Row LAB Clocks Local Local Interconnect Interconnect clocken a clock\_b renwe a aclr b Local Local Interconnect Interconnect clocken b clock a aclr\_a renwe b

Figure 2-53. M-RAM Block Control Signals

The R4, R24, C4, and direct link interconnects from adjacent LABs on either the right or left side drive the M-RAM block local interconnect. Up to 16 direct link input connections to the M-RAM block are possible from the left adjacent LABs and another 16 possible from the right adjacent LAB. M-RAM block outputs can also connect to left and right LABs through direct link interconnect. Figure 2–54 shows an example floorplan for the EP2SGX130 device and the location of the M-RAM interfaces. Figures 2–55 and 2–56 show the interface between the M-RAM block and the logic array.

Table 2–21 shows the number of DSP blocks in each Stratix II GX device. DSP block multipliers can optionally feed an adder/subtractor or accumulator in the block, depending on the configuration, which makes routing to ALMs easier, saves ALM routing resources, and increases performance because all connections and blocks are in the DSP block.

| Table 2–21. DSP Blocks in Stratix II GX Devices Note (1) |            |                              |     |    |  |  |  |  |  |  |  |

|----------------------------------------------------------|------------|------------------------------|-----|----|--|--|--|--|--|--|--|

| Device                                                   | DSP Blocks | Total 36 × 36<br>Multipliers |     |    |  |  |  |  |  |  |  |

| EP2SGX30                                                 | 16         | 128                          | 64  | 16 |  |  |  |  |  |  |  |

| EP2SGX60                                                 | 36         | 288                          | 144 | 36 |  |  |  |  |  |  |  |

| EP2SGX90                                                 | 48         | 384                          | 192 | 48 |  |  |  |  |  |  |  |

| EP2SGX130                                                | 63         | 504                          | 252 | 63 |  |  |  |  |  |  |  |

*Note to Table 2–21:*

Additionally, the DSP block input registers can efficiently implement shift registers for FIR filter applications, and DSP blocks support Q1.15 format rounding and saturation. Figure 2–58 shows the top-level diagram of the DSP block configured for  $18 \times 18$ -bit multiplier mode.

This list only shows functions that can fit into a single DSP block. Multiple DSP blocks can support larger multiplication functions.

| Table 2–27. Global and Region<br>(Part 2 of 3)              | al Clou  | ck Con   | nectio   | ns fron  | n Left   | Side C   | lock P   | ins and  | d Fast   | PLL O    | utputs   |          |

|-------------------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Left Side Global and Regional<br>Clock Network Connectivity | CLKO     | CLK1     | CLK2     | CLK3     | RCLKO    | RCLK1    | RCLK2    | RCLK3    | RCLK4    | RCLK5    | RCLK6    | RCLK7    |

| Drivers from internal logic                                 |          |          |          |          |          |          |          |          |          |          |          |          |

| GCLKDRV0                                                    | <b>✓</b> | <b>\</b> |          |          |          |          |          |          |          |          |          |          |

| GCLKDRV1                                                    | <b>\</b> | <b>✓</b> |          |          |          |          |          |          |          |          |          |          |

| GCLKDRV2                                                    |          |          | <b>~</b> | <b>✓</b> |          |          |          |          |          |          |          |          |

| GCLKDRV3                                                    |          |          | <b>✓</b> | <b>✓</b> |          |          |          |          |          |          |          |          |

| RCLKDRV0                                                    |          |          |          |          | <b>~</b> |          |          |          | <b>~</b> |          |          |          |

| RCLKDRV1                                                    |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| RCLKDRV2                                                    |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| RCLKDRV3                                                    |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| RCLKDRV4                                                    |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| RCLKDRV5                                                    |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| RCLKDRV6                                                    |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| RCLKDRV7                                                    |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| PLL 1 outputs                                               |          |          | 1        |          |          |          |          |          |          |          |          |          |

| c0                                                          | <b>✓</b> | <b>✓</b> |          |          | <b>~</b> |          | <b>✓</b> |          | <b>~</b> |          | <b>~</b> |          |

| c1                                                          | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |

| c2                                                          |          |          | <b>✓</b> | <b>✓</b> | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          |

| c3                                                          |          |          | <b>✓</b> | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |

| PLL 2 outputs                                               | I        |          | 1        | I        | I        | I        |          | I        | ı        | I        | I        |          |

| c0                                                          | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |

| c1                                                          | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          |

| c2                                                          |          |          | ~        | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |

| с3                                                          |          |          | <b>✓</b> | <b>✓</b> | <b>~</b> |          | <b>✓</b> |          | <b>~</b> |          | <b>~</b> |          |

| PLL 7 outputs                                               |          |          |          |          |          |          |          |          |          |          |          |          |

| c0                                                          |          |          | <b>✓</b> | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          |          |          |          |

| c1                                                          |          |          | <b>✓</b> | <b>✓</b> | <b>✓</b> |          | >        |          |          |          |          |          |

| c2                                                          | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          | <b>✓</b> |          |          |          |          |

| с3                                                          | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          | <b>✓</b> |          |          |          |          |          |

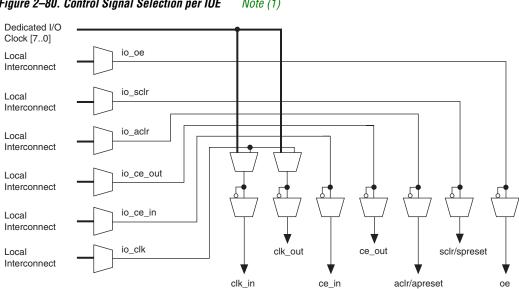

Figure 2-80. Control Signal Selection per IOE Note (1)

#### Note to Figure 2-80:

Control signals ce\_in, ce\_out, aclr/apreset, sclr/spreset, and oe can be global signals even though their control selection multiplexers are not directly fed by the ioe clk [7..0] signals. The ioe clk signals can drive the I/O local interconnect, which then drives the control selection multiplexers.

> In normal bidirectional operation, you can use the input register for input data requiring fast setup times. The input register can have its own clock input and clock enable separate from the OE and output registers. The output register can be used for data requiring fast clock-to-output performance. You can use the OE register for fast clock-to-output enable timing. The OE and output register share the same clock source and the same clock enable source from local interconnect in the associated LAB, dedicated I/O clocks, and the column and row interconnects. Figure 2-81 shows the IOE in bidirectional configuration.

| Table 2–42. Document Revision History (Part 2 of 6) |                                                                                                                                                     |                                                                                                                                                          |  |  |  |  |  |  |  |  |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Date and<br>Document<br>Version                     | Changes Made                                                                                                                                        | Summary of Changes                                                                                                                                       |  |  |  |  |  |  |  |  |

| February 2007<br>v2.0                               | Added Chapter 02 "Stratix II GX Transceivers" to the beginning of Chapter 03 "Stratix II GX Architecture".  • Changed chapter number to Chapter 02. | Combined Chapter 02 "Stratix II GX<br>Transceivers" and Chapter 03<br>"Stratix II GX Architecture" in the new<br>Chapter 02 "Stratix II GX Architecture" |  |  |  |  |  |  |  |  |

|                                                     | Added the "Document Revision History" section to this chapter.                                                                                      |                                                                                                                                                          |  |  |  |  |  |  |  |  |

|                                                     | Moved the "Stratix II GX Transceiver Clocking" section to after the "Receiver Path" section.                                                        |                                                                                                                                                          |  |  |  |  |  |  |  |  |

generated by the Quartus II software. JRunner is targeted for embedded JTAG configuration. The source code is developed for the Windows NT operating system (OS), but can be customized to run on other platforms.

For more information on the JRunner software driver, refer to the *AN 414: An Embedded Solution for PLD JTAG Configuration* and the source files on the Altera web site (www.altera.com).

## **Programming Serial Configuration Devices with SRunner**

A serial configuration device can be programmed in-system by an external microprocessor using SRunner. SRunner is a software driver developed for embedded serial configuration device programming that can be easily customized to fit into different embedded systems. SRunner reads a Raw Programming Data file (.rpd) and writes to serial configuration devices. The serial configuration device programming time using SRunner is comparable to the programming time when using the Quartus II software.

For more information about SRunner, refer to the *AN 418 SRunner: An Embedded Solution for Serial Configuration Device Programming* and the source code on the Altera web site.

For more information on programming serial configuration devices, refer to the *Serial Configuration Devices* (EPCS1, EPCS4, EPCS64, and EPCS128) Data Sheet in the Configuration Handbook.

## **Configuring Stratix II FPGAs with the MicroBlaster Driver**

The MicroBlaster software driver supports an RBF programming input file and is ideal for embedded FPP or PS configuration. The source code is developed for the Windows NT operating system, although it can be customized to run on other operating systems.

For more information on the MicroBlaster software driver, refer to the Configuring the MicroBlaster Fast Passive Parallel Software Driver White Paper or the Configuring the MicroBlaster Passive Serial Software Driver White Paper on the Altera web site.

## **PLL Reconfiguration**

The phase-locked loops (PLLs) in the Stratix II GX device family support reconfiguration of their multiply, divide, VCO-phase selection, and bandwidth selection settings without reconfiguring the entire device. You can use either serial data from the logic array or regular I/O pins to program the PLL's counter settings in a serial chain. This option provides

| Symbol/<br>Description         | Conditions                                                                                                                                                                                                              | -3 Speed Commercial Speed Grade |       | -4 Speed<br>Commercial and<br>Industrial Speed<br>Grade |     |       | -5 Speed<br>Commercial Speed<br>Grade |     | Unit |     |    |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-------|---------------------------------------------------------|-----|-------|---------------------------------------|-----|------|-----|----|

|                                |                                                                                                                                                                                                                         | Min                             | Тур   | Max                                                     | Min | Тур   | Max                                   | Min | Тур  | Max |    |

| Sinusoidal Jitter<br>Tolerance | Jitter Frequency = 22.1 KHz Data Rate = 614.4 Mbps, 1.2288 Gbps, 2.4576 Gbps REFCLK = 61.44 MHz for 614.4 Mbps REFCLK = 122.88 MHz for 1.2288 Gbps and 2.4576 Gbps Pattern = CJPAT Equalizer Setting = 6 DC Gain = 0 dB |                                 | > 8.5 |                                                         |     | > 8.5 |                                       |     | N/A  |     | UI |

| (peak-to-peak) (6)             | Jitter Frequency = 1.875MHz Data Rate = 614.4 Mbps, 1.2288 Gbps, 2.4576 Gbps REFCLK = 61.44 MHz for 614.4 Mbps REFCLK = 122.88 MHz for 1.2288 Gbps and 2.4576 Gbps Pattern = CJPAT Equalizer Setting = 6 DC Gain = 0 dB |                                 | > 0.1 |                                                         |     | > 0.1 |                                       |     | N/A  |     | UI |

# Power Consumption

Altera offers two ways to calculate power for a design: the Excel-based PowerPlay early power estimator power calculator and the Quartus<sup>®</sup> II PowerPlay power analyzer feature.

The interactive Excel-based PowerPlay early power estimator is typically used prior to designing the FPGA in order to get an estimate of device power. The Quartus II PowerPlay power analyzer provides better quality estimates based on the specifics of the design after place-and-route is complete. The power analyzer can apply a combination of user-entered, simulation-derived and estimated signal activities which, combined with detailed circuit models, can yield very accurate power estimates.

In both cases, these calculations should only be used as an estimation of power, not as a specification.

For more information on PowerPlay tools, refer to the *PowerPlay Early Power Estimators* (*EPE*) and *Power Analyzer*, the *Quartus II PowerPlay Analysis and Optimization Technology*, and the *PowerPlay Power Analyzer* chapter in volume 3 of the *Quartus II Handbook*. The PowerPlay early power estimators are available on the Altera web site at **www.altera.com**.

See Table 4–23 on page 42 for typical I<sub>CC</sub> standby specifications.

## **Timing Model**

The DirectDrive technology and MultiTrack interconnect ensure predictable performance, accurate simulation, and accurate timing analysis across all Stratix II GX device densities and speed grades. This section describes and specifies the performance, internal, external, and PLL timing specifications.

All specifications are representative of worst-case supply voltage and junction temperature conditions.

## **Preliminary and Final Timing**

Timing models can have either preliminary or final status. The Quartus II software issues an informational message during the design compilation if the timing models are preliminary. Table 4–52 shows the status of the Stratix II GX device timing models.

Preliminary status means the timing model is subject to change. Initially, timing numbers are created using simulation results, process data, and other known parameters. These tests are used to make the preliminary numbers as close to the actual timing parameters as possible.

| Table 4–54. Timing Measurement Methodology for Input Pins (Part 2 of 2)       Notes (1), (2), (3), (4) |                       |                      |                |           |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------|-----------------------|----------------------|----------------|-----------|--|--|--|--|--|--|

| I/O Standard                                                                                           | Mea                   | Measurement Point    |                |           |  |  |  |  |  |  |

| I/O Standard                                                                                           | V <sub>CCIO</sub> (V) | V <sub>REF</sub> (V) | Edge Rate (ns) | VMEAS (V) |  |  |  |  |  |  |

| 1.8-V HSTL Class II                                                                                    | 1.660                 | 0.830                | 1.660          | 0.83      |  |  |  |  |  |  |

| 1.5-V HSTL Class I                                                                                     | 1.375                 | 0.688                | 1.375          | 0.6875    |  |  |  |  |  |  |

| 1.5-V HSTL Class II                                                                                    | 1.375                 | 0.688                | 1.375          | 0.6875    |  |  |  |  |  |  |

| 1.2-V HSTL with OCT                                                                                    | 1.140                 | 0.570                | 1.140          | 0.570     |  |  |  |  |  |  |

| Differential SSTL-2 Class I                                                                            | 2.325                 | 1.163                | 2.325          | 1.1625    |  |  |  |  |  |  |

| Differential SSTL-2 Class II                                                                           | 2.325                 | 1.163                | 2.325          | 1.1625    |  |  |  |  |  |  |

| Differential SSTL-18 Class I                                                                           | 1.660                 | 0.830                | 1.660          | 0.83      |  |  |  |  |  |  |

| Differential SSTL-18 Class II                                                                          | 1.660                 | 0.830                | 1.660          | 0.83      |  |  |  |  |  |  |

| 1.5-V differential HSTL Class I                                                                        | 1.375                 | 0.688                | 1.375          | 0.6875    |  |  |  |  |  |  |

| 1.5-V differential HSTL Class II                                                                       | 1.375                 | 0.688                | 1.375          | 0.6875    |  |  |  |  |  |  |

| 1.8-V differential HSTL Class I                                                                        | 1.660                 | 0.830                | 1.660          | 0.83      |  |  |  |  |  |  |

| 1.8-V differential HSTL Class II                                                                       | 1.660                 | 0.830                | 1.660          | 0.83      |  |  |  |  |  |  |

| LVDS                                                                                                   | 2.325                 |                      | 0.100          | 1.1625    |  |  |  |  |  |  |

| LVPECL                                                                                                 | 3.135                 |                      | 0.100          | 1.5675    |  |  |  |  |  |  |

#### Notes to Table 4–54:

- (1) Input buffer sees no load at buffer input.

- (2) Input measuring point at buffer input is 0.5 V<sub>CCIO</sub>.

- (3) Output measuring point is  $0.5\,\mathrm{V}_{\mathrm{CC}}$  at internal node.

- (4) Input edge rate is 1 V/ns.

(5) Less than 50-mV ripple on V<sub>CCIO</sub> and V<sub>CCPD</sub>, V<sub>CCINT</sub> = 1.15 V with less than 30-mV ripple.

- (6)  $V_{CCPD} = 2.97 \text{ V}$ , less than 50-mV ripple on  $V_{CCIO}$  and  $V_{CCPD}$ ,  $V_{CCINT} = 1.15 \text{ V}$ .

| Table 4-55                  | Table 4–55. Stratix II GX Performance Notes (Part 3 of 3) Note (1) |       |                               |               |                          |                      |                   |                      |       |  |  |  |

|-----------------------------|--------------------------------------------------------------------|-------|-------------------------------|---------------|--------------------------|----------------------|-------------------|----------------------|-------|--|--|--|

|                             |                                                                    | Re    | esources Us                   | ed            |                          | Pe                   | rformance         |                      |       |  |  |  |

| Арр                         | olications                                                         | ALUTs | TriMatrix<br>Memory<br>Blocks | DSP<br>Blocks | -3 Speed<br>Grade<br>(2) | -3<br>Speed<br>Grade | -4 Speed<br>Grade | -5<br>Speed<br>Grade | Units |  |  |  |

| TriMatrix<br>Memory         | Single port RAM<br>64K x 9 bit                                     | 0     | 1                             | 0             | 364.96                   | 347.22               | 325.73            | 271.73               | MHz   |  |  |  |

| MegaRAM<br>block<br>(cont.) | Simple<br>dual-port RAM<br>64K x 9 bit                             | 0     | 1                             | 0             | 420.16                   | 400.0                | 375.93            | 313.47               | MHz   |  |  |  |

|                             | True dual-port<br>RAM 64K x 9 bit                                  | 0     | 1                             | 0             | 359.71                   | 342.46               | 322.58            | 268.09               | MHz   |  |  |  |

| DSP<br>block                | 9 x 9-bit<br>multiplier (5)                                        | 0     | 0                             | 1             | 430.29                   | 409.16               | 385.2             | 320.1                | MHz   |  |  |  |

|                             | 18 x 18-bit<br>multiplier (5)                                      | 0     | 0                             | 1             | 410.17                   | 390.01               | 367.1             | 305.06               | MHz   |  |  |  |

|                             | 18 x 18-bit<br>multiplier (7)                                      | 0     | 0                             | 1             | 450.04                   | 428.08               | 403.22            | 335.12               | MHz   |  |  |  |

|                             | 36 x 36-bit<br>multiplier (5)                                      | 0     | 0                             | 1             | 250.0                    | 238.15               | 224.01            | 186.6                | MHz   |  |  |  |

|                             | 36 x 36-bit<br>multiplier (6)                                      | 0     | 0                             | 1             | 410.17                   | 390.01               | 367.1             | 305.06               | MHz   |  |  |  |

|                             | 18-bit, 4-tap FIR filter                                           | 0     | 0                             | 1             | 410.17                   | 390.01               | 367.1             | 305.06               | MHz   |  |  |  |

#### Notes to Table 4-55:

- (1) These design performance numbers were obtained using the Quartus II software.

- (2) This column refers to -3 speed grades for EP2SGX30, EP2SGX60, and EP2SGX90 devices.

- (3) This column refers to -3 speed grades for EP2SGX130 devices.

- (4) This application uses registered inputs and outputs.

- (5) This application uses registered multiplier input and output stages within the DSP block.

- (6) This application uses registered multiplier input, pipeline, and output stages within the DSP block.

- (7) This application uses registered multiplier inputs with outputs of the multiplier stage feeding the accumulator or subtractor within the DSP block.

Table 4–86. Stratix II GX I/O Output Delay for Column Pins (Part 3 of 7) **Fast Corner** -3 Speed -4 Speed Drive -3 Speed -5 Speed **Parameter** I/O Standard Industrial/ Unit Strength Grade (3) Grade (4) Grade Grade Commercial SSTL-2 Class I 8 mA ps t<sub>OP</sub>  $t_{\mathsf{DIP}}$ ps 12 mA (1) ps t<sub>OP</sub> ps  $t_{DIP}$ SSTL-2 Class II 16 mA  $t_{OP}$ ps  $t_{\mathsf{DIP}}$ ps 20 mA  $t_{OP}$ ps  $t_{DIP}$ ps 24 mA (1)  $t_{OP}$ ps  $t_{DIP}$ ps SSTL-18 Class I 4 mA ps  $t_{OP}$ ps  $t_{DIP}$ 6 mA  $t_{OP}$ ps  $t_{\mathsf{DIP}}$ ps 8 mA t<sub>OP</sub> ps ps  $t_{DIP}$ 10 mA  $t_{OP}$ ps  $t_{\mathsf{DIP}}$ ps 12 mA (1)  $t_{OP}$ ps  $t_{DIP}$ ps SSTL-18 Class II 8 mA  $t_{OP}$ ps ps  $t_{DIP}$

ps

ps

ps

ps

ps

ps

16 mA

18 mA

20 mA (1)

t<sub>OP</sub>

$t_{\mathsf{DIP}}$

$t_{OP}$

$t_{DIP}$

t<sub>OP</sub>

$t_{DIP}$

| Table 4–95. Stra                | Table 4–95. Stratix II GX Maximum Output Clock Rate for Row Pins (Series Termination) (Part 2 of 2) |                |                |                |      |  |  |  |  |  |  |

|---------------------------------|-----------------------------------------------------------------------------------------------------|----------------|----------------|----------------|------|--|--|--|--|--|--|

| I/O Standard                    | Drive Strength                                                                                      | -3 Speed Grade | -4 Speed Grade | -5 Speed Grade | Unit |  |  |  |  |  |  |

| SSTL-2 Class I                  | OCT_50_OHMS                                                                                         | 600            | 500            | 500            | MHz  |  |  |  |  |  |  |

| SSTL-2 Class II                 | OCT_25_OHMS                                                                                         | 600            | 550            | 500            | MHz  |  |  |  |  |  |  |

| SSTL-18 Class I                 | OCT_50_OHMS                                                                                         | 590            | 400            | 350            | MHz  |  |  |  |  |  |  |

| 1.5-V HSTL<br>Class I           | OCT_50_OHMS                                                                                         | 600            | 550            | 500            | MHz  |  |  |  |  |  |  |

| 1.8-V HSTL<br>Class I           | OCT_50_OHMS                                                                                         | 650            | 600            | 600            | MHz  |  |  |  |  |  |  |

| Differential<br>SSTL-2 Class I  | OCT_50_OHMS                                                                                         | 600            | 500            | 500            | MHz  |  |  |  |  |  |  |

| Differential<br>SSTL-2 Class II | OCT_25_OHMS                                                                                         | 600            | 550            | 500            | MHz  |  |  |  |  |  |  |

| Differential<br>SSTL-18 Class I | OCT_50_OHMS                                                                                         | 590            | 400            | 350            | MHz  |  |  |  |  |  |  |

| Differential<br>HSTL-18 Class I | OCT_50_OHMS                                                                                         | 650            | 600            | 600            | MHz  |  |  |  |  |  |  |

| Differential<br>HSTL-15 Class I | OCT_50_OHMS                                                                                         | 600            | 550            | 500            |      |  |  |  |  |  |  |

Table 4–96 shows the maximum output clock toggle rate for Stratix II GX device series-terminated dedicated clock pins.

| Table 4–96. Stra<br>1 of 2) | Table 4–96. Stratix II GX Maximum Output Clock Rate for Dedicated Clock Pins (Series Termination) (Part<br>1 of 2) |                |                |                |      |  |  |  |  |  |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------|----------------|----------------|----------------|------|--|--|--|--|--|

| I/O Standard                | Drive Strength                                                                                                     | -3 Speed Grade | -4 Speed Grade | -5 Speed Grade | Unit |  |  |  |  |  |

| LVTTL                       | OCT_25_OHMS                                                                                                        | 400            | 400            | 350            | MHz  |  |  |  |  |  |

|                             | OCT_50_OHMS                                                                                                        | 400            | 400            | 350            | MHz  |  |  |  |  |  |

| LVCMOS                      | OCT_25_OHMS                                                                                                        | 350            | 350            | 300            | MHz  |  |  |  |  |  |

|                             | OCT_50_OHMS                                                                                                        | 350            | 350            | 300            | MHz  |  |  |  |  |  |

| 2.5 V                       | OCT_25_OHMS                                                                                                        | 350            | 350            | 300            | MHz  |  |  |  |  |  |

|                             | OCT_50_OHMS                                                                                                        | 350            | 350            | 300            | MHz  |  |  |  |  |  |

| 1.8 V                       | OCT_25_OHMS                                                                                                        | 700            | 550            | 450            | MHz  |  |  |  |  |  |

|                             | OCT_50_OHMS                                                                                                        | 700            | 550            | 450            | MHz  |  |  |  |  |  |

| 1.5 V                       | OCT_50_OHMS                                                                                                        | 550            | 450            | 400            | MHz  |  |  |  |  |  |

| SSTL-2 Class I              | OCT_50_OHMS                                                                                                        | 600            | 500            | 500            | MHz  |  |  |  |  |  |

| SSTL-2 Class II             | OCT_25_OHMS                                                                                                        | 600            | 550            | 500            | MHz  |  |  |  |  |  |

| SSTL-18 Class I             | OCT_50_OHMS                                                                                                        | 450            | 400            | 350            | MHz  |  |  |  |  |  |

Table 4–108 shows the high-speed I/O timing specifications for -4 speed grade Stratix II GX devices.

| •                                    |                          |                                 | -4 S        |      |     |       |                       |

|--------------------------------------|--------------------------|---------------------------------|-------------|------|-----|-------|-----------------------|

| Symbol                               | C                        | Conditions                      |             |      |     |       | Unit                  |

| $f_{IN} = f_{HSDR} / W$              | W = 2 to 32 (LVDS, I     | HyperTransport                  | technology) | 16   |     | 520   | MHz                   |

|                                      | W = 1 (SERDES by         | pass, LVDS only                 | /)          | 16   |     | 500   | MHz                   |

|                                      | W = 1 (SERDES us         | ed, LVDS only)                  |             | 150  |     | 717   | MHz                   |

| f <sub>HSDR</sub> (data rate)        | J = 4 to 10 (LVDS, F     | lyperTransport t                | technology) | 150  |     | 1,040 | Mbps                  |

|                                      | J = 2 (LVDS, Hyper       | Transport techno                | ology)      | (4)  |     | 760   | Mbps                  |

|                                      | J = 1 (LVDS only)        |                                 |             | (4)  |     | 500   | Mbps                  |

| f <sub>HSDRDPA</sub> (DPA data rate) | J = 4 to 10 (LVDS, F     | lyperTransport t                | echnology)  | 150  |     | 1,040 | Mbps                  |

| TCCS                                 | All differential stand   | ards                            | -           |      | 200 | ps    |                       |

| SW                                   | All differential stand   | ards                            |             | 330  |     | -     | ps                    |

| Output jitter                        |                          |                                 |             |      |     | 190   | ps                    |

| Output t <sub>RISE</sub>             | All differential I/O sta | andards                         |             |      |     | 160   | ps                    |

| Output t <sub>FALL</sub>             | All differential I/O sta | andards                         |             |      |     | 180   | ps                    |

| t <sub>DUTY</sub>                    |                          |                                 |             | 45   | 50  | 55    | %                     |

| DPA run length                       |                          |                                 |             |      |     | 6,400 | UI                    |

| DPA jitter tolerance                 | Data channel peak-       | to-peak jitter                  |             | 0.44 |     |       | UI                    |

| DPA lock time                        |                          |                                 |             |      |     |       | Number of repetitions |

|                                      | SPI-4                    | SPI-4 0000000000 10%            |             |      |     |       |                       |

|                                      | Parallel Rapid I/O       | Parallel Rapid I/O 00001111 25% |             |      |     |       | 1                     |

|                                      |                          | 10010000                        | 50%         | 256  |     |       | 1                     |

|                                      | Miscellaneous            | 10101010                        | 100%        | 256  |     |       | 1                     |

|                                      |                          | 01010101                        |             | 256  |     |       | 1                     |

<sup>(1)</sup> When J = 4 to 10, the SERDES block is used.

<sup>(2)</sup> When J = 1 or 2, the SERDES block is bypassed.

<sup>(3)</sup> The input clock frequency and the W factor must satisfy the following fast PLL VCO specification: 150 ≤nput clock frequency × W ≤1,040.

<sup>(4)</sup> The minimum specification is dependent on the clock source (fast PLL, enhanced PLL, clock pin, and so on) and the clock routing resource (global, regional, or local) utilized. The I/O differential buffer and input register do not have a minimum toggle rate.