Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | 4548                                                         |

| Number of Logic Elements/Cells | 90960                                                        |

| Total RAM Bits                 | 4520448                                                      |

| Number of I/O                  | 650                                                          |

| Number of Gates                | -                                                            |

| Voltage - Supply               | 1.15V ~ 1.25V                                                |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                              |

| Package / Case                 | 1508-BBGA, FCBGA                                             |

| Supplier Device Package        | 1508-FBGA, FC (40x40)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2sgx90ff1508c4n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

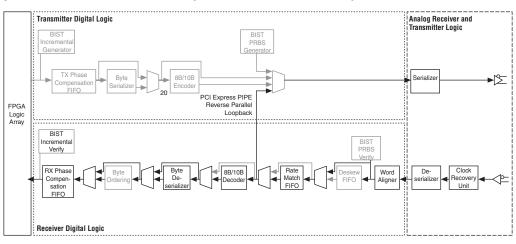

When the FIFO pointers initialize, the receiver domain clock must remain phase locked to receiver FPGA clock.

After resetting the receiver FIFO buffer, writing to the receiver FIFO buffer begins and continues on each parallel clock. The phase compensation FIFO buffer is eight words deep for PIPE mode and four words deep for all other modes.

## **Loopback Modes**

The Stratix II GX transceiver has built-in loopback modes for debugging and testing. The loopback modes are configured in the Stratix II GX ALT2GXB megafunction in the Quartus II software. The available loopback modes are:

- Serial loopback

- Parallel loopback

- Reverse serial loopback

- Reverse serial loopback (pre-CDR)

- PCI Express PIPE reverse parallel loopback (available only in PIPE mode)

#### Serial Loopback

The serial loopback mode exercises all the transceiver logic, except for the input buffer. Serial loopback is available for all non-PIPE modes. The loopback function is dynamically enabled through the rx\_seriallpbken port on a channel-by-channel basis.

In serial loopback mode, the data on the transmit side is sent by the PLD. A separate mode is available in the ALT2GXB megafunction under Basic protocol mode, in which PRBS data is generated and verified internally in the transceiver. The PRBS patterns available in this mode are shown in Table 2–10.

Table 2–10 shows the BIST data output and verifier alignment pattern.

| Table 2–10. BIST Data Output and Verifier Alignment Pattern |              |                     |          |        |          |  |  |  |  |

|-------------------------------------------------------------|--------------|---------------------|----------|--------|----------|--|--|--|--|

| Dottorn                                                     | Dalunamial   | Parallel Data Width |          |        |          |  |  |  |  |

| Pattern                                                     | Polynomial   | 8-Bit               | 10-Bit   | 16-Bit | 20-Bit   |  |  |  |  |

| PRBS-7                                                      | ×7 + ×6 + 1  |                     |          |        | <b>✓</b> |  |  |  |  |

| PRBS-10                                                     | ×10 + ×7 + 1 |                     | <b>✓</b> |        |          |  |  |  |  |

Figure 2–27 show the Stratix II GX block in reverse serial pre-CDR loopback mode.

Transmitter Digital Logic **Analog Receiver and** Transmitter Logic Generator Generato Byte Reverse Array Pre-CDR Loopback ncrementa Verify RX Phase Clock Word De-Compen-Recovery Ordering Aligner serialize Unit FIFO **Receiver Digital Logic**

Figure 2–27. Stratix II GX Block in Reverse Serial Pre-CDR Loopback Mode

#### PCI Express PIPE Reverse Parallel Loopback

This loopback mode, available only in PIPE mode, can be dynamically enabled by the tx\_detectrxloopback port of the PIPE interface. Figure 2–28 shows the datapath for this mode.

Figure 2–28. Stratix II GX Block in PCI Express PIPE Reverse Parallel Loopback Mode

Table 2-13. Available Clocking Connections for Transceivers in 2SGX60E **Clock Resource Transceiver** Region Bank 13 Bank 14 Bank 15 Regional **Global Clock** Clock 8 Clock I/O 8 Clock I/O 8 Clock I/O Region0 RCLK 20-27 **✓** 8 LRIO clock Region1 RCLK 20-27 8 LRIO clock Region2 RCLK 12-19 8 LRIO clock RCLK 12-19 Region3 8 LRIO clock

|                         | Clock           | Resource          |                        | Transceiver            |                        |                        |  |  |  |  |

|-------------------------|-----------------|-------------------|------------------------|------------------------|------------------------|------------------------|--|--|--|--|

| Region                  | Global<br>Clock | Regional<br>Clock | Bank 13<br>8 Clock I/O | Bank 14<br>8 Clock I/O | Bank 15<br>8 clock I/O | Bank 16<br>8 Clock I/O |  |  |  |  |

| Region0<br>8 LRIO clock | <b>✓</b>        | RCLK 20-27        | <b>✓</b>               |                        |                        |                        |  |  |  |  |

| Region1<br>8 LRIO clock | <b>✓</b>        | RCLK 20-27        |                        | ✓                      |                        |                        |  |  |  |  |

| Region2<br>8 LRIO clock | <b>✓</b>        | RCLK 12-19        |                        |                        | ✓                      |                        |  |  |  |  |

| Region3<br>8 LRIO clock | <b>✓</b>        | RCLK 12-19        |                        |                        |                        | ~                      |  |  |  |  |

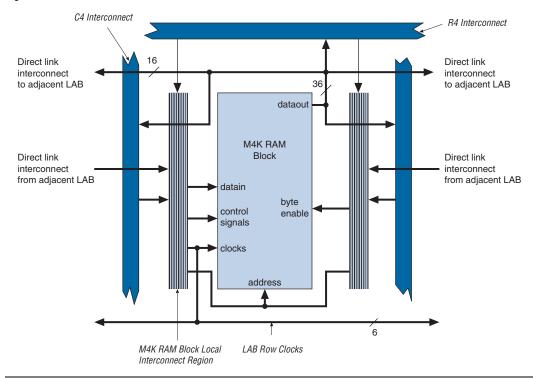

Figure 2-52. M4K RAM Block LAB Row Interface

#### M-RAM Block

The largest TriMatrix memory block, the M-RAM block, is useful for applications where a large volume of data must be stored on-chip. Each block contains 589,824 RAM bits (including parity bits). The M-RAM block can be configured in the following modes:

- True dual-port RAM

- Simple dual-port RAM

- Single-port RAM

- FIFO

You cannot use an initialization file to initialize the contents of a M-RAM block. All M-RAM block contents power up to an undefined value. Only synchronous operation is supported in the M-RAM block, so all inputs are registered. Output registers can be bypassed.

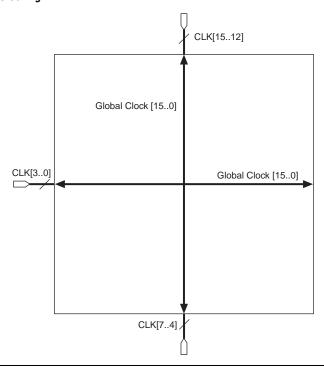

generated global clocks and asynchronous clears, clock enables, or other control signals with large fanout. Figure 2–61 shows the 12 dedicated CLK pins driving global clock networks.

Figure 2-61. Global Clocking

#### Regional Clock Network

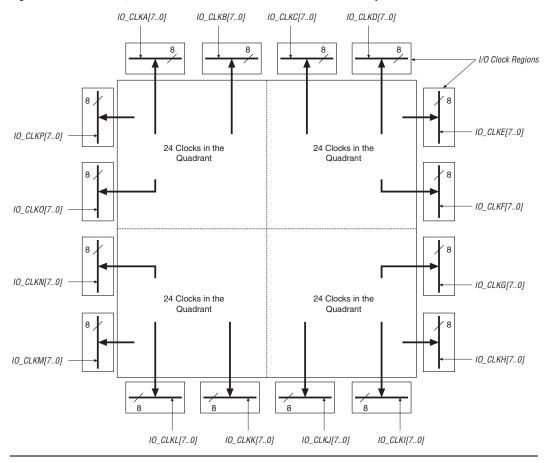

There are eight regional clock networks (RCLK[7..0]) in each quadrant of the Stratix II GX device that are driven by the dedicated CLK[15..12] and CLK[7..0] input pins, by PLL outputs, or by internal logic. The regional clock networks provide the lowest clock delay and skew for logic contained in a single quadrant. The CLK pins symmetrically drive the RCLK networks in a particular quadrant, as shown in Figure 2–62.

Figure 2-66. EP2SGX60, EP2SGX90 and EP2SGX130 Device I/O Clock Groups

You can use the Quartus II software to control whether a clock input pin drives either a global, regional, or dual-regional clock network. The Quartus II software automatically selects the clocking resources if not specified.

#### Clock Control Block

Each global clock, regional clock, and PLL external clock output has its own clock control block. The control block has two functions:

- Clock source selection (dynamic selection for global clocks)

- Clock power-down (dynamic clock enable or disable)

PLL Counter

Outputs (c[5..0])

6

Static Clock Select (1)

Enable/

Disable Internal

Logic

IOE (2)

Internal

Logic

Static Clock

Select (1)

PLL OUT

Figure 2-69. External PLL Output Clock Control Blocks

#### *Notes to Figure 2–69:*

- These clock select signals can only be set through a configuration file (.sof or .pof) and cannot be dynamically

controlled during user mode operation.

- (2) The clock control block feeds to a multiplexer within the PLL\_OUT pin's IOE. The PLL\_OUT pin is a dual-purpose pin. Therefore, this multiplexer selects either an internal signal or the output of the clock control block.

For the global clock control block, the clock source selection can be controlled either statically or dynamically. You have the option of statically selecting the clock source by using the Quartus II software to set specific configuration bits in the configuration file (.sof or .pof) or you can control the selection dynamically by using internal logic to drive the multiplexer select inputs. When selecting statically, the clock source can be set to any of the inputs to the select multiplexer. When selecting the clock source dynamically, you can either select between two PLL outputs (such as the C0 or C1 outputs from one PLL), between two PLLs (such as the C0/C1 clock output of one PLL or the C0/C1 clock output of the other PLL), between two clock pins (such as CLK0 or CLK1), or between a combination of clock pins or PLL outputs.

For the regional and PLL\_OUT clock control block, the clock source selection can only be controlled statically using configuration bits. Any of the inputs to the clock select multiplexer can be set as the clock source.

The connections to the global and regional clocks from the top clock pins and enhanced PLL outputs are shown in Table 2–28. The connections to the clocks from the bottom clock pins are shown in Table 2–29.

| Table 2–28. Global and Reg<br>(Part 1 of 2)                   | Table 2–28. Global and Regional Clock Connections from Top Clock Pins and Enhanced PLL Outputs<br>(Part 1 of 2) |          |          |          |          |          |          |          |          |          |          |          |          |

|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Top Side Global and<br>Regional Clock Network<br>Connectivity | DLLCLK                                                                                                          | CLK12    | CLK13    | CLK14    | CLK15    | RCLK24   | RCLK25   | RCLK26   | RCLK27   | RCLK28   | RCLK29   | RCLK30   | RCLK31   |

| Clock pins                                                    |                                                                                                                 |          |          |          |          |          |          |          |          |          |          |          |          |

| CLK12p                                                        | <b>✓</b>                                                                                                        | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| CLK13p                                                        | <b>✓</b>                                                                                                        | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| CLK14p                                                        | <b>✓</b>                                                                                                        |          |          | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| CLK15p                                                        | <b>✓</b>                                                                                                        |          |          | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| CLK12n                                                        |                                                                                                                 | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| CLK13n                                                        |                                                                                                                 |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| CLK14n                                                        |                                                                                                                 |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| CLK15n                                                        |                                                                                                                 |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| Drivers from internal logic                                   |                                                                                                                 |          |          |          |          |          |          |          | •        |          |          |          |          |

| GCLKDRV0                                                      |                                                                                                                 | <b>✓</b> |          |          |          |          |          |          |          |          |          |          |          |

| GCLKDRV1                                                      |                                                                                                                 |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |          |

| GCLKDRV2                                                      |                                                                                                                 |          |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |

| GCLKDRV3                                                      |                                                                                                                 |          |          |          | <b>✓</b> |          |          |          |          |          |          |          |          |

| RCLKDRV0                                                      |                                                                                                                 |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| RCLKDRV1                                                      |                                                                                                                 |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| RCLKDRV2                                                      |                                                                                                                 |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| RCLKDRV3                                                      |                                                                                                                 |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| RCLKDRV4                                                      |                                                                                                                 |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| RCLKDRV5                                                      |                                                                                                                 |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| RCLKDRV6                                                      |                                                                                                                 |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| RCLKDRV7                                                      |                                                                                                                 |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| Enhanced PLL5 outputs                                         | 1                                                                                                               | 1        | 1        | 1        | 1        | 1        | 1        | 1        |          | 1        | 1        | 1        |          |

| c0                                                            | <b>✓</b>                                                                                                        | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| c1                                                            | <b>✓</b>                                                                                                        | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

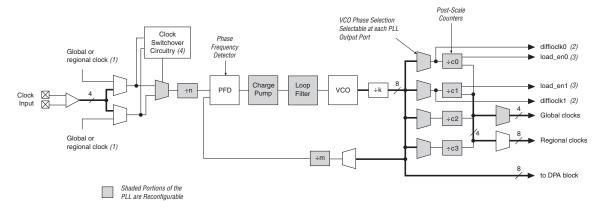

Figure 2-75. Stratix II GX Device Fast PLL

#### Notes to Figure 2-75:

- (1) The global or regional clock input can be driven by an output from another PLL, a pin-driven dedicated global or regional clock, or through a clock control block provided the clock control block is fed by an output from another PLL or a pin-driven dedicated global or regional clock. An internally generated global signal cannot drive the PLL.

- (2) In high-speed differential I/O support mode, this high-speed PLL clock feeds the serializer/deserializer (SERDES) circuitry. Stratix II GX devices only support one rate of data transfer per fast PLL in high-speed differential I/O support mode.

- (3) This signal is a differential I/O SERDES control signal.

- (4) Stratix II GX fast PLLs only support manual clock switchover.

Refer to the *PLLs in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II GX Device Handbook* for more information on enhanced and fast PLLs. Refer to "High-Speed Differential I/O with DPA Support" on page 2–136 for more information on high-speed differential I/O support.

# I/O Structure

The Stratix II GX IOEs provide many features, including:

- Dedicated differential and single-ended I/O buffers

- 3.3-V, 64-bit, 66-MHz PCI compliance

- 3.3-V, 64-bit, 133-MHz PCI-X 1.0 compliance

- Joint Test Action Group (JTAG) boundary-scan test (BST) support

- On-chip driver series termination

- On-chip termination for differential standards

- Programmable pull-up during configuration

- Output drive strength control

- Tri-state buffers

- Bus-hold circuitry

- Programmable pull-up resistors

- Programmable input and output delays

| Table 2–34. On-Chip Termination Support by I/O Banks (Part 2 of 2) |                           |                                   |                  |  |  |  |  |  |

|--------------------------------------------------------------------|---------------------------|-----------------------------------|------------------|--|--|--|--|--|

| On-Chip Termination Support                                        | I/O Standard Support      | Top and Bottom Banks (3, 4, 7, 8) | Left Bank (1, 2) |  |  |  |  |  |

|                                                                    | 3.3-V LVTTL               | ✓                                 | _                |  |  |  |  |  |

|                                                                    | 3.3-V LVCMOS              | ✓                                 | _                |  |  |  |  |  |

|                                                                    | 2.5-V LVTTL               | ✓                                 | _                |  |  |  |  |  |

|                                                                    | 2.5-V LVCMOS              | ✓                                 | _                |  |  |  |  |  |

|                                                                    | 1.8-V LVTTL               | ✓                                 | _                |  |  |  |  |  |

|                                                                    | 1.8-V LVCMOS              | ✓                                 | _                |  |  |  |  |  |

| Series termination with                                            | 1.5-V LVTTL               | ✓                                 | _                |  |  |  |  |  |

| calibration                                                        | 1.5-V LVCMOS              | ✓                                 | _                |  |  |  |  |  |

|                                                                    | SSTL-2 class I and II     | ✓                                 | _                |  |  |  |  |  |

|                                                                    | SSTL-18 class I and II    | ✓                                 | _                |  |  |  |  |  |

|                                                                    | 1.8-V HSTL class I        | ✓                                 | _                |  |  |  |  |  |

|                                                                    | 1.8-V HSTL class II       | <b>✓</b>                          | _                |  |  |  |  |  |

|                                                                    | 1.5-V HSTL class I        | <b>✓</b>                          | _                |  |  |  |  |  |

|                                                                    | 1.2-V HSTL                | ✓                                 | _                |  |  |  |  |  |

| <b>5</b> /// (1)                                                   | LVDS                      | _                                 | ✓                |  |  |  |  |  |

| Differential termination (1)                                       | HyperTransport technology |                                   | <b>✓</b>         |  |  |  |  |  |

#### Note to Table 2-34:

#### Differential On-Chip Termination

Stratix II GX devices support internal differential termination with a nominal resistance value of 100 for LVDS input receiver buffers. LVPECL input signals (supported on clock pins only) require an external termination resistor. Differential on-chip termination is supported across the full range of supported differential data rates, as shown in the *High-Speed I/O Specifications* section of the *DC & Switching Characteristics* chapter in volume 1 of the *Stratix II GX Device Handbook*.

For more information on differential on-chip termination, refer to the *High-Speed Differential I/O Interfaces with DPA in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II GX Device Handbook*.

<sup>(1)</sup> Clock pins CLK1 and CLK3, and pins FPLL [7..8] CLK do not support differential on-chip termination. Clock pins CLK0 and CLK2, do support differential on-chip termination. Clock pins in the top and bottom banks (CLK [4..7, 12..15]) do not support differential on-chip termination.

| Table 2–37. Supported TDO/TDI Voltage Combinations (Part 2 of 2) |              |                                                                 |                           |                           |                           |                           |  |  |  |  |

|------------------------------------------------------------------|--------------|-----------------------------------------------------------------|---------------------------|---------------------------|---------------------------|---------------------------|--|--|--|--|

| Device                                                           | TDI Input    | Stratix II GX TDO V <sub>CC10</sub> Voltage Level in I/O Bank 4 |                           |                           |                           |                           |  |  |  |  |

| Device                                                           | Buffer Power | V <sub>CC10</sub> = 3.3 V                                       | V <sub>CC10</sub> = 2.5 V | V <sub>CCIO</sub> = 1.8 V | V <sub>CCIO</sub> = 1.5 V | V <sub>CC10</sub> = 1.2 V |  |  |  |  |

| Non-<br>Stratix II GX                                            | VCC = 3.3 V  | <b>√</b> (1)                                                    | <b>√</b> (2)              | <b>√</b> (3)              | Level shifter required    | Level shifter required    |  |  |  |  |

|                                                                  | VCC = 2.5 V  | <b>√</b> (1), (4)                                               | <b>√</b> (2)              | <b>√</b> (3)              | Level shifter required    | Level shifter required    |  |  |  |  |

|                                                                  | VCC = 1.8 V  | <b>√</b> (1), (4)                                               | <b>✓</b> (2), (5)         | <b>✓</b>                  | Level shifter required    | Level shifter required    |  |  |  |  |

|                                                                  | VCC = 1.5 V  | <b>√</b> (1), (4)                                               | <b>√</b> (2), (5)         | <b>√</b> (6)              | ✓                         | ✓                         |  |  |  |  |

Notes to Table 2-37:

- (1) The TDO output buffer meets  $V_{OH}$  (MIN) = 2.4 V.

- (2) The TDO output buffer meets  $V_{OH}$  (MIN) = 2.0 V.

- (3) An external 250-Ω pull-up resistor is not required, but recommended if signal levels on the board are not optimal.

- (4) Input buffer must be 3.3-V tolerant.

- (5) Input buffer must be 2.5-V tolerant.

- (6) Input buffer must be 1.8-V tolerant.

# High-Speed Differential I/O with DPA Support

Stratix II GX devices contain dedicated circuitry for supporting differential standards at speeds up to 1 Gbps. The LVDS differential I/O standards are supported in the Stratix II GX device. In addition, the LVPECL I/O standard is supported on input and output clock pins on the top and bottom I/O banks.

The high-speed differential I/O circuitry supports the following high-speed I/O interconnect standards and applications:

- SPI-4 Phase 2 (POS-PHY Level 4)

- SFI-4

- Parallel RapidIO standard

There are two dedicated high-speed PLLs in the EP2SGX30 device and four dedicated high-speed PLLs in the EP2SGX60, EP2SGX90, and EP2SGX130 devices to multiply reference clocks and drive high-speed differential SERDES channels.

Tables 2–38 through 2–41 show the number of channels that each Fast PLL can clock in each of the Stratix II GX devices. In Tables 2–38 through 2–41, the first row for each transmitter or receiver provides the number of channels driven directly by the PLL. The second row below it shows the maximum channels a Fast PLL can drive if cross bank channels are used from the adjacent center Fast PLL. For example, in the 780-pin FineLine BGA EP2SGX30 device, PLL 1 can drive a maximum of

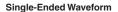

Figure 4-4. Transmitter Output Waveform

# Differential Waveform $V_{OD}$ (diff peak-peak) = 2 x $V_{OD}$ (single-ended) $V_{OD}$ p-n=0 $V_{OD}$

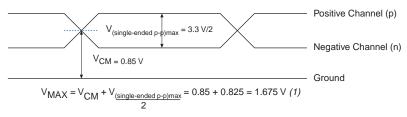

Figure 4-5. Maximum Receiver Input Pin Voltage

#### Single-Ended Waveform

*Note to Figure 4–5:*

(1) The absolute  $V_{MAX}$  that the receiver input pins can tolerate is 2 V.

Tables 4–7 through 4–12 show the typical  $V_{OD}$  for data rates from 600 Mbps to 6.375 Gbps. The specification is for measurement at the package ball.

| Table 4–7. Typical $V_{0D}$ Setting, TX Term = 100 $\Omega$ Note (1) |     |                              |     |     |      |      |      |  |  |  |

|----------------------------------------------------------------------|-----|------------------------------|-----|-----|------|------|------|--|--|--|

| V <sub>CCH</sub> TX = 1.5 V                                          |     | V <sub>OD</sub> Setting (mV) |     |     |      |      |      |  |  |  |

|                                                                      | 200 | 400                          | 600 | 800 | 1000 | 1200 | 1400 |  |  |  |

| V <sub>OD</sub> Typical (mV)                                         | 220 | 430                          | 625 | 830 | 1020 | 1200 | 1350 |  |  |  |

Note to Table 4-7:

(1) Applicable to data rates from 600 Mbps to 6.375 Gbps. Specification is for measurement at the package ball.

| Table 4–31.                            | PCML Specifications Note (1)             |                                                                                         |

|----------------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------|

| Symbol                                 | Parameter                                | References                                                                              |

| Reference Cl                           | ock                                      |                                                                                         |

| 3.3-V PCML<br>1.5-V PCML<br>1.2-V PCML | Reference clock supported PCML standards |                                                                                         |

| V <sub>ID</sub>                        | Peak-to-peak differential input voltage  | The specifications are located in the Reference Clock section of Table 4–6 on page 4–4. |

| V <sub>ICM</sub>                       | Input common mode voltage                | The specifications listed in Table 4–6 are applicable to PCML                           |

| R                                      | On-chip termination resistors            | input standards.                                                                        |

| Receiver                               |                                          |                                                                                         |

| 3.3-V PCML<br>1.5-V PCML<br>1.2-V PCML | Receiver supported PCML standards        |                                                                                         |

| V <sub>ID</sub>                        | Peak-to-peak differential input voltage  | The specifications are located in the Receiver section of Table 4–6 on page 4–4.        |

| V <sub>ICM</sub>                       | Input common mode voltage                | The specifications listed in Table 4–6 are applicable to PCML                           |

| R                                      | On-chip termination resistors            | input standards.                                                                        |

| Transmitter                            |                                          |                                                                                         |

| 1.5-V PCML<br>1.2-V PCML               | Transmitter supported PCML standards     |                                                                                         |

| V <sub>CCH</sub>                       | Output buffer supply voltage             | The specifications are located in Table 4–5 on page 4–4.                                |

| V <sub>OD</sub>                        | Peak-to-peak differential output voltage | The specifications are located in Tables 4–7, 4–8, 4–9, 4–10, 4–11, and 4–12.           |

|                                        |                                          | The specifications listed in these tables are applicable to PCML output standards.      |

| V <sub>OCM</sub>                       | Output common mode voltage               | The specifications are located in the Transmitter section of                            |

| R                                      | On-chip termination resistors            | Table 4–6 on page 4–4.                                                                  |

|                                        |                                          | The specifications listed in Table 4–6 are applicable to PCML output standards.         |

#### *Note to Table 4–31:*

(1) Stratix II GX devices support PCML input and output on GXB banks 13, 14, 15, 16, and 17. This table references Stratix II GX PCML specifications that are located in other sections of the *Stratix II GX Device Handbook*.

Final timing numbers are based on actual device operation and testing. These numbers reflect the actual performance of the device under worst-case voltage and junction temperature conditions.

| Table 4–52. Stratix II GX Device Timing Model Status |             |       |  |  |  |  |  |

|------------------------------------------------------|-------------|-------|--|--|--|--|--|

| Device                                               | Preliminary | Final |  |  |  |  |  |

| EP2SGX30                                             |             | ✓     |  |  |  |  |  |

| EP2SGX60                                             |             | ✓     |  |  |  |  |  |

| EP2SGX90                                             |             | ✓     |  |  |  |  |  |

| EP2SGX130                                            |             | ✓     |  |  |  |  |  |

#### I/O Timing Measurement Methodology

Different I/O standards require different baseline loading techniques for reporting timing delays. Altera characterizes timing delays with the required termination for each I/O standard and with 0 pF (except for PCI and PCI-X which use 10 pF) loading and the timing is specified up to the output pin of the FPGA device. The Quartus II software calculates the I/O timing for each I/O standard with a default baseline loading as specified by the I/O standards.

The following measurements are made during device characterization. Altera measures clock-to-output delays ( $t_{CO}$ ) at worst-case process, minimum voltage, and maximum temperature (PVT) for default loading conditions shown in Table 4–53. Use the following equations to calculate clock pin to output pin timing for Stratix II GX devices.

- t<sub>CO</sub> from clock pin to I/O pin = delay from clock pad to I/O output register + IOE output register clock-to-output delay + delay from output register to output pin + I/O output delay

- $t_{xz}/t_{zx}$  from clock pin to I/O pin = delay from clock pad to I/O output register + IOE output register clock-to-output delay + delay from output register to output pin + I/O output delay + output enable pin delay

Simulation using IBIS models is required to determine the delays on the PCB traces in addition to the output pin delay timing reported by the Quartus II software and the timing model in the device handbook.

- 1. Simulate the output driver of choice into the generalized test setup, using values from Table 4–53.

- 2. Record the time to  $V_{MEAS}$ .

| Table 4–59. M512 Block Internal Timing Microparameters (Part 2 of 2) |                           |                      |     |                |     |                |     |                |     |      |

|----------------------------------------------------------------------|---------------------------|----------------------|-----|----------------|-----|----------------|-----|----------------|-----|------|

| Symbol                                                               | Parameter                 | -3 Speed<br>Grade(2) |     | -3 Speed Grade |     | -4 Speed Grade |     | -5 Speed Grade |     | Unit |

|                                                                      |                           | Min                  | Max | Min            | Max | Min            | Max | Min            | Max |      |

| t <sub>M512CLR</sub>                                                 | Minimum clear pulse width | 144                  |     | 151            |     | 160            |     | 192            |     | ps   |

- (1) The M512 block  $f_{MAX}$  obtained using the Quartus II software does not necessarily equal to 1/TM512RC.

- (2) This column refers to –3 speed grades for EP2SGX30, EP2SGX60, and EP2SGX90 devices.

- (3) This column refers to –3 speed grades for EP2SGX130 devices.

| Table 4-60.             | M4K Block Interna                                | l Timing                  | Micropa | rameters | (Part 1              | of 2) | Note (1 | )              |      |      |

|-------------------------|--------------------------------------------------|---------------------------|---------|----------|----------------------|-------|---------|----------------|------|------|

| Symbol                  | Parameter                                        | <b>-3 Speed Grade</b> (2) |         |          | -3 Speed Grade $(3)$ |       | d Grade | -5 Speed Grade |      | Unit |

|                         |                                                  | Min                       | Max     | Min      | Max                  | Min   | Max     | Min            | Max  |      |

| t <sub>M4KRC</sub>      | Synchronous read cycle time                      | 1462                      | 2240    | 1462     | 2351                 | 1462  | 2500    | 1462           | 3000 | ps   |

| t <sub>M4KWERESU</sub>  | Write or read enable setup time before clock     | 22                        |         | 23       |                      | 24    |         | 29             |      | ps   |

| t <sub>M4KWEREH</sub>   | Write or read<br>enable hold time<br>after clock | 203                       |         | 213      |                      | 226   |         | 272            |      | ps   |

| t <sub>M4KBESU</sub>    | Byte enable setup time before clock              | 22                        |         | 23       |                      | 24    |         | 29             |      | ps   |

| t <sub>M4KBEH</sub>     | Byte enable hold time after clock                | 203                       |         | 213      |                      | 226   |         | 272            |      | ps   |

| t <sub>M4KDATAASU</sub> | A port data setup time before clock              | 22                        |         | 23       |                      | 24    |         | 29             |      | ps   |

| t <sub>M4KDATAAH</sub>  | A port data hold time after clock                | 203                       |         | 213      |                      | 226   |         | 272            |      | ps   |

| t <sub>M4KADDRASU</sub> | A port address<br>setup time before<br>clock     | 22                        |         | 23       |                      | 24    |         | 29             |      | ps   |

| t <sub>M4KADDRAH</sub>  | A port address<br>hold time after<br>clock       | 203                       |         | 213      |                      | 226   |         | 272            |      | ps   |

| t <sub>M4KDATABSU</sub> | B port data setup time before clock              | 22                        |         | 23       |                      | 24    |         | 29             |      | ps   |

| Table 4–85. Stratix II (           | GX I/O Input L     | Delay for Row                            | Pins (Part 3 of       | 3)                    |                   |                   |      |

|------------------------------------|--------------------|------------------------------------------|-----------------------|-----------------------|-------------------|-------------------|------|

| I/O Standard                       | Parameter          | Fast Corner<br>Industrial/<br>Commercial | -3 Speed<br>Grade (2) | -3 Speed<br>Grade (3) | -4 Speed<br>Grade | -5 Speed<br>Grade | Unit |

| Differential SSTL-18               | t <sub>Pl</sub>    | 605                                      | 960                   | 1006                  | 1070              | 1285              | ps   |

| Class I                            | t <sub>PCOUT</sub> | 266                                      | 433                   | 454                   | 483               | 580               | ps   |

| Differential SSTL-18               | t <sub>Pl</sub>    | 605                                      | 960                   | 1006                  | 1070              | 1285              | ps   |

| Class II                           | t <sub>PCOUT</sub> | 266                                      | 433                   | 454                   | 483               | 580               | ps   |

| 1.8-V differential HSTL            | t <sub>Pl</sub>    | 605                                      | 960                   | 1006                  | 1070              | 1285              | ps   |

| 1.8-V differential HSTL<br>Class I | t <sub>PCOUT</sub> | 266                                      | 433                   | 454                   | 483               | 580               | ps   |

| 1.8-V differential HSTL            | t <sub>Pl</sub>    | 605                                      | 960                   | 1006                  | 1070              | 1285              | ps   |

| Class II                           | t <sub>PCOUT</sub> | 266                                      | 433                   | 454                   | 483               | 580               | ps   |

| 1.5-V differential HSTL            | t <sub>Pl</sub>    | 631                                      | 1056                  | 1107                  | 1177              | 1413              | ps   |

| Class I                            | t <sub>PCOUT</sub> | 292                                      | 529                   | 555                   | 590               | 708               | ps   |

| 1.5-V differential HSTL            | t <sub>Pl</sub>    | 631                                      | 1056                  | 1107                  | 1177              | 1413              | ps   |

| Class II                           | t <sub>PCOUT</sub> | 292                                      | 529                   | 555                   | 590               | 708               | ps   |

<sup>(1)</sup> The parameters are only available on the left side of the device.

(2) This column refers to -3 speed grades for EP2SGX30, EP2SGX60, and EP2SGX90 devices.

(3) This column refers to -3 speed grades for EP2SGX130 devices.

Table 4–87. Stratix II GX I/O Output Delay for Row Pins (Part 2 of 4)

| I/O Standard    | Drive<br>Strength | Parameter        | Fast Corner<br>Industrial/<br>Commercial | -3 Speed<br>Grade (3) | -3 Speed<br>Grade (4) | -4 Speed<br>Grade | -5 Speed<br>Grade | Unit |

|-----------------|-------------------|------------------|------------------------------------------|-----------------------|-----------------------|-------------------|-------------------|------|

| LVCMOS          | 4 mA              | t <sub>OP</sub>  | 1200                                     | 2113                  | 2217                  | 2357              | 2549              | ps   |

|                 |                   | t <sub>DIP</sub> | 1157                                     | 2058                  | 2160                  | 2297              | 2476              | ps   |

|                 | 8 mA (1)          | t <sub>OP</sub>  | 1094                                     | 1853                  | 1944                  | 2067              | 2243              | ps   |

|                 |                   | t <sub>DIP</sub> | 1051                                     | 1798                  | 1887                  | 2007              | 2170              | ps   |

|                 | 12 mA (1)         | t <sub>OP</sub>  | 1061                                     | 1723                  | 1808                  | 1922              | 2089              | ps   |

|                 |                   | t <sub>DIP</sub> | 1018                                     | 1668                  | 1751                  | 1862              | 2016              | ps   |

| 2.5 V           | 4 mA              | t <sub>OP</sub>  | 1183                                     | 2091                  | 2194                  | 2332              | 2523              | ps   |

|                 |                   | t <sub>DIP</sub> | 1140                                     | 2036                  | 2137                  | 2272              | 2450              | ps   |

|                 | 8 mA              | t <sub>OP</sub>  | 1080                                     | 1872                  | 1964                  | 2088              | 2265              | ps   |

|                 |                   | t <sub>DIP</sub> | 1037                                     | 1817                  | 1907                  | 2028              | 2192              | ps   |

|                 | 12 mA (1)         | t <sub>OP</sub>  | 1061                                     | 1775                  | 1862                  | 1980              | 2151              | ps   |

|                 |                   | t <sub>DIP</sub> | 1018                                     | 1720                  | 1805                  | 1920              | 2078              | ps   |

| 1.8 V           | 2 mA              | t <sub>OP</sub>  | 1253                                     | 2954                  | 3100                  | 3296              | 3542              | ps   |

|                 |                   | t <sub>DIP</sub> | 1210                                     | 2899                  | 3043                  | 3236              | 3469              | ps   |

|                 | 4 mA              | t <sub>OP</sub>  | 1242                                     | 2294                  | 2407                  | 2559              | 2763              | ps   |

|                 |                   | t <sub>DIP</sub> | 1199                                     | 2239                  | 2350                  | 2499              | 2690              | ps   |

|                 | 6 mA              | t <sub>OP</sub>  | 1131                                     | 2039                  | 2140                  | 2274              | 2462              | ps   |

|                 |                   | t <sub>DIP</sub> | 1088                                     | 1984                  | 2083                  | 2214              | 2389              | ps   |

|                 | 8 mA (1)          | t <sub>OP</sub>  | 1100                                     | 1942                  | 2038                  | 2166              | 2348              | ps   |

|                 |                   | t <sub>DIP</sub> | 1057                                     | 1887                  | 1981                  | 2106              | 2275              | ps   |

| 1.5 V           | 2 mA              | t <sub>OP</sub>  | 1213                                     | 2530                  | 2655                  | 2823              | 3041              | ps   |

|                 |                   | t <sub>DIP</sub> | 1170                                     | 2475                  | 2598                  | 2763              | 2968              | ps   |

|                 | 4 mA (1)          | t <sub>OP</sub>  | 1106                                     | 2020                  | 2120                  | 2253              | 2440              | ps   |

|                 |                   | t <sub>DIP</sub> | 1063                                     | 1965                  | 2063                  | 2193              | 2367              | ps   |

| SSTL-2 Class I  | 8 mA              | t <sub>OP</sub>  | 1050                                     | 1759                  | 1846                  | 1962              | 2104              | ps   |

|                 |                   | t <sub>DIP</sub> | 1007                                     | 1704                  | 1789                  | 1902              | 2031              | ps   |

|                 | 12 mA (1)         | t <sub>OP</sub>  | 1026                                     | 1694                  | 1777                  | 1889              | 2028              | ps   |

|                 |                   | t <sub>DIP</sub> | 983                                      | 1639                  | 1720                  | 1829              | 1955              | ps   |

| SSTL-2 Class II | 16 mA (1)         | t <sub>OP</sub>  | 992                                      | 1581                  | 1659                  | 1763              | 1897              | ps   |

|                 |                   | t <sub>DIP</sub> | 949                                      | 1526                  | 1602                  | 1703              | 1824              | ps   |

| I/O Standard               | Drive Strength | -3 Speed<br>Grade | -4 Speed<br>Grade | -5 Speed<br>Grade | Unit |

|----------------------------|----------------|-------------------|-------------------|-------------------|------|

| 1.8-V differential         | 16 mA          | 500               | 500               | 450               | MHz  |

| Class II                   | 18 mA          | 550               | 500               | 500               | MHz  |

|                            | 20 mA          | 550               | 550               | 550               | MHz  |

| 1.5-V differential Class I | 4 mA           | 350               | 300               | 300               | MHz  |

|                            | 6 mA           | 500               | 500               | 450               | MHz  |

|                            | 8 mA           | 700               | 650               | 600               | MHz  |

|                            | 10 mA          | 700               | 700               | 650               | MHz  |

|                            | 12 mA          | 700               | 700               | 700               | MHz  |

| 1.5-V differential         | 16 mA          | 600               | 600               | 550               | MHz  |

| Class II                   | 18 mA          | 650               | 600               | 600               | MHz  |

|                            | 20 mA          | 700               | 650               | 600               | MHz  |

| HyperTransport             | -              | 300               | 250               | 125               | MHz  |

| LVPECL                     | -              | 450               | 400               | 300               | MHz  |

<sup>(1)</sup> This is the default setting in Quartus II software.

Table 4–94 shows the maximum output clock toggle rate for Stratix II GX device series-terminated column pins.

| Table 4–94. Stratix II GX Maximum Output Clock Rate for Column Pins (Series Termination) (Part 1 of 2) |                |                |                |                |      |  |

|--------------------------------------------------------------------------------------------------------|----------------|----------------|----------------|----------------|------|--|

| I/O Standard                                                                                           | Drive Strength | -3 Speed Grade | -4 Speed Grade | -5 Speed Grade | Unit |  |

| LVTTL                                                                                                  | OCT_25_OHMS    | 400            | 400            | 350            | MHz  |  |

|                                                                                                        | OCT_50_OHMS    | 400            | 400            | 350            | MHz  |  |

| LVCMOS                                                                                                 | OCT_25_OHMS    | 350            | 350            | 300            | MHz  |  |

|                                                                                                        | OCT_50_OHMS    | 350            | 350            | 300            | MHz  |  |

| 2.5 V                                                                                                  | OCT_25_OHMS    | 350            | 350            | 300            | MHz  |  |

|                                                                                                        | OCT_50_OHMS    | 350            | 350            | 300            | MHz  |  |

| 1.8 V                                                                                                  | OCT_25_OHMS    | 700            | 550            | 450            | MHz  |  |

|                                                                                                        | OCT_50_OHMS    | 700            | 550            | 450            | MHz  |  |

| 1.5 V                                                                                                  | OCT_50_OHMS    | 550            | 450            | 400            | MHz  |  |

| SSTL-2 Class I                                                                                         | OCT_50_OHMS    | 600            | 500            | 500            | MHz  |  |

| SSTL-2 Class II                                                                                        | OCT_25_OHMS    | 600            | 550            | 500            | MHz  |  |

**Table 4–100. Maximum DCD for DDIO Output on Row I/O Pins Without PLL in the Clock Path for -3 Devices** *Note* (1)

|                                             | Input I/O Standard (No PLL in Clock Path) |                  |        |                  |       |      |

|---------------------------------------------|-------------------------------------------|------------------|--------|------------------|-------|------|

| Maximum DCD (ps) for<br>Row DDIO Output I/O | TTL/CMOS                                  |                  | SSTL-2 | SSTL/HSTL        | LVDS  | Unit |

| Standard                                    | 3.3 and<br>2.5 V                          | 1.8 and<br>1.5 V | 2.5 V  | 1.8 and<br>1.5 V | 3.3 V |      |

| 3.3-V LVTTL                                 | 260                                       | 380              | 145    | 145              | 110   | ps   |

| 3.3-V LVCMOS                                | 210                                       | 330              | 100    | 100              | 65    | ps   |

| 2.5 V                                       | 195                                       | 315              | 85     | 85               | 75    | ps   |

| 1.8 V                                       | 150                                       | 265              | 85     | 85               | 120   | ps   |

| 1.5-V LVCMOS                                | 255                                       | 370              | 140    | 140              | 105   | ps   |

| SSTL-2 Class I                              | 175                                       | 295              | 65     | 65               | 70    | ps   |

| SSTL-2 Class II                             | 170                                       | 290              | 60     | 60               | 75    | ps   |

| SSTL-18 Class I                             | 155                                       | 275              | 55     | 50               | 90    | ps   |

| 1.8-V HSTL Class I                          | 150                                       | 270              | 60     | 60               | 95    | ps   |

| 1.5-V HSTL Class I                          | 150                                       | 270              | 55     | 55               | 90    | ps   |

| LVDS                                        | 180                                       | 180              | 180    | 180              | 180   | ps   |

(1) The information in Table 4–100 assumes the input clock has zero DCD.

Here is an example for calculating the DCD in percentage for a DDIO output on a row I/O on a -3 device:

If the input I/O standard is 2.5-V SSTL-2 and the DDIO output I/O standard is SSTL-2 Class= II, the maximum DCD is 60 ps (see Table 4–100). If the clock frequency is 267 MHz, the clock period T is:

$$T = 1/f = 1/267 \text{ MHz} = 3.745 \text{ ns} = 3,745 \text{ ps}$$

Calculate the DCD as a percentage:

$$(T/2 - DCD) / T = (3,745 ps/2 - 60 ps) / 3745 ps = 48.4\%$$

(for low boundary)

$$(T/2 + DCD) / T = (3,745 ps/2 + 60 ps) / 3745 ps = 51.6\%$$

(for high boundary)

| Table 4–112. DLL Frequency Range Specifications (Part 2 of 2) |                                    |    |  |  |

|---------------------------------------------------------------|------------------------------------|----|--|--|

| Frequency Mode                                                | Resolution<br>(Degrees)            |    |  |  |

| 3                                                             | 240 to 400 (-3 speed grade)        | 36 |  |  |

| 3                                                             | 240 to 350 (-4 and -5 speed grade) | 36 |  |  |

| <b>Table 4–113. DQS Jitter Specifications for DLL-Delayed Clock (t</b> <sub>DQS-JITTER</sub> )  Note (1) |     |     |  |  |  |  |

|----------------------------------------------------------------------------------------------------------|-----|-----|--|--|--|--|

| Number of DQS Delay Buffer Stages Commercial (ps) Industrial (ps)                                        |     |     |  |  |  |  |

| 1                                                                                                        | 80  | 110 |  |  |  |  |

| 2                                                                                                        | 110 | 130 |  |  |  |  |

| 3                                                                                                        | 130 | 180 |  |  |  |  |

| 4                                                                                                        | 160 | 210 |  |  |  |  |

- Peak-to-peak period jitter on the phase-shifted DQS clock. For example, jitter on two delay stages under commercial conditions is 200 ps peak-to-peak or 100 ps.

- (2) Delay stages used for requested DQS phase shift are reported in a project's Compilation Report in the Quartus II software.

| Table 4–114. DQS Phase-Shift Error Specifications for DLL-Delayed Clock (t <sub>DQS_PSERR</sub> ) |     |     |     |  |  |  |

|---------------------------------------------------------------------------------------------------|-----|-----|-----|--|--|--|

| Number of DQS Delay Buffer Stages (1) -3 Speed Grade (ps) -4 Speed Grade (ps) -5 Speed Grade (ps  |     |     |     |  |  |  |

| 1                                                                                                 | 25  | 30  | 35  |  |  |  |

| 2                                                                                                 | 50  | 60  | 70  |  |  |  |

| 3                                                                                                 | 75  | 90  | 105 |  |  |  |

| 4                                                                                                 | 100 | 120 | 140 |  |  |  |

(1) Delay stages used for request DQS phase shift are reported in a project's Compilation Report in the Quartus II software. For example, phase-shift error on two delay stages under -3 conditions is 50 ps peak-to-peak or 25 ps.