Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Obsolete                                                      |

| Number of LABs/CLBs            | 4548                                                          |

| Number of Logic Elements/Cells | 90960                                                         |

| Total RAM Bits                 | 4520448                                                       |

| Number of I/O                  | 650                                                           |

| Number of Gates                | -                                                             |

| Voltage - Supply               | 1.15V ~ 1.25V                                                 |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                               |

| Package / Case                 | 1508-BBGA, FCBGA                                              |

| Supplier Device Package        | 1508-FBGA, FC (40x40)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2sgx90ff1508c5es |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

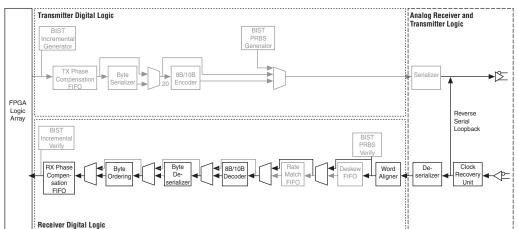

Figure 2–26 shows the data path in reverse serial loopback mode.

Figure 2–26. Stratix II GX Block in Reverse Serial Loopback Mode

#### Reverse Serial Pre-CDR Loopback

The reverse serial pre-CDR loopback mode uses the analog portion of the transceiver. An external source (pattern generator or transceiver) generates the source data. The high-speed serial source data arrives at the high-speed differential receiver input buffer, loops back before the CRU unit, and is transmitted though the high-speed differential transmitter output buffer. It is for test or verification use only to verify the signal being received after the gain and equalization improvements of the input buffer. The signal at the output is not exactly what is received since the signal goes through the output buffer and the VOD is changed to the VOD setting level. The pre-emphasis settings have no effect.

Figure 2–27 show the Stratix II GX block in reverse serial pre-CDR loopback mode.

**Transmitter Digital Logic Analog Receiver and** Transmitter Logic Generator Generato Byte Reverse Array Pre-CDR Loopback ncrementa Verify RX Phase Clock Word De-Compen-Recovery Ordering Aligner serialize Unit FIFO **Receiver Digital Logic**

Figure 2–27. Stratix II GX Block in Reverse Serial Pre-CDR Loopback Mode

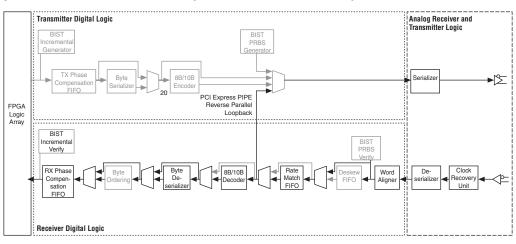

### PCI Express PIPE Reverse Parallel Loopback

This loopback mode, available only in PIPE mode, can be dynamically enabled by the tx\_detectrxloopback port of the PIPE interface. Figure 2–28 shows the datapath for this mode.

Figure 2–28. Stratix II GX Block in PCI Express PIPE Reverse Parallel Loopback Mode

The direct link interconnect allows a LAB, DSP block, or TriMatrix memory block to drive into the local interconnect of its left and right neighbors and then back into itself, providing fast communication between adjacent LABs and/or blocks without using row interconnect resources.

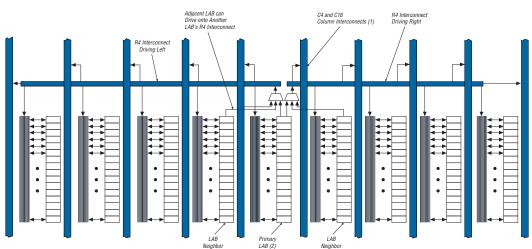

The R4 interconnects span four LABs, three LABs and one M512 RAM block, two LABs and one M4K RAM block, or two LABs and one DSP block to the right or left of a source LAB. These resources are used for fast row connections in a four-LAB region. Every LAB has its own set of R4 interconnects to drive either left or right. Figure 2–46 shows R4 interconnect connections from a LAB.

R4 interconnects can drive and be driven by DSP blocks and RAM blocks and row IOEs. For LAB interfacing, a primary LAB or LAB neighbor can drive a given R4 interconnect. For R4 interconnects that drive to the right, the primary LAB and right neighbor can drive onto the interconnect. For R4 interconnects that drive to the left, the primary LAB and its left neighbor can drive onto the interconnects. R4 interconnects can drive other R4 interconnects to extend the range of LABs they can drive. R4 interconnects can also drive C4 and C16 interconnects for connections from one row to another. Additionally, R4 interconnects can drive R24 interconnects.

Figure 2–46. R4 Interconnect Connections Notes (1), (2), (3)

#### *Notes to Figure 2–46:*

- (1) C4 and C16 interconnects can drive R4 interconnects.

- (2) This pattern is repeated for every LAB in the LAB row.

- (3) The LABs in Figure 2–46 show the 16 possible logical outputs per LAB.

| Memory Feature                              | M512 RAM Block<br>(32 × 18 Bits)                                        | M4K RAM Block<br>(128 × 36 Bits)                                                                 | M-RAM Block<br>(4K × 144 Bits)                                                                                   |

|---------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| Simple dual-port memory mixed width support | <b>✓</b>                                                                | ~                                                                                                | <b>✓</b>                                                                                                         |

| True dual-port memory mixed width support   |                                                                         | ~                                                                                                | <b>✓</b>                                                                                                         |

| Power-up conditions                         | Outputs cleared                                                         | Outputs cleared                                                                                  | Outputs unknown                                                                                                  |

| Register clears                             | Output registers                                                        | Output registers                                                                                 | Output registers                                                                                                 |

| Mixed-port read-during-write                | Unknown output/old data                                                 | Unknown output/old data                                                                          | Unknown output                                                                                                   |

| Configurations                              | 512 × 1<br>256 × 2<br>128 × 4<br>64 × 8<br>64 × 9<br>32 × 16<br>32 × 18 | 4K × 1<br>2K × 2<br>1K × 4<br>512 × 8<br>512 × 9<br>256 × 16<br>256 × 18<br>128 × 32<br>128 × 36 | 64K × 8<br>64K × 9<br>32K × 16<br>32K × 18<br>16K × 32<br>16K × 36<br>8K × 64<br>8K × 72<br>4K × 128<br>4K × 144 |

Note to Table 2-19:

TriMatrix memory provides three different memory sizes for efficient application support. The Quartus II software automatically partitions the user-defined memory into the embedded memory blocks using the most efficient size combinations. You can also manually assign the memory to a specific block size or a mixture of block sizes.

#### M512 RAM Block

The M512 RAM block is a simple dual-port memory block and is useful for implementing small FIFO buffers, DSP, and clock domain transfer applications. Each block contains 576 RAM bits (including parity bits). M512 RAM blocks can be configured in the following modes:

- Simple dual-port RAM

- Single-port RAM

- FIFO

- ROM

- Shift register

When configured as RAM or ROM, you can use an initialization file to pre-load the memory contents.

Violating the setup or hold time on the memory block address registers could corrupt memory contents. This

applies to both read and write operations.

Similar to all RAM blocks, M-RAM blocks can have different clocks on their inputs and outputs. Either of the two clocks feeding the block can clock M-RAM block registers (renwe, address, byte enable, datain, and output registers). The output register can be bypassed. The six labclk signals or local interconnect can drive the control signals for the A and B ports of the M-RAM block. ALMs can also control the clock\_a, clock\_b, renwe\_a, renwe\_b, clr\_a, clr\_b, clocken\_a, and clocken\_b signals, as shown in Figure 2–53.

Dedicated Row LAB Clocks Local Local Interconnect Interconnect clocken a clock\_b renwe a aclr b Local Local Interconnect Interconnect clocken b clock a aclr\_a renwe b

Figure 2-53. M-RAM Block Control Signals

The R4, R24, C4, and direct link interconnects from adjacent LABs on either the right or left side drive the M-RAM block local interconnect. Up to 16 direct link input connections to the M-RAM block are possible from the left adjacent LABs and another 16 possible from the right adjacent LAB. M-RAM block outputs can also connect to left and right LABs through direct link interconnect. Figure 2–54 shows an example floorplan for the EP2SGX130 device and the location of the M-RAM interfaces. Figures 2–55 and 2–56 show the interface between the M-RAM block and the logic array.

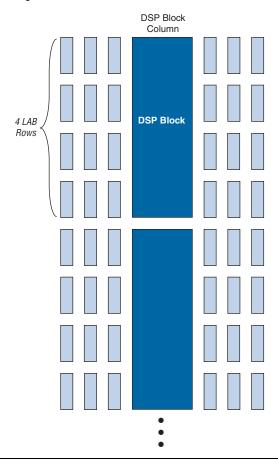

Figures 2–57 shows one of the columns with surrounding LAB rows.

Figure 2-57. DSP Blocks Arranged in Columns

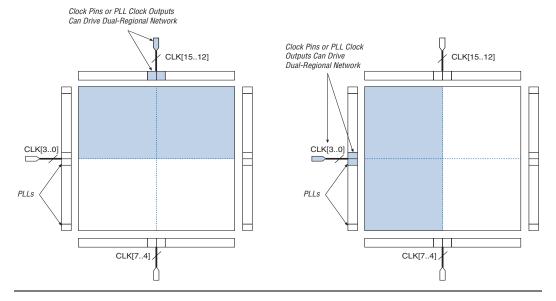

Figure 2-63. Dual-Regional Clocks

#### Combined Resources

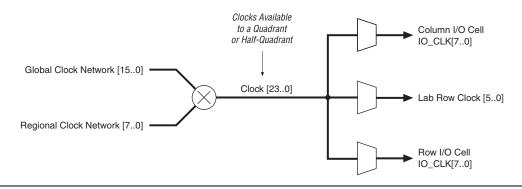

Within each quadrant, there are 24 distinct dedicated clocking resources consisting of 16 global clock lines and 8 regional clock lines. Multiplexers are used with these clocks to form buses to drive LAB row clocks, column IOE clocks, or row IOE clocks. Another multiplexer is used at the LAB level to select three of the six row clocks to feed the ALM registers in the LAB (see Figure 2–64).

Figure 2-64. Hierarchical Clock Networks per Quadrant

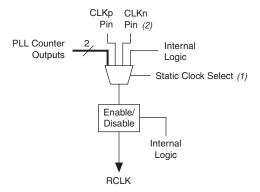

Figures 2–67 through 2–69 show the clock control block for the global clock, regional clock, and PLL external clock output, respectively.

Figure 2-67. Global Clock Control Blocks

#### *Notes to Figure 2–67:*

- These clock select signals can be dynamically controlled through internal logic when the device is operating in user mode.

- (2) These clock select signals can only be set through a configuration file (SRAM Object File [.sof] or Programmer Object File [.pof]) and cannot be dynamically controlled during user mode operation.

Figure 2-68. Regional Clock Control Blocks

#### *Notes to Figure 2–68:*

- These clock select signals can only be set through a configuration file (.sof or .pof) and cannot be dynamically

controlled during user mode operation.

- (2) Only the CLKn pins on the top and bottom of the device feed to regional clock select.

PLL Counter

Outputs (c[5..0])

6

Static Clock Select (1)

Enable/

Disable Internal

Logic

IOE (2)

Internal

Logic

Static Clock

Select (1)

PLL OUT

Figure 2-69. External PLL Output Clock Control Blocks

#### *Notes to Figure 2–69:*

- These clock select signals can only be set through a configuration file (.sof or .pof) and cannot be dynamically

controlled during user mode operation.

- (2) The clock control block feeds to a multiplexer within the PLL\_OUT pin's IOE. The PLL\_OUT pin is a dual-purpose pin. Therefore, this multiplexer selects either an internal signal or the output of the clock control block.

For the global clock control block, the clock source selection can be controlled either statically or dynamically. You have the option of statically selecting the clock source by using the Quartus II software to set specific configuration bits in the configuration file (.sof or .pof) or you can control the selection dynamically by using internal logic to drive the multiplexer select inputs. When selecting statically, the clock source can be set to any of the inputs to the select multiplexer. When selecting the clock source dynamically, you can either select between two PLL outputs (such as the C0 or C1 outputs from one PLL), between two PLLs (such as the C0/C1 clock output of one PLL or the C0/C1 clock output of the other PLL), between two clock pins (such as CLK0 or CLK1), or between a combination of clock pins or PLL outputs.

For the regional and PLL\_OUT clock control block, the clock source selection can only be controlled statically using configuration bits. Any of the inputs to the clock select multiplexer can be set as the clock source.

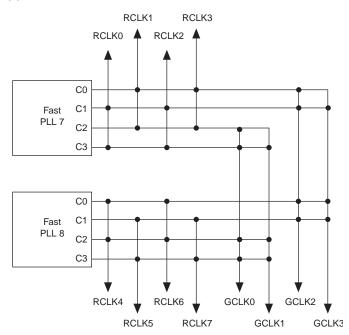

Figure 2–72. Global and Regional Clock Connections from Corner Clock Pins and Fast PLL Outputs Notes (1), (2)

#### *Notes to Figure 2–72:*

- (1) The global or regional clocks in a fast PLL's quadrant can drive the fast PLL input. A dedicated clock input pin or other PLL must drive the global or regional source. The source cannot be driven by internally generated logic before driving the fast PLL.

- (2) EP2SGX30C/D and EP2SGX60C/D devices only have two fast PLLs (1 and 2); they do not contain corner fast PLLs.

|          | <b>✓</b> |          |          |                                       | <b>✓</b> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |   |

|----------|----------|----------|----------|---------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---|

|          | <b>✓</b> |          |          |                                       | <b>/</b> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |   |

|          |          |          |          |                                       | 1        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |   |

|          |          | <b>✓</b> |          |                                       |          | <b>✓</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |   |

| <b>✓</b> |          |          | <b>✓</b> |                                       |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>✓</b> |   |

|          |          |          |          |                                       |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          | , |

|          | ✓<br>✓   | ✓ ✓ ✓ ✓  | ✓        | ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ | ✓        | \( \tag{ \tag}  \tag{ \tag{ \tag{ \tag{ \tag{ \tag{ \tag{ \tag{ \tag{ \ta | ✓        |   |

These dedicated circuits combined, with enhanced PLL clocking and phase-shift ability, provide a complete hardware solution for interfacing to high-speed memory.

For more information on external memory interfaces, refer to the *External Memory Interfaces in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II GX Device Handbook*.

## **Programmable Drive Strength**

The output buffer for each Stratix II GX device I/O pin has a programmable drive strength control for certain I/O standards. The LVTTL, LVCMOS, SSTL, and HSTL standards have several levels of drive strength that you can control. The default setting used in the Quartus II software is the maximum current strength setting that is used to achieve maximum I/O performance. For all I/O standards, the minimum setting is the lowest drive strength that guarantees the  $\rm I_{OH}/\rm I_{OL}$  of the standard. Using minimum settings provides signal slew rate control to reduce system noise and signal overshoot.

## 4. DC and Switching Characteristics

SIIGX51006-4.6

## Operating Conditions

Stratix<sup>®</sup> II GX devices are offered in both commercial and industrial grades. Industrial devices are offered in -4 speed grade and commercial devices are offered in -3 (fastest), -4, and -5 speed grades.

Tables 4–1 through 4–51 provide information on absolute maximum ratings, recommended operating conditions, DC electrical characteristics, and other specifications for Stratix II GX devices.

### **Absolute Maximum Ratings**

Table 4–1 contains the absolute maximum ratings for the Stratix II GX device family.

| Table 4–1          | Table 4–1. Stratix II GX Device Absolute Maximum Ratings       Notes (1), (2),(3) |                         |             |         |      |  |  |  |  |  |

|--------------------|-----------------------------------------------------------------------------------|-------------------------|-------------|---------|------|--|--|--|--|--|

| Symbol             | Parameter                                                                         | Conditions              | Minimum     | Maximum | Unit |  |  |  |  |  |

| V <sub>CCINT</sub> | Supply voltage                                                                    | With respect to ground  | -0.5        | 1.8     | V    |  |  |  |  |  |

| V <sub>CCIO</sub>  | Supply voltage                                                                    | With respect to ground  | -0.5        | 4.6     | V    |  |  |  |  |  |

| V <sub>CCPD</sub>  | Supply voltage                                                                    | With respect to ground  | -0.5        | 4.6     | V    |  |  |  |  |  |

| VI                 | DC input voltage (4)                                                              |                         | -0.5        | 4.6     | V    |  |  |  |  |  |

| I <sub>OUT</sub>   | DC output current, per pin                                                        |                         | -25         | 40      | mA   |  |  |  |  |  |

| T <sub>STG</sub>   | Storage temperature                                                               | No bias                 | -65         | 150     | С    |  |  |  |  |  |

| T <sub>J</sub>     | Junction temperature                                                              | BGA packages under bias | <b>-</b> 55 | 125     | С    |  |  |  |  |  |

#### Notes to Table 4-1:

- (1) See the Operating Requirements for Altera Devices Data Sheet for more information.

- (2) Conditions beyond those listed in Table 4–1 may cause permanent damage to a device. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse affects on the device.

- (3) Supply voltage specifications apply to voltage readings taken at the device pins, not at the power supply.

- (4) During transitions, the inputs may overshoot to the voltage shown in Table 4–2 based upon the input duty cycle. The DC case is equivalent to 100% duty cycle. During transitions, the inputs may undershoot to –2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

| Table 4-                           | -15. Typi | 5. Typical Pre-Emphasis (First Post-Tap), Note (1) (Part 2 of 2) |     |     |      |      |      |      |      |      |      |      |

|------------------------------------|-----------|------------------------------------------------------------------|-----|-----|------|------|------|------|------|------|------|------|

| V <sub>CCH</sub> TX<br>= 1.5 V     |           | First Post Tap Pre-Emphasis Level                                |     |     |      |      |      |      |      |      |      |      |

| V <sub>OD</sub><br>Setting<br>(mV) | 1         | 2                                                                | 3   | 4   | 5    | 6    | 7    | 8    | 9    | 10   | 11   | 12   |

| 600                                |           | 33%                                                              | 53% | 80% | 115% | 157% | 195% | 294% | 386% |      |      |      |

| 900                                |           | 19%                                                              | 28% | 38% | 56%  | 70%  | 86%  | 113% | 133% | 168% | 196% | 242% |

| 1200                               |           |                                                                  | 17% | 22% | 31%  | 40%  | 52%  | 62%  | 75%  | 86%  | 96%  | 112% |

Note to Table 4-15:

| Table 4-                           | -16. Typi | cal Pre-E                         | mphasis | (First Po | ost-Tap), | Note (1) |      |      |      |      |      |      |

|------------------------------------|-----------|-----------------------------------|---------|-----------|-----------|----------|------|------|------|------|------|------|

| V <sub>CCH</sub> TX<br>= 1.2 V     |           | First Post Tap Pre-Emphasis Level |         |           |           |          |      |      |      |      |      |      |

| V <sub>OD</sub><br>Setting<br>(mV) | 1         | 2                                 | 3       | 4         | 5         | 6        | 7    | 8    | 9    | 10   | 11   | 12   |

|                                    |           | TX Term = 100 $\Omega$            |         |           |           |          |      |      |      |      |      |      |

| 320                                | 24%       | 61%                               | 114%    |           |           |          |      |      |      |      |      |      |

| 480                                |           | 31%                               | 55%     | 86%       | 121%      | 170%     | 232% | 333% |      |      |      |      |

| 640                                |           | 20%                               | 35%     | 54%       | 72%       | 95%      | 124% | 157% | 195% | 233% | 307% | 373% |

| 800                                |           |                                   | 23%     | 36%       | 49%       | 64%      | 81%  | 97%  | 117% | 140% | 161% | 195% |

| 960                                |           |                                   | 18%     | 25%       | 35%       | 44%      | 57%  | 69%  | 82%  | 94%  | 108% | 127% |

*Note to Table 4–16:*

<sup>(1)</sup> Applicable to data rates from 600 Mbps to 6.375 Gbps. Specification is for measurement at the package ball.

<sup>(1)</sup> Applicable to data rates from 600 Mbps to 3.125 Gbps. Specification is for measurement at the package ball.

| Table 4–19. Strat                                | ix II GX Transceiver Bl                                                                                                                                                                                     | ock AC                                | Specif | ication | Notes (                                                 | 1), (2), | (3) <b>(P</b> | art 7 o | f 19)                      |       |      |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------|---------|---------------------------------------------------------|----------|---------------|---------|----------------------------|-------|------|

| Symbol/<br>Description                           | Conditions                                                                                                                                                                                                  | -3 Speed<br>Commercial Speed<br>Grade |        |         | -4 Speed<br>Commercial and<br>Industrial Speed<br>Grade |          |               |         | -5 Spe<br>nercial<br>Grade | Speed | Unit |

|                                                  |                                                                                                                                                                                                             | Min                                   | Тур    | Max     | Min                                                     | Тур      | Max           | Min     | Тур                        | Max   |      |

|                                                  | Jitter Frequency = 22.1 KHz Data Rate = 1.25, 2.5, 3.125 Gbps REFCLK = 125 MHz Pattern = CJPAT Equalizer Setting = 0 for 1.25 Gbps Equalizer Setting = 6 for 2.5 Gbps Equalizer Setting = 6 for 3.125 Gbps  |                                       | > 8.5  |         |                                                         | > 8.5    |               |         | > 8.5                      |       | UI   |

| Sinusoidal Jitter<br>Tolerance<br>(peak-to-peak) | Jitter Frequency = 1.875 MHz Data Rate = 1.25, 2.5, 3.125 Gbps REFCLK = 125 MHz Pattern = CJPAT Equalizer Setting = 0 for 1.25 Gbps Equalizer Setting = 6 for 2.5 Gbps Equalizer Setting = 6 for 3.125 Gbps |                                       | > 0.1  |         |                                                         | > 0.1    |               |         | > 0.1                      |       | UI   |

|                                                  | Jitter Frequency = 20 MHz Data Rate = 1.25, 2.5, 3.125 Gbps REFCLK = 125 MHz Pattern = CJPAT Equalizer Setting = 0 for 1.25 Gbps Equalizer Setting = 6 for 2.5 Gbps Equalizer Setting = 6 for 3.125 Gbps    |                                       | > 0.1  |         |                                                         | > 0.1    |               |         | > 0.1                      |       | UI   |

| Symbol/<br>Description                                                 | Conditions                                                                                                                                                                                                            | -3 Speed<br>Commercial Speed<br>Grade |       |     | -4 Speed<br>Commercial and<br>Industrial Speed<br>Grade |       |     | -5 Speed<br>Commercial Speed<br>Grade |     |     | Unit |

|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------|-----|---------------------------------------------------------|-------|-----|---------------------------------------|-----|-----|------|

|                                                                        |                                                                                                                                                                                                                       | Min                                   | Тур   | Max | Min                                                     | Тур   | Max | Min                                   | Тур | Max |      |

| Sinusoidal Jitter<br>Tolerance<br>(peak-to-peak) <i>(6)</i><br>(cont.) | Jitter Frequency = 20 MHz Data Rate = 614.4 Mbps, 1.2288 Gbps, 2.4576 Gbps REFCLK = 61.44 MHz for 614.4 Mbps REFCLK = 122.88 MHz for 1.2288 Gbps and 2.4576 Gbps Pattern = CJPAT Equalizer Setting = 6 DC Gain = 0 dB |                                       | > 0.1 |     |                                                         | > 0.1 |     |                                       | N/A |     | UI   |

- 3. Simulate the output driver of choice into the actual PCB trace and load, using the appropriate IBIS model or capacitance value to represent the load.

- 4. Record the time to  $V_{MEAS}$ .

- 5. Compare the results of steps 2 and 4. The increase or decrease in delay should be added to or subtracted from the I/O Standard Output Adder delays to yield the actual worst-case propagation delay (clock-to-output) of the PCB trace.

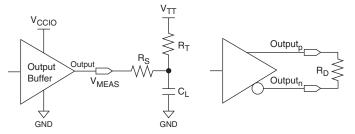

The Quartus II software reports the timing with the conditions shown in Table 4–53 using the above equation. Figure 4–8 shows the model of the circuit that is represented by the output timing of the Quartus II software.

Figure 4–8. Output Delay Timing Reporting Setup Modeled by Quartus II

Notes to Figure 4-8:

- (1) Output pin timing is reported at the output pin of the FPGA device. Additional delays for loading and board trace delay need to be accounted for with IBIS model simulations.

- (2) V<sub>CCPD</sub> is 3.085 V unless otherwise specified.

- (3)  $V_{CCINT}$  is 1.12 V unless otherwise specified.

| Table 4–53. Output Timing | Table 4–53. Output Timing Measurement Methodology for Output Pins (Part 1 of 2) Notes (1), (2), (3) |                         |               |                       |                     |                     |                       |  |  |

|---------------------------|-----------------------------------------------------------------------------------------------------|-------------------------|---------------|-----------------------|---------------------|---------------------|-----------------------|--|--|

| I/O Standard              |                                                                                                     | Loading and Termination |               |                       |                     |                     |                       |  |  |

| ·                         | <b>R</b> <sub>S</sub> (Ω)                                                                           | $R_D(\Omega)$           | $R_T(\Omega)$ | V <sub>CCIO</sub> (V) | V <sub>TT</sub> (V) | C <sub>L</sub> (pF) | V <sub>MEAS</sub> (V) |  |  |

| LVTTL (4)                 |                                                                                                     |                         |               | 3.135                 |                     | 0                   | 1.5675                |  |  |

| LVCMOS (4)                |                                                                                                     |                         |               | 3.135                 |                     | 0                   | 1.5675                |  |  |

| 2.5 V (4)                 |                                                                                                     |                         |               | 2.375                 |                     | 0                   | 1.1875                |  |  |

| 1.8 V (4)                 |                                                                                                     |                         |               | 1.710                 |                     | 0                   | 0.855                 |  |  |

| 1.5 V (4)                 |                                                                                                     |                         |               | 1.425                 |                     | 0                   | 0.7125                |  |  |

|                          | M512 Block Intern                                       |      |                       | 1    | •       | ,<br>   |         |         |         |      |

|--------------------------|---------------------------------------------------------|------|-----------------------|------|---------|---------|---------|---------|---------|------|

| Symbol                   | Parameter                                               |      | peed<br>de <i>(2)</i> |      | d Grade | -4 Spee | d Grade | -5 Spee | d Grade | Unit |

| •                        |                                                         | Min  | Max                   | Min  | Max     | Min     | Max     | Min     | Max     |      |

| t <sub>M512RC</sub>      | Synchronous read cycle time                             | 2089 | 2318                  | 2089 | 2433    | 2089    | 2587    | 2089    | 3104    | ps   |

| t <sub>M512WERESU</sub>  | Write or read<br>enable setup<br>time before clock      | 22   |                       | 23   |         | 24      |         | 29      |         | ps   |

| t <sub>M512WEREH</sub>   | Write or read<br>enable hold time<br>after clock        | 203  |                       | 213  |         | 226     |         | 272     |         | ps   |

| t <sub>M512DATASU</sub>  | Data setup time before clock                            | 22   |                       | 23   |         | 24      |         | 29      |         | ps   |

| t <sub>M512DATAH</sub>   | Data hold time after clock                              | 203  |                       | 213  |         | 226     |         | 272     |         | ps   |

| t <sub>M512WADDRSU</sub> | Write address<br>setup time before<br>clock             | 22   |                       | 23   |         | 24      |         | 29      |         | ps   |

| t <sub>M512WADDRH</sub>  | Write address<br>hold time after<br>clock               | 203  |                       | 213  |         | 226     |         | 272     |         | ps   |

| t <sub>M512RADDRSU</sub> | Read address<br>setup time before<br>clock              | 22   |                       | 23   |         | 24      |         | 29      |         | ps   |

| t <sub>M512RADDRH</sub>  | Read address<br>hold time after<br>clock                | 203  |                       | 213  |         | 226     |         | 272     |         | ps   |

| t <sub>M512DATACO1</sub> | Clock-to-output<br>delay when using<br>output registers | 298  | 478                   | 298  | 501     | 298     | 533     | 298     | 640     | ps   |

| t <sub>M512DATACO2</sub> | Clock-to-output<br>delay without<br>output registers    | 2102 | 2345                  | 2102 | 2461    | 2102    | 2616    | 2102    | 3141    | ps   |

| t <sub>M512CLKL</sub>    | Minimum clock low time                                  | 1315 |                       | 1380 |         | 1468    |         | 1762    |         | ps   |

| t <sub>M512CLKH</sub>    | Minimum clock high time                                 | 1315 |                       | 1380 |         | 1468    |         | 1762    |         | ps   |

| Table 4–88. Stratix I                | I GX Maximum Input | Clock Rate for Columi | n I/O Pins (Part 2 of 2 | )    |

|--------------------------------------|--------------------|-----------------------|-------------------------|------|

| I/O Standard                         | -3 Speed Grade     | -4 Speed Grade        | -5 Speed Grade          | Unit |

| Differential SSTL-18<br>Class I I    | 500                | 500                   | 500                     | MHz  |

| 1.8-V differential<br>HSTL Class I   | 500                | 500                   | 500                     | MHz  |

| 1.8-V differential<br>HSTL Class II  | 500                | 500                   | 500                     | MHz  |

| 1.5-V differential<br>HSTL Class I   | 500                | 500                   | 500                     | MHz  |

| 1.5-V differential<br>HSTL Class I I | 500                | 500                   | 500                     | MHz  |

| 1.2-V HSTL                           | 280                | 250                   | 250                     | MHz  |

| 1.2-V differential<br>HSTL           | 280                | 250                   | 250                     | MHz  |

Table 4–89 shows the maximum input clock toggle rates for Stratix II GX device row pins.

| Table 4–89. Stratix I          | II GX Maximum Input | Clock Rate for Row I/ | 0 Pins (Part 1 of 2) |      |

|--------------------------------|---------------------|-----------------------|----------------------|------|

| I/O Standard                   | -3 Speed Grade      | -4 Speed Grade        | -5 Speed Grade       | Unit |

| LVTTL                          | 500                 | 500                   | 450                  | MHz  |

| 2.5 V                          | 500                 | 500                   | 450                  | MHz  |

| 1.8 V                          | 500                 | 500                   | 450                  | MHz  |

| 1.5 V                          | 500                 | 500                   | 450                  | MHz  |

| LVCMOS                         | 500                 | 500                   | 450                  | MHz  |

| SSTL-2 Class I                 | 500                 | 500                   | 500                  | MHz  |

| SSTL-2 Class II                | 500                 | 500                   | 500                  | MHz  |

| SSTL-18 Class I                | 500                 | 500                   | 500                  | MHz  |

| SSTL-18 Class II               | 500                 | 500                   | 500                  | MHz  |

| 1.5-V HSTL Class I             | 500                 | 500                   | 500                  | MHz  |

| 1.5-V HSTL Class II            | 500                 | 500                   | 500                  | MHz  |

| 1.8-V HSTL Class I             | 500                 | 500                   | 500                  | MHz  |

| 1.8-V HSTL Class II            | 500                 | 500                   | 500                  | MHz  |

| PCI                            | 500                 | 500                   | 425                  | MHz  |

| PCI-X                          | 500                 | 500                   | 425                  | MHz  |

| Differential SSTL-2<br>Class I | 500                 | 500                   | 500                  | MHz  |

# 5. Reference and Ordering Information

SIIGX51007-1.3

## Software

Stratix ® II GX devices are supported by the Altera® Quartus® II design software, which provides a comprehensive environment for system-on-a-programmable-chip (SOPC) design. The Quartus II software includes HDL and schematic design entry, compilation and logic synthesis, full simulation and advanced timing analysis, SignalTap® II logic analyzer, and device configuration.

Refer to the *Quartus II Development Software Handbook* for more information on the *Quartus II software features*.

The Quartus II software supports the Windows XP/2000/NT, Sun Solaris 8/9, Linux Red Hat v7.3, Linux Red Hat Enterprise 3, and HP-UX operating systems. It also supports seamless integration with industry-leading EDA tools through the NativeLink interface.

## **Device Pin-Outs**

Stratix II GX device pin-outs (*Pin-Out Files for Altera Devices*) are available on the Altera web site at www.altera.com.

## Ordering Information

Figure 5–1 describes the ordering codes for Stratix II GX devices.

For more information on a specific package, refer to the *Package Information for Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II GX Device Handbook*.