# E·XFL

## Intel - EP2SGX90FF1508I4 Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Obsolete                                                    |

|--------------------------------|-------------------------------------------------------------|

| Number of LABs/CLBs            | 4548                                                        |

| Number of Logic Elements/Cells | 90960                                                       |

| Total RAM Bits                 | 4520448                                                     |

| Number of I/O                  | 650                                                         |

| Number of Gates                | -                                                           |

| Voltage - Supply               | 1.15V ~ 1.25V                                               |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                          |

| Package / Case                 | 1508-BBGA, FCBGA                                            |

| Supplier Device Package        | 1508-FBGA, FC (40x40)                                       |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2sgx90ff1508i4 |

|                                |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Support for multiple intellectual property megafunctions from Altera<sup>®</sup> MegaCore<sup>®</sup> functions and Altera Megafunction Partners Program (AMPP<sup>SM</sup>) megafunctions

- Support for design security using configuration bitstream encryption

- Support for remote configuration updates

- Transceiver block features:

- High-speed serial transceiver channels with clock data recovery (CDR) provide 600-megabits per second (Mbps) to 6.375-Gbps full-duplex transceiver operation per channel

- Devices available with 4, 8, 12, 16, or 20 high-speed serial transceiver channels providing up to 255 Gbps of serial bandwidth (full duplex)

- Dynamically programmable voltage output differential (V<sub>OD</sub>) and pre-emphasis settings for improved signal integrity

- Support for CDR-based serial protocols, including PCI Express, Gigabit Ethernet, SDI, Altera's SerialLite II, XAUI, CEI-6G, CPRI, Serial RapidIO, SONET/SDH

- Dynamic reconfiguration of transceiver channels to switch between multiple protocols and data rates

- Individual transmitter and receiver channel power-down capability for reduced power consumption during non-operation

- Adaptive equalization (AEQ) capability at the receiver to compensate for changing link characteristics

- Selectable on-chip termination resistors (100, 120, or 150 Ω) for improved signal integrity on a variety of transmission media

- Programmable transceiver-to-FPGA interface with support for 8-, 10-, 16-, 20-, 32-, and 40-bit wide data transfer

- 1.2- and 1.5-V pseudo current mode logic (PCML) for 600 Mbps to 6.375 Gbps (AC coupling)

- Receiver indicator for loss of signal (available only in PIPE mode)

- Built-in self test (BIST)

- Hot socketing for hot plug-in or hot swap and power sequencing support without the use of external devices

- Rate matcher, byte-reordering, bit-reordering, pattern detector, and word aligner support programmable patterns

- Dedicated circuitry that is compliant with PIPE, XAUI, and GIGE

- Built-in byte ordering so that a frame or packet always starts in a known byte lane

- Transmitters with two PLL inputs for each transceiver block with independent clock dividers to provide varying clock rates on each of its transmitters

# 2. Stratix II GX Architecture

#### SIIGX51003-2.2

## Transceivers

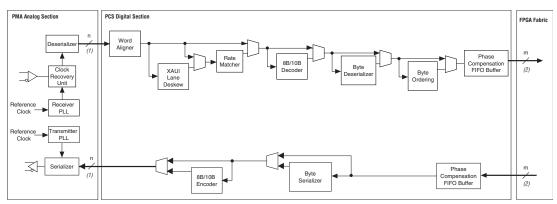

Stratix<sup>®</sup> II GX devices incorporate dedicated embedded circuitry on the right side of the device, which contains up to 20 high-speed 6.375-Gbps serial transceiver channels. Each Stratix II GX transceiver block contains four full-duplex channels and supporting logic to transmit and receive high-speed serial data streams. The transceivers deliver bidirectional point-to-point data transmissions, with up to 51 Gbps (6.375 Gbps per channel) of full-duplex data transmission per transceiver block. Figure 2–1 shows the function blocks that make up a transceiver channel within the Stratix II GX device.

Figure 2–1. Stratix II GX Transceiver Block Diagram

#### Notes to Figure 2–1:

- (1) n represents the number of bits in each word that need to be serialized by the transmitter portion of the PMA or have been deserialized by the receiver portion of the PMA. n = 8, 10, 16, or 20.

- (2) m represents the number of bits in the word that pass between the FPGA logic and the PCS portion of the transceiver. m = 8, 10, 16, 20, 32, or 40.

Transceivers within each block are independent and have their own set of dividers. Therefore, each transceiver can operate at different frequencies. Each block can select from two reference clocks to provide two clock domains that each transceiver can select from.

•

.

|                         | Clock R      | esource           |                        | Transceiver            |                        |  |  |  |  |

|-------------------------|--------------|-------------------|------------------------|------------------------|------------------------|--|--|--|--|

| Region                  | Global Clock | Regional<br>Clock | Bank 13<br>8 Clock I/O | Bank 14<br>8 Clock I/O | Bank 15<br>8 Clock I/O |  |  |  |  |

| Region0<br>8 LRIO clock | ~            | RCLK 20-27        | $\checkmark$           |                        |                        |  |  |  |  |

| Region1<br>8 LRIO clock | ~            | RCLK 20-27        | ~                      | $\checkmark$           |                        |  |  |  |  |

| Region2<br>8 LRIO clock | ~            | RCLK 12-19        |                        | $\checkmark$           | ~                      |  |  |  |  |

| Region3<br>8 LRIO clock | ~            | RCLK 12-19        |                        |                        | $\checkmark$           |  |  |  |  |

| Table 2–14. Avai        | ilable Clocking | g Connections f   | or Transceiver         | rs in 2SGX90F          |                        |                        |  |  |  |  |

|-------------------------|-----------------|-------------------|------------------------|------------------------|------------------------|------------------------|--|--|--|--|

|                         | Clock           | Resource          |                        | Transceiver            |                        |                        |  |  |  |  |

| Region                  | Global<br>Clock | Regional<br>Clock | Bank 13<br>8 Clock I/O | Bank 14<br>8 Clock I/O | Bank 15<br>8 clock I/O | Bank 16<br>8 Clock I/O |  |  |  |  |

| Region0<br>8 LRIO clock | $\checkmark$    | RCLK 20-27        | $\checkmark$           |                        |                        |                        |  |  |  |  |

| Region1<br>8 LRIO clock | $\checkmark$    | RCLK 20-27        |                        | $\checkmark$           |                        |                        |  |  |  |  |

| Region2<br>8 LRIO clock | $\checkmark$    | RCLK 12-19        |                        |                        | ~                      |                        |  |  |  |  |

| Region3<br>8 LRIO clock | $\checkmark$    | RCLK 12-19        |                        |                        |                        | $\checkmark$           |  |  |  |  |

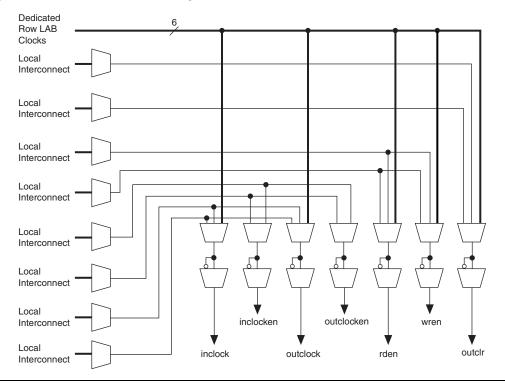

M512 RAM blocks can have different clocks on its inputs and outputs. The wren, datain, and write address registers are all clocked together from one of the two clocks feeding the block. The read address, rden, and output registers can be clocked by either of the two clocks driving the block, allowing the RAM block to operate in read and write or input and output clock modes. Only the output register can be bypassed. The six labclk signals or local interconnect can drive the inclock, outclock, wren, rden, and outclr signals. Because of the advanced interconnect between the LAB and M512 RAM blocks, ALMs can also control the wren and rden signals and the RAM clock, clock enable, and asynchronous clear signals. Figure 2–49 shows the M512 RAM block control signal generation logic.

Figure 2–49. M512 RAM Block Control Signals

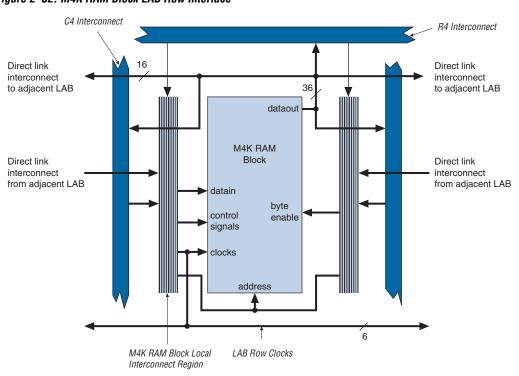

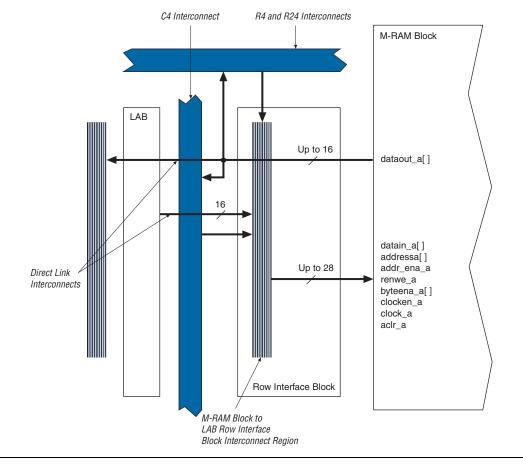

Figure 2–52. M4K RAM Block LAB Row Interface

### **M-RAM Block**

The largest TriMatrix memory block, the M-RAM block, is useful for applications where a large volume of data must be stored on-chip. Each block contains 589,824 RAM bits (including parity bits). The M-RAM block can be configured in the following modes:

- True dual-port RAM

- Simple dual-port RAM

- Single-port RAM

- FIFO

You cannot use an initialization file to initialize the contents of a M-RAM block. All M-RAM block contents power up to an undefined value. Only synchronous operation is supported in the M-RAM block, so all inputs are registered. Output registers can be bypassed.

Figure 2–56. M-RAM Row Unit Interface to Interconnect

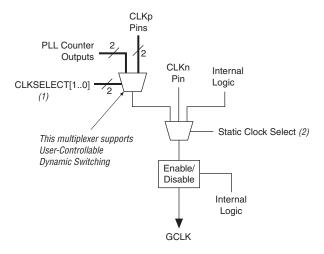

Figures 2–67 through 2–69 show the clock control block for the global clock, regional clock, and PLL external clock output, respectively.

#### Figure 2–67. Global Clock Control Blocks

#### Notes to Figure 2–67:

- These clock select signals can be dynamically controlled through internal logic when the device is operating in user mode.

- (2) These clock select signals can only be set through a configuration file (SRAM Object File [.sof] or Programmer Object File [.pof]) and cannot be dynamically controlled during user mode operation.

#### Figure 2–68. Regional Clock Control Blocks

#### Notes to Figure 2-68:

- (1) These clock select signals can only be set through a configuration file (**.sof** or **.pof**) and cannot be dynamically controlled during user mode operation.

- (2) Only the CLKn pins on the top and bottom of the device feed to regional clock select.

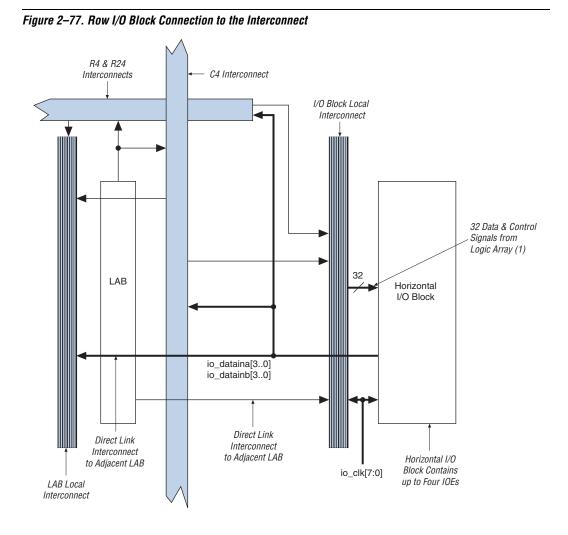

Figure 2–77 shows how a row I/O block connects to the logic array.

#### *Note to Figure 2–77:*

(1) The 32 data and control signals consist of eight data out lines: four lines each for DDR applications io\_dataouta[3..0] and io\_dataoutb[3..0], four output enables io\_oe[3..0], four input clock enables io\_ce\_in[3..0], four output clock enables io\_ce\_out[3..0], four clocks io\_clk[3..0], four asynchronous clear and preset signals io\_aclr/apreset[3..0], and four synchronous clear and preset signals io\_sclr/spreset[3..0].

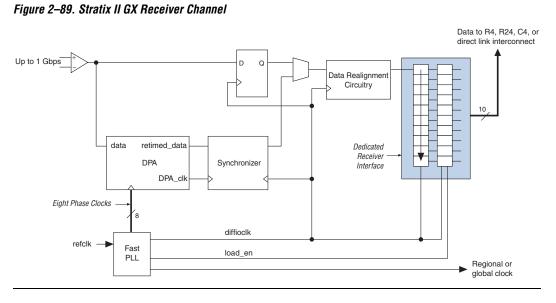

Figure 2–89 shows the block diagram of the Stratix II GX receiver channel.

An external pin or global or regional clock can drive the fast PLLs, which can output up to three clocks: two multiplied high-speed clocks to drive the SERDES block and/or external pin, and a low-speed clock to drive the logic array. In addition, eight phase-shifted clocks from the VCO can feed to the DPA circuitry.

•••

For more information on the fast PLL, see the *PLLs in Stratix II GX Devices* chapter in volume 2 of the *Stratix II GX Handbook*.

The eight phase-shifted clocks from the fast PLL feed to the DPA block. The DPA block selects the closest phase to the center of the serial data eye to sample the incoming data. This allows the source-synchronous circuitry to capture incoming data correctly regardless of the channel-to-channel or clock-to-channel skew. The DPA block locks to a phase closest to the serial data phase. The phase-aligned DPA clock is used to write the data into the synchronizer.

The synchronizer sits between the DPA block and the data realignment and SERDES circuitry. Since every channel utilizing the DPA block can have a different phase selected to sample the data, the synchronizer is needed to synchronize the data to the high-speed clock domain of the data realignment and the SERDES circuitry.

- Stratix II Performance and Logic Efficiency Analysis White Paper

- TriMatrix Embedded Memory Blocks in Stratix II & Stratix II GX Devices chapter in volume 2 of the Stratix II GX Device Handbook

## Document Revision History

Table 2–42 shows the revision history for this chapter.

| Table 2–42. Docu                | ment Revision History (Part 1 of 6)                                                                                                                                                                                                                     |                    |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Date and<br>Document<br>Version | Changes Made                                                                                                                                                                                                                                            | Summary of Changes |

| October 2007,<br>v2.2           | Updated:<br>• "Programmable Pull-Up Resistor"<br>• "Reverse Serial Pre-CDR Loopback"<br>• "Receiver Input Buffer"<br>• "Pattern Detection"<br>• "Control and Status Signals"<br>• "Individual Power Down and Reset for the<br>Transmitter and Receiver" |                    |

|                                 | Updated:<br>• Figure 2–14<br>• Figure 2–26<br>• Figure 2–27<br>• Figure 2–86 (notes only)<br>• Figure 2–87                                                                                                                                              |                    |

|                                 | Updated:<br>• Table 2–4<br>• Table 2–7                                                                                                                                                                                                                  |                    |

|                                 | Removed note from Table 2–31.                                                                                                                                                                                                                           |                    |

|                                 | Removed Tables 2-2, 2-7, and 2-8.                                                                                                                                                                                                                       |                    |

| August 2007, v2.1               | Minor text edits.<br>Added "Reverse Serial Pre-CDR Loopback"<br>section.                                                                                                                                                                                |                    |

|                                 | Updated Table 2–2.                                                                                                                                                                                                                                      |                    |

|                                 | Added "Referenced Documents" section.                                                                                                                                                                                                                   |                    |

# 3. Configuration & Testing

SIIGX51005-1.4

# IEEE Std. 1149.1 JTAG Boundary-Scan Support

All Stratix<sup>®</sup> II GX devices provide Joint Test Action Group (JTAG) boundary-scan test (BST) circuitry that complies with the IEEE Std. 1149.1. You can perform JTAG boundary-scan testing either before or after, but not during configuration. Stratix II GX devices can also use the JTAG port for configuration with the Quartus<sup>®</sup> II software or hardware using either Jam Files (.**jam**) or Jam Byte-Code Files (.**jbc**).

Stratix II GX devices support IOE I/O standard setting reconfiguration through the JTAG BST chain. The JTAG chain can update the I/O standard for all input and output pins any time before or during user mode through the CONFIG\_IO instruction. You can use this capability for JTAG testing before configuration when some of the Stratix II GX pins drive or receive from other devices on the board using voltage-referenced standards. Since the Stratix II GX device may not be configured before JTAG testing, the I/O pins may not be configured for appropriate electrical standards for chip-to-chip communication. Programming these I/O standards via JTAG allows you to fully test I/O connections to other devices.

A device operating in JTAG mode uses four required pins, TDI, TDO, TMS, and TCK, and one optional pin, TRST. The TCK pin has an internal weak pull-down resistor, while the TDI, TMS, and TRST pins have weak internal pull-up resistors. The JTAG input pins are powered by the 3.3-V VCCPD pins. The TDO output pin is powered by the VCCIO power supply in I/O bank 4.

Stratix II GX devices also use the JTAG port to monitor the logic operation of the device with the SignalTap<sup>®</sup> II embedded logic analyzer. Stratix II GX devices support the JTAG instructions shown in Table 3–1.

Stratix II GX devices must be within the first eight devices in a JTAG chain. All of these devices have the same JTAG controller. If any of the Stratix II GX devices appear after the eighth device in the JTAG chain, they will fail configuration. This does not affect SignalTap II embedded logic analysis.

| Table 4–2. | Maximum Duty Cycles i  | in Voltage Trans       | itions                         |

|------------|------------------------|------------------------|--------------------------------|

| Symbol     | Parameter              | Condition              | Maximum Duty Cycles<br>(%) (1) |

| VI         | Maximum duty cycles    | V <sub>I</sub> = 4.0 V | 100                            |

|            | in voltage transitions | V <sub>I</sub> = 4.1 V | 90                             |

|            |                        | V <sub>I</sub> = 4.2 V | 50                             |

|            |                        | V <sub>I</sub> = 4.3 V | 30                             |

|            |                        | $V_{I} = 4.4 V$        | 17                             |

|            |                        | V <sub>I</sub> = 4.5 V | 10                             |

Note to Table 4–2:

ſ

(1) During transition, the inputs may overshoot to the voltages shown based on the input duty cycle. The duty cycle case is equivalent to 100% duty cycle.

## **Recommended Operating Conditions**

Table 4–3 contains the Stratix II GX device family recommended operating conditions.

| Table 4–           | 3. Stratix II GX Device Recomme                                                     | nded Operating Conditions (Part                   | 1 of 2) A       | lote (1)          |      |

|--------------------|-------------------------------------------------------------------------------------|---------------------------------------------------|-----------------|-------------------|------|

| Symbol             | Parameter                                                                           | Conditions                                        | Minimum         | Maximum           | Unit |

| V <sub>CCINT</sub> | Supply voltage for internal logic and input buffers                                 | 100 μs ≤rise time ≤100 ms <i>(3)</i>              | 1.15            | 1.25              | V    |

| V <sub>CCIO</sub>  | Supply voltage for output<br>buffers, 3.3-V operation                               | 100 μs ⊴rise time ≤100 ms <i>(3)</i> , <i>(6)</i> | 3.135<br>(3.00) | 3.465<br>(3.60)   | V    |

|                    | Supply voltage for output<br>buffers, 2.5-V operation                               | 100 μs ⊴rise time ≤100 ms <i>(3)</i>              | 2.375           | 2.625             | V    |

|                    | Supply voltage for output buffers, 1.8-V operation                                  | 100 μs ⊴rise time ≤100 ms <i>(3)</i>              | 1.71            | 1.89              | V    |

|                    | Supply voltage for output buffers, 1.5-V operation                                  | 100 μs ⊴rise time ≤100 ms <i>(3)</i>              | 1.425           | 1.575             | V    |

|                    | Supply voltage for output buffers, 1.2-V operation                                  | 100 μs ≤rise time ≤100 ms <i>(3)</i>              | 1.15            | 1.25              | V    |

| V <sub>CCPD</sub>  | Supply voltage for pre-drivers as<br>well as configuration and JTAG<br>I/O buffers. | 100 μs ⊴rise time ≤100 ms <i>(4)</i>              | 3.135           | 3.465             | V    |

| VI                 | Input voltage (see Table 4-2)                                                       | (2), (5)                                          | -0.5            | 4.0               | V    |

| Vo                 | Output voltage                                                                      |                                                   | 0               | V <sub>CCIO</sub> | V    |

| Symbol/<br>Description       | Conditions                                                                               |                  | -3 Speed<br>Commercial Speed<br>Grade |      | -4 Speed<br>Commercial and<br>Industrial Speed<br>Grade |        |      | -5 Speed<br>Commercial Speed<br>Grade |       |      | Unit |

|------------------------------|------------------------------------------------------------------------------------------|------------------|---------------------------------------|------|---------------------------------------------------------|--------|------|---------------------------------------|-------|------|------|

|                              |                                                                                          | Min              | Тур                                   | Max  | Min                                                     | Тур    | Max  | Min                                   | Тур   | Max  |      |

| Fibre Channel Tra            | nsmit Jitter Generat                                                                     | ion <i>(8)</i> , | (17)                                  |      |                                                         |        |      |                                       |       |      |      |

| Total jitter FC-1            | REFCLK =<br>106.25 MHz<br>Pattern = CRPAT<br>V <sub>OD</sub> = 800 mV<br>No Pre-emphasis | -                | -                                     | 0.23 | -                                                       | -      | 0.23 | -                                     | -     | 0.23 | UI   |

| Deterministic jitter<br>FC-1 | REFCLK =<br>106.25 MHz<br>Pattern = CRPAT<br>V <sub>OD</sub> = 800 mV<br>No Pre-emphasis | -                | -                                     | 0.11 | -                                                       | -      | 0.11 | -                                     | -     | 0.11 | UI   |

| Total jitter FC-2            | REFCLK =<br>106.25 MHz<br>Pattern = CRPAT<br>V <sub>OD</sub> = 800 mV<br>No Pre-emphasis | -                | -                                     | 0.33 | -                                                       | -      | 0.33 | -                                     | -     | 0.33 | UI   |

| Deterministic jitter<br>FC-2 | REFCLK =<br>106.25 MHz<br>Pattern = CRPAT<br>V <sub>OD</sub> = 800 mV<br>No Pre-emphasis | -                | -                                     | 0.2  | -                                                       | -      | 0.2  | -                                     | -     | 0.2  | UI   |

| Total jitter FC-4            | REFCLK =<br>106.25 MHz<br>Pattern = CRPAT<br>V <sub>OD</sub> = 800 mV<br>No Pre-emphasis | -                | -                                     | 0.52 | -                                                       | -      | 0.52 | -                                     | -     | 0.52 | UI   |

| Deterministic jitter<br>FC-4 | REFCLK =<br>106.25 MHz<br>Pattern = CRPAT<br>V <sub>OD</sub> = 800 mV<br>No Pre-emphasis | -                | -                                     | 0.33 | -                                                       | -      | 0.33 | -                                     | -     | 0.33 | UI   |

| Fibre Channel Rec            | eiver Jitter Tolerand                                                                    | e (8), (         | 18)                                   |      |                                                         |        |      |                                       |       |      |      |

| Deterministic jitter<br>FC-1 | Pattern = CJTPAT<br>No Equalization<br>DC Gain = 0 dB                                    |                  | > 0.37                                | 7    |                                                         | > 0.37 | 7    |                                       | > 0.3 | 7    | UI   |

| Random jitter FC-<br>1       | Pattern = CJTPAT<br>No Equalization<br>DC Gain = 0 dB                                    |                  | > 0.31                                | l    |                                                         | > 0.31 | l    |                                       | > 0.3 | 1    | UI   |

| Symbol/<br>Description                                            | Conditions                                                                                                                                  |     | -3 Speed<br>Commercial Speed<br>Grade |     |     | -4 Speed<br>Commercial and<br>Industrial Speed<br>Grade |     |     | -5 Spe<br>nercia<br>Grado | l Speed | Unit |

|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------------|-----|-----|---------------------------------------------------------|-----|-----|---------------------------|---------|------|

|                                                                   |                                                                                                                                             | Min | Тур                                   | Max | Min | Тур                                                     | Max | Min | Тур                       | Max     |      |

| HiGig Receiver Jit                                                | ter Tolerance (13)                                                                                                                          |     |                                       |     |     |                                                         |     |     |                           |         |      |

| Deterministic Jitter<br>Tolerance<br>(peak-to-peak)               | Data Rate =<br>3.75 Gbps<br>REFCLK =<br>187.5 MHz<br>Pattern = CJPAT<br>No Equalization<br>DC Gain = 3 dB                                   |     | > 0.37                                |     |     | -                                                       |     |     | -                         |         | UI   |

| Contrinut                                                         | Data Rate =<br>3.75 Gbps<br>REFCLK =<br>187.5 MHz<br>Pattern = CJPAT<br>No Equalization<br>DC Gain = 3 dB                                   |     | > 0.65                                | i   |     | -                                                       |     |     | -                         |         | UI   |

| Deterministic and<br>Random Jitter<br>Tolerance<br>(peak-to-peak) | Jitter Frequency =<br>22.1 KHz<br>Data Rate =<br>3.75 Gbps<br>REFCLK =<br>187.5 MHz<br>Pattern = CJPAT<br>No Equalization<br>DC Gain = 3 dB |     | > 8.5                                 |     |     | -                                                       |     |     | -                         |         | UI   |

June 2009

| Symbol/<br>Description                              | Conditions                                                                                                                                   |      | -3 Speed<br>Commercial Speed<br>Grade |     |     | -4 Speed<br>Commercial and<br>Industrial Speed<br>Grade |     |     | -5 Speed<br>Commercial Speed<br>Grade |     |    |

|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------------------------|-----|-----|---------------------------------------------------------|-----|-----|---------------------------------------|-----|----|

|                                                     |                                                                                                                                              | Min  | Тур                                   | Max | Min | Тур                                                     | Max | Min | Тур                                   | Max |    |

| Sinusoidal Jitter                                   | Jitter Frequency =<br>1.875 MHz<br>Data Rate =<br>3.75 Gbps<br>REFCLK =<br>187.5 MHz<br>Pattern = CJPAT<br>No Equalization<br>DC Gain = 3 dB |      | > 0.1                                 |     |     | -                                                       |     |     | -                                     |     | UI |

| Tolerance<br>(peak-to-peak)                         | Jitter Frequency =<br>20 MHz<br>Data Rate =<br>3.75 Gbps<br>REFCLK =<br>187.5 MHz<br>Pattern = CJPAT<br>No Equalization<br>DC Gain = 3 dB    |      | > 0.1                                 |     |     | -                                                       |     |     | -                                     |     | UI |

| (OIF) CEI Transmi                                   | tter Jitter Generation                                                                                                                       | (14) |                                       |     | 1   |                                                         |     | 1   |                                       |     |    |

| Total Jitter<br>(peak-to-peak)                      | Data Rate =<br>6.375 Gbps<br>REFCLK =<br>318.75 MHz<br>Pattern = PRBS15<br>Vod=1000 mV (5)<br>NoPre-emphasis<br>BER = 10 <sup>-12</sup>      |      |                                       | 0.3 |     |                                                         | N/A |     |                                       | N/A | UI |

| (OIF) CEI Receive                                   | r Jitter Tolerance (14)                                                                                                                      | )    |                                       | •   | •   |                                                         | •   | •   |                                       |     |    |

| Deterministic Jitter<br>Tolerance<br>(peak-to-peak) | Data Rate =<br>6.375 Gbps<br>Pattern = PRBS31<br>Equalizer Setting =<br>15<br>DCGain = 0 dB<br>BER = $10^{-12}$                              |      | > 0.67                                | 5   |     | N/A                                                     |     |     | N/A                                   |     | UI |

| Table 4–59.          | Table 4–59. M512 Block Internal Timing Microparameters (Part 2 of 2) |     |                       |     |               |                |     |                |     |      |  |  |  |

|----------------------|----------------------------------------------------------------------|-----|-----------------------|-----|---------------|----------------|-----|----------------|-----|------|--|--|--|

| Symbol               | Parameter                                                            |     | peed<br>le <i>(2)</i> |     | d Grade<br>3) | -4 Speed Grade |     | -5 Speed Grade |     | Unit |  |  |  |

| -,                   |                                                                      | Min | Max                   | Min | Max           | Min            | Max | Min            | Max |      |  |  |  |

| t <sub>M512CLR</sub> | Minimum clear<br>pulse width                                         | 144 |                       | 151 |               | 160            |     | 192            |     | ps   |  |  |  |

(1) The M512 block  $f_{MAX}$  obtained using the Quartus II software does not necessarily equal to 1/TM512RC.

(2) This column refers to -3 speed grades for EP2SGX30, EP2SGX60, and EP2SGX90 devices.

(3) This column refers to -3 speed grades for EP2SGX130 devices.

| Symbol                  | Parameter                                          | -3 Speed Grade<br>(2) |      |      | -3 Speed Grade<br>(3) |      | -4 Speed Grade |      | -5 Speed Grade |    |

|-------------------------|----------------------------------------------------|-----------------------|------|------|-----------------------|------|----------------|------|----------------|----|

|                         |                                                    | Min                   | Max  | Min  | Max                   | Min  | Max            | Min  | Max            |    |

| t <sub>M4KRC</sub>      | Synchronous<br>read cycle time                     | 1462                  | 2240 | 1462 | 2351                  | 1462 | 2500           | 1462 | 3000           | ps |

| t <sub>M4KWERESU</sub>  | Write or read<br>enable setup<br>time before clock | 22                    |      | 23   |                       | 24   |                | 29   |                | ps |

| t <sub>M4KWEREH</sub>   | Write or read<br>enable hold time<br>after clock   | 203                   |      | 213  |                       | 226  |                | 272  |                | ps |

| t <sub>M4KBESU</sub>    | Byte enable<br>setup time before<br>clock          | 22                    |      | 23   |                       | 24   |                | 29   |                | ps |

| t <sub>M4KBEH</sub>     | Byte enable hold time after clock                  | 203                   |      | 213  |                       | 226  |                | 272  |                | ps |

| t <sub>M4KDATAASU</sub> | A port data setup time before clock                | 22                    |      | 23   |                       | 24   |                | 29   |                | ps |

| t <sub>M4KDATAAH</sub>  | A port data hold time after clock                  | 203                   |      | 213  |                       | 226  |                | 272  |                | ps |

| t <sub>M4KADDRASU</sub> | A port address<br>setup time before<br>clock       | 22                    |      | 23   |                       | 24   |                | 29   |                | ps |

| t <sub>M4KADDRAH</sub>  | A port address<br>hold time after<br>clock         | 203                   |      | 213  |                       | 226  |                | 272  |                | ps |

| t <sub>M4KDATABSU</sub> | B port data setup time before clock                | 22                    |      | 23   |                       | 24   |                | 29   |                | ps |

Therefore, the DCD percentage for the output clock is from 48.4% to 51.6%.

Table 4–101. Maximum DCD for DDIO Output on Row I/O Pins Without PLL in the Clock Path for -4 and -5DevicesNote (1)

| Maximum DCD (ps) for |          | Input I/O Sta | ndard (No Pl | L in the Clock F | Path) |      |

|----------------------|----------|---------------|--------------|------------------|-------|------|

| Row DDIO Output I/O  | TTL/0    | CMOS          | SSTL-2       | SSTL/HSTL        | LVDS  | Unit |

| Standard             | 3.3/2.5V | 1.8/1.5V      | 2.5V         | 1.8/1.5V         | 3.3V  |      |

| 3.3-V LVTTL          | 440      | 495           | 170          | 160              | 105   | ps   |

| 3.3-V LVCMOS         | 390      | 450           | 120          | 110              | 75    | ps   |

| 2.5 V                | 375      | 430           | 105          | 95               | 90    | ps   |

| 1.8 V                | 325      | 385           | 90           | 100              | 135   | ps   |

| 1.5-V LVCMOS         | 430      | 490           | 160          | 155              | 100   | ps   |

| SSTL-2 Class I       | 355      | 410           | 85           | 75               | 85    | ps   |

| SSTL-2 Class II      | 350      | 405           | 80           | 70               | 90    | ps   |

| SSTL-18 Class I      | 335      | 390           | 65           | 65               | 105   | ps   |

| 1.8-V HSTL Class I   | 330      | 385           | 60           | 70               | 110   | ps   |

| 1.5-V HSTL Class I   | 330      | 390           | 60           | 70               | 105   | ps   |

| LVDS                 | 180      | 180           | 180          | 180              | 180   | ps   |

(1) Table 4–101 assumes the input clock has zero DCD.

Table 4–102. Maximum DCD for DDIO Output on Column I/O Pins Without PLL in the Clock Path for -3

Devices (Part 1 of 2)

Note (1)

| Maximum DCD (ps) for<br>DDIO Column Output I/O<br>Standard | Input IO Standard (No PLL in the Clock Path) |          |        |              |        |      |  |

|------------------------------------------------------------|----------------------------------------------|----------|--------|--------------|--------|------|--|

|                                                            | TTL/CMOS                                     |          | SSTL-2 | SSTL/HSTL    | HSTL12 | Unit |  |

|                                                            | 3.3/2.5V                                     | 1.8/1.5V | 2.5V   | .5V 1.8/1.5V |        |      |  |

| 3.3-V LVTTL                                                | 260                                          | 380      | 145    | 145          | 145    | ps   |  |

| 3.3-V LVCMOS                                               | 210                                          | 330      | 100    | 100          | 100    | ps   |  |

| 2.5 V                                                      | 195                                          | 315      | 85     | 85           | 85     | ps   |  |

| 1.8 V                                                      | 150                                          | 265      | 85     | 85           | 85     | ps   |  |

| 1.5-V LVCMOS                                               | 255                                          | 370      | 140    | 140          | 140    | ps   |  |

| SSTL-2 Class I                                             | 175                                          | 295      | 65     | 65           | 65     | ps   |  |

| SSTL-2 Class II                                            | 170                                          | 290      | 60     | 60           | 60     | ps   |  |

| SSTL-18 Class I                                            | 155                                          | 275      | 55     | 50           | 50     | ps   |  |

| Maximum DCD (ps) for<br>DDIO Column Output I/O<br>Standard | Note (1) Input IO Standard (No PLL in the Clock Path) |          |        |           |        |      |

|------------------------------------------------------------|-------------------------------------------------------|----------|--------|-----------|--------|------|

|                                                            | TTL/CMOS                                              |          | SSTL-2 | SSTL/HSTL | HSTL12 | Unit |

|                                                            | 3.3/2.5V                                              | 1.8/1.5V | 2.5V   | 1.8/1.5V  | 1.2V   |      |

| SSTL-18 Class II                                           | 140                                                   | 260      | 70     | 70        | 70     | ps   |

| 1.8-V HSTL Class I                                         | 150                                                   | 270      | 60     | 60        | 60     | ps   |

| 1.8-V HSTL Class II                                        | 150                                                   | 270      | 60     | 60        | 60     | ps   |

| 1.5-V HSTL Class I                                         | 150                                                   | 270      | 55     | 55        | 55     | ps   |

| 1.5-V HSTL Class II                                        | 125                                                   | 240      | 85     | 85        | 85     | ps   |

| 1.2-V HSTL                                                 | 240                                                   | 360      | 155    | 155       | 155    | ps   |

| LVPECL                                                     | 180                                                   | 180      | 180    | 180       | 180    | ps   |

Table A 109 Maximum DCD for DDIO Output on Column 1/0 Bins Without DLL in the Clock Both for 2

(1) Table 4–102 assumes the input clock has zero DCD.

Table 4–103. Maximum DCD for DDIO Output on Column I/O Pins Without PLL in the Clock Path for -4 and -5 Devices Note (1)

| Maximum DCD (ps) for<br>DDIO Column Output I/O | Input IO Standard (No PLL in the Clock Path) |          |        |           |      |  |

|------------------------------------------------|----------------------------------------------|----------|--------|-----------|------|--|

|                                                | TTL/(                                        | CMOS     | SSTL-2 | SSTL/HSTL | Unit |  |

| Standard                                       | 3.3/2.5V                                     | 1.8/1.5V | 2.5V   | 1.8/1.5V  |      |  |

| 3.3-V LVTTL                                    | 440                                          | 495      | 170    | 160       | ps   |  |

| 3.3-V LVCMOS                                   | 390                                          | 450      | 120    | 110       | ps   |  |

| 2.5 V                                          | 375                                          | 430      | 105    | 95        | ps   |  |

| 1.8 V                                          | 325                                          | 385      | 90     | 100       | ps   |  |

| 1.5-V LVCMOS                                   | 430                                          | 490      | 160    | 155       | ps   |  |

| SSTL-2 Class I                                 | 355                                          | 410      | 85     | 75        | ps   |  |

| SSTL-2 Class II                                | 350                                          | 405      | 80     | 70        | ps   |  |

| SSTL-18 Class I                                | 335                                          | 390      | 65     | 65        | ps   |  |

| SSTL-18 Class II                               | 320                                          | 375      | 70     | 80        | ps   |  |

| 1.8-V HSTL Class I                             | 330                                          | 385      | 60     | 70        | ps   |  |

| 1.8-V HSTL Class II                            | 330                                          | 385      | 60     | 70        | ps   |  |

| 1.5-V HSTL Class I                             | 330                                          | 390      | 60     | 70        | ps   |  |

| 1.5-V HSTL Class II                            | 330                                          | 360      | 90     | 100       | ps   |  |

| LVPECL                                         | 180                                          | 180      | 180    | 180       | ps   |  |

(1) Table 4–103 assumes the input clock has zero DCD.

Table 4–108 shows the high-speed I/O timing specifications for -4 speed grade Stratix II GX devices.

| • • •                                | Conditions                                        |                          |      |       | peed C |       |                       |

|--------------------------------------|---------------------------------------------------|--------------------------|------|-------|--------|-------|-----------------------|

| Symbol                               |                                                   |                          |      |       | Тур    | Max   | Unit                  |

| $f_{IN} = f_{HSDR} / W$              | W = 2 to 32 (LVDS, HyperTransport technology) (3) |                          |      | 16    |        | 520   | MHz                   |

|                                      | W = 1 (SERDES bypass, LVDS only)                  |                          |      |       |        | 500   | MHz                   |

|                                      | W = 1 (SERDES us                                  | 150                      |      | 717   | MHz    |       |                       |

| f <sub>HSDR</sub> (data rate)        | J = 4 to 10 (LVDS, H                              | 150                      |      | 1,040 | Mbps   |       |                       |

|                                      | J = 2 (LVDS, Hyper]                               | (4)                      |      | 760   | Mbps   |       |                       |

|                                      | J = 1 (LVDS only)                                 | (4)                      |      | 500   | Mbps   |       |                       |

| f <sub>HSDRDPA</sub> (DPA data rate) | J = 4 to 10 (LVDS, HyperTransport technology)     |                          |      |       |        | 1,040 | Mbps                  |

| TCCS                                 | All differential standards                        |                          |      |       |        | 200   | ps                    |

| SW                                   | All differential standards                        |                          |      |       |        | -     | ps                    |

| Output jitter                        |                                                   |                          |      |       |        | 190   | ps                    |

| Output t <sub>RISE</sub>             | All differential I/O standards                    |                          |      |       |        | 160   | ps                    |

| Output t <sub>FALL</sub>             | All differential I/O standards                    |                          |      |       |        | 180   | ps                    |

| t <sub>DUTY</sub>                    |                                                   |                          |      | 45    | 50     | 55    | %                     |

| DPA run length                       |                                                   |                          |      |       |        | 6,400 | UI                    |

| DPA jitter tolerance                 | Data channel peak-to-peak jitter                  |                          |      |       |        |       | UI                    |

| DPA lock time                        |                                                   |                          |      |       |        |       | Number of repetitions |

|                                      | SPI-4                                             | 0000000000<br>1111111111 | 10%  | 256   |        |       |                       |

|                                      | Parallel Rapid I/O                                | 00001111                 | 25%  | 256   |        |       |                       |

|                                      |                                                   | 10010000                 | 50%  | 256   |        |       |                       |

|                                      | Miscellaneous                                     | 10101010                 | 100% | 256   |        |       |                       |

|                                      | 01010101                                          |                          |      |       |        | 1     | 1                     |

(1) When J = 4 to 10, the SERDES block is used.

- (2) When J = 1 or 2, the SERDES block is bypassed.

- (3) The input clock frequency and the W factor must satisfy the following fast PLL VCO specification: 150 ≤nput clock frequency × W ≤1,040.

- (4) The minimum specification is dependent on the clock source (fast PLL, enhanced PLL, clock pin, and so on) and the clock routing resource (global, regional, or local) utilized. The I/O differential buffer and input register do not have a minimum toggle rate.