#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 64MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, Memory Card, SPI, SSC, UART/USART, USB           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT             |

| Number of I/O              | 47                                                                       |

| Program Memory Size        | 512KB (512K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 64K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                             |

| Data Converters            | A/D 10x10/12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-VFQFN Exposed Pad                                                     |

| Supplier Device Package    | 64-QFN (9x9)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam3sd8ba-mu |

|                            |                                                                          |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

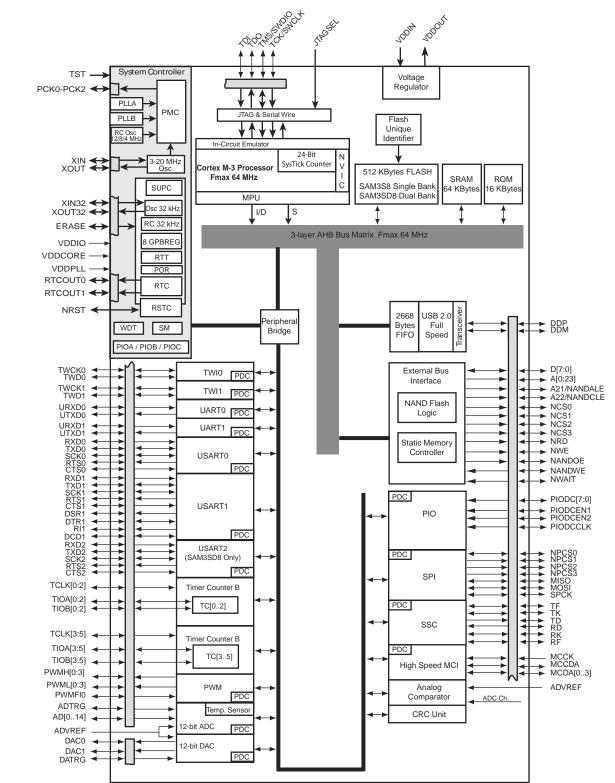

## 2. Block Diagram

Figure 2-1. SAM3S8/SD8 100-pin version Block Diagram

# SAM3S8/SD8 Summary

| Signal Nama                                                                                                | Function                               | Tumo                                                                            | Active   | Voltage | Commente |

|------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------------------------------------------------------------------------|----------|---------|----------|

| Signal Name                                                                                                | Universal Synchronous Asynchron        | Туре                                                                            | Level    |         | Comments |

|                                                                                                            | USARTx Serial Clock                    |                                                                                 |          |         |          |

| SCKx                                                                                                       |                                        | I/O                                                                             |          |         |          |

| TXDx                                                                                                       | USARTx Transmit Data                   | I/O                                                                             |          |         |          |

| RXDx                                                                                                       | USARTx Receive Data                    | Input                                                                           |          |         |          |

| RTSx                                                                                                       | USARTx Request To Send                 | Output                                                                          |          |         |          |

| CTSx                                                                                                       | USARTx Clear To Send                   | Input                                                                           |          |         |          |

| DTR1                                                                                                       | USART1 Data Terminal Ready             | I/O                                                                             |          |         |          |

| DSR1                                                                                                       | USART1 Data Set Ready                  | Input                                                                           |          |         |          |

| DCD1                                                                                                       | USART1 Data Carrier Detect             | Output                                                                          |          |         |          |

| RI1                                                                                                        | USART1 Ring Indicator                  | Input                                                                           |          |         |          |

|                                                                                                            | Synchronous Seria                      | al Controller                                                                   | - SSC    |         |          |

| TD                                                                                                         | SSC Transmit Data                      | Output                                                                          |          |         |          |

| RD                                                                                                         | SSC Receive Data                       | Input                                                                           |          |         |          |

| ТК                                                                                                         | SSC Transmit Clock                     | I/O                                                                             |          |         |          |

| RK                                                                                                         | SSC Receive Clock                      | I/O                                                                             |          |         |          |

| TF                                                                                                         | SSC Transmit Frame Sync                | I/O                                                                             |          |         |          |

| RF                                                                                                         | SSC Receive Frame Sync                 | I/O                                                                             |          |         |          |

|                                                                                                            | Timer/Cou                              | unter - TC                                                                      | 1        | 1       |          |

| TCLKx                                                                                                      | TC Channel x External Clock Input      | Input                                                                           |          |         |          |

| TIOAx                                                                                                      | TC Channel x I/O Line A                | I/O                                                                             |          |         |          |

| TIOBx                                                                                                      | TC Channel x I/O Line B                | I/O                                                                             |          |         |          |

|                                                                                                            | Pulse Width Modulati                   | on Controlle                                                                    | er- PWMC |         |          |

| PWMHx                                                                                                      | PWM Waveform Output High for channel x | Output                                                                          |          |         |          |

| PWMLx     PWM Waveform Output Low for channel x     Output     Output     only output complement when deal |                                        | only output in<br>complementary mode<br>when dead time insertion<br>is enabled. |          |         |          |

| PWMFI0                                                                                                     | PWM Fault Input                        | Input                                                                           |          |         |          |

|                                                                                                            | Serial Periphera                       | I Interface -                                                                   | SPI      |         |          |

| MISO                                                                                                       | Master In Slave Out                    | I/O                                                                             |          |         |          |

| MOSI                                                                                                       | Master Out Slave In                    | I/O                                                                             |          |         |          |

| SPCK                                                                                                       | SPI Serial Clock                       | I/O                                                                             |          |         |          |

| SPI_NPCS0                                                                                                  | SPI Peripheral Chip Select 0           | I/O                                                                             | Low      |         |          |

| SPI_NPCS1 -<br>SPI_NPCS3                                                                                   | SPI Peripheral Chip Select             | Output                                                                          | Low      |         |          |

## Table 3-1. Signal Description List (Continued)

## 4. Package and Pinout

SAM3S8/SD8 devices are pin-to-pin compatible with AT91SAM7S legacy products for 64-pin version. Furthermore, SAM3S8/SD8 products have new functionalities referenced in italic in Table 4-1, Table 4-3.

## 4.1 SAM3S8C/8DC Package and Pinout

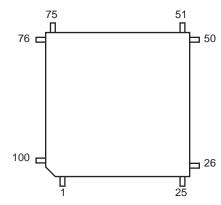

### 4.1.1 100-Lead LQFP Package Outline

Figure 4-1. Orientation of the 100-lead LQFP Package

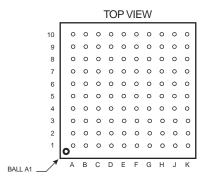

### 4.1.2 100-ball TFBGA Package Outline

The 100-Ball TFBGA package has a 0.8 mm ball pitch and respects Green Standards. Its dimensions are  $9 \times 9 \times 1.1$  mm. Figure 4-2 shows the orientation of the 100-ball TFBGA Package.

### Figure 4-2. Orientation of the 100-ball TFBGA Package

### 4.1.3 100-Lead LQFP Pinout

| 1  | ADVREF              |  |

|----|---------------------|--|

| 2  | GND                 |  |

| 3  | PB0/AD4             |  |

| 4  | PC29/AD13           |  |

| 5  | PB1/AD5             |  |

| 6  | PC30/AD14           |  |

| 7  | PB2/AD6             |  |

| 8  | PC31                |  |

| 9  | PB3/AD7             |  |

| 10 | VDDIN               |  |

| 11 | VDDOUT              |  |

| 12 | PA17/PGMD5/AD0      |  |

| 13 | PC26                |  |

| 14 | PA18/PGMD6/AD1      |  |

| 15 | PA21/PGMD9/AD8      |  |

| 16 | VDDCORE             |  |

| 17 | PC27                |  |

| 18 | PA19/PGMD7/AD2      |  |

| 19 | PC15/AD11           |  |

| 20 | PA22/PGMD10/AD<br>9 |  |

| 21 | PC13/AD10           |  |

| 22 | PA23/PGMD11         |  |

| 23 | PC12/AD12           |  |

| 24 | PA20/PGMD8/AD3      |  |

| 25 | PC0                 |  |

|    |                     |  |

| Table 4-1. | SAM3S8C/SD8C 100-lead LQFP pinout |

|------------|-----------------------------------|

|            |                                   |

| 100-1 |                         |

|-------|-------------------------|

| 26    | GND                     |

| 27    | VDDIO                   |

| 28    | PA16/PGMD4              |

| 29    | PC7                     |

| 30    | PA15/PGMD3              |

| 31    | PA14/PGMD2              |

| 32    | PC6                     |

| 33    | PA13/PGMD1              |

| 34    | PA24/PGMD12             |

| 35    | PC5                     |

| 36    | VDDCORE                 |

| 37    | PC4                     |

| 38    | PA25/PGMD13             |

| 39    | PA26/PGMD14             |

| 40    | PC3                     |

| 41    | PA12/PGMD0              |

| 42    | PA11/PGMM3              |

| 43    | PC2                     |

| 44    | PA10/PGMM2              |

| 45    | GND                     |

| 46    | PA9/PGMM1               |

| 47    | PC1                     |

| 48    | PA8/XOUT32/<br>PGMM0    |

| 49    | PA7/XIN32/<br>PGMNVALID |

| 50    | VDDIO                   |

|       |                         |

| 51 | TDI/PB4     |  |

|----|-------------|--|

| 52 | PA6/PGMNOE  |  |

| 53 | PA5/PGMRDY  |  |

| 54 | PC28        |  |

| 55 | PA4/PGMNCMD |  |

| 56 | VDDCORE     |  |

| 57 | PA27/PGMD15 |  |

| 58 | PC8         |  |

| 59 | PA28        |  |

| 60 | NRST        |  |

| 61 | TST         |  |

| 62 | PC9         |  |

| 63 | PA29        |  |

| 64 | PA30        |  |

| 65 | PC10        |  |

| 66 | PA3         |  |

| 67 | PA2/PGMEN2  |  |

| 68 | PC11        |  |

| 69 | VDDIO       |  |

| 70 | GND         |  |

| 71 | PC14        |  |

| 72 | PA1/PGMEN1  |  |

| 73 | PC16        |  |

| 74 | PA0/PGMEN0  |  |

| 75 | PC17        |  |

|    |             |  |

| 76  | TDO/TRACESWO/<br>PB5 |

|-----|----------------------|

| 77  | JTAGSEL              |

| 78  | PC18                 |

| 79  | TMS/SWDIO/PB6        |

| 80  | PC19                 |

| 81  | PA31                 |

| 82  | PC20                 |

| 83  | TCK/SWCLK/PB7        |

| 84  | PC21                 |

| 85  | VDDCORE              |

| 86  | PC22                 |

| 87  | ERASE/PB12           |

| 88  | DDM/PB10             |

| 89  | DDP/PB11             |

| 90  | PC23                 |

| 91  | VDDIO                |

| 92  | PC24                 |

| 93  | PB13/DAC0            |

| 94  | PC25                 |

| 95  | GND                  |

| 96  | PB8/XOUT             |

| 97  | PB9/PGMCK/XIN        |

| 98  | VDDIO                |

| 99  | PB14/DAC1            |

| 100 | VDDPLL               |

Т

## 4.2 SAM3S8B/D8B Package and Pinout

### 4.2.1 64-Lead LQFP Package Outline

Figure 4-3. Orientation of the 64-lead LQFP Package

1

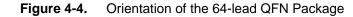

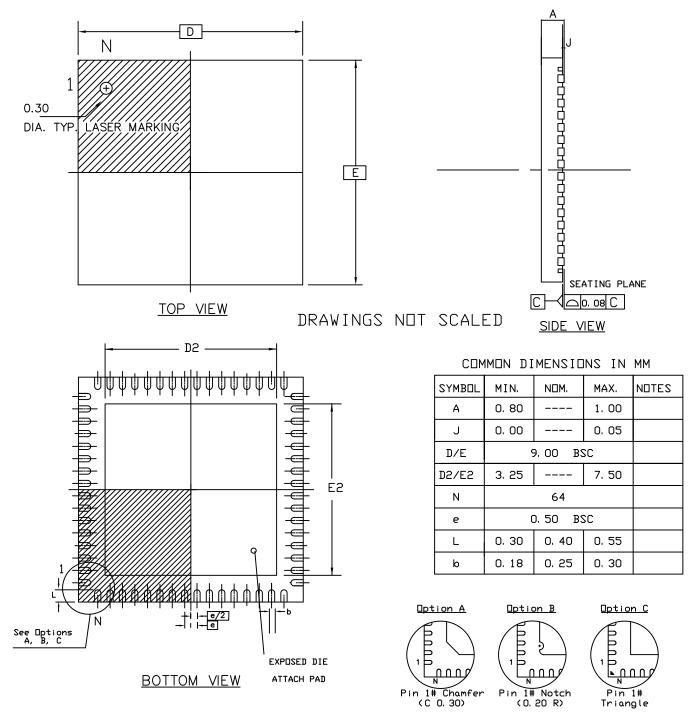

### 4.2.2 64-lead QFN Package Outline

# 12 SAM3S8/SD8 Summary

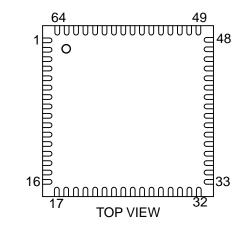

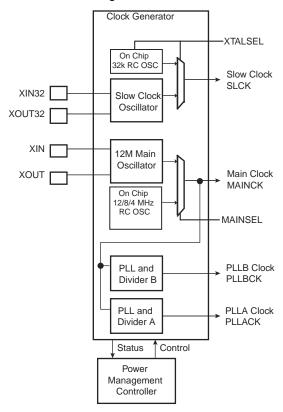

### Figure 5-1. Single Supply

Note: Restrictions

With Main Supply < 2.0 V, USB and ADC/DAC and Analog comparator are not usable. With Main Supply  $\ge$  2.0V and < 3V, USB is not usable. With Main Supply  $\ge$  3V, all peripherals are usable.

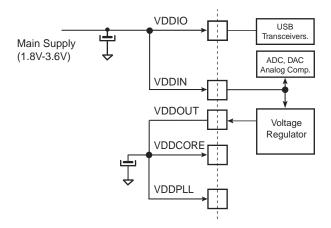

### Figure 5-2. Core Externally Supplied

Note: Restrictions

With Main Supply < 2.0V, USB is not usable.

With VDDIN < 2.0V, ADC, DAC and Analog comparator are not usable.

With Main Supply  $\geq$  2.0V and < 3V, USB is not usable.

With Main Supply and VDDIN  $\ge$  3V, all peripherals are usable.

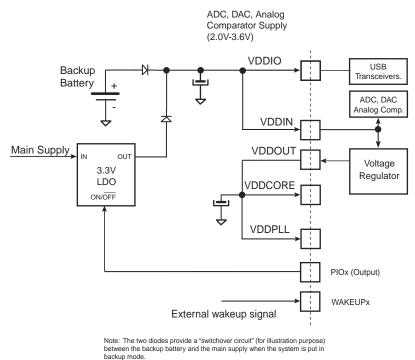

Figure 5-3 below provides an example of the powering scheme when using a backup battery. Since the PIO state is preserved when in backup mode, any free PIO line can be used to switch off the external regulator by driving the PIO line at low level (PIO is input, pull-up enabled after backup reset). External wake-up of the system can be from a push button or any signal. See Section 5.6 "Wake-up Sources" for further details.

### Figure 5-3. Backup Battery

### 5.4 Active Mode

Active mode is the normal running mode with the core clock running from the fast RC oscillator, the main crystal oscillator or the PLLA. The power management controller can be used to adapt the frequency and to disable the peripheral clocks.

### 5.5 Low-power Modes

The various low-power modes of the SAM3S8/SD8 are described below:

### 5.5.1 Backup Mode

The purpose of backup mode is to achieve the lowest power consumption possible in a system which is performing periodic wake-ups to perform tasks but not requiring fast startup time (<0.1ms). Total current consumption is  $1.5 \mu$ A typical.

The Supply Controller, zero-power power-on reset, RTT, RTC, Backup registers and 32 kHz oscillator (RC or crystal oscillator selected by software in the Supply Controller) are running. The regulator and the core supply are off.

Backup mode is based on the Cortex-M3 deep sleep mode with the voltage regulator disabled.

The SAM3S8/SD8 can be awakened from this mode through WUP0-15 pins, the supply monitor (SM), the RTT or RTC wake-up event.

Backup mode is entered by using WFE instructions with the SLEEPDEEP bit in the Cortex-M3 System Control Register set to 1. (See the Power management description in The ARM Cortex-M3 Processor section of the product datasheet).

Exit from Backup mode happens if one of the following enable wake up events occurs:

• WKUPEN0-15 pins (level transition, configurable debouncing)

# 16 SAM3S8/SD8 Summary

### 5.5.4 Low Power Mode Summary Table

The modes detailed above are the main low-power modes. Each part can be set to on or off separately and wake up sources can be individually configured. Table 5-1 below shows a summary of the configurations of the low-power modes.

| Mode           | SUPC,<br>32 kHz<br>Oscillator,<br>RTC, RTT<br>Backup<br>Registers,<br>POR<br>(Backup<br>Region) | Regulator | Core<br>Memory<br>Peripherals           | Mode Entry                                          | Potential Wake Up<br>Sources                                                                                                                                                                  | Core at<br>Wake Up | PIO State<br>while in Low<br>Power Mode | PIO State<br>at Wake Up                             | Consumption               | Wake-up<br>Time <sup>(1)</sup> |

|----------------|-------------------------------------------------------------------------------------------------|-----------|-----------------------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------------------------|-----------------------------------------------------|---------------------------|--------------------------------|

| Backup<br>Mode | ON                                                                                              | OFF       | OFF<br>(Not powered)                    | WFE<br>+SLEEPDEEP<br>bit = 1                        | WUP0-15 pins<br>SM alarm<br>RTC alarm<br>RTT alarm                                                                                                                                            | Reset              | Previous                                | PIOA &<br>PIOB &<br>PIOC<br>Inputs with<br>pull ups | 1.5 µА typ <sup>(4)</sup> | < 0.1 ms                       |

| Wait<br>Mode   | ON                                                                                              | ON        | Powered<br>(Not clocked)                | WFE<br>+SLEEPDEEP<br>bit = 0<br>+LPM bit = 1        | Any Event from: Fast<br>startup through<br>WUP0-15 pins<br>RTC alarm<br>RTT alarm<br>USB wake-up                                                                                              | Clocked<br>back    | Previous<br>state saved                 | Unchanged                                           | 5 μΑ/15 μΑ <sup>(5)</sup> | < 10 µs                        |

| Sleep<br>Mode  | ON                                                                                              | ON        | Powered <sup>(7)</sup><br>(Not clocked) | WFE or WFI<br>+SLEEPDEEP<br>bit = 0<br>+LPM bit = 0 | Entry mode =WFI<br>Interrupt Only; Entry<br>mode =WFE Any<br>Enabled Interrupt<br>and/or Any Event<br>from: Fast start-up<br>through WUP0-15<br>pins<br>RTC alarm<br>RTT alarm<br>USB wake-up | Clocked<br>back    | Previous<br>state saved                 | Unchanged                                           | (6)                       | (6)                            |

Notes: 1. When considering wake-up time, the time required to start the PLL is not taken into account. Once started, the device works with the 4/8/12 MHz fast RC oscillator. The user has to add the PLL start-up time if it is needed in the system. The wake-up time is defined as the time taken for wake up until the first instruction is fetched.

- 2. The external loads on PIOs are not taken into account in the calculation.

- 3. Supply Monitor current consumption is not included.

- 4. Total Current consumption.

- 5 μA on VDDCORE, 15 μA for total current consumption (using internal voltage regulator), 8 μA for total current consumption (without using internal voltage regulator).

- 6. Depends on MCK frequency.

- 7. In this mode the core is supplied and not clocked but some peripherals can be clocked.

### 5.6 Wake-up Sources

The wake-up events allow the device to exit the backup mode. When a wake-up event is detected, the Supply Controller performs a sequence which automatically reenables the core power supply and the SRAM power supply, if they are not already enabled.

### Figure 5-4. Wake-up Source

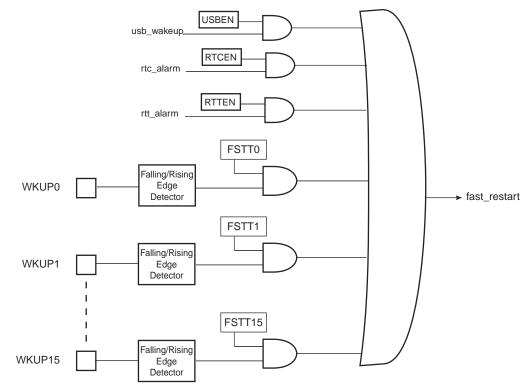

## 5.7 Fast Startup

The SAM3S8/SD8 allows the processor to restart in a few microseconds while the processor is in wait mode or in sleep mode. A fast start up can occur upon detection of a low level on one of the 19 wake-up inputs (WKUP0 to 15 + SM + RTC + RTT).

The fast restart circuitry, as shown in Figure 5-5, is fully asynchronous and provides a fast startup signal to the Power Management Controller. As soon as the fast start-up signal is asserted, the PMC automatically restarts the embedded 4 MHz Fast RC oscillator, switches the master clock on this 4MHz clock and reenables the processor clock.

| SYSTEM_IO<br>bit number | Default function<br>after reset | Other function | Constraints for<br>normal start     | Configuration                                                  |

|-------------------------|---------------------------------|----------------|-------------------------------------|----------------------------------------------------------------|

| 12                      | ERASE                           | PB12           | Low Level at startup <sup>(1)</sup> |                                                                |

| 10                      | DDM                             | PB10           | -                                   |                                                                |

| 11                      | DDP                             | PB11           | -                                   | In Matrix User Interface Registers                             |

| 7                       | TCK/SWCLK                       | PB7            | -                                   | (Refer to the System I/O<br>Configuration Register in the "Bus |

| 6                       | TMS/SWDIO                       | PB6            | -                                   | Matrix" section of the datasheet.)                             |

| 5                       | TDO/TRACESWO                    | PB5            | -                                   |                                                                |

| 4                       | TDI                             | PB4            | -                                   |                                                                |

| -                       | PA7                             | XIN32          | -                                   | See footnote <sup>(2)</sup> below                              |

| -                       | PA8                             | XOUT32         | -                                   | See loothote - below                                           |

| -                       | PB9                             | XIN            | -                                   | See footnote <sup>(3)</sup> below                              |

| -                       | PB8                             | XOUT           | -                                   | See loothote (*) below                                         |

### Table 6-1. System I/O Configuration Pin List.

Notes: 1. If PB12 is used as PIO input in user applications, a low level must be ensured at startup to prevent Flash erase before the user application sets PB12 into PIO mode,

2. In the product Datasheet Refer to: "Slow Clock Generator" of the "Supply Controller" section.

3. In the product Datasheet Refer to: "3 to 20 MHZ Crystal Oscillator" information in the "PMC" section.

### 6.2.1 Serial Wire JTAG Debug Port (SWJ-DP) Pins

The SWJ-DP pins are TCK/SWCLK, TMS/SWDIO, TDO/SWO, TDI and commonly provided on a standard 20-pin JTAG connector defined by ARM. For more details about voltage reference and reset state, refer to Table 3-1 on page 5.

At startup, SWJ-DP pins are configured in SWJ-DP mode to allow connection with debugging probe. Please refer to the "Debug and Test" Section of the product datasheet.

SWJ-DP pins can be used as standard I/Os to provide users more general input/output pins when the debug port is not needed in the end application. Mode selection between SWJ-DP mode (System IO mode) and general IO mode is performed through the AHB Matrix Special Function Registers (MATRIX\_SFR). Configuration of the pad for pull-up, triggers, debouncing and glitch filters is possible regardless of the mode.

The JTAGSEL pin is used to select the JTAG boundary scan when asserted at a high level. It integrates a permanent pull-down resistor of about 15 k $\Omega$  to GND, so that it can be left unconnected for normal operations.

By default, the JTAG Debug Port is active. If the debugger host wants to switch to the Serial Wire Debug Port, it must provide a dedicated JTAG sequence on TMS/SWDIO and TCK/SWCLK which disables the JTAG-DP and enables the SW-DP. When the Serial Wire Debug Port is active, TDO/TRACESWO can be used for trace.

The asynchronous TRACE output (TRACESWO) is multiplexed with TDO. So the asynchronous trace can only be used with SW-DP, not JTAG-DP. For more information about SW-DP and JTAG-DP switching, please refer to the "Debug and Test" Section.

#### 7.5 **Master to Slave Access**

All the Masters can normally access all the Slaves. However, some paths do not make sense, for example allowing access from the Cortex-M3 S Bus to the Internal ROM. Thus, these paths are forbidden or simply not wired, and shown as "-" in the following table.

|        | Masters                | 0                    | 1                  | 2   | 3     |

|--------|------------------------|----------------------|--------------------|-----|-------|

| Slaves |                        | Cortex-M3 I/D<br>Bus | Cortex-M3 S<br>Bus | PDC | CRCCU |

| 0      | Internal SRAM          | -                    | Х                  | х   | х     |

| 1      | Internal ROM           | Х                    | -                  | Х   | х     |

| 2      | Internal Flash         | х                    | -                  | -   | Х     |

| 3      | External Bus Interface | -                    | Х                  | Х   | Х     |

| 4      | Peripheral Bridge      | -                    | Х                  | Х   | -     |

Table 7-3. SAM3S8 SD8 Master to Slave Access

#### 7.6 **Peripheral DMA Controller**

- · Handles data transfer between peripherals and memories

- · Low bus arbitration overhead

- One Master Clock cycle needed for a transfer from memory to peripheral

- Two Master Clock cycles needed for a transfer from peripheral to memory

- Next Pointer management for reducing interrupt latency requirement

The Peripheral DMA Controller handles transfer requests from the channel according to the following priorities (Low to High priorities):

Table 7 4 Peripheral DMA Controller

| Table 7-4.   | Peripheral DMA Controlle |

|--------------|--------------------------|

| Instance nam | ne Channel T/R           |

| USART2       | Transmit                 |

| USART2       | Receive                  |

| PWM          | Transmit                 |

| TWI1         | Transmit                 |

| TWI0         | Transmit                 |

| UART1        | Transmit                 |

| UART0        | Transmit                 |

| USART1       | Transmit                 |

| USART0       | Transmit                 |

| DACC         | Transmit                 |

| SPI          | Transmit                 |

|              |                          |

# SAM3S8/SD8 Summary

### 10.1 System Controller and Peripherals Mapping

Please refer to Section 8-1 "SAM3S8/SD8 Product Mapping" on page 27.

All the peripherals are in the bit band region and are mapped in the bit band alias region.

### 10.2 Power-on-Reset, Brownout and Supply Monitor

The SAM3S8/SD8 embeds three features to monitor, warn and/or reset the chip:

- Power-on-Reset on VDDIO

- Brownout Detector on VDDCORE

- Supply Monitor on VDDIO

#### 10.2.1 Power-on-Reset

The Power-on-Reset monitors VDDIO. It is always activated and monitors voltage at start up but also during power down. If VDDIO goes below the threshold voltage, the entire chip is reset. For more information, refer to the Electrical Characteristics section of the datasheet.

### 10.2.2 Brownout Detector on VDDCORE

The Brownout Detector monitors VDDCORE. It is active by default. It can be deactivated by software through the Supply Controller (SUPC\_MR). It is especially recommended to disable it during low-power modes such as wait or sleep modes.

If VDDCORE goes below the threshold voltage, the reset of the core is asserted. For more information, refer to the Supply Controller (SUPC) and Electrical Characteristics sections of the datasheet.

### 10.2.3 Supply Monitor on VDDIO

The Supply Monitor monitors VDDIO. It is not active by default. It can be activated by software and is fully programmable with 16 steps for the threshold (between 1.9V to 3.4V). It is controlled by the Supply Controller (SUPC). A sample mode is possible. It allows to divide the supply monitor power consumption by a factor of up to 2048. For more information, refer to the SUPC and Electrical Characteristics sections of the datasheet.

### 10.3 Reset Controller

The Reset Controller is based on a Power-on-Reset cell, and a Supply Monitor on VDDCORE.

The Reset Controller is capable to return to the software the source of the last reset, either a general reset, a wake-up reset, a software reset, a user reset or a watchdog reset.

The Reset Controller controls the internal resets of the system and the NRST pin input/output. It is capable to shape a reset signal for the external devices, simplifying to a minimum connection of a push-button on the NRST pin to implement a manual reset.

The configuration of the Reset Controller is saved as supplied on VDDIO.

### 10.4 Supply Controller (SUPC)

The Supply Controller controls the power supplies of each section of the processor and the peripherals (via Voltage regulator control)

The Supply Controller has its own reset circuitry and is clocked by the 32 kHz Slow clock generator.

# SAM3S8/SD8 Summary

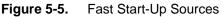

Figure 10-2. Clock Generator Block Diagram

### **10.6 Power Management Controller**

The Power Management Controller provides all the clock signals to the system. It provides:

- the Processor Clock, HCLK

- the Free running processor clock, FCLK

- the Cortex SysTick external clock

- the Master Clock, MCK, in particular to the Matrix and the memory interfaces

- the USB Clock, UDPCK

- independent peripheral clocks, typically at the frequency of MCK

- three programmable clock outputs: PCK0, PCK1 and PCK2

The Supply Controller selects between the 32 kHz RC oscillator or the crystal oscillator. The unused oscillator is disabled automatically so that power consumption is optimized.

By default, at startup the chip runs out of the Master Clock using the fast RC oscillator running at 4 MHz.

The user can trim the 8 and 12 MHz RC Oscillator frequency by software.

- Lock of the configuration by the connected peripheral

- Synchronous output, provides set and clear of several I/O lines in a single write

- Write Protect Registers

- Programmable Schmitt trigger inputs

- Parallel capture mode

- Can be used to interface a CMOS digital image sensor, an ADC....

- One clock, 8-bit parallel data and two data enable on I/O lines

- Data can be sampled one time out of two (for chrominance sampling only)

- Supports connection of one Peripheral DMA Controller channel (PDC) which offers buffer reception without processor intervention

### **10.16 Peripheral Identifiers**

Table 10-3 defines the Peripheral Identifiers of the SAM3S8/SD8. A peripheral identifier is required for the control of the peripheral interrupt with the Nested Vectored Interrupt Controller and control of the peripheral clock with the Power Management Controller.

|             |               |                | PMC           |                                    |  |

|-------------|---------------|----------------|---------------|------------------------------------|--|

| Instance ID | Instance Name | NVIC Interrupt | Clock Control | Instance Description               |  |

| 0           | SUPC          | X              |               | Supply Controller                  |  |

| 1           | RSTC          | X              |               | Reset Controller                   |  |

| 2           | RTC           | x              |               | Real Time Clock                    |  |

| 3           | RTT           | x              |               | Real Time Timer                    |  |

| 4           | WDT           | X              |               | Watchdog Timer                     |  |

| 5           | PMC           | X              |               | Power Management Controller        |  |

| 6           | EEFC          | X              |               | Enhanced Embedded Flash Controller |  |

| 7           | -             | -              |               | Reserved                           |  |

| 8           | UART0         | X              | x             | UART 0                             |  |

| 9           | UART1         | X              | X             | UART 1                             |  |

| 10          | SMC           | X              | X             | Static Memory Controller           |  |

| 11          | PIOA          | X              | x             | Parallel I/O Controller A          |  |

| 12          | PIOB          | X              | x             | Parallel I/O Controller B          |  |

| 13          | PIOC          | x              | x             | Parallel I/O Controller C          |  |

| 14          | USART0        | X              | x             | USART 0                            |  |

| 15          | USART1        | X              | x             | USART 1                            |  |

| 16          | USART2        | X              | x             | USART 2 (SAM3SD8 100 pins only)    |  |

| 17          | -             | -              | -             | Reserved                           |  |

| 18          | HSMCI         | X              | X             | Multimedia Card Interface          |  |

| 19          | TWIO          | X              | X             | Two Wire Interface 0               |  |

| 20          | TWI1          | X              | X             | Two Wire Interface 1               |  |

| 21          | SPI           | X              | X             | Serial Peripheral Interface        |  |

Table 10-3. Peripheral Identifiers

| Instance ID | Instance Name | NVIC Interrupt | PMC<br>Clock Control | Instance Description          |  |

|-------------|---------------|----------------|----------------------|-------------------------------|--|

| 22          | SSC           | X              | X                    | Synchronous Serial Controller |  |

| 23          | TC0           | X              | X                    | Timer/Counter 0               |  |

| 24          | TC1           | X              | X                    | Timer/Counter 1               |  |

| 25          | TC2           | X              | X                    | Timer/Counter 2               |  |

| 26          | TC3           | X              | X                    | Timer/Counter 3               |  |

| 27          | TC4           | X              | X                    | Timer/Counter 4               |  |

| 28          | TC5           | X              | X                    | Timer/Counter 5               |  |

| 29          | ADC           | X              | X                    | Analog To Digital Converter   |  |

| 30          | DACC          | X              | X                    | Digital To Analog Converter   |  |

| 31          | PWM           | X              | X                    | Pulse Width Modulation        |  |

| 32          | CRCCU         | X              | X                    | CRC Calculation Unit          |  |

| 33          | ACC           | X              | X                    | Analog Comparator             |  |

| 34          | UDP           | X              | X                    | USB Device Port               |  |

Table 10-3.

Peripheral Identifiers (Continued)

### 10.17 Peripheral Signal Multiplexing on I/O Lines

The SAM3S8/SD8 features 2 PIO controllers on 64-pin versions (PIOA and PIOB) or 3 PIO controllers on the 100-pin version (PIOA, PIOB and PIOC), that multiplex the I/O lines of the peripheral set.

The SAM3S8/SD8 64-pin and 100-pin PIO Controllers control up to 32 lines. Each line can be assigned to one of three peripheral functions: A, B or C. The multiplexing tables in the following paragraphs define how the I/O lines of the peripherals A, B and C are multiplexed on the PIO Controllers. The column "Comments" has been inserted in this table for the user's own comments; it may be used to track how pins are defined in an application.

Note that some peripheral functions which are output only, might be duplicated within the tables.

Inch

#### SAM3S8/SD8 Summary 52

Symbol

| Symbol | Min       | Nom      | Max  | Min       | Nom       | Мах   |

|--------|-----------|----------|------|-----------|-----------|-------|

| А      | -         | -        | 1.60 | -         | -         | 0.063 |

| A1     | 0.05      | -        | 0.15 | 0.002     | -         | 0.006 |

| A2     | 1.35      | 1.40     | 1.45 | 0.053     | 0.055     | 0.057 |

| D      | 12.00 BSC |          |      | 0.472 BSC |           |       |

| D1     | 10.00 BSC |          |      | 0.383 BSC |           |       |

| Е      | 12.00 BSC |          |      | 0.472 BSC |           |       |

| E1     | 10.00 BSC |          |      | 0.383 BSC |           |       |

| R2     | 0.08      | -        | 0.20 | 0.003     | -         | 0.008 |

| R1     | 0.08      | -        | _    | 0.003     | -         | -     |

| q      | 0°        | 3.5°     | 7°   | 0°        | 3.5°      | 7°    |

| θ1     | 0°        | -        | -    | 0°        | -         | _     |

| θ2     | 11°       | 12°      | 13°  | 11°       | 12°       | 13°   |

| θ3     | 11°       | 12°      | 13°  | 11°       | 12°       | 13°   |

| С      | 0.09      | -        | 0.20 | 0.004     | -         | 0.008 |

| L      | 0.45      | 0.60     | 0.75 | 0.018     | 0.024     | 0.030 |

| L1     |           | 1.00 REF |      |           | 0.039 REF |       |

64-lead LQFP Package Dimensions (in mm) Table 12-1.

Millimeter

## Figure 12-3. 64-lead LQFP Package Mechanical Drawing

Figure 12-4. 64-lead QFN Package Mechanical Drawing

# **Revision History**

In the information that follows, the most recent version of the document is referenced first.

| Doc. Rev | Comments                                                                                                                           | Change<br>Request<br>Ref. |

|----------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| 11090BS  | Corrected Figure 12-3 "64-lead LQFP Package Mechanical Drawing" and inserted Table 12-1 "64-lead LQFP Package Dimensions (in mm)". | 9389                      |

| Doc. Rev | Comments    | Change<br>Request<br>Ref. |

|----------|-------------|---------------------------|

| 11090AS  | First issue |                           |

#### **Atmel Corporation**

1600 Technology Drive San Jose, CA 95110 USA **Tel:** (+1) (408) 441-0311 **Fax:** (+1) (408) 487-2600 www.atmel.com

#### Atmel Asia Limited

Unit 01-5 & 16, 19F BEA Tower, Millennium City 5 418 Kwun Tong Road Kwun Tong, Kowloon HONG KONG Tel: (+852) 2245-6100 Fax: (+852) 2722-1369 Atmel Munich GmbH Business Campus Parkring 4 D-85748 Garching b. Munich GERMANY Tel: (+49) 89-31970-0 Fax: (+49) 89-3194621

#### Atmel Japan G.K.

16F Shin-Osaki Kangyo Bldg 1-6-4 Osaki, Shinagawa-ku Tokyo 141-0032 JAPAN **Tel:** (+81) (3) 6417-0300 **Fax:** (+81) (3) 6417-0370

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERCUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not sintended of uservations in applications intended to support or sustain life.

#### © 2013 Atmel Corporation. All rights reserved.

Atmel<sup>®</sup>, Atmel logo and combinations thereof, QTouch<sup>®</sup>, DataFlash<sup>®</sup>, SAM-BA<sup>®</sup> and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries.Windows<sup>®</sup> and others, are registered trademarks or trademarks of Microsoft Corporation in the US and/or other countries. ARM<sup>®</sup>, Cortex<sup>®</sup>, Thumb<sup>®</sup>-2 and others are registered trademarks or trademarks of ARM Ltd. Other terms and product names may be trademarks of others.