# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                              |

|---------------------------------|-----------------------------------------------------------------------|

| Core Processor                  | PowerPC e300c4s                                                       |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                        |

| Speed                           | 667MHz                                                                |

| Co-Processors/DSP               | -                                                                     |

| RAM Controllers                 | DDR, DDR2                                                             |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | -                                                                     |

| Ethernet                        | 10/100/1000Mbps (2)                                                   |

| SATA                            | SATA 3Gbps (2)                                                        |

| USB                             | USB 2.0 + PHY (1)                                                     |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                      |

| Operating Temperature           | 0°C ~ 125°C (TA)                                                      |

| Security Features               | -                                                                     |

| Package / Case                  | 689-BBGA Exposed Pad                                                  |

| Supplier Device Package         | 689-TEPBGA II (31x31)                                                 |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc8377vralg |

|                                 |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.10 PCI Express Controller

The PCI Express controller includes the following features:

- PCI Express 1.0a compatible

- Two  $\times 1$  links or one  $\times 2$  link width

- Auto-detection of number of connected lanes

- Selectable operation as root complex or endpoint

- Both 32- and 64-bit addressing

- 128-byte maximum payload size

- Support for MSI and INTx interrupt messages

- Virtual channel 0 only

- Selectable Traffic Class

- Full 64-bit decode with 32-bit wide windows

- Dedicated four channel descriptor-based DMA engine per interface

### 1.11 Serial ATA (SATA) Controllers

The serial ATA (SATA) controllers have the following features:

- Supports Serial ATA Rev 2.5 Specification

- Spread spectrum clocking on receive

- Asynchronous notification

- Hot Plug including asynchronous signal recovery

- Link power management

- Native command queuing

- Staggered spin-up and port multiplier support

- Port multiplier support

- SATA 1.5 and 3.0 Gb/s operation

- Interrupt driven

- Power management support

- Error handling and diagnostic features

- Far end/near end loopback

- Failed CRC error reporting

- Increased ALIGN insertion rates

- Scrambling and CONT override

|                  | Characteristic                                                                    | Symbol            | Max Value                         | Unit | Note    |

|------------------|-----------------------------------------------------------------------------------|-------------------|-----------------------------------|------|---------|

| Input voltage    | DDR DRAM signals                                                                  | MV <sub>IN</sub>  | –0.3 to (GV <sub>DD</sub> + 0.3)  | V    | 2, 4    |

|                  | DDR DRAM reference                                                                | MV <sub>REF</sub> | –0.3 to (GV <sub>DD</sub> + 0.3)  | V    | 2, 4    |

|                  | Three-speed Ethernet signals                                                      | LV <sub>IN</sub>  | -0.3 to (LV <sub>DD</sub> + 0.3)  | V    | —       |

|                  | PCI, DUART, CLKIN, system control and power management, $I^2C$ , and JTAG signals | OV <sub>IN</sub>  | –0.3 to (OV <sub>DD</sub> + 0.3)  | V    | 3, 4, 5 |

|                  | Local Bus                                                                         | LB <sub>IN</sub>  | -0.3 to (LBV <sub>DD</sub> + 0.3) | V    | —       |

| Storage temperat | ture range                                                                        | T <sub>STG</sub>  | –55 to 150                        | °C   | —       |

Table 2. Absolute Maximum Ratings<sup>1</sup> (continued)

Notes:

- 1. Functional and tested operating conditions are given in Table 3. Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage to the device.

- 2. Caution: MV<sub>IN</sub> must not exceed GV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 3. Caution: OV<sub>IN</sub> must not exceed OV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 4. (M,O)V<sub>IN</sub> and MV<sub>REF</sub> may overshoot/undershoot to a voltage and for a maximum duration as shown in Figure 2.

- 5. Overshoot/undershoot by OV<sub>IN</sub> on the PCI interface does not comply to the PCI Electrical Specification for 3.3-V operation, as shown in Figure 2.

- 6. L[1,2]\_nV<sub>DD</sub> includes SDAV<sub>DD\_0</sub>, XCOREV<sub>DD</sub>, and XPADV<sub>DD</sub> power inputs.

### 2.1.2 Power Supply Voltage Specification

This table provides recommended operating conditions for the device. Note that the values in this table are the recommended and tested operating conditions. Proper device operation outside of these conditions is not guaranteed.

| Characteristic                                                 |                                       | Symbol                 | Recommended<br>Value                              | Unit | Note |

|----------------------------------------------------------------|---------------------------------------|------------------------|---------------------------------------------------|------|------|

| Core supply voltage                                            | up to 667 MHz $V_{DD}$ 1.0 ± 50 mV    |                        | V                                                 | 1    |      |

|                                                                | 800 MHz                               |                        | 1.05 ± 50 mV                                      | V    | 1    |

| PLL supply voltage (e300 core, eLBC and                        | up to 667 MHz                         | AV <sub>DD</sub>       | 1.0 ± 50 mV                                       | V    | 1, 2 |

| system)                                                        | 800 MHz                               |                        | 1.05 ± 50 mV                                      | V    | 1, 2 |

| DDR1 and DDR2 DRAM I/O voltage                                 |                                       | GV <sub>DD</sub>       | 2.5 V ± 125 mV<br>1.8 V ± 90 mV                   | V    | 1    |

| Three-speed Ethernet I/O, MII management vo                    | ltage                                 | LV <sub>DD</sub> [1,2] | 3.3 V ± 165 mV<br>2.5 V ± 125 mV                  | V    | _    |

| PCI, local bus, DUART, system control and pow JTAG I/O voltage | ver management, I <sup>2</sup> C, and | OV <sub>DD</sub>       | 3.3 V ± 165 mV                                    | V    | 1    |

| Local Bus                                                      |                                       | LBV <sub>DD</sub>      | 1.8 V ± 90 mV<br>2.5 V ± 125 mV<br>3.3 V ± 165 mV | V    | —    |

**Table 3. Recommended Operating Conditions**

| Characteristic              |                      | Symbol                           | Recommended<br>Value                                    | Unit | Note |

|-----------------------------|----------------------|----------------------------------|---------------------------------------------------------|------|------|

| SerDes                      | up to 667 MHz        | L[1,2]_ <i>n</i> V <sub>DD</sub> | 1.0 ± 50 mV                                             | V    | 1, 3 |

|                             | 800 MHz              |                                  | 1.05 V ± 50 mV                                          | V    | 1, 3 |

| Operating temperature range | commerical           | T <sub>a</sub><br>T <sub>j</sub> | T <sub>a</sub> =0 (min)—<br>T <sub>j</sub> =125 (max)   | °C   | —    |

|                             | extended temperature | T <sub>a</sub><br>T <sub>j</sub> | T <sub>a</sub> =–40 (min)—<br>T <sub>j</sub> =125 (max) | °C   | —    |

#### Table 3. Recommended Operating Conditions (continued)

#### Notes:

- 1. GV<sub>DD</sub>, OV<sub>DD</sub>, AV<sub>DD</sub>, and V<sub>DD</sub> must track each other and must vary in the same direction—either in the positive or negative direction.

- 2. AV<sub>DD</sub> is the input to the filter discussed in Section 25.1, "PLL Power Supply Filtering," and is not necessarily the voltage at the AVDD pin.

- 3.  $L[1,2]_nV_{DD}$ , SDAV<sub>DD\_0</sub>, XCOREV<sub>DD</sub>, and XPADV<sub>DD</sub> power inputs.

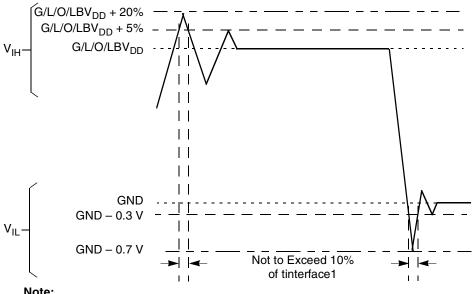

This figure shows the undershoot and overshoot voltages at the interfaces of the device.

#### Note:

1. Note that  $t_{\mbox{interface}}$  refers to the clock period associated with the bus clock interface. 2. Note that with the PCI overshoot allowed (as specified above), the device does not fully comply with the maximum AC ratings and device protection guideline outlined in the PCI Rev. 2.3 Specification (Section 4.2.2.3).

#### Figure 2. Overshoot/Undershoot Voltage for $GV_{DD}/LV_{DD}/OV_{DD}/LBV_{DD}$

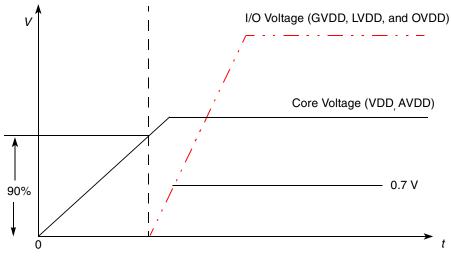

voltage supplies— $GV_{DD}$ ,  $LV_{DD}$ , and  $OV_{DD}$ —do not have any ordering requirements with respect to one another.

Figure 3. Power-Up Sequencing Example

Note that the SerDes power supply  $(L[1,2]_nV_{DD})$  should follow the same timing as the core supply  $(V_{DD})$ .

The device does not require the core supply voltage and I/O supply voltages to be powered down in any particular order.

## **3 Power Characteristics**

The estimated typical power dissipation for the chip device is shown in this table.

| Core Frequency<br>(MHz) | CSB/DDR Frequency<br>(MHz) | Sleep Power<br>at T <sub>j</sub> = 65°C (W) $^2$ | Typical Application<br>at $T_j = 65^{\circ}C$ (W) <sup>2</sup> | Typical Application at $T_j = 125^{\circ}C$ (W) <sup>3</sup> | Max Application at $T_j = 125^{\circ}C$ (W) <sup>4</sup> |

|-------------------------|----------------------------|--------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------|

| 333                     | 333                        | 1.45                                             | 1.9                                                            | 3.2                                                          | 3.8                                                      |

| 333                     | 167                        | 1.45                                             | 1.8                                                            | 3.0                                                          | 3.6                                                      |

| 400                     | 400                        | 1.45                                             | 2.0                                                            | 3.3                                                          | 4.0                                                      |

| 400                     | 266                        | 1.45                                             | 1.9                                                            | 3.1                                                          | 3.8                                                      |

| 450                     | 300                        | 1.45                                             | 2.0                                                            | 3.2                                                          | 3.8                                                      |

| 450                     | 225                        | 1.45                                             | 1.9                                                            | 3.1                                                          | 3.7                                                      |

| 500                     | 333                        | 1.45                                             | 2.0                                                            | 3.3                                                          | 3.9                                                      |

| 500                     | 250                        | 1.45                                             | 1.9                                                            | 3.2                                                          | 3.8                                                      |

| 522                     | 355                        | 1.45                                             | 2.0                                                            | 3.3                                                          | 4.0                                                      |

| 533                     | 266                        | 1.45                                             | 2.0                                                            | 3.2                                                          | 3.9                                                      |

Table 5. Power Dissipation <sup>1</sup>

| Interface                    | Parameter          | GV <sub>DD</sub><br>(1.8 V) | GV <sub>DD</sub> /LBV <sub>DD</sub><br>(2.5 V) | OV <sub>DD</sub><br>(3.3 V) | LV <sub>DD</sub><br>(3.3 V) | LV <sub>DD</sub><br>(2.5 V) | L[1,2]_ <i>n</i> V <sub>DD</sub><br>(1.0 V) | Unit | Comments                                     |

|------------------------------|--------------------|-----------------------------|------------------------------------------------|-----------------------------|-----------------------------|-----------------------------|---------------------------------------------|------|----------------------------------------------|

| PCI I/O<br>Load =            | 33 MHz,<br>32-bit  | —                           |                                                | 0.04                        | _                           |                             | _                                           | W    |                                              |

| 20 pf                        | 66 MHz,<br>32-bit  | —                           | _                                              | 0.07                        | _                           | _                           | —                                           | W    |                                              |

|                              | 167 MHz,<br>32-bit | 0.09                        | 0.17                                           | 0.29                        | _                           | _                           | —                                           | W    | _                                            |

| Local Bus                    | 133 MHz,<br>32-bit | 0.07                        | 0.14                                           | 0.24                        | —                           | _                           | _                                           | W    |                                              |

| I/O<br>Load =                | 83 MHz,<br>32-bit  | 0.05                        | 0.09                                           | 0.15                        | _                           | _                           | _                                           | W    |                                              |

| 25 pf                        | 66 MHz,<br>32-bit  | 0.04                        | 0.07                                           | 0.13                        | —                           | _                           | _                                           | W    |                                              |

|                              | 50 MHz,<br>32-bit  | 0.03                        | 0.06                                           | 0.1                         | _                           |                             | _                                           | W    |                                              |

|                              | MII or RMII        | _                           |                                                | —                           | 0.02                        | _                           |                                             | W    | Multiply by<br>number of<br>interfaces used. |

| eTSEC I/O<br>Load =<br>25 pf | RGMII or<br>RTBI   | —                           | —                                              | —                           | —                           | 0.05                        | —                                           | W    | _                                            |

| USB                          | 12 Mbps            | _                           | _                                              | 0.01                        | —                           | —                           | —                                           | W    | _                                            |

| (60MHz<br>Clock)             | 480 Mbps           | —                           | _                                              | 0.2                         | —                           | -                           | —                                           | W    |                                              |

| SerDes                       | per lane           | —                           | —                                              |                             | —                           | —                           | 0.029                                       | W    | —                                            |

| Other I/O                    | —                  | —                           |                                                | 0.01                        | —                           | —                           |                                             | W    | —                                            |

Table 6. Typical I/O Power Dissipation (continued)

Note: The values given are for typical, and not worst case, switching.

# 4 Clock Input Timing

This section provides the clock input DC and AC electrical characteristics for the chip. Note that the PCI\_CLK/PCI\_SYNC\_IN signal or CLKIN signal is used as the PCI input clock depending on whether the device is configured as a host or agent device. CLKIN is used when the device is in host mode.

| Input low voltage                              | V <sub>IL</sub> | -0.3  | MV <sub>REF</sub> – 0.18 | V  | _ |

|------------------------------------------------|-----------------|-------|--------------------------|----|---|

| Output leakage current                         | I <sub>OZ</sub> | -50   | 50                       | μA | 4 |

| Output high current (V <sub>OUT</sub> = 1.9 V) | I <sub>OH</sub> | -15.2 | —                        | mA | — |

| Output low current (V <sub>OUT</sub> = 0.38 V) | I <sub>OL</sub> | 15.2  | —                        | mA | — |

Table 15. DDR SDRAM DC Electrical Characteristics for GV<sub>DD</sub> (typ) = 2.5 V (continued)

Notes:

1.  ${\rm GV}_{\rm DD}$  is expected to be within 50 mV of the DRAM  ${\rm GV}_{\rm DD}$  at all times.

MV<sub>REF</sub> is expected to be equal to 0.5 × GV<sub>DD</sub>, and to track GV<sub>DD</sub> DC variations as measured at the receiver. Peak-to-peak noise on MV<sub>REF</sub> may not exceed ±2% of the DC value.

V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be equal to MV<sub>REF</sub> This rail should track variations in the DC level of MV<sub>REF</sub>

4. Output leakage is measured with all outputs disabled, 0 V  $\leq$  V\_{OUT}  $\leq$  GV\_{DD}

5. See AN3665, "MPC837xE Design Checklist," for proper DDR termination.

Table 16 provides the DDR capacitance when  $GV_{DD}(typ) = 2.5$  V.

#### Table 16. DDR SDRAM Capacitance for GV<sub>DD</sub> (typ) = 2.5 V

| Parameter                               | Symbol           | Min | Мах | Unit | Note |

|-----------------------------------------|------------------|-----|-----|------|------|

| Input/output capacitance: DQ, DQS       | C <sub>IO</sub>  | 6   | 8   | pF   | 1    |

| Delta input/output capacitance: DQ, DQS | C <sub>DIO</sub> | _   | 0.5 | pF   | 1    |

Note:

1. This parameter is sampled.  $GV_{DD} = 2.5 V \pm 0.125 V$ , f = 1 MHz, T<sub>A</sub> = 25°C,  $V_{OUT} = GV_{DD}/2$ ,  $V_{OUT}$  (peak-to-peak) = 0.2 V.

This table provides the current draw characteristics for MV<sub>REF</sub>.

#### Table 17. Current Draw Characteristics for MV<sub>REF</sub>

| Parameter                                          | Symbol             | Min | Тур        | Max        | Unit | Note |

|----------------------------------------------------|--------------------|-----|------------|------------|------|------|

| Current draw for MV <sub>REF</sub><br>DDR1<br>DDR2 | I <sub>MVREF</sub> |     | 250<br>150 | 600<br>400 | μΑ   | 1, 2 |

Note:

1. The voltage regulator for  $MV_{REF}$  must be able to supply up to the stated maximum current.

2. This current is divided equally between MVREF1 and MVREF2, where half the current flows through each pin.

### 6.2 DDR1 and DDR2 SDRAM AC Electrical Characteristics

This section provides the AC electrical characteristics for the DDR SDRAM interface.

### 6.2.1 DDR1 and DDR2 SDRAM Input AC Timing Specifications

This table provides the input AC timing specifications for the DDR2 SDRAM when GVDD(typ) = 1.8 V.

### Table 18. DDR2 SDRAM Input AC Timing Specifications for 1.8-V Interface

| Parameter             | Symbol          | Min                      | Мах                      | Unit |

|-----------------------|-----------------|--------------------------|--------------------------|------|

| AC input low voltage  | V <sub>IL</sub> | —                        | MV <sub>REF</sub> – 0.25 | V    |

| AC input high voltage | V <sub>IH</sub> | MV <sub>REF</sub> + 0.25 | —                        | V    |

This table provides the input AC timing specifications for the DDR1 SDRAM when  $GV_{DD}(typ) = 2.5 \text{ V}$ .

### Table 19. DDR1 SDRAM Input AC Timing Specifications for 2.5-V Interface

| Parameter             | Symbol          | Min                      | Мах                      | Unit |

|-----------------------|-----------------|--------------------------|--------------------------|------|

| AC input low voltage  | V <sub>IL</sub> | _                        | MV <sub>REF</sub> – 0.31 | V    |

| AC input high voltage | V <sub>IH</sub> | MV <sub>REF</sub> + 0.31 | _                        | V    |

This table provides the input AC timing specifications for the DDR1 and DDR2 SDRAM interface.

#### Table 20. DDR1 and DDR2 SDRAM Input AC Timing Specifications

| Parameter                                                                                            | Symbol | Min                  | Мах               | Unit | Note                |

|------------------------------------------------------------------------------------------------------|--------|----------------------|-------------------|------|---------------------|

| Controller skew for MDQS-MDQ/MECC/MDM<br>400 MHz data rate<br>333 MHz data rate<br>266 MHz data rate |        | -500<br>-750<br>-750 | 500<br>750<br>750 | ps   | 1, 2<br>3<br>—<br>— |

Note:

1. t<sub>CISKEW</sub> represents the total amount of skew consumed by the controller between MDQS*n* and any corresponding bit that will be captured with MDQS*n*. This should be subtracted from the total timing budget.

The amount of skew that can be tolerated from MDQS to a corresponding MDQ signal is called t<sub>DISKEW</sub>. This can be determined by the following equation: t<sub>DISKEW</sub> = ±[T/4 - It<sub>CISKEW</sub>] where T is the MCK clock period and It<sub>CISKEW</sub> is the absolute value of t<sub>CISKEW</sub>.

3. This specification applies only to DDR2 interface.

| Parameter                                                               | Symbol          | Min | Мах | Unit |

|-------------------------------------------------------------------------|-----------------|-----|-----|------|

| Low-level output voltage,<br>I <sub>OL</sub> = 100 μA                   | V <sub>OL</sub> | _   | 0.2 | V    |

| Input current,<br>(0 V $\leq$ V <sub>IN</sub> $\leq$ OV <sub>DD</sub> ) | I <sub>IN</sub> | _   | ±30 | μΑ   |

### Table 22. DUART DC Electrical Characteristics (continued)

Note: The symbol  $V_{IN}$ , in this case, represents the  $OV_{IN}$  symbol referenced in Table 2.

### 7.2 DUART AC Electrical Specifications

this table provides the AC timing parameters for the DUART interface of the device.

#### Table 23. DUART AC Timing Specifications

| Parameter         | Value       | Unit | Note |

|-------------------|-------------|------|------|

| Minimum baud rate | 256         | baud | —    |

| Maximum baud rate | > 1,000,000 | baud | 1    |

| Oversample rate   | 16          |      | 2    |

#### Notes:

1. Actual attainable baud rate will be limited by the latency of interrupt processing.

2. The middle of a start bit is detected as the 8<sup>th</sup> sampled 0 after the 1-to-0 transition of the start bit. Subsequent bit values are sampled each 16<sup>th</sup> sample.

# 8 Ethernet: Enhanced Three-Speed Ethernet (eTSEC)

This section provides the AC and DC electrical characteristics for the enhanced three-speed Ethernet controller.

### 8.1 Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1000 Mbps)—MII/RGMII/RTBI/RMII DC Electrical Characteristics

The electrical characteristics specified here apply to media independent interface (MII), reduced gigabit media independent interface (RGMII), reduced ten-bit interface (RTBI), reduced media independent interface (RMII) signals, management data input/output (MDIO) and management data clock (MDC).

The MII and RMII interfaces are defined for 3.3 V, while the RGMII and RTBI interfaces can be operated at 2.5 V. The RGMII and RTBI interfaces follow the *Reduced Gigabit Media-Independent Interface* (*RGMII*) Specification Version 1.3. The RMII interface follows the *RMII Consortium RMII Specification Version 1.2*.

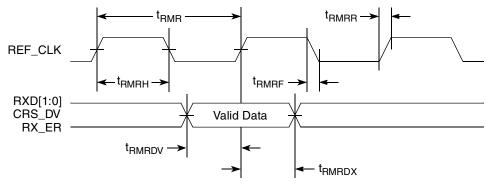

This figure shows the RMII receive AC timing diagram.

Figure 14. RMII Receive AC Timing Diagram

### 8.3 Management Interface Electrical Characteristics

The electrical characteristics specified here apply to MII management interface signals MDIO (management data input/output) and MDC (management data clock).

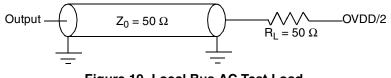

This figure provides the AC test load for eTSEC.

Figure 15. eTSEC AC Test Load

### 8.3.1 MII Management DC Electrical Characteristics

The MDC and MDIO are defined to operate at a supply voltage of 2.5 V or 3.3 V. The DC electrical characteristics for MDIO and MDC are provided in Table 31 and Table 32.

| Table 31. MII Management DC Electrical Characteristics When Powered at 2.5 V |

|------------------------------------------------------------------------------|

|------------------------------------------------------------------------------|

| Parameter              | Co                        | onditions                        | Symbol            | Min       | Мах                     | Unit |

|------------------------|---------------------------|----------------------------------|-------------------|-----------|-------------------------|------|

| Supply voltage (2.5 V) |                           | _                                | LV <sub>DD1</sub> | 2.37      | 2.63                    | V    |

| Output high voltage    | I <sub>OH</sub> = -1.0 mA | LV <sub>DD1</sub> = Min          | V <sub>OH</sub>   | 2.00      | LV <sub>DD1</sub> + 0.3 | V    |

| Output low voltage     | I <sub>OL</sub> = 1.0 mA  | LV <sub>DD1</sub> = Min          | V <sub>OL</sub>   | GND – 0.3 | 0.40                    | V    |

| Input high voltage     | _                         | LV <sub>DD1</sub> = Min          | V <sub>IH</sub>   | 1.7       | _                       | V    |

| Input low voltage      | _                         | LV <sub>DD1</sub> = Min          | V <sub>IL</sub>   | -0.3      | 0.70                    | V    |

| Input high current     | V <sub>II</sub>           | <sub>N</sub> = LV <sub>DD1</sub> | I <sub>IH</sub>   | —         | 20                      | μΑ   |

| Input low current      | VI                        | $_{\rm N} = {\rm LV}_{\rm DD1}$  | I <sub>IL</sub>   | -15       | _                       | μΑ   |

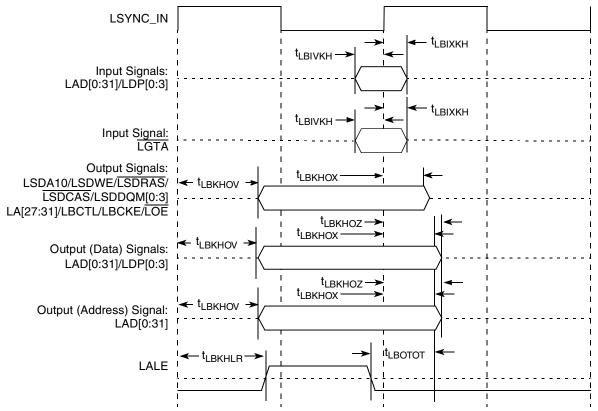

This table describes the general timing parameters of the local bus interface of the device when in PLL bypass mode.

| Parameter                                                   | Symbol <sup>1</sup>  | Min | Max | Unit | Note |

|-------------------------------------------------------------|----------------------|-----|-----|------|------|

| Local bus cycle time                                        | t <sub>LBK</sub>     | 15  | —   | ns   | 2    |

| Input setup to local bus clock                              | t <sub>LBIVKH</sub>  | 7.0 | —   | ns   | 3, 4 |

| Input hold from local bus clock                             | t <sub>LBIXKH</sub>  | 1.0 | —   | ns   | 3, 4 |

| LALE output fall to LAD output transition (LATCH hold time) | t <sub>LBOTOT1</sub> | 1.5 | —   | ns   | 5    |

| LALE output fall to LAD output transition (LATCH hold time) | t <sub>LBOTOT2</sub> | 3.0 | —   | ns   | 6    |

| LALE output fall to LAD output transition (LATCH hold time) | t <sub>LBOTOT3</sub> | 2.5 | —   | ns   | 7    |

| Local bus clock to LALE rise                                | t <sub>LBKHLR</sub>  | —   | 4.5 | ns   | _    |

| Local bus clock to output valid                             | t <sub>LBKHOV</sub>  | —   | 3.0 | ns   | 3    |

| Local bus clock to output high impedance for LAD/LDP        | t <sub>lbkhoz</sub>  | —   | 4.0 | ns   | 3, 8 |

### Table 40. Local Bus General Timing Parameters—PLL Bypass Mode

#### Notes:

The symbols used for timing specifications herein follow the pattern of t<sub>(First two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(First two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one(1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the output (O) going invalid (X) or output hold time.

- All timings are in reference to falling edge of LCLK0 (for all outputs and for LGTA and LUPWAIT inputs) or rising edge of LCLK0 (for all other inputs).

- 3. All signals are measured from LBV<sub>DD</sub>/2 of the rising/falling edge of LCLK0 to  $0.4 \times LBV_{DD}$  of the signal in question for 3.3-V signaling levels.

- 4. Input timings are measured at the pin.

- 5. t<sub>LBOTOT1</sub> should be used when LBCR[AHD] is set and the load on LALE output pin is at least 10pF less than the load on LAD output pins.

- t<sub>LBOTOT2</sub> should be used when LBCR[AHD] is not set and the load on LALE output pin is at least 10pF less than the load on LAD output pins.

- 7. t<sub>LBOTOT3</sub> should be used when LBCR[AHD] is not set and the load on LALE output pin equals to the load on LAD output pins.

- 8. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

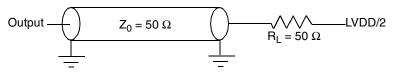

This figure provides the AC test load for the local bus.

Figure 19. Local Bus AC Test Load

This figures show the local bus signals.

Figure 20. Local Bus Signals, Non-special Signals Only (PLL Enable Mode)

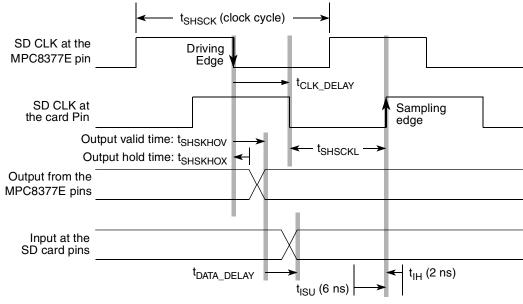

### t<sub>CLK\_DELAY</sub> + t<sub>IH</sub> - t<sub>SFSKHOX</sub> < t<sub>SFSCKL</sub>+ t<sub>DATA\_DELAY</sub>

This means that clock can be delayed versus data up to 15 ns (external delay line) in ideal case of  $t_{SFSCLKL} = 20$  ns:

$t_{CLK\_DELAY} + 5 - 0 < 20 + t_{DATA\_DELAY}$  $t_{CLK\_DELAY} < 15 + t_{DATA\_DELAY}$

### 11.2.1.3 Full-Speed Write Combined Formula

The following equation is the combined formula to calculate the allowed skew range between the SD\_CLK and SD\_DAT/CMD signals on the PCB.

```

t_{CLK\_DELAY} + t_{IH} - t_{SFSKHOX} < t_{SFSCKL} + t_{DATA\_DELAY} < t_{SFSCK} + t_{CLK\_DELAY} - t_{ISU} - t_{SFSKHOV} Eqn. 6

```

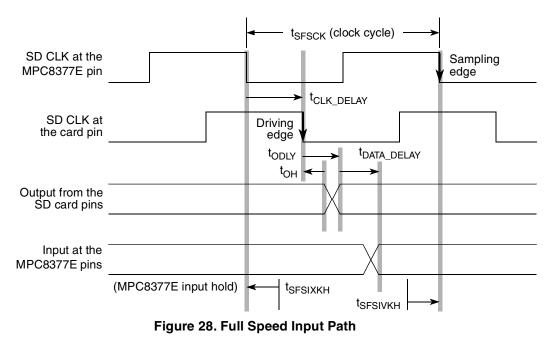

### 11.2.2 Full-Speed Input Path (Read)

This figure provides the data and command input timing diagram.

### 11.2.2.1 Full-Speed Read Meeting Setup (Maximum Delay)

The following equations show how to calculate the allowed combined propagation delay range of the SD\_CLK and SD\_DAT/CMD signals on the PCB.

$$t_{CLK\_DELAY} + t_{DATA\_DELAY} + t_{ODLY} + t_{SFSIVKH} < t_{SFSCK} Eqn. 7$$

$$t_{CLK\_DELAY} + t_{DATA\_DELAY} < t_{SFSCK} - t_{ODLY} - t_{SFSIVKH} - t_{INT\_CLK\_DLY} Eqn. 8$$

Eqn. 5

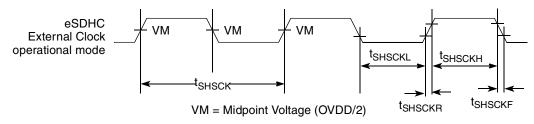

This figure provides the eSDHC clock input timing diagram.

Figure 29. eSDHC Clock Input Timing Diagram

### 11.3.1 High-Speed Output Path (Write)

This figure provides the data and command output timing diagram.

Figure 30. High Speed Output Path

### 11.3.1.1 High-Speed Write Meeting Setup (Maximum Delay)

The following equations show how to calculate the allowed skew range between the SD\_CLK and SD\_DAT/CMD signals on the PCB.

Zero clock delay:

$$t_{SHSKHOV} + t_{DATA_{DELAY}} + t_{ISU} < t_{SHSCKL}$$

Eqn. 10

With clock delay:

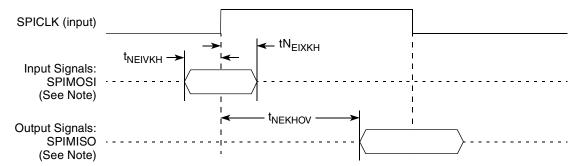

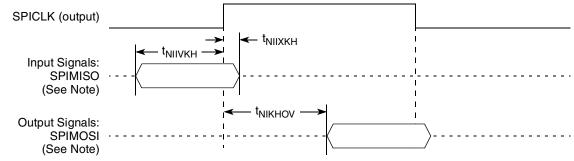

This figure shows the SPI timing in slave mode (external clock).

Note: The clock edge is selectable on SPI.

This figure shows the SPI timing in master mode (internal clock).

Note: The clock edge is selectable on SPI.

Figure 50. SPI AC Timing in Master Mode (Internal Clock) Diagram

# 21 High-Speed Serial Interfaces (HSSI)

This chip features two serializer/deserializer (SerDes) interfaces to be used for high-speed serial interconnect applications. See Table 1 for the interfaces supported.

This section describes the common portion of SerDes DC electrical specifications, which is the DC requirement for SerDes reference clocks. The SerDes data lane's transmitter and receiver reference circuits are also shown.

### 21.1 Signal Terms Definition

The SerDes utilizes differential signaling to transfer data across the serial link. This section defines terms used in the description and specification of differential signals.

Figure 51 shows how the signals are defined. For illustration purpose, only one SerDes lane is used for description. The figure shows waveform for either a transmitter output (SD*n*\_TX and  $\overline{SDn}_T\overline{X}$ ) or a receiver input (SD*n*\_RX and  $\overline{SDn}_R\overline{X}$ ). Each signal swings between A volts and B volts where A > B.

| Signal | Package Pin Number | Pin Type | Power Supply | Note |

|--------|--------------------|----------|--------------|------|

| MDQ2   | C7                 | I/O      | GVDD         | 11   |

| MDQ3   | D8                 | I/O      | GVDD         | 11   |

| MDQ4   | A7                 | I/O      | GVDD         | 11   |

| MDQ5   | A5                 | I/O      | GVDD         | 11   |

| MDQ6   | A3                 | I/O      | GVDD         | 11   |

| MDQ7   | C6                 | I/O      | GVDD         | 11   |

| MDQ8   | D7                 | I/O      | GVDD         | 11   |

| MDQ9   | E8                 | I/O      | GVDD         | 11   |

| MDQ10  | B1                 | I/O      | GVDD         | 11   |

| MDQ11  | D5                 | I/O      | GVDD         | 11   |

| MDQ12  | ВЗ                 | I/O      | GVDD         | 11   |

| MDQ13  | D6                 | I/O      | GVDD         | 11   |

| MDQ14  | C3                 | I/O      | GVDD         | 11   |

| MDQ15  | C2                 | I/O      | GVDD         | 11   |

| MDQ16  | D4                 | I/O      | GVDD         | 11   |

| MDQ17  | E6                 | I/O      | GVDD         | 11   |

| MDQ18  | F6                 | I/O      | GVDD         | 11   |

| MDQ19  | G4                 | I/O      | GVDD         | 11   |

| MDQ20  | F8                 | I/O      | GVDD         | 11   |

| MDQ21  | E4                 | I/O      | GVDD         | 11   |

| MDQ22  | C1                 | I/O      | GVDD         | 11   |

| MDQ23  | G6                 | I/O      | GVDD         | 11   |

| MDQ24  | F2                 | I/O      | GVDD         | 11   |

| MDQ25  | G5                 | I/O      | GVDD         | 11   |

| MDQ26  | H6                 | I/O      | GVDD         | 11   |

| MDQ27  | H4                 | I/O      | GVDD         | 11   |

| MDQ28  | D1                 | I/O      | GVDD         | 11   |

| MDQ29  | G3                 | I/O      | GVDD         | 11   |

| MDQ30  | H5                 | I/O      | GVDD         | 11   |

| MDQ31  | F1                 | I/O      | GVDD         | 11   |

| MDQ32  | W6                 | I/O      | GVDD         | 11   |

| MDQ33  | AC1                | I/O      | GVDD         | 11   |

| MDQ34  | AC3                | I/O      | GVDD         | 11   |

| Signal                            | Package Pin Number | Pin Type | Power Supply | Note |

|-----------------------------------|--------------------|----------|--------------|------|

| MDQS4                             | AB5                | I/O      | GVDD         | 11   |

| MDQS5                             | AD1                | I/O      | GVDD         | 11   |

| MDQS6                             | AH1                | I/O      | GVDD         | 11   |

| MDQS7                             | AJ3                | I/O      | GVDD         | 11   |

| MDQS8                             | G1                 | I/O      | GVDD         | 11   |

| MECC0/MSRCID0                     | J6                 | I/O      | GVDD         | _    |

| MECC1/MSRCID1                     | J3                 | I/O      | GVDD         |      |

| MECC2/MSRCID2                     | K2                 | I/O      | GVDD         | _    |

| MECC3/MSRCID3                     | К3                 | I/O      | GVDD         | _    |

| MECC4/MSRCID4                     | J5                 | I/O      | GVDD         | _    |

| MECC5/MDVAL                       | J2                 | I/O      | GVDD         | _    |

| MECC6                             | L5                 | I/O      | GVDD         | _    |

| MECC7                             | L2                 | I/O      | GVDD         | _    |

| MODT0                             | N5                 | 0        | GVDD         | 6    |

| MODT1                             | U6                 | 0        | GVDD         | 6    |

| MODT2                             | M6                 | 0        | GVDD         | 6    |

| MODT3                             | P6                 | 0        | GVDD         | 6    |

| MRAS_B                            | AA3                | 0        | GVDD         | _    |

| MVREF1                            | K4                 | I        | GVDD         | 11   |

| MVREF2                            | W4                 | I        | GVDD         | 11   |

| MWE_B                             | Y2                 | 0        | GVDD         | _    |

|                                   | DUART Interface    |          | 1            |      |

| UART_SIN1/<br>MSRCID2/LSRCID2     | L28                | I/O      | OVDD         | _    |

| UART_SOUT1/<br>MSRCID0/LSRCID0    | L27                | 0        | OVDD         |      |

| UART_CTS_B[1]/<br>MSRCID4/LSRCID4 | K26                | I/O      | OVDD         | _    |

| UART_RTS_B1                       | N27                | 0        | OVDD         | _    |

| UART_SIN2/<br>MSRCID3/LSRCID3     | K27                | I/O      | OVDD         | _    |

| UART_SOUT2/<br>MSRCID1/LSRCID1    | K28                | 0        | OVDD         | _    |

| UART_CTS_B[2]/<br>MDVAL/LDVAL     | K29                | I/O      | OVDD         | _    |

| Signal        | Package Pin Number                | Pin Type      | Power Supply | Note |

|---------------|-----------------------------------|---------------|--------------|------|

| UART_RTS_B[2] | L29                               | 0             | OVDD         | _    |

|               | Enhanced Local Bus Controller (eL | BC) Interface |              |      |

| LAD0          | E24                               | I/O           | LBVDD        | _    |

| LAD1          | G28                               | I/O           | LBVDD        |      |

| LAD2          | H25                               | I/O           | LBVDD        |      |

| LAD3          | F26                               | I/O           | LBVDD        |      |

| LAD4          | C26                               | I/O           | LBVDD        | _    |

| LAD5          | J28                               | I/O           | LBVDD        | _    |

| LAD6          | F21                               | I/O           | LBVDD        |      |

| LAD7          | F23                               | I/O           | LBVDD        | _    |

| LAD8          | E25                               | I/O           | LBVDD        | _    |

| LAD9          | E26                               | I/O           | LBVDD        | _    |

| LAD10         | A23                               | I/O           | LBVDD        |      |

| LAD11         | F24                               | I/O           | LBVDD        |      |

| LAD12         | G24                               | I/O           | LBVDD        |      |

| LAD13         | F25                               | I/O           | LBVDD        |      |

| LAD14         | H28                               | I/O           | LBVDD        |      |

| LAD15         | G25                               | I/O           | LBVDD        |      |

| LA11/LAD16    | F27                               | I/O           | LBVDD        |      |

| LA12/LAD17    | B21                               | I/O           | LBVDD        |      |

| LA13/LAD18    | A25                               | I/O           | LBVDD        |      |

| LA14/LAD19    | C28                               | I/O           | LBVDD        |      |

| LA15/LAD20    | H24                               | I/O           | LBVDD        |      |

| LA16/LAD21    | E23                               | I/O           | LBVDD        |      |

| LA17/LAD22    | B28                               | I/O           | LBVDD        |      |

| LA18/LAD23    | D28                               | I/O           | LBVDD        |      |

| LA19/LAD24    | A27                               | I/O           | LBVDD        |      |

| LA20/LAD25    | C25                               | I/O           | LBVDD        | _    |

| LA21/LAD26    | B27                               | I/O           | LBVDD        |      |

| LA22/LAD27    | H27                               | I/O           | LBVDD        | —    |

| LA23/LAD28    | E21                               | I/O           | LBVDD        |      |

| LA24/LAD29    | F20                               | I/O           | LBVDD        | _    |

| Signal                                | Package Pin Number | Pin Type | Power Supply | Note |

|---------------------------------------|--------------------|----------|--------------|------|

| LA25/LAD30                            | D29                | I/O      | LBVDD        | _    |

| LA26/LAD31                            | E20                | I/O      | LBVDD        | _    |

| LA27                                  | H26                | 0        | LBVDD        | _    |

| LA28                                  | C29                | 0        | LBVDD        | _    |

| LA29                                  | E28                | 0        | LBVDD        | _    |

| LA30                                  | B26                | 0        | LBVDD        | _    |

| LA31                                  | J25                | 0        | LBVDD        | _    |

| LA10/LALE                             | H29                | 0        | LBVDD        | _    |

| LBCTL                                 | A22                | 0        | LBVDD        | _    |

| LCLK0                                 | B22                | 0        | LBVDD        | _    |

| LCLK1                                 | C23                | 0        | LBVDD        | _    |

| LCLK2                                 | B23                | 0        | LBVDD        | _    |

| LCS_B0                                | D25                | 0        | LBVDD        | _    |

| LCS_B1                                | F19                | 0        | LBVDD        | _    |

| LCS_B2                                | C27                | 0        | LBVDD        | _    |

| LCS_B3                                | D24                | 0        | LBVDD        | _    |

| LCS_B4/LDP0                           | C24                | I/O      | LBVDD        | _    |

| LCS_B5/LDP1                           | B29                | I/O      | LBVDD        | _    |

| LA7/LCS_B6/LDP2                       | E29                | I/O      | LBVDD        | _    |

| LA8/LCS_B7/LDP3                       | F29                | I/O      | LBVDD        | _    |

| LFCLE/LGPL0                           | D21                | 0        | LBVDD        | _    |

| LFALE/LGPL1                           | A26                | 0        | LBVDD        | _    |

| LFRE_B/LGPL2/LOE_B                    | F22                | 0        | LBVDD        | _    |

| LFWP_B/LGPL3                          | C21                | 0        | LBVDD        | _    |

| LGPL4/LFRB_B/LGTA_B/<br>LUPWAIT/LPBSE | J29                | I/O      | LBVDD        | 16   |

| LA9/LGPL5                             | G29                | 0        | LBVDD        |      |

| LSYNC_IN                              | A21                | I        | LBVDD        | _    |

| LSYNC_OUT                             | D23                | 0        | LBVDD        | _    |

| LWE_B0/LFWE0/LBS_B0                   | E22                | 0        | LBVDD        | _    |

| LWE_B1/LFWE1/LBS_B1                   | B25                | 0        | LBVDD        | _    |

| LWE_B2/LFWE2/LBS_B2                   | E27                | 0        | LBVDD        | _    |

| LWE_B3/LFWE3/LBS_B3                   | F28                | 0        | LBVDD        | _    |

| Table 81. Package Thermal Characteristics for TePI | BGA II (continued) |

|----------------------------------------------------|--------------------|

|----------------------------------------------------|--------------------|

| Parameter                                     | Symbol | Value | Unit | Note |

|-----------------------------------------------|--------|-------|------|------|

| Junction-to-package natural convection on top | ΨJT    | 6     | °C/W | 6    |

Notes:

- 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per JEDEC JESD51-2 with the single layer board horizontal. Board meets JESD51-9 specification.

- 3. Per JEDEC JESD51-6 with the board horizontal.

- 4. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

### 24.2 Thermal Management Information

For the following sections,  $P_D = (V_{DD} \times I_{DD}) + P_{I/O}$  where  $P_{I/O}$  is the power dissipation of the I/O drivers.

### 24.2.1 Estimation of Junction Temperature with Junction-to-Ambient Thermal Resistance

An estimation of the chip junction temperature, T<sub>J</sub>, can be obtained from the equation:

$$T_J = T_A + (R_{\theta JA} \times P_D)$$

where:

$T_J$  = junction temperature (°C)  $T_A$  = ambient temperature for the package (°C)  $R_{\theta JA}$  = junction to ambient thermal resistance (°C/W)  $P_D$  = power dissipation in the package (W)

The junction to ambient thermal resistance is an industry-standard value that provides a quick and easy estimation of thermal performance. Generally, the value obtained on a single layer board is appropriate for a tightly packed printed circuit board. The value obtained on the board with the internal planes is usually appropriate if the board has low power dissipation and the components are well separated. Test cases have demonstrated that errors of a factor of two (in the quantity  $T_I - T_A$ ) are possible.

# 24.2.2 Estimation of Junction Temperature with Junction-to-Board Thermal Resistance

### NOTE

The heat sink cannot be mounted on the package.

The thermal performance of a device cannot be adequately predicted from the junction to ambient thermal resistance. The thermal performance of any component is strongly dependent on the power dissipation of surrounding components. In addition, the ambient temperature varies widely within the application. For many natural convection and especially closed box applications, the board temperature at the perimeter (edge) of the package is approximately the same as the local air temperature near the device. Specifying the local ambient conditions explicitly as the board temperature provides a more precise description of the local ambient conditions that determine the temperature of the device.

At a known board temperature, the junction temperature is estimated using the following equation:

$$T_J = T_A + (R_{\theta JB} \times P_D)$$

where:

$T_A$  = ambient temperature for the package (°C)  $R_{\theta JB}$  = junction to board thermal resistance (°C/W) per JESD51-8  $P_D$  = power dissipation in the package (W)

When the heat loss from the package case to the air can be ignored, acceptable predictions of junction temperature can be made. The application board should be similar to the thermal test condition: the component is soldered to a board with internal planes.

### 24.2.3 Experimental Determination of Junction Temperature

### NOTE

The heat sink cannot be mounted on the package.

To determine the junction temperature of the device in the application after prototypes are available, use the thermal characterization parameter ( $\Psi_{JT}$ ) to determine the junction temperature and a measure of the temperature at the top center of the package case using the following equation:

$$T_J = T_T + (\Psi_{JT} \times P_D)$$

where:

$T_J$  = junction temperature (°C)

$T_T$  = thermocouple temperature on top of package (°C)

$\Psi_{JT}$  = junction to ambient thermal resistance (°C/W)

$P_D$  = power dissipation in the package (W)

The thermal characterization parameter is measured per the JESD51-2 specification using a 40 gauge type T thermocouple epoxied to the top center of the package case. The thermocouple should be positioned so that the thermocouple junction rests on the package. A small amount of epoxy is placed over the thermocouple junction and over about 1 mm of wire extending from the junction. The thermocouple wire is placed flat against the package case to avoid measurement errors caused by cooling effects of the thermocouple wire.

### 24.2.4 Heat Sinks and Junction-to-Case Thermal Resistance

For the power values the device is expected to operate at, it is anticipated that a heat sink will be required. A preliminary estimate of heat sink performance can be obtained from the following first-cut approach.