#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Active                                                      |

|---------------------------------|-------------------------------------------------------------|

| Core Processor                  | PowerPC e300c4s                                             |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                              |

| Speed                           | 800MHz                                                      |

| Co-Processors/DSP               | Security; SEC 3.0                                           |

| RAM Controllers                 | DDR, DDR2                                                   |

| Graphics Acceleration           | No                                                          |

| Display & Interface Controllers | -                                                           |

| Ethernet                        | 10/100/1000Mbps (2)                                         |

| SATA                            | SATA 3Gbps (2)                                              |

| USB                             | USB 2.0 + PHY (1)                                           |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                            |

| Operating Temperature           | 0°C ~ 125°C (TA)                                            |

| Security Features               | Cryptography, Random Number Generator                       |

| Package / Case                  | 689-BBGA Exposed Pad                                        |

| Supplier Device Package         | 689-TEPBGA II (31x31)                                       |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc8377evranga |

|                                 |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.12 Enhanced Secured Digital Host Controller (eSDHC)

The enhanced SD host controller (eSDHC) has the following features:

- Conforms to SD Host Controller Standard Specification, Rev 2.0 with Test Event register support.

- Compatible with the MMC System Specification, Rev 4.0

- Compatible with the *SD Memory Card Specification, Rev 2.0*, and supports High Capacity SD memory cards

- Compatible with the SDIO Card Specification Rev, 1.2

- Designed to work with SD Memory, miniSD Memory, SDIO, miniSDIO, SD Combo, MMC, MMC*plus*, MMC 4x, and RS-MMC cards

- SD bus clock frequency up to 50 MHz

- Supports 1-/4-bit SD and SDIO modes, 1-/4-bit MMC modes

- Supports internal DMA capabilities

# 2 Electrical Characteristics

This section provides the AC and DC electrical specifications and thermal characteristics for the chip. The device is currently targeted to these specifications. Some of these specifications are independent of the I/O cell, but are included for a more complete reference. These are not purely I/O buffer design specifications.

## 2.1 **Overall DC Electrical Characteristics**

This section covers the ratings, conditions, and other characteristics.

## 2.1.1 Absolute Maximum Ratings

This table provides the absolute maximum ratings.

| Table 2. | Absolute | Maximum | Ratings <sup>1</sup> |

|----------|----------|---------|----------------------|

|----------|----------|---------|----------------------|

| Characteristic                                                                          | Symbol                           | Max Value                    | Unit | Note |

|-----------------------------------------------------------------------------------------|----------------------------------|------------------------------|------|------|

| Core supply voltage                                                                     | V <sub>DD</sub>                  | –0.3 to 1.1                  | V    |      |

| PLL supply voltage (e300 core, eLBC, and system)                                        | AV <sub>DD</sub>                 | -0.3 to 1.1                  | V    | _    |

| DDR1 and DDR2 DRAM I/O voltage                                                          | GV <sub>DD</sub>                 | –0.3 to 2.75<br>–0.3 to 1.98 | V    | —    |

| Three-speed Ethernet I/O, MII management voltage                                        | LV <sub>DD</sub> [1,2]           | -0.3 to 3.63                 | V    | —    |

| PCI, DUART, system control and power management, I <sup>2</sup> C, and JTAG I/O voltage | OV <sub>DD</sub>                 | -0.3 to 3.63                 | V    | _    |

| Local bus                                                                               | LBV <sub>DD</sub>                | -0.3 to 3.63                 | V    | —    |

| SerDes                                                                                  | L[1,2]_ <i>n</i> V <sub>DD</sub> | -0.3 to 1.1                  | V    | 6    |

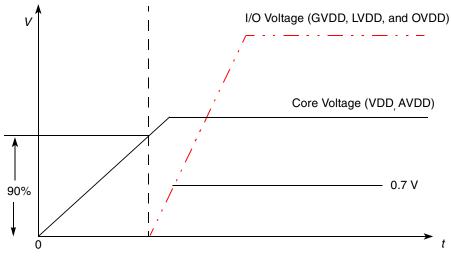

voltage supplies— $GV_{DD}$ ,  $LV_{DD}$ , and  $OV_{DD}$ —do not have any ordering requirements with respect to one another.

Figure 3. Power-Up Sequencing Example

Note that the SerDes power supply  $(L[1,2]_nV_{DD})$  should follow the same timing as the core supply  $(V_{DD})$ .

The device does not require the core supply voltage and I/O supply voltages to be powered down in any particular order.

# **3** Power Characteristics

The estimated typical power dissipation for the chip device is shown in this table.

| Core Frequency<br>(MHz) | CSB/DDR Frequency<br>(MHz) | Sleep Power<br>at T <sub>j</sub> = 65°C (W) $^2$ | Typical Application<br>at $T_j = 65^{\circ}C$ (W) <sup>2</sup> | Typical Application at $T_j = 125^{\circ}C$ (W) <sup>3</sup> | Max Application at $T_j = 125^{\circ}C$ (W) <sup>4</sup> |

|-------------------------|----------------------------|--------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------|

| 333                     | 333                        | 1.45                                             | 1.9                                                            | 3.2                                                          | 3.8                                                      |

| 333                     | 167                        | 1.45                                             | 1.8                                                            | 3.0                                                          | 3.6                                                      |

| 400                     | 400                        | 1.45                                             | 2.0                                                            | 3.3                                                          | 4.0                                                      |

| 400                     | 266                        | 1.45                                             | 1.9                                                            | 3.1                                                          | 3.8                                                      |

| 450                     | 300                        | 1.45                                             | 2.0                                                            | 3.2                                                          | 3.8                                                      |

| 450                     | 225                        | 1.45                                             | 1.9                                                            | 3.1                                                          | 3.7                                                      |

| 500                     | 333                        | 1.45                                             | 2.0                                                            | 3.3                                                          | 3.9                                                      |

| 500                     | 250                        | 1.45                                             | 1.9                                                            | 3.2                                                          | 3.8                                                      |

| 522                     | 355                        | 1.45                                             | 2.0                                                            | 3.3                                                          | 4.0                                                      |

| 533                     | 266                        | 1.45                                             | 2.0                                                            | 3.2                                                          | 3.9                                                      |

Table 5. Power Dissipation <sup>1</sup>

## 4.3 eTSEC Gigabit Reference Clock Timing

This table provides the eTSEC gigabit reference clocks (EC\_GTX\_CLK125) AC timing specifications.

|     |      | ٦ | Table 9. E | C_GTX   | _CLK125 | AC Tin | ning Specifications |  |

|-----|------|---|------------|---------|---------|--------|---------------------|--|

| • • | <br> |   |            | ~ ~ ~ ~ |         |        |                     |  |

| At recommended operating conditions with $LV_{DD}$ = 2.5 ± 0.125 mV/ 3.3 V ± 165 mV |  |

|-------------------------------------------------------------------------------------|--|

|                                                                                     |  |

| Parameter/Condition                                                                                                                                       | Symbol                                 | Min | Typical | Мах         | Unit | Note |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-----|---------|-------------|------|------|

| EC_GTX_CLK125 frequency                                                                                                                                   | t <sub>G125</sub>                      | —   | 125     | —           | MHz  | _    |

| EC_GTX_CLK125 cycle time                                                                                                                                  | t <sub>G125</sub>                      | —   | 8       | —           | ns   | _    |

| EC_GTX_CLK rise and fall time $\label{eq:LV} \begin{array}{c} \text{LV}_{\text{DD}} = 2.5 \text{ V} \\ \text{LV}_{\text{DD}} = 3.3 \text{ V} \end{array}$ | t <sub>G125R</sub> /t <sub>G125F</sub> | _   | _       | 0.75<br>1.0 | ns   | 1    |

| EC_GTX_CLK125 duty cycle<br>1000Base-T for RGMII, RTBI                                                                                                    | t <sub>G125H</sub> /t <sub>G125</sub>  | 47  | —       | 53          | %    | 2    |

| EC_GTX_CLK125 jitter                                                                                                                                      | —                                      | —   | —       | ±150        | ps   | 2    |

Notes:

1. Rise and fall times for EC\_GTX\_CLK125 are measured from 0.5 and 2.0 V for  $LV_{DD}$  = 2.5 V and from 0.6 and 2.7 V for  $LV_{DD}$  = 3.3 V.

EC\_GTX\_CLK125 is used to generate the GTX clock for the eTSEC transmitter with 2% degradation. The EC\_GTX\_CLK125 duty cycle can be loosened from 47%/53% as long as the PHY device can tolerate the duty cycle generated by the eTSEC GTX\_CLK. See Section 8.2.2, "RGMII and RTBI AC Timing Specifications," for the duty cycle for 10Base-T and 100Base-T reference clock.

# 5 **RESET Initialization**

This section describes the DC and AC electrical specifications for the reset initialization timing and electrical requirements of the chip.

## 5.1 **RESET DC Electrical Characteristics**

This table provides the DC electrical characteristics for the RESET pins of the device.

| Characteristic      | Symbol          | Condition                 | Min  | Мах                    | Unit |

|---------------------|-----------------|---------------------------|------|------------------------|------|

| Input high voltage  | V <sub>IH</sub> | —                         | 2.0  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | —                         | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> | _                         | —    | ± 30                   | μA   |

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -8.0 mA | 2.4  | —                      | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA  | —    | 0.5                    | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA  | —    | 0.4                    | V    |

Table 10. RESET Pins DC Electrical Characteristics

Notes:

• This table applies for pins PORESET and HRESET. The PORESET is input pin, thus stated output voltages are not relevant.

• HRESET and SRESET are open drain pin, thus V<sub>OH</sub> is not relevant for these pins.

## 5.2 **RESET AC Electrical Characteristics**

This table provides the reset initialization AC timing specifications of the device.

| Parameter/Condition                                                                                                                                                          | Min | Max | Unit                     | Note |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|--------------------------|------|

| Required assertion time of HRESET to activate reset flow                                                                                                                     | 32  | _   | t <sub>PCI_SYNC_IN</sub> | 1    |

| Required assertion time of $\overrightarrow{\text{PORESET}}$ with stable clock applied to CLKIN when the device is in PCI host mode                                          | 32  | —   | t <sub>CLKIN</sub>       | 2    |

| Required assertion time of $\overrightarrow{\text{PORESET}}$ with stable clock applied to PCI_CLK when the device is in PCI agent mode                                       | 32  | —   | t <sub>PCI_SYNC_IN</sub> | 1    |

| HRESET assertion (output)                                                                                                                                                    | 512 | _   | t <sub>PCI_SYNC_IN</sub> | 1    |

| HRESET negation to negation (output)                                                                                                                                         | 16  | —   | t <sub>PCI_SYNC_IN</sub> | 1    |

| Input setup time for POR config signals (CFG_RESET_SOURCE[0:3],<br>CFG_CLKIN_DIV, and CFG_LBMUX) with respect to negation of PORESET<br>when the device is in PCI host mode  | 4   | —   | t <sub>CLKIN</sub>       | 2    |

| Input setup time for POR config signals (CFG_RESET_SOURCE[0:3],<br>CFG_CLKIN_DIV, and CFG_LBMUX) with respect to negation of PORESET<br>when the device is in PCI agent mode | 4   | —   | <sup>t</sup> PCI_SYNC_IN | 1    |

| Input hold time for POR config signals with respect to negation of HRESET                                                                                                    | 0   | —   | ns                       | _    |

| Time for the device to turn off POR config signals with respect to the assertion of HRESET                                                                                   | _   | 4   | ns                       | 3    |

| Time for the device to start driving functional output signals multiplexed with the POR configuration signals with respect to the negation of HRESET                         | 1   | —   | t <sub>PCI_SYNC_IN</sub> | 1, 3 |

#### Table 11. RESET Initialization Timing Specifications

#### Notes:

1. t<sub>PCI\_SYNC\_IN</sub> is the clock period of the input clock applied to PCI\_SYNC\_IN. When the device is In PCI host mode the primary clock is applied to the CLKIN input, and PCI\_SYNC\_IN period depends on the value of CFG\_CLKIN\_DIV. See the *MPC8379E Integrated Host Processor Reference Manual* for more details.

2. t<sub>CLKIN</sub> is the clock period of the input clock applied to CLKIN. It is only valid when the device is in PCI host mode. See the *MPC8379E Integrated Host Processor Reference Manual* for more details.

3. POR config signals consists of CFG\_RESET\_SOURCE[0:3], CFG\_LBMUX, and CFG\_CLKIN\_DIV.

#### Table 12 provides the PLL lock times.

#### Table 12. PLL Lock Times

| Parameter      | Min | Мах | Unit | Note |

|----------------|-----|-----|------|------|

| PLL lock times | —   | 100 | μs   | —    |

Note:

• The device guarantees the PLL lock if the clock settings are within spec range. The core clock also depends on the core PLL ratio. See Section 23, "Clocking," for more information.

# 6 DDR1 and DDR2 SDRAM

This section describes the DC and AC electrical specifications for the DDR SDRAM interface of the chip. Note that DDR1 SDRAM is  $GV_{DD}(typ) = 2.5 \text{ V}$  and DDR2 SDRAM is  $GV_{DD}(typ) = 1.8 \text{ V}$ .

## 6.1 DDR1 and DDR2 SDRAM DC Electrical Characteristics

This table provides the recommended operating conditions for the DDR2 SDRAM component(s) of the device when  $GV_{DD}(typ) = 1.8 \text{ V}$ .

| Parameter                                       | Symbol            | Min                       | Мах                       | Unit | Note |

|-------------------------------------------------|-------------------|---------------------------|---------------------------|------|------|

| I/O supply voltage                              | GV <sub>DD</sub>  | 1.71                      | 1.89                      | V    | 1    |

| I/O reference voltage                           | MV <sub>REF</sub> | $0.49 	imes GV_{DD}$      | $0.51 	imes GV_{DD}$      | V    | 2, 5 |

| I/O termination voltage                         | V <sub>TT</sub>   | MV <sub>REF</sub> - 0.04  | MV <sub>REF</sub> + 0.04  | V    | 3    |

| Input high voltage                              | V <sub>IH</sub>   | MV <sub>REF</sub> + 0.140 | GV <sub>DD</sub> + 0.3    | V    | _    |

| Input low voltage                               | V <sub>IL</sub>   | -0.3                      | MV <sub>REF</sub> – 0.140 | V    | _    |

| Output leakage current                          | I <sub>OZ</sub>   | -50                       | 50                        | μA   | 4    |

| Output high current (V <sub>OUT</sub> = 1.40 V) | I <sub>ОН</sub>   | -13.4                     | _                         | mA   | _    |

| Output low current (V <sub>OUT</sub> = 0.3 V)   | I <sub>OL</sub>   | 13.4                      |                           | mA   |      |

Table 13. DDR2 SDRAM DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 1.8 V

Notes:

1.  $GV_{DD}$  is expected to be within 50 mV of the DRAM  $GV_{DD}$  at all times.

2.  $MV_{REF}$  is expected to be equal to  $0.5 \times GV_{DD}$ , and to track  $GV_{DD}$  DC variations as measured at the receiver. Peak-to-peak noise on  $MV_{REF}$  may not exceed ±2% of the DC value.

3. V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be equal to MV<sub>REF</sub>. This rail should track variations in the DC level of MV<sub>REF</sub>.

4. Output leakage is measured with all outputs disabled,  $0 V \le V_{OUT} \le GV_{DD}$ .

5. See AN3665, "MPC837xE Design Checklist," for proper DDR termination.

Table 14 provides the DDR2 capacitance when  $GV_{DD}(typ) = 1.8$  V.

#### Table 14. DDR2 SDRAM Capacitance for GV<sub>DD</sub>(typ) = 1.8 V

| Parameter                                    | Symbol           | Min | Мах | Unit | Note |

|----------------------------------------------|------------------|-----|-----|------|------|

| Input/output capacitance: DQ, DQS, DQS       | C <sub>IO</sub>  | 6   | 8   | pF   | 1    |

| Delta input/output capacitance: DQ, DQS, DQS | C <sub>DIO</sub> | _   | 0.5 | pF   | 1    |

#### Note:

1. This parameter is sampled.  $GV_{DD}$  = 1.8 V ± 0.090 V, f = 1 MHz, T<sub>A</sub> = 25°C, V<sub>OUT</sub> =  $GV_{DD}/2$ , V<sub>OUT</sub> (peak-to-peak) = 0.2 V.

This table provides the recommended operating conditions for the DDR SDRAM component(s) when  $GV_{DD}(typ) = 2.5 \text{ V}.$

Table 15. DDR SDRAM DC Electrical Characteristics for  $GV_{DD}$  (typ) = 2.5 V

| Parameter               | Symbol Min        |                          | Мах                      | Unit | Note |

|-------------------------|-------------------|--------------------------|--------------------------|------|------|

| I/O supply voltage      | GV <sub>DD</sub>  | 2.375                    | 2.625                    | V    | 1    |

| I/O reference voltage   | MV <sub>REF</sub> | $0.49 	imes GV_{DD}$     | $0.51 	imes GV_{DD}$     | V    | 2, 5 |

| I/O termination voltage | V <sub>TT</sub>   | MV <sub>REF</sub> – 0.04 | MV <sub>REF</sub> + 0.04 | V    | 3    |

| Input high voltage      | V <sub>IH</sub>   | MV <sub>REF</sub> + 0.18 | GV <sub>DD</sub> + 0.3   | V    |      |

## 6.2.2 DDR1 and DDR2 SDRAM Output AC Timing Specifications

This table shows the DDR1 and DDR2 SDRAM output AC timing specifications.

| Table 21. DDRT and DDR2 SDRAM Output AC Timing Specifications                                                                     |                                             |                              |                             |      |      |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------------------------------|-----------------------------|------|------|--|--|--|--|--|

| Parameter                                                                                                                         | Symbol <sup>1</sup>                         | Min                          | Max                         | Unit | Note |  |  |  |  |  |

| MCK <i>n</i> cycle time, MCK <i>n</i> /MCK <i>n</i> crossing                                                                      | t <sub>MCK</sub>                            | 5                            | 10                          | ns   | 2    |  |  |  |  |  |

| ADDR/CMD output setup with respect to MCK<br>400 MHz data rate<br>333 MHz data rate<br>266 MHz data rate<br>200 MHz data rate     | <sup>t</sup> DDKHAS                         | 1.95<br>2.40<br>3.15<br>4.20 | <br>                        | ns   | 3, 7 |  |  |  |  |  |

| ADDR/CMD output hold with respect to MCK<br>400 MHz data rate<br>333 MHz data rate<br>266 MHz data rate<br>200 MHz data rate      | <sup>t</sup> DDKHAX                         | 1.95<br>2.40<br>3.15<br>4.20 | <br>                        | ns   | 3, 7 |  |  |  |  |  |

| MCS <i>n</i> output setup with respect to MCK<br>400 MHz data rate<br>333 MHz data rate<br>266 MHz data rate<br>200 MHz data rate | t <sub>DDKHCS</sub>                         | 1.95<br>2.40<br>3.15<br>4.20 | <br>                        | ns   | 3    |  |  |  |  |  |

| MCS <i>n</i> output hold with respect to MCK<br>400 MHz data rate<br>333 MHz data rate<br>266 MHz data rate<br>200 MHz data rate  | tddkhcx                                     | 1.95<br>2.40<br>3.15<br>4.20 | <br>                        | ns   | 3    |  |  |  |  |  |

| MCK to MDQS skew                                                                                                                  | t <sub>DDKHMH</sub>                         | -0.6                         | 0.6                         | ns   | 4, 8 |  |  |  |  |  |

| MDQ//MDM output setup with respect to MDQS<br>400 MHz data rate<br>333 MHz data rate<br>266 MHz data rate<br>200 MHz data rate    | <sup>t</sup> DDKHDS,<br><sup>t</sup> DDKLDS | 550<br>800<br>1100<br>1200   | <br>                        | ps   | 5, 8 |  |  |  |  |  |

| MDQ//MDM output hold with respect to MDQS<br>400 MHz data rate<br>333 MHz data rate<br>266 MHz data rate<br>200 MHz data rate     | <sup>t</sup> ddkhdx,<br><sup>t</sup> ddkldx | 700<br>800<br>1100<br>1200   | <br>                        | ps   | 5, 8 |  |  |  |  |  |

| MDQS preamble start                                                                                                               | t <sub>DDKHMP</sub>                         | –0.5 × t <sub>MCK</sub> –0.6 | $-0.5 \times t_{MCK} + 0.6$ | ns   | 6, 8 |  |  |  |  |  |

#### Table 21. DDR1 and DDR2 SDRAM Output AC Timing Specifications

| Parameter                                                               | Symbol          | Min | Мах | Unit |

|-------------------------------------------------------------------------|-----------------|-----|-----|------|

| Low-level output voltage,<br>I <sub>OL</sub> = 100 μA                   | V <sub>OL</sub> | _   | 0.2 | V    |

| Input current,<br>(0 V $\leq$ V <sub>IN</sub> $\leq$ OV <sub>DD</sub> ) | I <sub>IN</sub> | _   | ±30 | μΑ   |

#### Table 22. DUART DC Electrical Characteristics (continued)

Note: The symbol  $V_{IN}$ , in this case, represents the  $OV_{IN}$  symbol referenced in Table 2.

## 7.2 DUART AC Electrical Specifications

this table provides the AC timing parameters for the DUART interface of the device.

#### Table 23. DUART AC Timing Specifications

| Parameter         | Value       | Unit | Note |

|-------------------|-------------|------|------|

| Minimum baud rate | 256         | baud | —    |

| Maximum baud rate | > 1,000,000 | baud | 1    |

| Oversample rate   | 16          |      | 2    |

#### Notes:

1. Actual attainable baud rate will be limited by the latency of interrupt processing.

2. The middle of a start bit is detected as the 8<sup>th</sup> sampled 0 after the 1-to-0 transition of the start bit. Subsequent bit values are sampled each 16<sup>th</sup> sample.

# 8 Ethernet: Enhanced Three-Speed Ethernet (eTSEC)

This section provides the AC and DC electrical characteristics for the enhanced three-speed Ethernet controller.

## 8.1 Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1000 Mbps)—MII/RGMII/RTBI/RMII DC Electrical Characteristics

The electrical characteristics specified here apply to media independent interface (MII), reduced gigabit media independent interface (RGMII), reduced ten-bit interface (RTBI), reduced media independent interface (RMII) signals, management data input/output (MDIO) and management data clock (MDC).

The MII and RMII interfaces are defined for 3.3 V, while the RGMII and RTBI interfaces can be operated at 2.5 V. The RGMII and RTBI interfaces follow the *Reduced Gigabit Media-Independent Interface* (*RGMII*) Specification Version 1.3. The RMII interface follows the *RMII Consortium RMII Specification Version 1.2*.

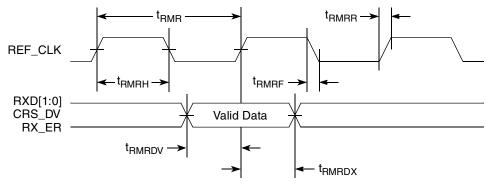

This figure shows the RMII receive AC timing diagram.

Figure 14. RMII Receive AC Timing Diagram

## 8.3 Management Interface Electrical Characteristics

The electrical characteristics specified here apply to MII management interface signals MDIO (management data input/output) and MDC (management data clock).

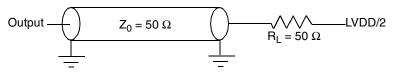

This figure provides the AC test load for eTSEC.

Figure 15. eTSEC AC Test Load

## 8.3.1 MII Management DC Electrical Characteristics

The MDC and MDIO are defined to operate at a supply voltage of 2.5 V or 3.3 V. The DC electrical characteristics for MDIO and MDC are provided in Table 31 and Table 32.

| Table 31. MII Management DC Electrical Characteristics When Powered at 2.5 V |

|------------------------------------------------------------------------------|

|------------------------------------------------------------------------------|

| Parameter              | Conditions                |                                 | Symbol            | Min       | Мах                     | Unit |

|------------------------|---------------------------|---------------------------------|-------------------|-----------|-------------------------|------|

| Supply voltage (2.5 V) |                           | _                               | LV <sub>DD1</sub> | 2.37      | 2.63                    | V    |

| Output high voltage    | I <sub>OH</sub> = -1.0 mA | LV <sub>DD1</sub> = Min         | V <sub>OH</sub>   | 2.00      | LV <sub>DD1</sub> + 0.3 | V    |

| Output low voltage     | I <sub>OL</sub> = 1.0 mA  | LV <sub>DD1</sub> = Min         | V <sub>OL</sub>   | GND – 0.3 | 0.40                    | V    |

| Input high voltage     | _                         | LV <sub>DD1</sub> = Min         | V <sub>IH</sub>   | 1.7       | _                       | V    |

| Input low voltage      | _                         | LV <sub>DD1</sub> = Min         | V <sub>IL</sub>   | -0.3      | 0.70                    | V    |

| Input high current     | V <sub>II</sub>           | $V_{IN} = LV_{DD1}$             |                   | —         | 20                      | μΑ   |

| Input low current      | VI                        | $_{\rm N} = {\rm LV}_{\rm DD1}$ | I <sub>IL</sub>   | -15       | _                       | μΑ   |

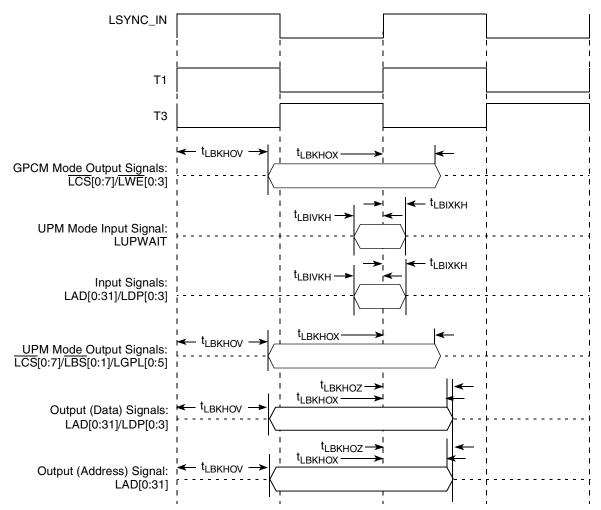

Figure 22. Local Bus Signals, GPCM/UPM Signals for LCRR[CLKDIV] = 2 (PLL Enable Mode)

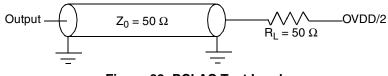

This figure provides the AC test load for PCI.

Figure 39. PCI AC Test Load

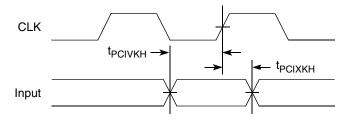

This figure shows the PCI input AC timing conditions.

Figure 40. PCI Input AC Timing Measurement Conditions

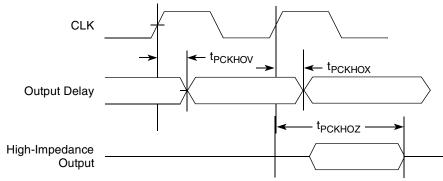

This figure shows the PCI output AC timing conditions.

Figure 41. PCI Output AC Timing Measurement Condition

## **15 PCI Express**

This section describes the DC and AC electrical specifications for the PCI Express bus.

# 15.1 DC Requirements for PCI Express SD\_REF\_CLK and SD\_REF\_CLK

For more information see Section 21, "High-Speed Serial Interfaces (HSSI)."

## 15.5.1 Compliance Test and Measurement Load

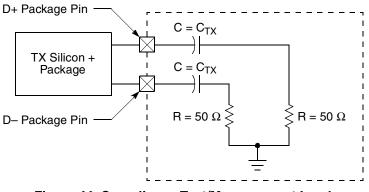

The AC timing and voltage parameters must be verified at the measurement point, as specified within 0.2 inches of the package pins, into a test/measurement load shown in Figure 44.

#### NOTE

The allowance of the measurement point to be within 0.2 inches of the package pins is meant to acknowledge that package/board routing may benefit from D+ and D- not being exactly matched in length at the package pin boundary. If the vendor does not explicitly state where the measurement point is located, the measurement point is assumed to be the D+ and D- package pins.

Figure 44. Compliance Test/Measurement Load

# 16 Serial ATA (SATA)

This section describes the DC and AC electrical specifications for the serial ATA (SATA) of the MPC8377E. Note that the external cabled applications or long backplane applications (Gen1x and Gen2x) are not supported.

## 16.1 Requirements for SATA REF\_CLK

The reference clock is a single ended input clock required for the SATA interface operation. The AC requirements for the SATA reference clock are listed in the Table 54.

| Parameter                                            | Condition        | Symbol                | Min  | Typical     | Мах  | Unit | Note |

|------------------------------------------------------|------------------|-----------------------|------|-------------|------|------|------|

| SD_REF_CLK/ SD_REF_CLK<br>frequency range            | _                | t <sub>CLK_REF</sub>  | —    | 100/125/150 | _    | MHz  | 1    |

| SD_REF_CLK/ SD_REF_CLK<br>clock frequency tolerance  | —                | <sup>t</sup> CLK_TOL  | -350 | 0           | +350 | ppm  | _    |

| SD_REF_CLK/ SD_REF_CLK<br>reference clock duty cycle | Measured at 1.6V | <sup>t</sup> CLK_DUTY | 40   | 50          | 60   | %    | —    |

Table 54. SATA Reference Clock Input Requirements

This table provides the differential transmitter output AC characteristics for the SATA interface at Gen1i or 1.5 Gbits/s transmission.

| Parameter                                 | Symbol                      | Min      | Typical | Мах      | Units             | Note |

|-------------------------------------------|-----------------------------|----------|---------|----------|-------------------|------|

| Channel speed                             | t <sub>CH_SPEED</sub>       | —        | 1.5     | —        | Gbps              | —    |

| Unit interval                             | Τ <sub>UI</sub>             | 666.4333 | 666.667 | 670.2333 | ps                | —    |

| Total jitter, data-data<br>5 UI           | U <sub>SATA_TXTJ5UI</sub>   | —        | —       | 0.355    | UI <sub>p-p</sub> | 1    |

| Total jitter, data-data<br>250 UI         | U <sub>SATA_TXTJ250UI</sub> | —        | —       | 0.47     | UI <sub>p-p</sub> | 1    |

| Deterministic jitter, data-data<br>5 UI   | U <sub>SATA_TXDJ5UI</sub>   | _        | _       | 0.175    | UI <sub>p-p</sub> | 1    |

| Deterministic jitter, data-data<br>250 UI | U <sub>SATA_TXDJ250UI</sub> | _        | _       | 0.22     | UI <sub>p-p</sub> | 1    |

Table 56. Gen1i/1.5G Transmitter AC Specifications

Note:

1. Measured at Tx output pins peak to peak phase variation, random data pattern.

## 16.2.2 Gen2i/3G Transmitter Specifications

This table provides the differential transmitter output DC characteristics for the SATA interface at Gen2i or 3.0 Gbits/s transmission.

Table 57. Gen 2i/3G Transmitter DC Specifications

| Parameter                      | Symbol                     | Min | Typical | Мах | Units             | Note |

|--------------------------------|----------------------------|-----|---------|-----|-------------------|------|

| Tx differential output voltage | V <sub>SATA_TXDIFF</sub>   | 400 | 550     | 700 | mV <sub>p-p</sub> | 1    |

| Tx differential pair impedance | Z <sub>SATA_TXDIFFIM</sub> | 85  | 100     | 115 | Ω                 | —    |

Note:

1. Terminated by 50  $\Omega$  load.

This table provides the differential transmitter output AC characteristics for the SATA interface at Gen2i or 3.0 Gbits/s transmission.

Table 58. Gen 2i/3G Transmitter AC Specifications

| Parameter                                                  | Symbol                       | Min   | Typical | Мах    | Units             | Note |

|------------------------------------------------------------|------------------------------|-------|---------|--------|-------------------|------|

| Channel speed                                              | <sup>t</sup> CH_SPEED        | —     | 3.0     | _      | Gbps              | —    |

| Unit interval                                              | T <sub>UI</sub>              | 333.2 | 333.33  | 335.11 | ps                | —    |

| Total jitter<br>f <sub>C3dB</sub> =f <sub>BAUD</sub> /10   | U <sub>SATA_TXTJfB/10</sub>  | —     | —       | 0.3    | UI <sub>p-p</sub> | 1    |

| Total jitter<br>f <sub>C3dB</sub> = f <sub>BAUD</sub> /500 | U <sub>SATA_TXTJfB/500</sub> | —     | —       | 0.37   | UI <sub>p-p</sub> | 1    |

| Parameter                                          | Symbol                        | Min | Typical | Мах  | Units             | Note |

|----------------------------------------------------|-------------------------------|-----|---------|------|-------------------|------|

| Total jitter<br>$f_{C3dB} = f_{BAUD}/1667$         | U <sub>SATA_TXTJfB/1667</sub> | _   | _       | 0.55 | UI <sub>p-p</sub> | 1    |

| Deterministic jitter<br>$f_{C3dB} = f_{BAUD}/10$   | U <sub>SATA_TXDJfB/10</sub>   | —   | _       | 0.17 | UI <sub>p-p</sub> | 1    |

| Deterministic jitter<br>$f_{C3dB} = f_{BAUD}/500$  | U <sub>SATA_TXDJfB/500</sub>  | _   | _       | 0.19 | UI <sub>p-p</sub> | 1    |

| Deterministic jitter<br>$f_{C3dB} = f_{BAUD}/1667$ | U <sub>SATA_TXDJfB/1667</sub> | —   | —       | 0.35 | UI <sub>p-p</sub> | 1    |

Table 58. Gen 2i/3G Transmitter AC Specifications (continued)

Note:

1. Measured at Tx output pins peak to peak phase variation, random data pattern.

## 16.3 Differential Receiver (Rx) Input Characteristics

This section discusses the Gen1i/1.5G and Gen2i/3G differential receiver input AC characteristics.

## 16.3.1 Gen1i/1.5G Receiver Specifications

This table provides the Gen1i or 1.5 Gbits/s differential receiver input DC characteristics for the SATA interface.

Table 59. Gen1i/1.5G Receiver Input DC Specifications

| Parameter                       | Symbol                   | Min | Typical | Мах | Units             | Note |

|---------------------------------|--------------------------|-----|---------|-----|-------------------|------|

| Differential input voltage      | V <sub>SATA_RXDIFF</sub> | 240 | 500     | 600 | mV <sub>p-p</sub> | 1    |

| Differential Rx input impedance | Z <sub>SATA_RXSEIM</sub> | 85  | 100     | 115 | Ω                 | _    |

Note:

1. Voltage relative to common of either signal comprising a differential pair.

This table provides the Gen1i or 1.5 Gbits/s differential receiver input AC characteristics for the SATA interface.

Table 60. Gen 1i/1.5G Receiver AC Specifications

| Parameter                               | Symbol                      | Min      | Typical | Мах      | Units             | Note |

|-----------------------------------------|-----------------------------|----------|---------|----------|-------------------|------|

| Unit interval                           | T <sub>UI</sub>             | 666.4333 | 666.667 | 670.2333 | ps                | —    |

| Total jitter, data-data<br>5 UI         | U <sub>SATA_TXTJ5UI</sub>   | —        | —       | 0.43     | UI <sub>p-p</sub> | 1    |

| Total jitter, data-data<br>250 UI       | U <sub>SATA_TXTJ250UI</sub> | —        | —       | 0.60     | UI <sub>p-p</sub> | 1    |

| Deterministic jitter, data-data<br>5 UI | U <sub>SATA_TXDJ5UI</sub>   | —        | _       | 0.25     | UI <sub>p-p</sub> | 1    |

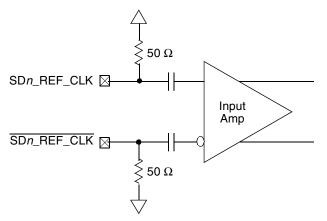

The SerDes reference clock input can be either differential or single-ended. Refer to the Differential Mode and Single-ended Mode description below for further detailed requirements.

- The maximum average current requirement that also determines the common mode voltage range

- When the SerDes reference clock differential inputs are DC coupled externally with the clock driver chip, the maximum average current allowed for each input pin is 8 mA. In this case, the exact common mode input voltage is not critical as long as it is within the range allowed by the maximum average current of 8 mA (refer to the following bullet for more detail), since the input is AC-coupled on-chip.

- This current limitation sets the maximum common mode input voltage to be less than 0.4 V  $(0.4 \text{ V} \div 50 = 8 \text{ mA})$  while the minimum common mode input level is 0.1 V above SGND\_SRDS*n* (xcorevss). For example, a clock with a 50/50 duty cycle can be produced by a clock driver with output driven by its current source from 0 mA to 16 mA (0–0.8 V), such that each phase of the differential input has a single-ended swing from 0 V to 800 mV with the common mode voltage at 400 mV.

- If the device driving the SD*n*\_REF\_CLK and  $\overline{\text{SD}n_\text{REF}\text{-}\text{CLK}}$  inputs cannot drive 50  $\Omega$  to SGND\_SRDS*n* (xcorevss) DC, or it exceeds the maximum input current limitations, then it must be AC-coupled off-chip.

- The input amplitude requirement

- This requirement is described in detail in the following sections.

Figure 52. Receiver of SerDes Reference Clocks

## 21.2.2 DC Level Requirement for SerDes Reference Clocks

The DC level requirement for the device SerDes reference clock inputs is different depending on the signaling mode used to connect the clock driver chip and SerDes reference clock inputs as described below.

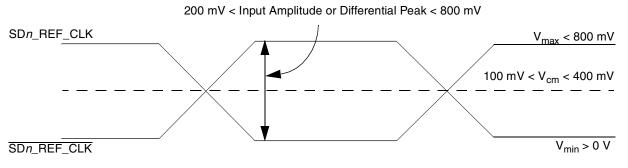

- Differential Mode

- The input amplitude of the differential clock must be between 400 mV and 1600 mV differential peak-peak (or between 200 mV and 800 mV differential peak). In other words, each signal wire of the differential pair must have a single-ended swing less than 800 mV and

greater than 200 mV. This requirement is the same for both external DC-coupled or AC-coupled connection.

- For external DC-coupled connection, as described in Section 21.2.1, "SerDes Reference Clock Receiver Characteristics," the maximum average current requirements sets the requirement for average voltage (common mode voltage) to be between 100 mV and 400 mV.

Figure 53 shows the SerDes reference clock input requirement for DC-coupled connection scheme.

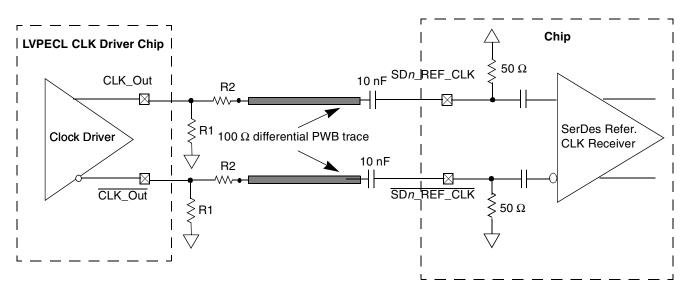

- For external AC-coupled connection, there is no common mode voltage requirement for the clock driver. Since the external AC-coupling capacitor blocks the DC level, the clock driver and the SerDes reference clock receiver operate in different command mode voltages. The SerDes reference clock receiver in this connection scheme has its common mode voltage set to SGND\_SRDSn. Each signal wire of the differential inputs is allowed to swing below and above the command mode voltage (SGND\_SRDSn). Figure 54 shows the SerDes reference clock input requirement for AC-coupled connection scheme.

- Single-ended Mode

- The reference clock can also be single-ended. The SD \_REF\_CLK input amplitude (single-ended swing) must be between 400 mV and 800 mV<sub>p-p</sub> (from V<sub>min</sub> to V<sub>max</sub>) with  $\overline{SDn}_REF_CLK$  either left unconnected or tied to ground.

- The SD*n*\_REF\_CLK input average voltage must be between 200 mV and 400 mV. Figure 55 shows the SerDes reference clock input requirement for single-ended signaling mode.

- To meet the input amplitude requirement, the reference clock inputs might need to be DC or AC-coupled externally. For the best noise performance, the reference of the clock could be DC or AC-coupled into the unused phase (SDn\_REF\_CLK) through the same source impedance as the clock input (SDn\_REF\_CLK) in use.

Figure 53. Differential Reference Clock Input DC Requirements (External DC-Coupled)

driver chip manufacturer to verify whether this connection scheme is compatible with a particular clock driver chip.

Figure 58. AC-Coupled Differential Connection with LVPECL Clock Driver (Reference Only)

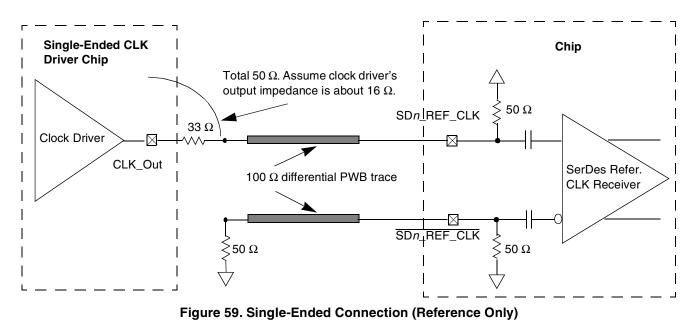

This figure shows the SerDes reference clock connection reference circuits for a single-ended clock driver. It assumes the DC levels of the clock driver are compatible with device SerDes reference clock input's DC requirement.

## 21.2.4 AC Requirements for SerDes Reference Clocks

The clock driver selected should provide a high quality reference clock with low phase noise and cycle-to-cycle jitter. Phase noise less than 100 KHz can be tracked by the PLL and data recovery loops and is less of a problem. Phase noise above 15 MHz is filtered by the PLL. The most problematic phase noise

| Signal | Package Pin Number | Pin Type | Power Supply | Note |

|--------|--------------------|----------|--------------|------|

| MBA2   | M3                 | 0        | GVDD         | _    |

| MCAS_B | W5                 | 0        | GVDD         | _    |

| MCK_B0 | H1                 | 0        | GVDD         | _    |

| MCK_B1 | К1                 | 0        | GVDD         |      |

| MCK_B2 | V1                 | 0        | GVDD         | _    |

| MCK_B3 | W2                 | 0        | GVDD         | _    |

| MCK_B4 | AA1                | 0        | GVDD         | _    |

| MCK_B5 | AB2                | 0        | GVDD         | _    |

| MCK0   | J1                 | 0        | GVDD         | _    |

| MCK1   | L1                 | 0        | GVDD         | _    |

| MCK2   | V2                 | 0        | GVDD         | _    |

| МСКЗ   | W1                 | 0        | GVDD         | _    |

| MCK4   | Y1                 | 0        | GVDD         | _    |

| MCK5   | AB1                | 0        | GVDD         | _    |

| MCKE0  | M4                 | 0        | GVDD         | 3    |

| MCKE1  | R5                 | 0        | GVDD         | 3    |

| MCS_B0 | W3                 | 0        | GVDD         |      |

| MCS_B1 | P3                 | 0        | GVDD         | _    |

| MCS_B2 | T4                 | 0        | GVDD         | _    |

| MCS_B3 | R4                 | 0        | GVDD         | _    |

| MDIC0  | AH8                | I/O      | GVDD         | 9    |

| MDIC1  | AJ8                | I/O      | GVDD         | 9    |

| MDM0   | B6                 | 0        | GVDD         | _    |

| MDM1   | B2                 | 0        | GVDD         | _    |

| MDM2   | E2                 | 0        | GVDD         | _    |

| MDM3   | E1                 | 0        | GVDD         |      |

| MDM4   | Y6                 | 0        | GVDD         |      |

| MDM5   | AC6                | 0        | GVDD         |      |

| MDM6   | AE6                | 0        | GVDD         |      |

| MDM7   | AJ4                | 0        | GVDD         |      |

| MDM8   | L6                 | 0        | GVDD         | _    |

| MDQ0   | A8                 | I/O      | GVDD         | 11   |

| MDQ1   | A6                 | I/O      | GVDD         | 11   |

#### Table 72. TePBGA II Pinout Listing (continued)

| Signal                            | Package Pin Number | Pin Type | Power Supply | Note |

|-----------------------------------|--------------------|----------|--------------|------|

| MDQS4                             | AB5                | I/O      | GVDD         | 11   |

| MDQS5                             | AD1                | I/O      | GVDD         | 11   |

| MDQS6                             | AH1                | I/O      | GVDD         | 11   |

| MDQS7                             | AJ3                | I/O      | GVDD         | 11   |

| MDQS8                             | G1                 | I/O      | GVDD         | 11   |

| MECC0/MSRCID0                     | J6                 | I/O      | GVDD         | _    |

| MECC1/MSRCID1                     | J3                 | I/O      | GVDD         |      |

| MECC2/MSRCID2                     | K2                 | I/O      | GVDD         | _    |

| MECC3/MSRCID3                     | К3                 | I/O      | GVDD         | _    |

| MECC4/MSRCID4                     | J5                 | I/O      | GVDD         | _    |

| MECC5/MDVAL                       | J2                 | I/O      | GVDD         | _    |

| MECC6                             | L5                 | I/O      | GVDD         | _    |

| MECC7                             | L2                 | I/O      | GVDD         | _    |

| MODT0                             | N5                 | 0        | GVDD         | 6    |

| MODT1                             | U6                 | 0        | GVDD         | 6    |

| MODT2                             | M6                 | 0        | GVDD         | 6    |

| MODT3                             | P6                 | 0        | GVDD         | 6    |

| MRAS_B                            | AA3                | 0        | GVDD         | _    |

| MVREF1                            | K4                 | I        | GVDD         | 11   |

| MVREF2                            | W4                 | I        | GVDD         | 11   |

| MWE_B                             | Y2                 | 0        | GVDD         | _    |

|                                   | DUART Interface    | I        |              |      |

| UART_SIN1/<br>MSRCID2/LSRCID2     | L28                | I/O      | OVDD         | _    |

| UART_SOUT1/<br>MSRCID0/LSRCID0    | L27                | 0        | OVDD         |      |

| UART_CTS_B[1]/<br>MSRCID4/LSRCID4 | K26                | I/O      | OVDD         | _    |

| UART_RTS_B1                       | N27                | 0        | OVDD         | _    |

| UART_SIN2/<br>MSRCID3/LSRCID3     | K27                | I/O      | OVDD         | _    |

| UART_SOUT2/<br>MSRCID1/LSRCID1    | K28                | 0        | OVDD         | _    |

| UART_CTS_B[2]/<br>MDVAL/LDVAL     | K29                | I/O      | OVDD         |      |

#### Table 72. TePBGA II Pinout Listing (continued)

These capacitors should have a value of 0.01 or 0.1  $\mu$ F. Only ceramic SMT (surface mount technology) capacitors should be used to minimize lead inductance, preferably 0402 or 0603 sizes.

In addition, it is recommended that there be several bulk storage capacitors distributed around the PCB, feeding the VDD, OVDD, GVDD, and LVDD planes, to enable quick recharging of the smaller chip capacitors. These bulk capacitors should have a low ESR (equivalent series resistance) rating to ensure the quick response time necessary. They should also be connected to the power and ground planes through two vias to minimize inductance. Suggested bulk capacitors— $100-330 \mu F$  (AVX TPS tantalum or Sanyo OSCON).

## 25.3 Connection Recommendations

To ensure reliable operation, it is highly recommended that unused inputs be connected to an appropriate signal level. Unused active low inputs should be tied to OVDD, GVDD, or LVDD as required. Unused active high inputs should be connected to GND. All NC (no-connect) signals must remain unconnected.

Power and ground connections must be made to all external VDD, GVDD, LVDD, OVDD, and GND pins of the device.

## 25.4 Output Buffer DC Impedance

The device drivers are characterized over process, voltage, and temperature. For all buses, the driver is a push-pull single-ended driver type (open drain for  $I^2C$ ).

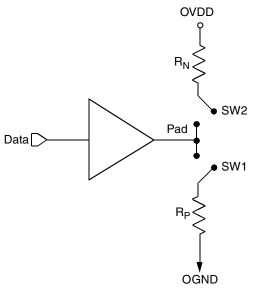

To measure  $Z_0$  for the single-ended drivers, an external resistor is connected from the chip pad to OVDD or GND. Then, the value of each resistor is varied until the pad voltage is  $OV_{DD}/2$  (see Figure 66). The output impedance is the average of two components, the resistances of the pull-up and pull-down devices. When data is held high, SW1 is closed (SW2 is open) and  $R_P$  is trimmed until the voltage at the pad equals  $OV_{DD}/2$ .  $R_P$  then becomes the resistance of the pull-up devices.  $R_P$  and  $R_N$  are designed to be close to each other in value. Then,  $Z_0 = (R_P + R_N)/2$ .

Figure 66. Driver Impedance Measurement

| Table 87. | Document | Revision | History | (continued) |

|-----------|----------|----------|---------|-------------|

|-----------|----------|----------|---------|-------------|

| Revision | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2        | 10/2009 | <ul> <li>In Table 3, "Recommended Operating Conditions," added "Operating temperature range" values.</li> <li>In Table 5, "Power Dissipation <sup>1</sup>," corrected maximal application for 800/400 MHz to 4.3 W.</li> <li>In Table 5, "Power Dissipation <sup>1</sup>," added a column for "Typical Application at T<sub>j</sub> = 65°C (W)".</li> <li>In Table 5, "Power Dissipation <sup>1</sup>," added a column for "Sleep Power at T<sub>j</sub> = 65°C (W)".</li> <li>In Table 11, removed overbar from CFG_CLKIN_DIV.</li> <li>In Table 17, "Current Draw Characteristics for MV<sub>REF</sub>," updated I<sub>MVREF</sub> maximum value for both DDR1 and DDR2 to 600 and 400 µA, respectively. Also, updated Note 1 and added Note 2.</li> <li>In Table 20, "DDR1 and DDR2 SDRAM Input AC Timing Specifications," column headings renamed to "Min" and "Max". Footnote 2 updated to state "T is the MCK clock period".</li> <li>In Table 20, "DDR1 and DDR2 SDRAM Input AC Timing Specifications," and Table 21, "DDR1 and DDR2 SDRAM Output AC Timing Specifications," and Table 21, "DDR1 and DDR2 SDRAM Output AC Timing Specifications," and Table 21, "DDR1 and DDR2 SDRAM Output AC Timing Specifications," updated t<sub>RMTDX</sub>I to 2.0 ns.</li> <li>In Table 60, Gen 1i/1.5G Transmitter AC Specifications," and Table 62, Gen 2i/3G Transmitter AC Specifications," corrected titles from "Transmitter" to "Receiver".</li> <li>In Table 72, "TePBGA II Pinout Listing," removed pin THERM0; it is now Reserved. Also added 1.05 V to VDD pin.</li> <li>In Table 74, "Operating Frequencies for TePBGA II," corrected "DDR2 memory bus frequency (MCK)" range to 125–200.</li> <li>In Table 79, "e300 Core PLL Configuration," added 3.5:1 and 4:1 core_clk: csb_clk ratio options.</li> <li>In Table 79, "e300 Core PLL Configuration," added 3.5:1 and 4:1 core_clk: to t<sub>NIKHOX</sub> and t<sub>NEKHOV</sub> respectively.</li> </ul> |

| 1        | 02/2009 | <ul> <li>In Table 3, "Recommended Operating Conditions," added two new rows for 800 MHz, and created two rows for SerDes. In addition, changed 666 to 667 MHz.</li> <li>In Table 5, "Power Dissipation <sup>1</sup>," added Notes 4 and 5. In addition, changed 666 to 667 MHz.</li> <li>In Table 13, "DDR2 SDRAM DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 1.8 V," Table 21, "DDR1 and DDR2 SDRAM Output AC Timing Specifications," and Table 72, "TePBGA II Pinout Listing," added footnote to references to MVREF, MDQ, and MDQS, referencing AN3665, <i>MPC837xE Design Checklist</i>.</li> <li>In Table 21, updated t<sub>DDKHCX</sub> minimum value for 333 MHz to 2.40.</li> <li>In Table 72, "TePBGA II Pinout Listing," added footnote to USBDR_STP_SUSPEND and modified footnote 10 and added footnote 14.</li> <li>In Table 74, "Operating Frequencies for TePBGA II," changed 667 to 800 MHz for <i>core_clk</i>.</li> <li>In Table 80, "Example Clock Frequency Combinations," added 800 MHz cells for e300 core.</li> <li>Updated part numbering information in AF column in Table 84, "Part Numbering Nomenclature." In addition, modified extended temperature information in notes 1 and 4.</li> <li>In Table 85, "Available Parts (Core/DDR Data Rate)," added new row for 800/400 MHz.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0        | 12/2008 | Initial public release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |