# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                              |

|---------------------------------|-----------------------------------------------------------------------|

| Core Processor                  | PowerPC e300c4s                                                       |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                        |

| Speed                           | 800MHz                                                                |

| Co-Processors/DSP               | -                                                                     |

| RAM Controllers                 | DDR, DDR2                                                             |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | -                                                                     |

| Ethernet                        | 10/100/1000Mbps (2)                                                   |

| SATA                            | SATA 3Gbps (2)                                                        |

| USB                             | USB 2.0 + PHY (1)                                                     |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                      |

| Operating Temperature           | 0°C ~ 125°C (TA)                                                      |

| Security Features               | -                                                                     |

| Package / Case                  | 689-BBGA Exposed Pad                                                  |

| Supplier Device Package         | 689-TEPBGA II (31x31)                                                 |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8377vranga |

|                                 |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Core Frequency<br>(MHz) |     | Sleep Power<br>at T <sub>j</sub> = 65°C (W) <sup>2</sup> | Typical Application at $T_j = 65^{\circ}C$ (W) <sup>2</sup> | Typical Application at $T_j = 125^{\circ}C$ (W) <sup>3</sup> | Max Application at $T_j = 125$ °C (W) <sup>4</sup> |

|-------------------------|-----|----------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------|

| 600                     | 400 | 1.45                                                     | 2.1                                                         | 3.4                                                          | 4.1                                                |

| 000                     | 300 | 1.45                                                     | 2.0                                                         | 3.3                                                          | 4.0                                                |

| 667                     | 333 | 1.45                                                     | 2.1                                                         | 3.3                                                          | 4.1                                                |

| 667                     | 266 | 1.45                                                     | 2.0                                                         | 3.3                                                          | 3.9                                                |

| 800                     | 400 | 1.45                                                     | 2.5                                                         | 3.8                                                          | 4.3                                                |

### Table 5. Power Dissipation <sup>1</sup> (continued)

#### Notes:

1. The values do not include I/O supply power (OV<sub>DD</sub>,  $LV_{DD}$ ,  $GV_{DD}$ ) or  $AV_{DD}$ . For I/O power values, see Table 6.

2. Typical power is based on a voltage of  $V_{DD}$  = 1.0 V for core frequencies  $\leq$  667 MHz or  $V_{DD}$  = 1.05 V for core frequencies of 800 MHz, and running a Dhrystone benchmark application.

3. Typical power is based on a voltage of  $V_{DD}$  = 1.0 V for core frequencies  $\leq$  667 MHz or  $V_{DD}$  = 1.05 V for core frequencies of 800 MHz, and running a Dhrystone benchmark application.

4. Maximum power is based on a voltage of  $V_{DD}$  = 1.0 V for core frequencies  $\leq$  667 MHz or  $V_{DD}$  = 1.05 V for core frequencies of 800 MHz, worst case process, and running an artificial smoke test.

This table shows the estimated typical I/O power dissipation for the device.

| Interface                | Parameter                       | GV <sub>DD</sub><br>(1.8 V) | GV <sub>DD</sub> /LBV <sub>DD</sub><br>(2.5 V) | OV <sub>DD</sub><br>(3.3 V) | LV <sub>DD</sub><br>(3.3 V) | LV <sub>DD</sub><br>(2.5 V) | L[1,2]_ <i>n</i> V <sub>DD</sub><br>(1.0 V) | Unit | Comments |

|--------------------------|---------------------------------|-----------------------------|------------------------------------------------|-----------------------------|-----------------------------|-----------------------------|---------------------------------------------|------|----------|

|                          | 200 MHz data<br>rate, 32-bit    | 0.28                        | 0.35                                           | —                           | —                           | —                           | _                                           | W    | _        |

|                          | 200 MHz data<br>rate, 64-bit    | 0.41                        | 0.49                                           | _                           | _                           | _                           | _                                           | W    |          |

|                          | 266 MHz data<br>rate, 32-bit    | 0.31                        | 0.4                                            | —                           | _                           | —                           |                                             | W    |          |

|                          | 266 MHz data<br>rate, 64-bit    | 0.46                        | 0.56                                           | —                           | _                           | —                           |                                             | W    |          |

| DDR I/O<br>65%           | 300 MHz data<br>rate, 32-bit    | 0.33                        | 0.43                                           | —                           | —                           | —                           | _                                           | W    |          |

| utilization<br>2 pair of | 300 MHz data<br>rate, 64-bit    | 0.48                        | 0.6                                            | _                           | _                           | _                           | _                                           | W    |          |

| clocks                   | 333 MHz data<br>rate, 32-bit    | 0.35                        | 0.45                                           | —                           | —                           | —                           | _                                           | W    |          |

|                          | 333 MHz data<br>rate, 64-bit    | 0.51                        | 0.64                                           | _                           | _                           | _                           | _                                           | W    |          |

|                          | 400 MHz<br>data rate,<br>32-bit | 0.38                        |                                                | —                           | _                           | —                           |                                             | W    |          |

|                          | 400 MHz<br>data rate,<br>64-bit | 0.56                        |                                                | _                           | _                           | _                           |                                             | W    |          |

Table 6. Typical I/O Power Dissipation

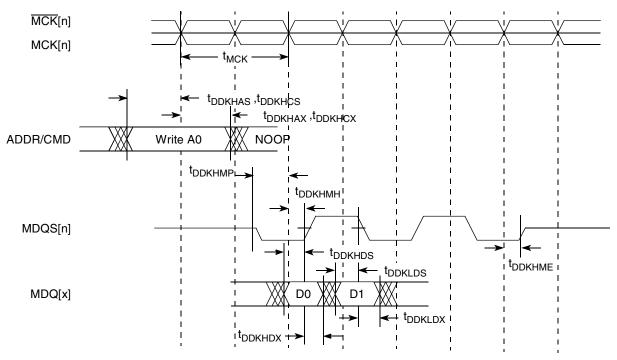

This figure shows the DDR1 and DDR2 SDRAM output timing diagram.

Figure 5. DDR1 and DDR2 SDRAM Output Timing Diagram

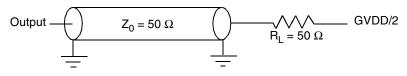

This figure provides AC test load for the DDR bus.

Figure 6. DDR AC Test Load

# 7 DUART

This section describes the DC and AC electrical specifications for the DUART interface of the chip.

# 7.1 DUART DC Electrical Characteristics

This table provides the DC electrical characteristics for the DUART interface of the device.

Table 22. DUART DC Electrical Characteristics

| Parameter                                               | Symbol          | Min                    | Мах                    | Unit |

|---------------------------------------------------------|-----------------|------------------------|------------------------|------|

| High-level input voltage                                | V <sub>IH</sub> | 2                      | OV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage OV <sub>DD</sub>                | V <sub>IL</sub> | -0.3                   | 0.8                    | V    |

| High-level output voltage,<br>I <sub>OH</sub> = −100 μA | V <sub>OH</sub> | OV <sub>DD</sub> – 0.2 |                        | V    |

# 8.2.3 RMII AC Timing Specifications

This section describes the RMII transmit and receive AC timing specifications.

# 8.2.3.1 RMII Transmit AC Timing Specifications

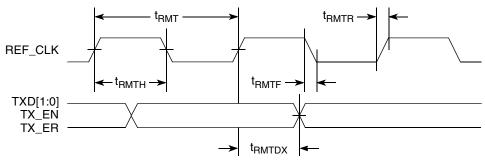

This table shows the RMII transmit AC timing specifications.

### Table 29. RMII Transmit AC Timing Specifications

At recommended operating conditions with LV<sub>DD</sub> of 3.3 V  $\pm$  5%.

| Parameter                                  | Symbol <sup>1</sup> | Min  | Typical | Мах  | Unit |

|--------------------------------------------|---------------------|------|---------|------|------|

| REF_CLK clock period                       | t <sub>RMT</sub>    | 15.0 | 20.0    | 25.0 | ns   |

| REF_CLK duty cycle                         | t <sub>RMTH</sub>   | 35   | 50      | 65   | %    |

| REF_CLK peak-to-peak jitter                | t <sub>RMTJ</sub>   | —    | —       | 250  | ps   |

| Rise time REF_CLK (20%–80%)                | t <sub>RMTR</sub>   | 1.0  | —       | 2.0  | ns   |

| Fall time REF_CLK (80%-20%)                | t <sub>RMTF</sub>   | 1.0  | —       | 2.0  | ns   |

| REF_CLK to RMII data TXD[1:0], TX_EN delay | t <sub>RMTDX</sub>  | 2.0  |         | 10.0 | ns   |

#### Note:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MTKHDX</sub> symbolizes MII transmit timing (MT) for the time t<sub>MTX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general, the clock reference symbol representation is based on two to three letters representing the clock of a particular functional. For example, the subscript of t<sub>MTX</sub> represents the MII(M) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

This figure shows the RMII transmit AC timing diagram.

Figure 12. RMII Transmit AC Timing Diagram

| Parameter                                            | Symbol <sup>1</sup> | Min | Max | Unit | Note |

|------------------------------------------------------|---------------------|-----|-----|------|------|

| Local bus clock to output high impedance for LAD/LDP | t <sub>lbkhoz</sub> | —   | 3.8 | ns   | 3, 8 |

| Output hold from local bus clock for LAD/LDP         | t <sub>LBKHOX</sub> | 1   | —   | ns   | 3    |

### Table 39. Local Bus General Timing Parameters—PLL Enable Mode (continued)

Notes:

- The symbols used for timing specifications herein follow the pattern of t<sub>(First two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(First two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one(1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the output (O) going invalid (X) or output hold time.

- 2. All timings are in reference to rising edge of LSYNC\_IN at LBV<sub>DD</sub>/2 and the 0.4 × LBV<sub>DD</sub> of the signal in question.

- 3. All signals are measured from LBV<sub>DD</sub>/2 of the rising/falling edge of LSYNC\_IN to  $0.5 \times LBV_{DD}$  of the signal in question. 4. Input timings are measured at the pin.

- 5. t<sub>LBOTOT1</sub> should be used when LBCR[AHD] is set and the load on LALE output pin is at least 10pF less than the load on LAD output pins.

- 6. t<sub>LBOTOT2</sub> should be used when LBCR[AHD] is not set and the load on LALE output pin is at least 10pF less than the load on LAD output pins.

- 7. t<sub>LBOTOT3</sub> should be used when LBCR[AHD] is not set and the load on LALE output pin equals to the load on LAD output pins.

- 8. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

This table describes the general timing parameters of the local bus interface of the device when in PLL bypass mode.

| Parameter                                                   | Symbol <sup>1</sup>  | Min | Max | Unit | Note |

|-------------------------------------------------------------|----------------------|-----|-----|------|------|

| Local bus cycle time                                        | t <sub>LBK</sub>     | 15  | —   | ns   | 2    |

| Input setup to local bus clock                              | t <sub>LBIVKH</sub>  | 7.0 | —   | ns   | 3, 4 |

| Input hold from local bus clock                             | t <sub>LBIXKH</sub>  | 1.0 | —   | ns   | 3, 4 |

| LALE output fall to LAD output transition (LATCH hold time) | t <sub>LBOTOT1</sub> | 1.5 | —   | ns   | 5    |

| LALE output fall to LAD output transition (LATCH hold time) | t <sub>LBOTOT2</sub> | 3.0 | —   | ns   | 6    |

| LALE output fall to LAD output transition (LATCH hold time) | t <sub>LBOTOT3</sub> | 2.5 | —   | ns   | 7    |

| Local bus clock to LALE rise                                | t <sub>LBKHLR</sub>  | —   | 4.5 | ns   | _    |

| Local bus clock to output valid                             | t <sub>LBKHOV</sub>  | —   | 3.0 | ns   | 3    |

| Local bus clock to output high impedance for LAD/LDP        | t <sub>lbkhoz</sub>  | —   | 4.0 | ns   | 3, 8 |

### Table 40. Local Bus General Timing Parameters—PLL Bypass Mode

#### Notes:

The symbols used for timing specifications herein follow the pattern of t<sub>(First two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(First two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one(1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the output (O) going invalid (X) or output hold time.

- All timings are in reference to falling edge of LCLK0 (for all outputs and for LGTA and LUPWAIT inputs) or rising edge of LCLK0 (for all other inputs).

- 3. All signals are measured from LBV<sub>DD</sub>/2 of the rising/falling edge of LCLK0 to  $0.4 \times LBV_{DD}$  of the signal in question for 3.3-V signaling levels.

- 4. Input timings are measured at the pin.

- 5. t<sub>LBOTOT1</sub> should be used when LBCR[AHD] is set and the load on LALE output pin is at least 10pF less than the load on LAD output pins.

- t<sub>LBOTOT2</sub> should be used when LBCR[AHD] is not set and the load on LALE output pin is at least 10pF less than the load on LAD output pins.

- 7. t<sub>LBOTOT3</sub> should be used when LBCR[AHD] is not set and the load on LALE output pin equals to the load on LAD output pins.

- 8. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

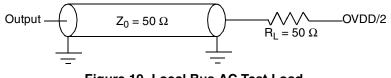

This figure provides the AC test load for the local bus.

Figure 19. Local Bus AC Test Load

# 11.2.2.2 Full-Speed Read Meeting Hold (Minimum Delay)

There is no minimum delay constraint due to the full clock cycle between the driving and sampling of data.

### $t_{CLK\_DELAY} + t_{OH} + t_{DATA\_DELAY} > t_{SFSIXKH}$

Eqn. 9

This means that Data + Clock delay must be greater than -2 ns. This is always fulfilled.

# 11.3 eSDHC AC Timing Specifications (High-Speed Mode)

This table provides the eSDHC AC timing specifications for high-speed mode as defined in Figure 30 and Figure 31.

### Table 43. eSDHC AC Timing Specifications for High-Speed Mode

At recommended operating conditions  $\text{OV}_{\text{DD}}$  = 3.3 V  $\pm$  165 mV.

| Parameter                                           | Symbol <sup>1</sup>                         | Min | Max | Unit | Note |

|-----------------------------------------------------|---------------------------------------------|-----|-----|------|------|

| SD_CLK clock frequency—high speed mode              | f <sub>SHSCK</sub>                          | 0   | 50  | MHz  | —    |

| SD_CLK clock cycle                                  | t <sub>SHSCK</sub>                          | 20  | —   | ns   | _    |

| SD_CLK clock frequency—identification mode          | f <sub>SIDCK</sub>                          | 0   | 400 | KHz  | _    |

| SD_CLK clock low time                               | t <sub>SHSCKL</sub>                         | 7   | _   | ns   | 2    |

| SD_CLK clock high time                              | t <sub>SHSCKH</sub>                         | 7   | _   | ns   | 2    |

| SD_CLK clock rise and fall times                    | t <sub>SHSCKR∕</sub><br>t <sub>SHSCKF</sub> | _   | 3   | ns   | 2    |

| Input setup times: SD_CMD, SD_DATx, SD_CD to SD_CLK | t <sub>SHSIVKH</sub>                        | 5   | —   | ns   | 2    |

| Input hold times: SD_CMD, SD_DATx, SD_CD to SD_CLK  | t <sub>SHSIXKH</sub>                        | 0   | —   | ns   | 2    |

| Output delay time: SD_CLK to SD_CMD, SD_DATx valid  | t <sub>SHSKHOV</sub>                        | _   | 4   | ns   | 2    |

| Output Hold time: SD_CLK to SD_CMD, SD_DATx invalid | t <sub>SHSKHOX</sub>                        | 0   | —   | ns   | 2    |

| SD_CLK delay within device                          | t <sub>INT_CLK_DLY</sub>                    | 1.5 | _   | ns   | 4    |

| SD Card Input Setup                                 | t <sub>ISU</sub>                            | 6   | _   | ns   | 3    |

| SD Card Input Hold                                  | t <sub>IH</sub>                             | 2   | _   | ns   | 3    |

| SD Card Output Valid                                | t <sub>ODLY</sub>                           | _   | 14  | ns   | 3    |

| SD Card Output Hold                                 | t <sub>OH</sub>                             | 2.5 |     | ns   | 3    |

Notes:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first three letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(first three letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>SFSIXKH</sub> symbolizes eSDHC full mode speed device timing (SFS) input (I) to go invalid (X) with respect to the clock reference (K) going to high (H). Also t<sub>SFSKHOV</sub> symbolizes eSDHC full speed timing (SFS) for the clock reference (K) to go high (H), with respect to the output (O) going valid (V) or data output valid time. Note that, in general, the clock reference symbol representation is based on five letters representing the clock of a particular functional. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

2. Measured at capacitive load of 40 pF.

3. For reference only, according to the SD card specifications.

4. Average, for reference only.

| Parameter                                                                  | Symbol <sup>2</sup>                        | Min    | Мах     | Unit | Note |

|----------------------------------------------------------------------------|--------------------------------------------|--------|---------|------|------|

| JTAG external clock to output high impedance:<br>Boundary-scan data<br>TDO | t <sub>JTKLDZ</sub><br>t <sub>JTKLOZ</sub> | 2<br>2 | 19<br>9 | ns   | 5    |

Table 45. JTAG AC Timing Specifications (Independent of CLKIN) <sup>1</sup> (continued)

Notes:

- 1. All outputs are measured from the midpoint voltage of the falling/rising edge of  $t_{TCLK}$  to the midpoint of the signal in question. The output timings are measured at the pins. All output timings assume a purely resistive 50  $\Omega$  load (see Figure 17). Time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

- 2. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>JTDVKH</sub> symbolizes JTAG device timing (JT) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>JTDXKH</sub> symbolizes JTAG timing (JT) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

- 3. TRST is an asynchronous level sensitive signal. The setup time is for test purposes only.

- 4. Non-JTAG signal input timing with respect to t<sub>TCLK</sub>.

- 5. Non-JTAG signal output timing with respect to t<sub>TCLK</sub>.

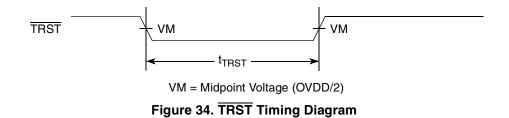

This figure provides the AC test load for TDO and the boundary-scan outputs of the device.

Figure 32. AC Test Load for the JTAG Interface

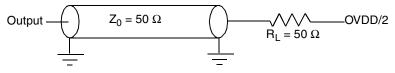

This figure provides the JTAG clock input timing diagram.

VM = Midpoint Voltage (OVDD/2)

Figure 33. JTAG Clock Input Timing Diagram

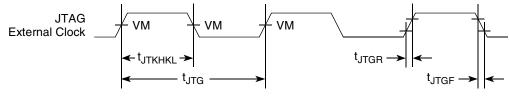

This figure provides the  $\overline{\text{TRST}}$  timing diagram.

| Parameter                                                                              | Comments                                                                                                                                                                                                                                                                                                                                                                       | Symbol                                       | Min   | Typical | Max | Units | Note    |

|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-------|---------|-----|-------|---------|

| Minimum receiver eye<br>width                                                          | The maximum interconnect<br>media and transmitter jitter that<br>can be tolerated by the receiver<br>can be derived as<br>$T_{RX-MAX-JITTER} = 1 -$<br>$U_{PEEWRX} = 0.6$ UI.                                                                                                                                                                                                  | T <sub>RX-EYE</sub>                          | 0.4   | _       | _   | UI    | 2, 3    |

| Maximum time between<br>the jitter median and<br>maximum deviation from<br>the median. | Jitter is defined as the<br>measurement variation of the<br>crossing points ( $V_{PEDPPRX} = 0$<br>V) in relation to a recovered Tx<br>UI. A recovered Tx UI is<br>calculated over 3500<br>consecutive unit intervals of<br>sample data. Jitter is measured<br>using all edges of the 250<br>consecutive UI in the center of<br>the 3500 UI used for calculating<br>the Tx UI. | T <sub>RX-EYE-MEDIAN-to</sub><br>-MAX-JITTER | _     |         | 0.3 | UI    | 2, 3, 7 |

| AC peak common mode<br>input voltage                                                   | $V_{PEACPCMRX} =  V_{RXD+} - V_{RXD} /2 - V_{RX-CM-DC} \\V_{RX-CM-DC} = DC_{(avg)} \text{ of }  V_{RX-D+} - V_{RX-D} /2$                                                                                                                                                                                                                                                       | V <sub>RX-CM-ACp</sub>                       | _     | _       | 150 | mV    | 2       |

| Differential return loss                                                               | Measured over 50 MHz to 1.25<br>GHz with the D+ and D- lines<br>biased at +300 mV and -300<br>mV, respectively.                                                                                                                                                                                                                                                                | RL <sub>RX-DIFF</sub>                        | 10    | —       | _   | dB    | 4       |

| Common mode return<br>loss                                                             | Measured over 50 MHz to 1.25<br>GHz with the D+ and D- lines<br>biased at 0 V.                                                                                                                                                                                                                                                                                                 | RL <sub>RX-CM</sub>                          | 6     | _       | _   | dB    | 4       |

| DC differential input<br>impedance                                                     | RX DC differential mode impedance.                                                                                                                                                                                                                                                                                                                                             | Z <sub>RX-DIFF-DC</sub>                      | 80    | 100     | 120 | Ω     | 5       |

| DC Input Impedance                                                                     | Required RX D+ as well as D-<br>DC impedance ( $50 \pm 20\%$<br>tolerance).                                                                                                                                                                                                                                                                                                    | Z <sub>RX-DC</sub>                           | 40    | 50      | 60  | Ω     | 2, 5    |

| Powered down DC input<br>impedance                                                     | Required RX D+ as well as D–<br>DC impedance when the<br>receiver terminations do not<br>have power.                                                                                                                                                                                                                                                                           | Z <sub>RX-HIGH-IMP-DC</sub>                  | 200 k | —       | _   | Ω     | 6       |

| Electrical idle detect<br>threshold                                                    | $V_{PEEIDT} = 2 \times IV_{RX-D+} - V_{RX-D-}I$<br>Measured at the package pins<br>of the receiver                                                                                                                                                                                                                                                                             | V <sub>RX-IDLE</sub> -DET-DIFF<br>p-p        | 65    | —       | 175 | mV    | —       |

| Table 54. | SATA | Reference | <b>Clock Inp</b> | ut Requirements | (continued) |

|-----------|------|-----------|------------------|-----------------|-------------|

|-----------|------|-----------|------------------|-----------------|-------------|

| Parameter                                                                           | Condition                                 | Symbol              | Min | Typical | Max | Unit | Note |

|-------------------------------------------------------------------------------------|-------------------------------------------|---------------------|-----|---------|-----|------|------|

| SD_REF_CLK/ SD_REF_CLK<br>cycle to cycle Clock jitter (period<br>jitter)            | Cycle-to-cycle at<br>ref clock input      | <sup>t</sup> CLK_CJ | _   | _       | 100 | ps   |      |

| SD_REF_CLK/ SD_REF_CLK total<br>reference clock jitter, phase jitter<br>(peak-peak) | Peak-to-peak jitter<br>at ref clock input | t <sub>CLK_PJ</sub> | -50 | _       | +50 | ps   | 2, 3 |

Notes:

1. Only 100/125/150 MHz have been tested, other in between values will not work correctly with the rest of the system.

2. In a frequency band from 150 kHz to 15 MHz at BER of  $10^{-12}$ .

3. Total peak to peak Deterministic Jitter "D<sub>I</sub>" should be less than or equal to 50 ps.

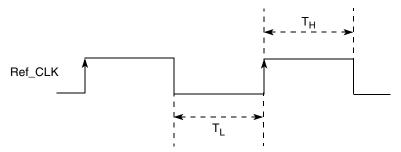

This figure shows the SATA reference clock timing waveform.

Figure 45. SATA Reference Clock Timing Waveform

# 16.2 Transmitter (Tx) Output Characteristics

This section discusses the Gen1i/1.5G and Gen2i/3G transmitter output characteristics for the SATA interface.

# 16.2.1 Gen1i/1.5G Transmitter Specifications

This table provides the DC differential transmitter output DC characteristics for the SATA interface at Gen1i or 1.5 Gbits/s transmission.

| Parameter                      | Symbol                     | Min | Typical | Мах | Units             | Note |

|--------------------------------|----------------------------|-----|---------|-----|-------------------|------|

| Tx differential output voltage | V <sub>SATA_TXDIFF</sub>   | 400 | 500     | 600 | mV <sub>p-p</sub> | 1    |

| Tx differential pair impedance | Z <sub>SATA_TXDIFFIM</sub> | 85  | 100     | 115 | Ω                 | _    |

Note:

1. Terminated by 50  $\Omega$  load.

| Parameter                                 | Symbol                      | Min | Typical | Мах  | Units             | Note |

|-------------------------------------------|-----------------------------|-----|---------|------|-------------------|------|

| Deterministic jitter, data-data<br>250 UI | U <sub>SATA_TXDJ250UI</sub> | _   | _       | 0.35 | UI <sub>p-p</sub> | 1    |

### Table 60. Gen 1i/1.5G Receiver AC Specifications (continued)

Note:

1. Measured at Tx output pins peak to peak phase variation, random data pattern.

# 16.3.2 Gen2i/3G Receiver (Rx) Specifications

This table provides the Gen2i or 3 Gbits/s differential receiver input DC characteristics for the SATA interface.

Table 61. Gen2i/3G Receiver Input DC Specifications

| Parameter                       | Symbol                   | Min | Typical | Мах | Units | Note |

|---------------------------------|--------------------------|-----|---------|-----|-------|------|

| Differential input voltage      | V <sub>SATA_RXDIFF</sub> | 275 | 500     | 750 | mVp-p | 1    |

| Differential RX input impedance | Z <sub>SATA_RXSEIM</sub> | 85  | 100     | 115 | Ω     | —    |

#### Note:

1. Voltage relative to common of either signal comprising a differential pair.

This table provides the differential receiver output AC characteristics for the SATA interface at Gen2i or 3.0 Gbits/s transmission.

Table 62. Gen 2i/3G Receiver AC Specifications

| Parameter                                                          | Symbol                        | Min   | Typical | Max    | Units             | Note |

|--------------------------------------------------------------------|-------------------------------|-------|---------|--------|-------------------|------|

| Channel Speed                                                      | t <sub>CH_SPEED</sub>         | —     | 3.0     | —      | Gbps              | —    |

| Unit Interval                                                      | T <sub>UI</sub>               | 333.2 | 333.33  | 335.11 | ps                | —    |

| Total jitter<br>f <sub>C3dB</sub> = f <sub>BAUD</sub> /10          | U <sub>SATA_TXTJfB/10</sub>   | —     | —       | 0.46   | UI <sub>p-p</sub> | 1    |

| Total jitter<br>f <sub>C3dB</sub> = f <sub>BAUD</sub> /500         | U <sub>SATA_TXTJfB/500</sub>  | —     | _       | 0.60   | UI <sub>p-p</sub> | 1    |

| Total jitter<br>f <sub>C3dB</sub> = f <sub>BAUD</sub> /1667        | U <sub>SATA_TXTJfB/1667</sub> | —     | —       | 0.65   | UI <sub>p-p</sub> | 1    |

| Deterministic jitter<br>$f_{C3dB} = f_{BAUD}/10$                   | U <sub>SATA_TXDJfB/10</sub>   | _     | —       | 0.35   | UI <sub>p-p</sub> | 1    |

| Deterministic jitter<br>f <sub>C3dB</sub> = f <sub>BAUD</sub> /500 | U <sub>SATA_TXDJfB/500</sub>  | —     | -       | 0.42   | UI <sub>p-p</sub> | 1    |

| Deterministic jitter<br>$f_{C3dB} = f_{BAUD}/1667$                 | U <sub>SATA_TXDJfB/1667</sub> | —     | —       | 0.35   | UI <sub>p-p</sub> | 1    |

Note:

1. Measured at Tx output pins peak to peak phase variation, random data pattern.

## NOTE

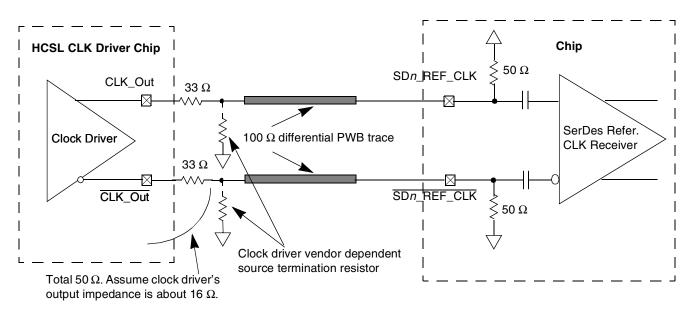

Figure 56 to Figure 59 below are for conceptual reference only. Due to the fact that clock driver chip's internal structure, output impedance, and termination requirements are different between various clock driver chip manufacturers, it is very possible that the clock circuit reference designs provided by the clock driver chip vendor are different from what is shown below. They might also vary from one vendor to the other. Therefore, Freescale Semiconductor can neither provide the optimal clock driver reference circuits, nor guarantee the correctness of the following clock driver connection reference circuits. The system designer is recommended to contact the selected clock driver chip vendor for the optimal reference circuits with the device SerDes reference clock receiver requirement provided in this document.

This figure shows the SerDes reference clock connection reference circuits for HCSL type clock driver. It assumes that the DC levels of the clock driver chip is compatible with device SerDes reference clock input's DC requirement.

Figure 56. DC-Coupled Differential Connection with HCSL Clock Driver (Reference Only)

This figure shows the SerDes reference clock connection reference circuits for LVDS type clock driver. Since LVDS clock driver's common-mode voltage is higher than the device SerDes reference clock input's allowed range (100 to 400 mV), AC-coupled connection scheme must be used. It assumes the LVDS

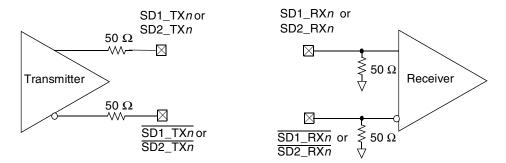

# 21.3 SerDes Transmitter and Receiver Reference Circuits

This figure shows the reference circuits for SerDes data lane's transmitter and receiver.

Figure 62. SerDes Transmitter and Receiver Reference Circuits

The DC and AC specification of SerDes data lanes are defined in each interface protocol section below in this document based on the application usage:

- Section 8, "Ethernet: Enhanced Three-Speed Ethernet (eTSEC)"

- Section 15, "PCI Express"

- Section 16, "Serial ATA (SATA)"

Note that an external AC coupling capacitor is required for the above three serial transmission protocols with the capacitor value defined in specification of each protocol section.

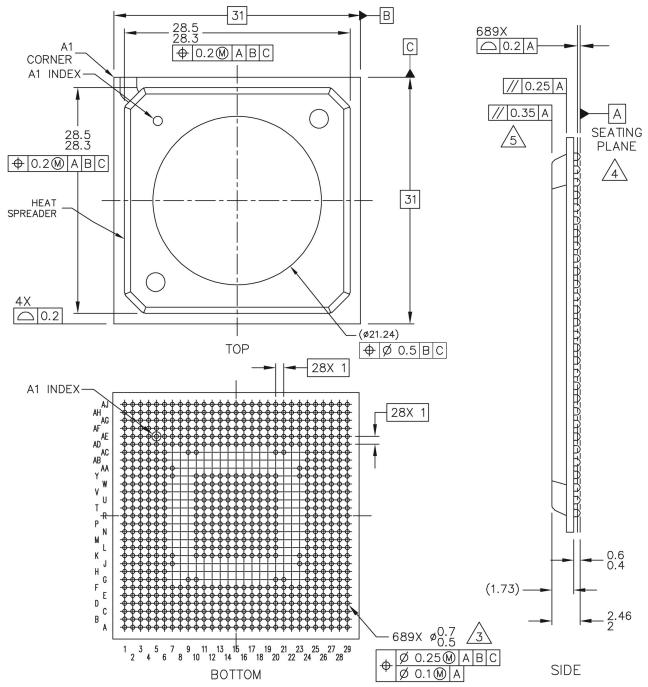

# 22 Package and Pin Listings

This section details package parameters, pin assignments, and dimensions.

# 22.1 Package Parameters for the MPC8377E TePBGA II

The package parameters are provided in the following list. The package type is  $31 \text{ mm} \times 31 \text{ mm}$ , 689 plastic ball grid array (TePBGA II).

| Package outline         | $31 \text{ mm} \times 31 \text{ mm}$ |

|-------------------------|--------------------------------------|

| Interconnects           | 689                                  |

| Pitch                   | 1.00 mm                              |

| Module height (typical) | 2.0 mm to 2.46 mm (maximum)          |

| Solder Balls            | 3.5% Ag, 96.5% Sn                    |

| Ball diameter (typical) | 0.60 mm                              |

This figure shows the mechanical dimensions and bottom surface nomenclature of the TEPBGA II package.

Figure 63. Mechanical Dimensions and Bottom Surface Nomenclature of the TEPBGA II

### Note:

- <sup>1</sup> All dimensions are in millimeters.

- <sup>2</sup> Dimensioning and tolerancing per ASME Y14. 5M-1994.

- <sup>3</sup> Maximum solder ball diameter measured parallel to Datum A.

- <sup>4</sup> Datum A, the seating plane, is determined by the spherical crowns of the solder balls.

| Signal | Package Pin Number | Pin Type | Power Supply | Note |

|--------|--------------------|----------|--------------|------|

| MDQ35  | AE1                | I/O      | GVDD         | 11   |

| MDQ36  | V6                 | I/O      | GVDD         | 11   |

| MDQ37  | Y5                 | I/O      | GVDD         | 11   |

| MDQ38  | AA4                | I/O      | GVDD         | 11   |

| MDQ39  | AB6                | I/O      | GVDD         | 11   |

| MDQ40  | AD3                | I/O      | GVDD         | 11   |

| MDQ41  | AC4                | I/O      | GVDD         | 11   |

| MDQ42  | AD4                | I/O      | GVDD         | 11   |

| MDQ43  | AF1                | I/O      | GVDD         | 11   |

| MDQ44  | AE4                | I/O      | GVDD         | 11   |

| MDQ45  | AC5                | I/O      | GVDD         | 11   |

| MDQ46  | AE2                | I/O      | GVDD         | 11   |

| MDQ47  | AE3                | I/O      | GVDD         | 11   |

| MDQ48  | AG1                | I/O      | GVDD         | 11   |

| MDQ49  | AG2                | I/O      | GVDD         | 11   |

| MDQ50  | AG3                | I/O      | GVDD         | 11   |

| MDQ51  | AF5                | I/O      | GVDD         | 11   |

| MDQ52  | AE5                | I/O      | GVDD         | 11   |

| MDQ53  | AD7                | I/O      | GVDD         | 11   |

| MDQ54  | AH2                | I/O      | GVDD         | 11   |

| MDQ55  | AG4                | I/O      | GVDD         | 11   |

| MDQ56  | AH3                | I/O      | GVDD         | 11   |

| MDQ57  | AG5                | I/O      | GVDD         | 11   |

| MDQ58  | AF8                | I/O      | GVDD         | 11   |

| MDQ59  | AJ5                | I/O      | GVDD         | 11   |

| MDQ60  | AF6                | I/O      | GVDD         | 11   |

| MDQ61  | AF7                | I/O      | GVDD         | 11   |

| MDQ62  | AH6                | I/O      | GVDD         | 11   |

| MDQ63  | AH7                | I/O      | GVDD         | 11   |

| MDQS0  | C8                 | I/O      | GVDD         | 11   |

| MDQS1  | C4                 | I/O      | GVDD         | 11   |

| MDQS2  | E3                 | I/O      | GVDD         | 11   |

| MDQS3  | G2                 | I/O      | GVDD         | 11   |

| Signal                                | Package Pin Number | Pin Type | Power Supply | Note |

|---------------------------------------|--------------------|----------|--------------|------|

| LA25/LAD30                            | D29                | I/O      | LBVDD        | _    |

| LA26/LAD31                            | E20                | I/O      | LBVDD        | _    |

| LA27                                  | H26                | 0        | LBVDD        | _    |

| LA28                                  | C29                | 0        | LBVDD        | _    |

| LA29                                  | E28                | 0        | LBVDD        | _    |

| LA30                                  | B26                | 0        | LBVDD        | _    |

| LA31                                  | J25                | 0        | LBVDD        | _    |

| LA10/LALE                             | H29                | 0        | LBVDD        | _    |

| LBCTL                                 | A22                | 0        | LBVDD        | _    |

| LCLK0                                 | B22                | 0        | LBVDD        | _    |

| LCLK1                                 | C23                | 0        | LBVDD        | _    |

| LCLK2                                 | B23                | 0        | LBVDD        | _    |

| LCS_B0                                | D25                | 0        | LBVDD        | _    |

| LCS_B1                                | F19                | 0        | LBVDD        | _    |

| LCS_B2                                | C27                | 0        | LBVDD        | _    |

| LCS_B3                                | D24                | 0        | LBVDD        | _    |

| LCS_B4/LDP0                           | C24                | I/O      | LBVDD        | _    |

| LCS_B5/LDP1                           | B29                | I/O      | LBVDD        | _    |

| LA7/LCS_B6/LDP2                       | E29                | I/O      | LBVDD        | _    |

| LA8/LCS_B7/LDP3                       | F29                | I/O      | LBVDD        | _    |

| LFCLE/LGPL0                           | D21                | 0        | LBVDD        | _    |

| LFALE/LGPL1                           | A26                | 0        | LBVDD        | _    |

| LFRE_B/LGPL2/LOE_B                    | F22                | 0        | LBVDD        | _    |

| LFWP_B/LGPL3                          | C21                | 0        | LBVDD        | _    |

| LGPL4/LFRB_B/LGTA_B/<br>LUPWAIT/LPBSE | J29                | I/O      | LBVDD        | 16   |

| LA9/LGPL5                             | G29                | 0        | LBVDD        |      |

| LSYNC_IN                              | A21                | I        | LBVDD        | _    |

| LSYNC_OUT                             | D23                | 0        | LBVDD        | _    |

| LWE_B0/LFWE0/LBS_B0                   | E22                | 0        | LBVDD        | _    |

| LWE_B1/LFWE1/LBS_B1                   | B25                | 0        | LBVDD        | _    |

| LWE_B2/LFWE2/LBS_B2                   | E27                | 0        | LBVDD        | _    |

| LWE_B3/LFWE3/LBS_B3                   | F28                | 0        | LBVDD        | _    |

### Table 72. TePBGA II Pinout Listing (continued)

| Table 72. Te | PBGA II P | inout Listing | (continued) |

|--------------|-----------|---------------|-------------|

|--------------|-----------|---------------|-------------|

| Signal                                            | Package Pin Number         | Pin Type | Power Supply | Note |

|---------------------------------------------------|----------------------------|----------|--------------|------|

| GPIO1[10]/GTM1_TGATE4_B/<br>GTM2_TGATE3_B/DACK3_B | J27                        | I/O      | OVDD         |      |

| GPIO1[11]/GTM1_TOUT4_B/<br>GTM2_TOUT3_B/DDONE3_B  | P24                        | I/O      | OVDD         | —    |

|                                                   | USB/GPIO2 Interface        |          | •            |      |

| USBDR_CLK/GPIO2[23]                               | AJ11                       | I/O      | OVDD         | _    |

| USBDR_DIR_DPPULLUP/<br>GPIO2[9]                   | AG12                       | I/O      | OVDD         |      |

| USBDR_NXT/GPIO2[8]                                | AJ10                       | I/O      | OVDD         | _    |

| USBDR_PCTL0/GPIO2[11]/<br>SD_DAT2                 | AF10                       | I/O      | OVDD         |      |

| USBDR_PCTL1/GPIO2[22]/<br>SD_DAT3                 | AE9                        | I/O      | OVDD         |      |

| USBDR_PWRFAULT/<br>GPIO2[10]/SD_DAT1              | AG13                       | I/O      | OVDD         |      |

| USBDR_STP_SUSPEND                                 | AH12                       | 0        | OVDD         | 12   |

| USBDR_D0_ENABLEN/<br>GPIO2[0]                     | AG10                       | I/O      | OVDD         | _    |

| USBDR_D1_SER_TXD/<br>GPIO2[1]                     | AF13                       | I/O      | OVDD         |      |

| USBDR_D2_VMO_SE0/<br>GPIO2[2]                     | AG11                       | I/O      | OVDD         |      |

| USBDR_D3_SPEED/GPIO2[3]                           | AH11                       | I/O      | OVDD         | _    |

| USBDR_D4_DP/GPIO2[4]                              | AG9                        | I/O      | OVDD         | _    |

| USBDR_D5_DM/GPIO2[5]                              | AF9                        | I/O      | OVDD         |      |

| USBDR_D6_SER_RCV/<br>GPIO2[6]                     | AH13                       | I/O      | OVDD         | —    |

| USBDR_D7_DRVVBUS/<br>GPIO2[7]                     | AH10                       | I/O      | OVDD         | _    |

| ·                                                 | I <sup>2</sup> C Interface |          |              |      |

| IIC1_SCL                                          | C12                        | I/O      | OVDD         | 2    |

| IIC1_SDA                                          | B12                        | I/O      | OVDD         | 2    |

| IIC2_SCL                                          | A10                        | I/O      | OVDD         | 2    |

| IIC2_SDA                                          | A12                        | I/O      | OVDD         | 2    |

| ·                                                 | JTAG Interface             |          |              |      |

| ТСК                                               | B13                        | I        | OVDD         | _    |

| Signal                              | Package Pin Number                | Pin Type                                | Power Supply | Note |

|-------------------------------------|-----------------------------------|-----------------------------------------|--------------|------|

|                                     | Programmable Interrupt Controller | (PIC) Interface                         |              |      |

| MCP_OUT_B                           | AD14                              | 0                                       | OVDD         | 2    |

| IRQ_B0/MCP_IN_B/GPIO2[12]           | F9                                | I/O                                     | OVDD         | _    |

| IRQ_B1/GPIO2[13]                    | E9                                | I/O                                     | OVDD         | _    |

| IRQ_B2/GPIO2[14]                    | F10                               | I/O                                     | OVDD         | _    |

| IRQ_B3/GPIO2[15]                    | D9                                | I/O                                     | OVDD         | _    |

| IRQ_B4/GPIO2[16]/SD_WP              | C9                                | I/O                                     | OVDD         | _    |

| IRQ_B5/GPIO2[17]/<br>USBDR_PWRFAULT | AE10                              | I/O                                     | OVDD         | —    |

| IRQ_B6/GPIO2[18]                    | AD10                              | I/O                                     | OVDD         | _    |

| IRQ_B7/GPIO2[19]                    | AD9                               | I/O                                     | OVDD         | —    |

| ·                                   | PMC Interface                     | ·                                       |              |      |

| QUIESCE_B                           | D13                               | 0                                       | OVDD         |      |

|                                     | SerDes1 Interface                 | ·                                       |              |      |

| L1_SD_IMP_CAL_RX                    | AJ14                              | I                                       | L1_XPADVDD   | _    |

| L1_SD_IMP_CAL_TX                    | AG19                              | I                                       | L1_XPADVDD   | _    |

| L1_SD_REF_CLK                       | AJ17                              | I                                       | L1_XPADVDD   | _    |

| L1_SD_REF_CLK_B                     | AH17                              | I                                       | L1_XPADVDD   | _    |

| L1_SD_RXA_N                         | AJ15                              | I                                       | L1_XPADVDD   | —    |

| L1_SD_RXA_P                         | AH15                              | I                                       | L1_XPADVDD   | —    |

| L1_SD_RXE_N                         | AJ19                              | I                                       | L1_XPADVDD   | —    |

| L1_SD_RXE_P                         | AH19                              | I                                       | L1_XPADVDD   | —    |

| L1_SD_TXA_N                         | AF15                              | 0                                       | L1_XPADVDD   | —    |

| L1_SD_TXA_P                         | AE15                              | 0                                       | L1_XPADVDD   | —    |

| L1_SD_TXE_N                         | AF18                              | 0                                       | L1_XPADVDD   | —    |

| L1_SD_TXE_P                         | AE18                              | 0                                       | L1_XPADVDD   | —    |

| L1_SDAVDD_0                         | AJ18                              | SerDes PLL<br>Power<br>(1.0 or 1.05 V)  |              | _    |

| L1_SDAVSS_0                         | AG17                              | SerDes PLL<br>GND                       | —            | _    |

| L1_XCOREVDD                         | AH14, AJ16, AF17, AH20, AJ20      | SerDes Core<br>Power<br>(1.0 or 1.05 V) | —            | _    |

### Table 72. TePBGA II Pinout Listing (continued)

| Unit            | Default Frequency | Options                            |  |  |

|-----------------|-------------------|------------------------------------|--|--|

| PCI Express1, 2 | csb_clk/3         | Off, csb_clk, csb_clk/2, csb_clk/3 |  |  |

| SATA1, 2        | csb_clk/3         | Off, csb_clk                       |  |  |

### Table 73. Configurable Clock Units (continued)

<sup>1</sup> This only applies to  $I^2C1$  ( $I^2C2$  clock is not configurable).

This table provides the operating frequencies for the TePBGA II package under recommended operating conditions (see Table 3).

| Parameter <sup>1</sup>                            | Minimum Operating<br>Frequency (MHz) | Maximum Operating<br>Frequency (MHz) |  |  |

|---------------------------------------------------|--------------------------------------|--------------------------------------|--|--|

| e300 core frequency ( <i>core_clk</i> )           | 333                                  | 800                                  |  |  |

| Coherent system bus frequency (csb_clk)           | 133                                  | 400                                  |  |  |

| DDR2 memory bus frequency (MCK) <sup>1</sup>      | 250                                  | 400                                  |  |  |

| DDR1 memory bus frequency (MCK) <sup>2</sup>      | 167                                  | 333                                  |  |  |

| Local bus frequency (LCLKn) <sup>1</sup>          | —                                    | 133                                  |  |  |

| Local bus controller frequency ( <i>lbc_clk</i> ) | _                                    | 400                                  |  |  |

| PCI input frequency (CLKIN or PCI_CLK)            | 25                                   | 66                                   |  |  |

| eTSEC frequency                                   | 133                                  | 400                                  |  |  |

| Security encryption controller frequency          | _                                    | 200                                  |  |  |

| USB controller frequency                          | _                                    | 200                                  |  |  |

| eSDHC controller frequency                        | —                                    | 200                                  |  |  |

| PCI Express controller frequency                  | —                                    | 400                                  |  |  |

| SATA controller frequency                         | —                                    | 200                                  |  |  |

### Table 74. Operating Frequencies for TePBGA II

Notes:

1. The CLKIN frequency, RCWLR[SPMF], and RCWLR[COREPLL] settings must be chosen such that the resulting *csb\_clk*, MCK, LCLK[0:2], and *core\_clk* frequencies do not exceed their respective maximum or minimum operating frequencies. The value of SCCR[xCM] must be programmed such that the maximum internal operating frequency of the Security core, USB modules, SATA, and eSDHC will not exceed their respective value listed in this table.

2. The DDR data rate is  $2 \times$  the DDR memory bus frequency.

3. The local bus frequency is ½, ¼, or 1/8 of the *lbiu\_clk* frequency (depending on LCRR[CLKDIV]) which is in turn 1× or 2× the *csb\_clk* frequency (depending on RCWLR[LBCM]).

The value of this resistance and the strength of the driver's current source can be found by making two measurements. First, the output voltage is measured while driving logic 1 without an external differential termination resistor. The measured voltage is  $V_1 = R_{source} \times I_{source}$ . Second, the output voltage is measured while driving logic 1 with an external precision differential termination resistor of value  $R_{term}$ . The measured voltage is  $V_2 = (1/(1/R_1 + 1/R_2)) \times I_{source}$ . Solving for the output impedance gives  $R_{source} = R_{term} \times (V_1/V_2 - 1)$ . The drive current is then  $I_{source} = V_1/R_{source}$ .

This table summarizes the signal impedance targets. The driver impedance are targeted at minimum  $V_{DD}$ , nominal  $OV_{DD}$ , 105°C.

| Impedance      | Local Bus, Ethernet,<br>DUART, Control,<br>Configuration, Power<br>Management | PCI Signals<br>(not including PCI<br>output clocks) | PCI Output Clocks<br>(including<br>PCI_SYNC_OUT) | DDR DRAM  | Symbol            | Unit |

|----------------|-------------------------------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------|-----------|-------------------|------|

| R <sub>N</sub> | 42 Target                                                                     | 25 Target                                           | 42 Target                                        | 20 Target | Z <sub>0</sub>    | W    |

| R <sub>P</sub> | 42 Target                                                                     | 25 Target                                           | 42 Target                                        | 20 Target | Z <sub>0</sub>    | W    |

| Differential   | NA                                                                            | NA                                                  | NA                                               | NA        | Z <sub>DIFF</sub> | W    |

**Table 83. Impedance Characteristics**

Note: Nominal supply voltages. See Table 2,  $T_i = 105^{\circ}C$ .

# 25.5 Configuration Pin Muxing

The device provides the user with power-on configuration options which can be set through the use of external pull-up or pull-down resistors of 4.7 k $\Omega$  on certain output pins (see customer visible configuration pins). These pins are generally used as output only pins in normal operation.

While HRESET is asserted however, these pins are treated as inputs. The value presented on these pins while HRESET is asserted, is latched when PORESET deasserts, at which time the input receiver is disabled and the I/O circuit takes on its normal function. Careful board layout with stubless connections to these pull-up/pull-down resistors coupled with the large value of the pull-up/pull-down resistor should minimize the disruption of signal quality or speed for output pins thus configured.

# 25.6 Pull-Up Resistor Requirements

The device requires high resistance pull-up resistors (10 k $\Omega$  is recommended) on open drain type pins including I<sup>2</sup>C pins and IPIC interrupt pins.

For more information on required pull-up resistors and the connections required for the JTAG interface, see AN3665, "MPC837xE Design Checklist."

# 26 Ordering Information

Ordering information for the parts fully covered by this specification document is provided in Section 26.1, "Part Numbers Fully Addressed by This Document."

| Revision | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 6        | 07/2011 | In Section 2.2, "Power Sequencing," updated power down sequencing information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 5        | 07/2011 | <ul> <li>In Table 2, "Absolute Maximum Ratings<sup>1</sup>," removed footnote 5 from LB<sub>IN</sub> to OV<sub>IN</sub>. Also, corrected footnote 5.</li> <li>In Table 3, "Recommended Operating Conditions," added footnote 2 to AV<sub>DD</sub>.</li> <li>In Figure 2, "Overshoot/Undershoot Voltage for GV<sub>DD</sub>/LV<sub>DD</sub>/OV<sub>DD</sub>/LBV<sub>DD</sub>," added LBV<sub>DD</sub>.</li> <li>In Table 13, "DDR2 SDRAM DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 1.8 V," updated I<sub>OZ</sub> min/max to -50/50.</li> <li>In Figure 11, "RGMII and RTBI AC Timing and Multiplexing Diagrams," added distinction between t<sub>SKRGT_RX</sub> and t<sub>SKRGT_TX</sub> signals.</li> <li>In Table 33, "MII Management AC Timing Specifications," updated MDC frequency—removed Min and Max values, added Typical value. Also, updated footnote 2 and removed footnote 3.</li> <li>In Table 48, "PCI DC Electrical Characteristics," updated V<sub>IH</sub> min value to 2.0.</li> <li>In Table 72, "TePBGA II Pinout Listing," added Note to LGPL4/LFRB_B/LGTA_B/LUPWAIT/LPBSE (to be consistent with AN3665, "MPC837xE Design Checklist."</li> <li>In Table 74, "Operating Frequencies for TePBGA II," added Minimum Operating Frequency values.</li> </ul>                                                                                                                                                                                                                |  |

| 4        | 11/2010 | <ul> <li>In Table 25, "RGMII and RTBI DC Electrical Characteristics," updated V<sub>IH</sub> min value to 1.7.</li> <li>In Table 40, "Local Bus General Timing Parameters—PLL Bypass Mode," added row for t<sub>LBKHLR</sub>.</li> <li>In Section 10.2, "Local Bus AC Electrical Specifications," and in Section 23, "Clocking," updated LCCR to LCRR.</li> <li>In Table 72, "TePBGA II Pinout Listing," added SD_WP to pin C9. Also clarified TEST_SEL0 and TEST_SEL1 pins—no change in functionality.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 3        | 03/2010 | <ul> <li>Added Section 4.3, "eTSEC Gigabit Reference Clock Timing."</li> <li>In Table 34, "USB DC Electrical Characteristics," and Table 35, "USB General Timing Parameters (ULPI Mode Only)," added table footnotes .</li> <li>In Table 39, "Local Bus General Timing Parameters—PLL Enable Mode," and Table 40, "Local Bus General Timing Parameters—PLL Bypass Mode," corrected footnotes for t<sub>LBOTOT1</sub>, t<sub>LBOTOT2</sub>, t<sub>LBOTOT3</sub>.</li> <li>In Figure 22, "Local Bus Signals, GPCM/UPM Signals for LCRR[CLKDIV] = 2 (PLL Enable Mode)," and Figure 24, "Local Bus Signals, GPCM/UPM Signals for LCRR[CLKDIV] = 4 (PLL Enable Mode)," shifted "Input Signals: LAD[0:31]/LDP[0:3]" from the falling edge to the rising edge of LSYNC_IN.</li> <li>In Figure 63, "Mechanical Dimensions and Bottom Surface Nomenclature of the TEPBGA II," added heat spreader.</li> <li>In Section 25.6, "Pull-Up Resistor Requirements," removed "Ethernet Management MDIO pin" from list of open drain type pins.</li> <li>In Table 72, "TePBGA II Pinout Listing," updated the Pin Type column for AVDD_C, AVDD_L, and AVDD_P pins.</li> <li>in Table 72, "TePBGA II Pinout Listing," added Note 16 to eTSEC pins.</li> <li>In Table 77, "CSB Frequency Options for Host Mode," and Table 78, "CSB Frequency Options for Agent Mode," updated <i>csb_clk</i> frequencies available.</li> <li>In Table 84, "Part Numbering Nomenclature," removed footnote to "e300 core Frequency."</li> </ul> |  |

### Table 87. Document Revision History (continued)