Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | AVR                                                       |

| Core Size                  | 32-Bit Single-Core                                        |

| Speed                      | 50MHz                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                    |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 36                                                        |

| Program Memory Size        | 128KB (128K x 8)                                          |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 32K x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                              |

| Data Converters            | A/D 8x12b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                         |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 48-TQFP                                                   |

| Supplier Device Package    | 48-TQFP (7x7)                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/atmel/atuc128l4u-aut |

|                            |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# ATUC64/128/256L3/4U

- One Master/Slave Serial Peripheral Interface (SPI) with Chip Select Signals

- Up to 15 SPI Slaves can be Addressed

- Two Master and Two Slave Two-wire Interfaces (TWI), 400 kbit/s I<sup>2</sup>C-compatible

- One 8-channel Analog-to-digital Converter (ADC) with up to 12 Bits Resolution

Internal Temperature Sensor

- Eight Analog Comparators (AC) with Optional Window Detection

- Capacitive Touch (CAT) Module

- Hardware-assisted Atmel<sup>®</sup> AVR<sup>®</sup> QTouch<sup>®</sup> and Atmel<sup>®</sup> AVR<sup>®</sup> QMatrix Touch Acquisition

- Supports QTouch and QMatrix Capture from Capacitive Touch Sensors

- QTouch Library Support

- Capacitive Touch Buttons, Sliders, and Wheels

- QTouch and QMatrix Acquisition

- Audio Bitstream DAC (ABDACB) Suitable for Stereo Audio

- Inter-IC Sound (IISC) Controller

- Compliant with Inter-IC Sound (I<sup>2</sup>S) Specification

- On-chip Non-intrusive Debug System

- Nexus Class 2+, Runtime Control, Non-intrusive Data and Program Trace

- aWire Single-pin Programming Trace and Debug Interface, Muxed with Reset Pin

- NanoTrace Provides Trace Capabilities through JTAG or aWire Interface

- 64-pin TQFP/QFN (51 GPIO Pins), 48-pin TQFP/QFN/TLLGA (36 GPIO Pins)

- Six High-drive I/O Pins (64-pin Packages), Four High-drive I/O Pins (48-pin Packages)

- Single 1.62-3.6V Power Supply

# 3.3 Signal Descriptions

The following table gives details on signal name classified by peripheral.

| Signal Name       | Function                             | Туре             | Active<br>Level | Comments |

|-------------------|--------------------------------------|------------------|-----------------|----------|

|                   | Audio Bitstream I                    | DAC - ABDACB     |                 |          |

| CLK               | D/A Clock out                        | Output           |                 |          |

| DAC1 - DAC0       | D/A Bitstream out                    | Output           |                 |          |

| DACN1 - DACN0     | D/A Inverted bitstream out           | Output           |                 |          |

|                   | Analog Comparator                    | Interface - ACIF | В               |          |

| ACAN3 - ACAN0     | Negative inputs for comparators "A"  | Analog           |                 |          |

| ACAP3 - ACAP0     | Positive inputs for comparators "A"  | Analog           |                 |          |

| ACBN3 - ACBN0     | Negative inputs for comparators "B"  | Analog           |                 |          |

| ACBP3 - ACBP0     | Positive inputs for comparators "B"  | Analog           |                 |          |

| ACREFN            | Common negative reference            | Analog           |                 |          |

|                   | ADC Interface                        | e - ADCIFB       |                 |          |

| AD8 - AD0         | Analog Signal                        | Analog           |                 |          |

| ADP1 - ADP0       | Drive Pin for resistive touch screen | Output           |                 |          |

| TRIGGER           | External trigger                     | Input            |                 |          |

|                   | aWire -                              | AW               |                 |          |

| DATA              | aWire data                           | I/O              |                 |          |

| DATAOUT           | aWire data output for 2-pin mode     | I/O              |                 |          |

|                   | Capacitive Touch                     | Module - CAT     |                 |          |

| CSA16 - CSA0      | Capacitive Sense A                   | I/O              |                 |          |

| CSB16 - CSB0      | Capacitive Sense B                   | I/O              |                 |          |

| DIS               | Discharge current control            | Analog           |                 |          |

| SMP               | SMP signal                           | Output           |                 |          |

| SYNC              | Synchronize signal                   | Input            |                 |          |

| VDIVEN            | Voltage divider enable               | Output           |                 |          |

|                   | External Interrupt                   | Controller - EIC |                 |          |

| NMI (EXTINT0)     | Non-Maskable Interrupt               | Input            |                 |          |

| EXTINT5 - EXTINT1 | TINT1 External interrupt             |                  |                 |          |

|                   | Glue Logic Cont                      | roller - GLOC    |                 |          |

| IN7 - IN0         | Inputs to lookup tables              | Input            |                 |          |

| OUT1 - OUT0       | Outputs from lookup tables           | Output           |                 |          |

|                   | Inter-IC Sound (I2S)                 | Controller - IIS | С               | +        |

**Table 3-7.**Signal Descriptions List

### 3.4.5 TWI Pins PA05/PA07/PA17

When these pins are used for TWI, the pins are open-drain outputs with slew-rate limitation and inputs with spike filtering. When used as GPIO pins or used for other peripherals, the pins have the same characteristics as other GPIO pins.

After reset a TWI function is selected on these pins instead of the GPIO. Please refer to the GPIO Module Configuration chapter for details.

# 3.4.6 GPIO Pins

All the I/O lines integrate a pull-up resistor. Programming of this pull-up resistor is performed independently for each I/O line through the GPIO Controllers. After reset, I/O lines default as inputs with pull-up resistors disabled, except PA00 which has the pull-up resistor enabled. PA20 selects SCIF-RC32OUT (GPIO Function F) as default enabled after reset.

## 3.4.7 High-drive Pins

The six pins PA02, PA06, PA08, PA09, PB01, and PB15 have high-drive output capabilities. Refer to Section 35. on page 897 for electrical characteristics.

## 3.4.8 USB Pins PB13/PB14

When these pins are used for USB, the pins are behaving according to the USB specification. When used as GPIO pins or used for other peripherals, the pins have the same behaviour as other normal I/O pins, but the characteristics are different. Refer to Section 35. on page 897 for electrical characteristics.

To be able to use the USB I/O the VDDIN power supply must be 3.3V nominal.

# 3.4.9 RC32OUT Pin

#### 3.4.9.1 Clock output at startup

After power-up, the clock generated by the 32kHz RC oscillator (RC32K) will be output on PA20, even when the device is still reset by the Power-On Reset Circuitry. This clock can be used by the system to start other devices or to clock a switching regulator to rise the power supply voltage up to an acceptable value.

The clock will be available on PA20, but will be disabled if one of the following conditions are true:

- PA20 is configured to use a GPIO function other than F (SCIF-RC32OUT)

- PA20 is configured as a General Purpose Input/Output (GPIO)

- The bit FRC32 in the Power Manager PPCR register is written to zero (refer to the Power Manager chapter)

The maximum amplitude of the clock signal will be defined by VDDIN.

Once the RC32K output on PA20 is disabled it can never be enabled again.

# 3.4.9.2 XOUT32\_2 function

PA20 selects RC32OUT as default enabled after reset. This function is not automatically disabled when the user enables the XOUT32\_2 function on PA20. This disturbs the oscillator and may result in the wrong frequency. To avoid this, RC32OUT must be disabled when XOUT32\_2 is enabled.

32142D-06/2013

Atmel

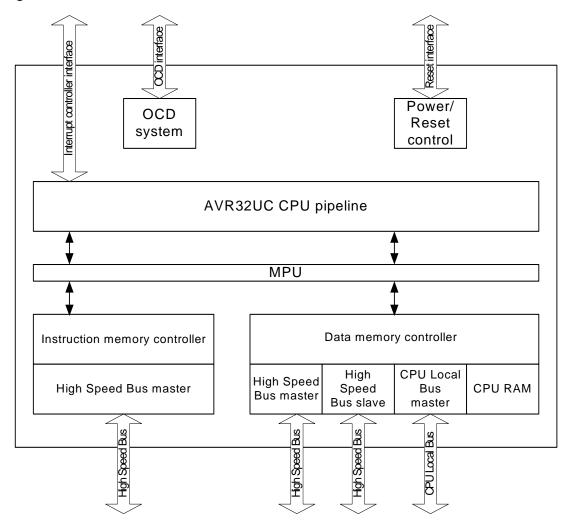

Figure 4-1. Overview of the AVR32UC CPU

# 4.3.1 Pipeline Overview

AVR32UC has three pipeline stages, Instruction Fetch (IF), Instruction Decode (ID), and Instruction Execute (EX). The EX stage is split into three parallel subsections, one arithmetic/logic (ALU) section, one multiply (MUL) section, and one load/store (LS) section.

Instructions are issued and complete in order. Certain operations require several clock cycles to complete, and in this case, the instruction resides in the ID and EX stages for the required number of clock cycles. Since there is only three pipeline stages, no internal data forwarding is required, and no data dependencies can arise in the pipeline.

Figure 4-2 on page 24 shows an overview of the AVR32UC pipeline stages.

Atmel

| 7.7.25 Perfori<br>Name: | mance Chai<br>PRSTA | nnel 1 Read St<br>LL1 | all Cycles |         |    |    |    |

|-------------------------|---------------------|-----------------------|------------|---------|----|----|----|

| Access Type:            | Read-o              | nly                   |            |         |    |    |    |

| Offset:                 | 0x820               |                       |            |         |    |    |    |

| Reset Value:            | 0x0000              | 0000                  |            |         |    |    |    |

| 31                      | 30                  | 29                    | 28         | 27      | 26 | 25 | 24 |

|                         |                     |                       | STALL      | [31:24] |    |    |    |

|                         |                     |                       |            |         |    |    |    |

| 23                      | 22                  | 21                    | 20         | 19      | 18 | 17 | 16 |

|                         |                     |                       | STALL      | [23:16] |    |    |    |

|                         |                     |                       |            |         |    |    |    |

| 15                      | 14                  | 13                    | 12         | 11      | 10 | 9  | 8  |

|                         |                     |                       | STALL      | -[15:8] |    |    |    |

|                         |                     |                       |            |         |    |    |    |

| 7                       | 6                   | 5                     | 4          | 3       | 2  | 1  | 0  |

|                         |                     |                       | STAL       | L[7:0]  |    |    |    |

STALL: Stall Cycles Counted Since Last Reset

Clock cycles are counted using the CLK\_PDCA\_HSB clock

**Atmel**

| 8.7.2.11       | Endpoin | Endpoint n Status Register |       |  |  |  |

|----------------|---------|----------------------------|-------|--|--|--|

| Register Name: |         | UESTAn, n in [06]          |       |  |  |  |

| Access Type:   |         | Read-Only 0x0100           |       |  |  |  |

| Offset:        |         | 0x0130 + (n *              | 0x04) |  |  |  |

| Reset Value:   |         | 0x0000000                  |       |  |  |  |

| 31  | 30                      | 29 | 28      | 27      | 26                 | 25      | 24    |

|-----|-------------------------|----|---------|---------|--------------------|---------|-------|

| -   | -                       | -  | -       | -       | -                  | -       | -     |

|     |                         |    |         |         |                    |         |       |

| 23  | 22                      | 21 | 20      | 19      | 18                 | 17      | 16    |

| -   | -                       | -  | -       | -       | -                  | CTRLDIR | -     |

|     |                         |    |         |         |                    |         |       |

| 15  | 14                      | 13 | 12      | 11      | 10                 | 9       | 8     |

| CUR | CURRBK NBUSYBK RAMACERI |    | NBUSYBK |         | -                  | DTS     | SEQ   |

|     |                         |    |         |         |                    |         |       |

| 7   | 6                       | 5  | 4       | 3       | 2                  | 1       | 0     |

| -   | STALLEDI/<br>CRCERRI    | -  | NAKINI  | NAKOUTI | RXSTPI/<br>ERRORFI | RXOUTI  | TXINI |

# • CTRLDIR: Control Direction

Writing a zero or a one to this bit has no effect.

This bit is cleared after a SETUP packet to indicate that the following packet is an OUT packet.

This bit is set after a SETUP packet to indicate that the following packet is an IN packet.

# • CURRBK: Current Bank

This bit is set for non-control endpoints, indicating the current bank:

| CURRBK |   | Current Bank |

|--------|---|--------------|

| 0      | 0 | Bank0        |

| 0      | 1 | Bank1        |

| 1      | 0 | Reserved     |

| 1      | 1 | Reserved     |

This field may be updated one clock cycle after the RWALL bit changes, so the user should not poll this field as an interrupt bit.

# • NBUSYBK: Number of Busy Banks

This field is set to indicate the number of busy banks:

| NBUS | SYBK | Number of Busy Banks |

|------|------|----------------------|

| 0    | 0    | 0 (all banks free)   |

| 0    | 1    | 1                    |

| 1    | 0    | 2                    |

| 1    | 1    | Reserved             |

| BOOTPROT | Pages protected by<br>BOOTPROT | Size of protected<br>memory |

|----------|--------------------------------|-----------------------------|

| 7        | None                           | 0                           |

| 6        | 0-1                            | 1 Kbyte                     |

| 5        | 0-3                            | 2Kbyte                      |

| 4        | 0-7                            | 4Kbyte                      |

| 3        | 0-15                           | 8Kbyte                      |

| 2        | 0-31                           | 16Kbyte                     |

| 1        | 0-63                           | 32 Kbyte                    |

| 0        | 0-127                          | 64Kbyte                     |

# Table 9-3. Boot Loader Area Specified by BOOTPROT

The SECURE fuses have the following functionality:

Table 9-5.

Secure State Configuration

| SECURE | Functionality                               | SSE | SSDE |

|--------|---------------------------------------------|-----|------|

| 00     | Secure state disabled                       | 0   | 0    |

| 01     | Secure enabled, secure state debug enabled  | 1   | 1    |

| 10     | Secure enabled, secure state debug disabled | 1   | 0    |

| 11     | Secure state disabled                       | 0   | 0    |

To erase or write a general-purpose fuse bit, the commands Write General-Purpose Fuse Bit (WGPB) and Erase General-Purpose Fuse Bit (EGPB) are provided. Writing one of these commands, together with the number of the fuse to write/erase, performs the desired operation.

An entire General-Purpose Fuse byte can be written at a time by using the Program GP Fuse Byte (PGPFB) instruction. A PGPFB to GP fuse byte 2 is not allowed if the flash is locked by the security bit. The PFB command is issued with a parameter in the PAGEN field:

- PAGEN[2:0] byte to write

- PAGEN[10:3] Fuse value to write

All general-purpose fuses can be erased by the Erase All General-Purpose fuses (EAGP) command. An EAGP command is not allowed if the flash is locked by the security bit.

Two errors can be detected in the FSR register after issuing these commands:

- Programming Error: A bad keyword and/or an invalid command have been written in the FCMD register.

- Lock Error:

- A write or erase of the BOOTPROT or EPFL or UPROT fuse bits was attempted while the flash is locked by the security bit.

- A write or erase of the SECURE fuse bits was attempted when SECURE mode was enabled.

The lock bits are implemented using the lowest 16 general-purpose fuse bits. This means that the 16 lowest general-purpose fuse bits can also be written/erased using the commands for locking/unlocking regions, see Section 9.5.3.

# • FSZ: Flash Size

The size of the flash. Not all device families will provide all flash sizes indicated in the table.

| FSZ | Flash Size | FSZ | Flash Size |

|-----|------------|-----|------------|

| 0   | 4 Kbyte    | 8   | 192 Kbyte  |

| 1   | 8 Kbyte    | 9   | 256 Kbyte  |

| 2   | 16 Kbyte   | 10  | 384 Kbyte  |

| 3   | 32 Kbyte   | 11  | 512 Kbyte  |

| 4   | 48 Kbyte   | 12  | 768 Kbyte  |

| 5   | 64 Kbyte   | 13  | 1024 Kbyte |

| 6   | 96 Kbyte   | 14  | 2048 Kbyte |

| 7   | 128 Kbyte  | 15  | Reserved   |

# Table 9-10.Flash Size

Atmel

# ATUC64/128/256L3/4U

# 9.9.1 Flash General Purpose Fuse Register Low (FGPFRLO)

| 31          | 30    | 29      | 28                    | 27     | 26       | 25 | 24   |

|-------------|-------|---------|-----------------------|--------|----------|----|------|

| BOD         | EN    | BODHYST | BODHYST BODLEVEL[5:1] |        |          |    |      |

|             |       |         |                       |        |          |    |      |

| 23          | 22    | 21      | 20                    | 19     | 18       | 17 | 16   |

| BODLEVEL[0] | UPROT | SEC     | URE                   |        | BOOTPROT |    | EPFL |

|             |       |         |                       |        |          |    |      |

| 15          | 14    | 13      | 12                    | 11     | 10       | 9  | 8    |

|             |       |         | LOCK[                 | [15:8] |          |    |      |

|             |       |         |                       |        |          |    |      |

| 7           | 6     | 5       | 4                     | 3      | 2        | 1  | 0    |

|             |       |         | LOCK                  | [7:0]  |          |    |      |

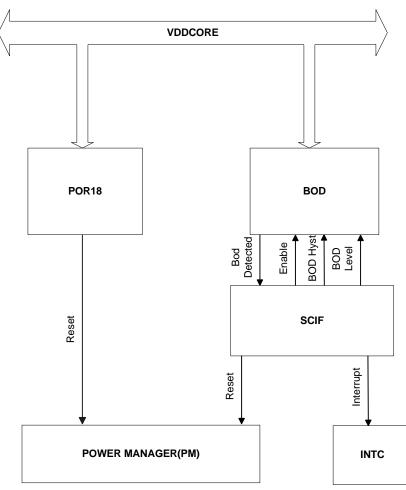

## BODEN: Brown Out Detector Enable

| BODEN | Description                     |

|-------|---------------------------------|

| 00    | BOD disabled                    |

| 01    | BOD enabled, BOD reset enabled  |

| 10    | BOD enabled, BOD reset disabled |

| 11    | BOD disabled                    |

#### • BODHYST: Brown Out Detector Hysteresis

- 0: The Brown out detector hysteresis is disabled

- 1: The Brown out detector hysteresis is enabled

#### • BODLEVEL: Brown Out Detector Trigger Level

This controls the voltage trigger level for the Brown out detector. Refer to "Electrical Characteristics" on page 897.

# • UPROT, SECURE, BOOTPROT, EPFL, LOCK

- These are Flash Controller fuses and are described in the FLASHCDW section.

- 9.9.1.1 Default Fuse Value

The devices are shipped with the FGPFRLO register value:0xE07FFFFF:

- BODEN fuses set to 11. BOD is disabled.

- BODHYST fuse set to 1. The BOD hysteresis is enabled.

- BODLEVEL fuses set to 000000. This is the minimum voltage trigger level for BOD. This level is lower than the POR level, so when BOD is enabled, it will never trigger with this default value.

- UPROT fuse set to 1.

- SECURE fuse set to 11.

- BOOTPROT fuses set to 111. The bootloader protection is disabled.

- EPFL fuse set to 1. External privileged fetch is not locked.

- LOCK fuses set to 1111111111111111. No region locked.

After the JTAG or aWire chip erase command, the FGPFR register value is 0xFFFFFFF.

The CTRL, HYST, and LEVEL fields in the BOD Control Register are loaded factory defined calibration values from flash fuses after a reset. If the Flash Calibration Done bit in the BOD Control Register (BOD.FCD) is zero, the flash calibration will be redone after any reset, and the BOD.FCD bit will be set before program execution starts in the CPU. If BOD.FCD is one, the flash calibration is redone after any reset except for a BOD reset. The BOD.FCD bit is cleared after a reset, except for a BOD reset. BOD.FCD is set when these fields have been updated after a flash calibration. It is possible to override the values in the BOD.CTRL, BOD.HYST, and BOD.LEVEL fields after reset by writing to the BOD Control Register. Please refer to the Fuse Settings chapter for more details about BOD fuses and how to program the fuses.

## 14.5.6 Bandgap

Rev: 1.2.0.0

The flash memory, the BOD, and the Temperature Sensor need a stable voltage reference to operate. This reference voltage is provided by an internal Bandgap voltage reference. This reference is automatically turned on at start-up and turned off during some sleep modes to save power. The Bandgap reference is powered by the internal regulator supply voltage and will not be powered during Shutdown sleep mode. Please refer to the Power Manager chapter for details.

32142D-06/2013

Atmel

| 15.6.20 Vers | Version Register |  |  |  |

|--------------|------------------|--|--|--|

| Name:        | VERSION          |  |  |  |

| Access Type: | Read-only        |  |  |  |

| Offset:      | 0xFC             |  |  |  |

| Reset Value: | -                |  |  |  |

| 31 | 30 | 29 | 28    | 27            | 26  | 25  | 24 |

|----|----|----|-------|---------------|-----|-----|----|

| -  | -  | -  | -     | -             | -   | -   | -  |

|    |    |    |       |               |     |     |    |

| 23 | 22 | 21 | 20    | 19            | 18  | 17  | 16 |

| -  | -  | -  | -     |               | VAR | ANT |    |

|    |    |    |       |               |     |     |    |

| 15 | 14 | 13 | 12    | 11            | 10  | 9   | 8  |

| -  | -  | -  | -     | VERSION[11:8] |     |     |    |

|    |    |    |       |               |     |     |    |

| 7  | 6  | 5  | 4     | 3             | 2   | 1   | 0  |

|    |    |    | VERSI | ON[7:0]       |     |     |    |

• VARIANT: Variant Number

Reserved. No functionality associated.

• VERSION: Version Number

Version number of the module. No functionality associated.

# 20.7.5 Interrupt Mask Register

| Name:        | IMR       |

|--------------|-----------|

| Access Type: | Read-only |

Offset: 0x10

**Reset Value:** 0x0000000

| 31    | 30    | 29         | 28     | 27     | 26        | 25      | 24      |

|-------|-------|------------|--------|--------|-----------|---------|---------|

| _     | _     | LINSNRE    | LINCE  | LINIPE | LINISFE   | LINBE   | _       |

| 23    | 22    | 21         | 20     | 19     | 18        | 17      | 16      |

| -     | -     | —          | _      | CTSIC  | —         | -       | _       |

| 15    | 14    | 13         | 12     | 11     | 10        | 9       | 8       |

| LINTC | LINID | NACK/LINBK | RXBUFF | —      | ITER/UNRE | TXEMPTY | TIMEOUT |

| 7     | 6     | 5          | 4      | 3      | 2         | 1       | 0       |

| PARE  | FRAME | OVRE       | _      | _      | RXBRK     | TXRDY   | RXRDY   |

0: The corresponding interrupt is disabled.

1: The corresponding interrupt is enabled.

A bit in this register is cleared when the corresponding bit in IDR is written to one.

A bit in this register is set when the corresponding bit in IER is written to one.

**Atmel**

| 25.7.9   | Status Clear Register |            |  |  |

|----------|-----------------------|------------|--|--|

| Name:    | SCR                   |            |  |  |

| Access   | Туре:                 | Write-only |  |  |

| Offset:  |                       | 0x20       |  |  |

| Reset Va | alue:                 | 0x00000000 |  |  |

| 31 | 30 | 29 | 28 | 27 | 26    | 25 | 24   |

|----|----|----|----|----|-------|----|------|

| -  | -  | -  | -  | -  | -     | -  | -    |

| 23 | 22 | 21 | 20 | 19 | 18    | 17 | 16   |

| -  | -  | -  | -  | -  | -     | -  | -    |

|    |    |    |    |    |       | _  |      |

| 15 | 14 | 13 | 12 | 1  | 10    | 9  | 8    |

| -  | -  | -  | -  | -  | -     | -  | -    |

|    |    |    |    |    |       |    |      |

| 7  | 6  | 5  | 4  | 3  | 2     | 1  | 0    |

| -  | -  | -  | -  | -  | READY | -  | TOFL |

Writing a zero to a bit in this register has no effect.

Writing a one to a bit in this register will clear the corresponding bit in SR and the corresponding interrupt request. This register always reads as zero.

# 29. ADC Interface (ADCIFB)

Rev:1.0.1.1

# 29.1 Features

- Multi-channel Analog-to-Digital Converter with up to 12-bit resolution

- Enhanced Resolution Mode

- 11-bit resolution obtained by interpolating 4 samples

- 12-bit resolution obtained by interpolating 16 samples

- Glueless interface with resistive touch screen panel, allowing

- Resistive Touch Screen position measurement

- Pen detection and pen loss detection

- Integrated enhanced sequencer

- ADC Mode

- Resistive Touch Screen Mode

- Numerous trigger sources

- Software

- Embedded 16-bit timer for periodic trigger

- Pen detect trigger

- Continuous trigger

- External trigger, rising, falling, or any-edge trigger

- Peripheral event trigger

- ADC Sleep Mode for low power ADC applications

- Programmable ADC timings

- Programmable ADC clock

- Programmable startup time

# 29.2 Overview

The ADC Interface (ADCIFB) converts analog input voltages to digital values. The ADCIFB is based on a Successive Approximation Register (SAR) 10-bit Analog-to-Digital Converter (ADC). The conversions extend from 0V to ADVREFP.

The ADCIFB supports 8-bit and 10-bit resolution mode, in addition to enhanced resolution mode with 11-bit and 12-bit resolution. Conversion results are reported in a common register for all channels.

The 11-bit and 12-bit resolution modes are obtained by interpolating multiple samples to acquire better accuracy. For 11-bit mode 4 samples are used, which gives an effective sample rate of 1/4 of the actual sample frequency. For 12-bit mode 16 samples are used, giving a effective sample rate of 1/16 of actual. This arrangement allows conversion speed to be traded for better accuracy.

Conversions can be started for all enabled channels, either by a software trigger, by detection of a level change on the external trigger pin (TRIGGER), or by an integrated programmable timer.

When the Resistive Touch Screen Mode is enabled, an integrated sequencer automatically configures the pad control signals and performs resistive touch screen conversions.

The ADCIFB also integrates an ADC Sleep Mode, a Pen-Detect Mode, and an Analog Compare Mode, and connects with one Peripheral DMA Controller channel. These features reduce both power consumption and processor intervention.

| 31.7.31 Parameter | Parameter Register |  |  |

|-------------------|--------------------|--|--|

| Name:             | PARAMETER          |  |  |

| Access Type:      | Read-only          |  |  |

| Offset:           | 0xF8               |  |  |

| Reset Value:      | -                  |  |  |

| 31 | 30       | 29 | 28   | 27    | 26 | 25 | 24 |

|----|----------|----|------|-------|----|----|----|

|    |          |    | SP[3 | 1:24] |    |    |    |

| 23 | 22       | 21 | 20   | 19    | 18 | 17 | 16 |

|    |          |    | SP[2 | 3:16] |    |    |    |

| 15 | 14       | 13 | 12   | 11    | 10 | 9  | 8  |

|    | SP[15:8] |    |      |       |    |    |    |

| 7  | 6        | 5  | 4    | 3     | 2  | 1  | 0  |

|    | SP[7:0]  |    |      |       |    |    |    |

# • SP[n]: Sensor pair implemented

0: The corresponding sensor pair is not implemented

1: The corresponding sensor pair is implemented.

**Atmel**

# 32.4 I/O Lines Description

| Pin Name  | Pin Description           | Туре   |  |  |  |

|-----------|---------------------------|--------|--|--|--|

| IN0-INm   | Inputs to lookup tables   | Input  |  |  |  |

| OUT0-OUTn | Output from lookup tables | Output |  |  |  |

Table 32-1.I/O Lines Description

Each LUT have 4 inputs and one output. The inputs and outputs for the LUTs are mapped sequentially to the inputs and outputs. This means that LUT0 is connected to IN0 to IN3 and OUT0. LUT1 is connected to IN4 to IN7 and OUT1. In general, LUTn is connected to IN[4n] to IN[4n+3] and OUTn.

# 32.5 Product Dependencies

In order to use this module, other parts of the system must be configured correctly, as described below.

# 32.5.1 I/O Lines

The pins used for interfacing the GLOC may be multiplexed with I/O Controller lines. The programmer must first program the I/O Controller to assign the desired GLOC pins to their peripheral function. If I/O lines of the GLOC are not used by the application, they can be used for other purposes by the I/O Controller.

It is only required to enable the GLOC inputs and outputs actually in use. Pullups for pins configured to be used by the GLOC will be disabled.

# 32.5.2 Clocks

The clock for the GLOC bus interface (CLK\_GLOC) is generated by the Power Manager. This clock is enabled at reset, and can be disabled in the Power Manager. It is recommended to disable the GLOC before disabling the clock, to avoid freezing the module in an undefined state.

Additionally, the GLOC depends on a dedicated Generic Clock (GCLK). The GCLK can be set to a wide range of frequencies and clock sources, and must be enabled by the System Control Interface (SCIF) before the GLOC filter can be used.

# 32.5.3 Debug Operation

When an external debugger forces the CPU into debug mode, the GLOC continues normal operation.

# 32.6 Functional Description

#### 32.6.1 Enabling the Lookup Table Inputs

Since the inputs to each lookup table (LUT) unit can be multiplexed with other peripherals, each input must be explicitly enabled by writing a one to the corresponding enable bit (AEN) in the corresponding Control Register (CR).

If no inputs are enabled, the output OUTn will be the least significant bit in the TRUTHn register.

Starting in Run-Test/Idle, OCD registers are accessed in the following way:

- 1. Select the IR Scan path.

- 2. In Capture-IR: The IR output value is latched into the shift register.

- 3. In Shift-IR: The instruction register is shifted by the TCK input.

- 4. Return to Run-Test/Idle.

- 5. Select the DR Scan path.

- 6. In Shift-DR: Scan in the direction bit (1=read, 0=write) and the 7-bit address for the OCD register.

- 7. Go to Update-DR and re-enter Select-DR Scan.

- 8. In Shift-DR: For a read operation, scan out the contents of the addressed register. For a write operation, scan in the new contents of the register.

- 9. Return to Run-Test/Idle.

For any operation, the full 7 bits of the address must be provided. For write operations, 32 data bits must be provided, or the result will be undefined. For read operations, shifting may be terminated once the required number of bits have been acquired.

| Instructions                       | Details                                       |

|------------------------------------|-----------------------------------------------|

| IR input value                     | <b>10000</b> (0x10)                           |

| IR output value                    | peb01                                         |

| DR Size                            | 34 bits                                       |

| DR input value (Address phase)     | aaaaaaar xxxxxxxx xxxxxxxx xxxxxxx xx         |

| DR input value (Data read phase)   | <b>XXXXXXXX XXXXXXXX XXXXXXXX XXXXXXXX</b> XX |

| DR input value (Data write phase)  | ddddddd ddddddd ddddddd ddddddd xx            |

| DR output value (Address phase)    | xx xxxxxxxx xxxxxxxx xxxxxxxx xxxxxxeb        |

| DR output value (Data read phase)  | eb ddddddd ddddddd ddddddd ddddddd            |

| DR output value (Data write phase) | xx xxxxxxx xxxxxxx xxxxxxx xxxxxxeb           |

#### 34.5.3.2 MEMORY\_SERVICE

This instruction allows access to registers in an optional Memory Service Unit. The 7-bit register index, a read/write control bit, and the 32-bit data is accessed through the JTAG port.

The data register is alternately interpreted by the SAB as an address register and a data register. The SAB starts in address mode after the MEMORY\_SERVICE instruction is selected, and toggles between address and data mode each time a data scan completes with the busy bit cleared.

Starting in Run-Test/Idle, Memory Service registers are accessed in the following way:

- 1. Select the IR Scan path.

- 2. In Capture-IR: The IR output value is latched into the shift register.

- 3. In Shift-IR: The instruction register is shifted by the TCK input.

- 4. Return to Run-Test/Idle.

- 5. Select the DR Scan path.

- 6. In Shift-DR: Scan in the direction bit (1=read, 0=write) and the 7-bit address for the Memory Service register.

- 1. The size of the data field: 7 (size and starting address + read length indicator) in the length field.

- 2. The size of the transfer: Words, halfwords, or bytes.

- 3. The starting address of the transfer.

- 4. The number of **bytes** to read (max 65532).

The 4 MSB of the 36 bit SAB address are submitted together with the size field (2 bits). The 4 remaining address bytes are submitted before the number of bytes to read. The size of the transfer is specified using the values from the following table:

## Table 34-43. Size Field Decoding

| Size field | Description       |

|------------|-------------------|

| 00         | Byte transfer     |

| 01         | Halfword transfer |

| 10         | Word transfer     |

| 11         | Reserved          |

Below is an example read command:

- 1. 0x55 (sync)

- 2. 0x81 (command)

- 3. 0x00 (length MSB)

- 4. 0x07 (length LSB)

- 5. 0x25 (size and address MSB, the two MSB of this byte are unused and set to zero)

- 6. 0x00

- 7. 0x00

- 8. 0x00

- 9. 0x04 (address LSB)

- 10. 0x00

- 11. 0x04

- 12. 0xXX (CRC MSB)

- 13. 0xXX (CRC LSB)

The length field is set to 0x0007 because there are 7 bytes of additional data: 5 bytes of address and size and 2 bytes with the number of bytes to read. The address and size field indicates one word (four bytes) should be read from address 0x500000004.

| Table 34-44. | MEMORY_ | _READ Details |

|--------------|---------|---------------|

|--------------|---------|---------------|

Atmel

| Command            | Details                                                                                                               |

|--------------------|-----------------------------------------------------------------------------------------------------------------------|

| Command value      | 0x81                                                                                                                  |

| Additional data    | Size, Address and Length                                                                                              |

| Possible responses | 0xC1: MEMDATA (Section 34.6.8.4)<br>0xC2: MEMORY_READWRITE_STATUS (Section 34.6.8.5)<br>0x41: NACK (Section 34.6.8.2) |

# 35.9.9.2 Strong Pull-up Pull-down

Table 35-37. Strong Pull-up Pull-down

| Parameter          | Min | Тур | Max | Unit |  |

|--------------------|-----|-----|-----|------|--|

| Pull-down resistor |     | 1   |     | kOhm |  |

| Pull-up resistor   |     | 1   |     |      |  |

# 35.9.10 USB Transceiver Characteristics

The USB on-chip buffers comply with the Universal Serial Bus (USB) v2.0 standard. All AC parameters related to these buffers can be found within the USB 2.0 electrical specifications.

# 35.9.10.1 Electrical Characteristics

## Table 35-38. Electrical Parameters

| Symbol           | Parameter                                | Conditions                                 | Min | Тур | Max | Unit |

|------------------|------------------------------------------|--------------------------------------------|-----|-----|-----|------|

| R <sub>EXT</sub> | Recommended external USB series resistor | In series with each USB pin with $\pm 5\%$ |     | 39  |     | Ohm  |

# Atmel

| 20 | Universal Synchronous Asynchronous Receiver Transmitter (USART)<br>434 |                             |     |

|----|------------------------------------------------------------------------|-----------------------------|-----|

|    | 20.1                                                                   | Features                    | 434 |

|    | 20.2                                                                   | Overview                    | 434 |

|    | 20.3                                                                   | Block Diagram               | 435 |

|    | 20.4                                                                   | I/O Lines Description       | 436 |

|    | 20.5                                                                   | Product Dependencies        | 436 |

|    | 20.6                                                                   | Functional Description      | 437 |

|    | 20.7                                                                   | User Interface              | 463 |

|    | 20.8                                                                   | Module Configuration        | 485 |

| 21 | Serial I                                                               | Peripheral Interface (SPI)  | 486 |

|    | 21.1                                                                   | Features                    | 486 |

|    | 21.2                                                                   | Overview                    | 486 |

|    | 21.3                                                                   | Block Diagram               | 487 |

|    | 21.4                                                                   | Application Block Diagram   | 487 |

|    | 21.5                                                                   | I/O Lines Description       | 488 |

|    | 21.6                                                                   | Product Dependencies        | 488 |

|    | 21.7                                                                   | Functional Description      | 488 |

|    | 21.8                                                                   | User Interface              | 499 |

|    | 21.9                                                                   | Module Configuration        | 526 |

| 22 | Two-wi                                                                 | ire Master Interface (TWIM) | 527 |

|    | 22.1                                                                   | Features                    | 527 |

|    | 22.2                                                                   | Overview                    | 527 |

|    | 22.3                                                                   | List of Abbreviations       | 528 |

|    | 22.4                                                                   | Block Diagram               | 528 |

|    | 22.5                                                                   | Application Block Diagram   | 529 |

|    | 22.6                                                                   | I/O Lines Description       | 529 |

|    | 22.7                                                                   | Product Dependencies        | 529 |

|    | 22.8                                                                   | Functional Description      | 531 |

|    | 22.9                                                                   | User Interface              | 543 |

|    | 22.10                                                                  | Module Configuration        | 560 |

| 23 | Two-wi                                                                 | ire Slave Interface (TWIS)  | 561 |

|    | 23.1                                                                   | Features                    | 561 |

|    | 23.2                                                                   | Overview                    | 561 |

|    | 23.3                                                                   | List of Abbreviations       |     |