Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| 2 0 000                    |                                                              |

|----------------------------|--------------------------------------------------------------|

| Product Status             | Active                                                       |

| Core Processor             | HCS12X                                                       |

| Core Size                  | 16-Bit                                                       |

| Speed                      | 80MHz                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, SCI, SPI                           |

| Peripherals                | LVD, POR, PWM, WDT                                           |

| Number of I/O              | 91                                                           |

| Program Memory Size        | 128KB (128K x 8)                                             |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 2K x 8                                                       |

| RAM Size                   | 12K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 2.75V                                                |

| Data Converters            | A/D 16x10b                                                   |

| Oscillator Type            | External                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                           |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 112-LQFP                                                     |

| Supplier Device Package    | 112-LQFP (20x20)                                             |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=s912xdg128f2mal |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Vector Address <sup>1</sup>  | XGATE<br>Channel ID <sup>2</sup> | Interrupt Source                       | CCR<br>Mask                       | Local Enable                      |

|------------------------------|----------------------------------|----------------------------------------|-----------------------------------|-----------------------------------|

| \$FFFE                       | _                                | System reset or illegal access reset   | None                              | None                              |

| \$FFFC                       | —                                | Clock monitor reset                    | None                              | PLLCTL (CME, SCME)                |

| \$FFFA                       | —                                | COP watchdog reset                     | None                              | COP rate select                   |

| Vector base + \$F8           | —                                | Unimplemented instruction trap         | None                              | None                              |

| Vector base+ \$F6            | —                                | SWI                                    | None                              | None                              |

| Vector base+ \$F4            | —                                | XIRQ                                   | X Bit                             | None                              |

| Vector base+ \$F2            | —                                | ĪRQ                                    | l bit                             | IRQCR (IRQEN)                     |

| Vector base+ \$F0            | \$78                             | Real time interrupt                    | I bit                             | CRGINT (RTIE)                     |

| Vector base+ \$EE            | \$77                             | Enhanced capture timer channel 0       | I bit                             | TIE (COI)                         |

| Vector base + \$EC           | \$76                             | Enhanced capture timer channel 1       | l bit                             | TIE (C1I)                         |

| Vector base+ \$EA            | \$75                             | Enhanced capture timer channel 2       | I bit                             | TIE (C2I)                         |

| Vector base+ \$E8            | \$74                             | Enhanced capture timer channel 3       | I bit                             | TIE (C3I)                         |

| Vector base+ \$E6            | \$73                             | Enhanced capture timer channel 4       | I bit                             | TIE (C4I)                         |

| Vector base+ \$E4            | \$72                             | Enhanced capture timer channel 5       | I bit                             | TIE (C5I)                         |

| Vector base + \$E2 \$71      |                                  | Enhanced capture timer channel 6       | I bit                             | TIE (C6I)                         |

| Vector base+ \$E0            | \$70                             | Enhanced capture timer channel 7       | I bit                             | TIE (C7I)                         |

| Vector base+ \$DE            | \$6F                             | Enhanced capture timer overflow        | I bit                             | TSRC2 (TOF)                       |

| Vector base+ \$DC            | \$6E                             | Pulse accumulator A overflow           | I bit                             | PACTL (PAOVI)                     |

| Vector base + \$DA           | \$6D                             | Pulse accumulator input edge           | I bit                             | PACTL (PAI)                       |

| Vector base + \$D8           | \$6C                             | SPI0                                   |                                   | SPI0CR1 (SPIE, SPTIE)             |

| Vector base+ \$D6            | \$6B                             | B SCI0                                 |                                   | SCI0CR2<br>(TIE, TCIE, RIE, ILIE) |

| Vector base + \$D4 \$6A SCI1 |                                  | l bit                                  | SCI1CR2<br>(TIE, TCIE, RIE, ILIE) |                                   |

| Vector base + \$D2           | \$69                             | ATD0                                   | l bit                             | ATD0CTL2 (ASCIE)                  |

| Vector base + \$D2           |                                  | Reserved                               | • •                               |                                   |

| Vector base + \$D0           | \$68                             | ATD1                                   | l bit                             | ATD1CTL2 (ASCIE)                  |

| Vector base + \$CE           | \$67                             | Port J                                 | l bit                             | PIEJ (PIEJ7-PIEJ0)                |

| Vector base + \$CC           | base + \$CC \$66 Port H          |                                        | l bit                             | PIEH (PIEH7-PIEH0)                |

| Vector base + \$CA           | \$65                             | Modulus down counter underflow         | l bit                             | MCCTL(MCZI)                       |

| Vector base + \$C8           | \$64                             | Pulse accumulator B overflow           |                                   | PBCTL(PBOVI)                      |

| Vector base + \$C6           | \$63                             | CRG PLL lock I bit CRGINT(             |                                   | CRGINT(LOCKIE)                    |

| Vector base + \$C4           | \$62                             | CRG self-clock mode I bit CRGINT (SCMI |                                   | CRGINT (SCMIE)                    |

| Vector base + \$C2           |                                  | Reserved                               |                                   |                                   |

| Vector base + \$C0           | \$60                             | IIC0 bus                               | I bit                             | IBCR0 (IBIE)                      |

| CD | сс | СВ | СА | Analog Input<br>Channel |

|----|----|----|----|-------------------------|

| 0  | 0  | 0  | 0  | AN0                     |

| 0  | 0  | 0  | 1  | AN1                     |

| 0  | 0  | 1  | 0  | AN2                     |

| 0  | 0  | 1  | 1  | AN3                     |

| 0  | 1  | 0  | 0  | AN4                     |

| 0  | 1  | 0  | 1  | AN5                     |

| 0  | 1  | 1  | 0  | AN6                     |

| 0  | 1  | 1  | 1  | AN7                     |

| 1  | 0  | 0  | 0  | AN8                     |

| 1  | 0  | 0  | 1  | AN9                     |

| 1  | 0  | 1  | 0  | AN10                    |

| 1  | 0  | 1  | 1  | AN11                    |

| 1  | 1  | 0  | 0  | AN12                    |

| 1  | 1  | 0  | 1  | AN13                    |

| 1  | 1  | 1  | 0  | AN14                    |

| 1  | 1  | 1  | 1  | AN15                    |

Table 4-17. Analog Input Channel Select Coding

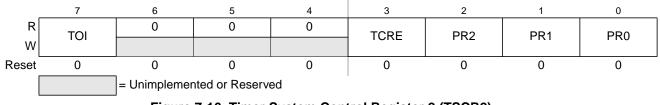

# 7.3.2.11 Timer System Control Register 2 (TSCR2)

Figure 7-16. Timer System Control Register 2 (TSCR2)

Read or write: Anytime

All bits reset to zero.

| Field          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TOI       | Timer Overflow Interrupt Enable         0       Timer overflow interrupt disabled.         1       Hardware interrupt requested when TOF flag set.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3<br>TCRE      | <ul> <li>Timer Counter Reset Enable — This bit allows the timer counter to be reset by a successful channel 7 output compare. This mode of operation is similar to an up-counting modulus counter.</li> <li>0 Counter reset disabled and counter free runs.</li> <li>1 Counter reset by a successful output compare on channel 7.</li> <li>Note: If register TC7 = 0x0000 and TCRE = 1, then the TCNT register will stay at 0x0000 continuously. If register TC7 = 0xFFFF and TCRE = 1, the TOF flag will never be set when TCNT is reset from 0xFFFF to 0x0000.</li> </ul> |

| 2:0<br>PR[2:0] | <b>Timer Prescaler Select</b> — These three bits specify the division rate of the main Timer prescaler when the PRNT bit of register TSCR1 is set to 0. The newly selected prescale factor will not take effect until the next synchronized edge where all prescale counter stages equal zero. See Table 7-15.                                                                                                                                                                                                                                                              |

| PR2 | PR1 | PR0 | Prescale Factor |

|-----|-----|-----|-----------------|

| 0   | 0   | 0   | 1               |

| 0   | 0   | 1   | 2               |

| 0   | 1   | 0   | 4               |

| 0   | 1   | 1   | 8               |

| 1   | 0   | 0   | 16              |

| 1   | 0   | 1   | 32              |

| 1   | 1   | 0   | 64              |

| 1   | 1   | 1   | 128             |

### Table 7-15. Prescaler Selection

# 7.4.1 Enhanced Capture Timer Modes of Operation

The enhanced capture timer has 8 input capture, output compare (IC/OC) channels, same as on the HC12 standard timer (timer channels TC0 to TC7). When channels are selected as input capture by selecting the IOSx bit in TIOS register, they are called input capture (IC) channels.

Four IC channels (channels 7–4) are the same as on the standard timer with one capture register each that memorizes the timer value captured by an action on the associated input pin.

Four other IC channels (channels 3–0), in addition to the capture register, also have one buffer each called a holding register. This allows two different timer values to be saved without generating any interrupts.

Four 8-bit pulse accumulators are associated with the four buffered IC channels (channels 3–0). Each pulse accumulator has a holding register to memorize their value by an action on its external input. Each pair of pulse accumulators can be used as a 16-bit pulse accumulator.

The 16-bit modulus down-counter can control the transfer of the IC registers and the pulse accumulators contents to the respective holding registers for a given period, every time the count reaches zero.

The modulus down-counter can also be used as a stand-alone time base with periodic interrupt capability.

# 7.4.1.1 IC Channels

The IC channels are composed of four standard IC registers and four buffered IC channels.

- An IC register is empty when it has been read or latched into the holding register.

- A holding register is empty when it has been read.

### 7.4.1.1.1 Non-Buffered IC Channels

The main timer value is memorized in the IC register by a valid input pin transition. If the corresponding NOVWx bit of the ICOVW register is cleared, with a new occurrence of a capture, the contents of IC register are overwritten by the new value. If the corresponding NOVWx bit of the ICOVW register is set, the capture register cannot be written unless it is empty. This will prevent the captured value from being overwritten until it is read.

### 7.4.1.1.2 Buffered IC Channels

There are two modes of operations for the buffered IC channels:

1. IC latch mode (LATQ = 1)

The main timer value is memorized in the IC register by a valid input pin transition (see Figure 7-65 and Figure 7-66).

The value of the buffered IC register is latched to its holding register by the modulus counter for a given period when the count reaches zero, by a write 0x0000 to the modulus counter or by a write to ICLAT in the MCCTL register.

If the corresponding NOVWx bit of the ICOVW register is cleared, with a new occurrence of a capture, the contents of IC register are overwritten by the new value. In case of latching, the contents of its holding register are overwritten.

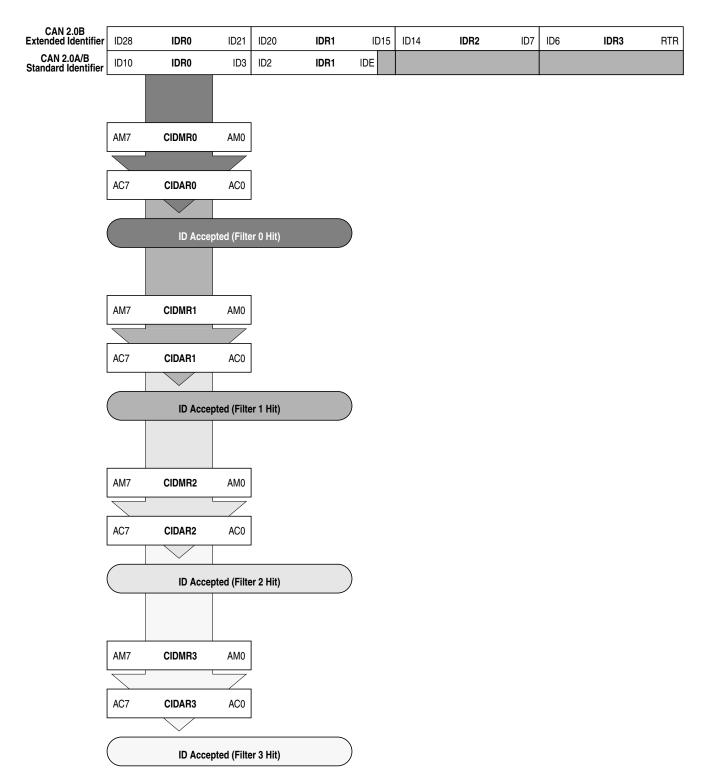

#### Chapter 10 Freescale's Scalable Controller Area Network (S12MSCANV3)

Figure 10-42. 8-bit Maskable Identifier Acceptance Filters

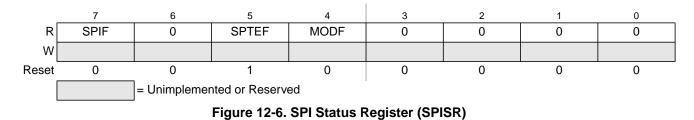

# 12.3.2.4 SPI Status Register (SPISR)

### Read: Anytime

### Write: Has no effect

| Table 12-7. | SPISR | Field | Descriptions |

|-------------|-------|-------|--------------|

|             |       |       |              |

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>SPIF  | <ul> <li>SPIF Interrupt Flag — This bit is set after a received data byte has been transferred into the SPI data register. This bit is cleared by reading the SPISR register (with SPIF set) followed by a read access to the SPI data register.</li> <li>0 Transfer not yet complete.</li> <li>1 New data copied to SPIDR.</li> </ul>                                                                                                                                                                         |

| 5<br>SPTEF | <ul> <li>SPI Transmit Empty Interrupt Flag — If set, this bit indicates that the transmit data register is empty. To clear this bit and place data into the transmit data register, SPISR must be read with SPTEF = 1, followed by a write to SPIDR. Any write to the SPI data register without reading SPTEF = 1, is effectively ignored.</li> <li>0 SPI data register not empty.</li> <li>1 SPI data register empty.</li> </ul>                                                                              |

| 4<br>MODF  | <ul> <li>Mode Fault Flag — This bit is set if the SS input becomes low while the SPI is configured as a master and mode fault detection is enabled, MODFEN bit of SPICR2 register is set. Refer to MODFEN bit description in Section 12.3.2.2, "SPI Control Register 2 (SPICR2)". The flag is cleared automatically by a read of the SPI status register (with MODF set) followed by a write to the SPI control register 1.</li> <li>Mode fault has not occurred.</li> <li>Mode fault has occurred.</li> </ul> |

#### Chapter 15 Background Debug Module (S12XBDMV2)

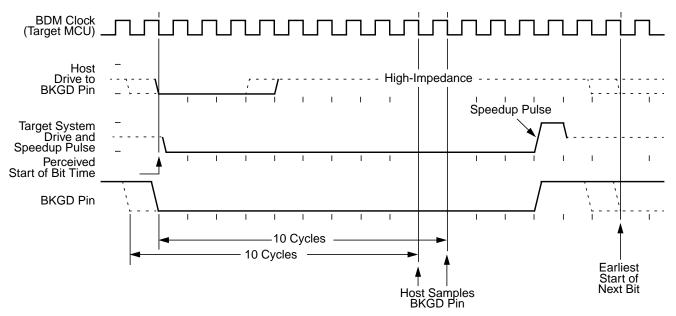

Figure 15-10 shows the host receiving a logic 0 from the target. Since the host is asynchronous to the target, there is up to a one clock-cycle delay from the host-generated falling edge on BKGD to the start of the bit time as perceived by the target. The host initiates the bit time but the target finishes it. Since the target wants the host to receive a logic 0, it drives the BKGD pin low for 13 target clock cycles then briefly drives it high to speed up the rising edge. The host samples the bit level about 10 target clock cycles after starting the bit time.

Figure 15-10. BDM Target-to-Host Serial Bit Timing (Logic 0)

# 15.4.7 Serial Interface Hardware Handshake Protocol

BDM commands that require CPU execution are ultimately treated at the MCU bus rate. Since the BDM clock source can be asynchronously related to the bus frequency, when CLKSW = 0, it is very helpful to provide a handshake protocol in which the host could determine when an issued command is executed by the CPU. The alternative is to always wait the amount of time equal to the appropriate number of cycles at the slowest possible rate the clock could be running. This sub-section will describe the hardware handshake protocol.

The hardware handshake protocol signals to the host controller when an issued command was successfully executed by the target. This protocol is implemented by a 16 serial clock cycle low pulse followed by a brief speedup pulse in the BKGD pin. This pulse is generated by the target MCU when a command, issued by the host, has been successfully executed (see Figure 15-11). This pulse is referred to as the ACK pulse. After the ACK pulse has finished: the host can start the bit retrieval if the last issued command was a read command, or start a new command if the last command was a write command or a control command (BACKGROUND, GO, GO\_UNTIL or TRACE1). The ACK pulse is not issued earlier than 32 serial clock cycles after the BDM command was issued. The end of the BDM command is assumed to be the 16th tick of the last bit. This minimum delay assures enough time for the host to perceive the ACK pulse. Note also that, there is no upper limit for the delay between the command and the related ACK pulse, since the command execution depends upon the CPU bus frequency, which in some cases could be very slow

Due to internal visibility of CPU accesses the CPU will be halted during XGATE or BDM access to any PRR. This rule applies also in normal modes to ensure that operation of the device is the same as in emulation modes.

A summary of PRR accesses is the following:

- An aligned word access to a PRR will take 2 bus cycles.

- A misaligned word access to a PRRs will take 4 cycles. If one of the two bytes accessed by the misaligned word access is not a PRR, the access will take only 3 cycles.

- A byte access to a PRR will take 2 cycles.

| PRR Name | PRR Local Address | PRR Location |

|----------|-------------------|--------------|

| PORTA    | \$0000            | PIM          |

| PORTB    | \$0001            | PIM          |

| DDRA     | \$0002            | PIM          |

| DDRB     | \$0003            | PIM          |

| PORTC    | \$0004            | PIM          |

| PORTD    | \$0005            | PIM          |

| DDRC     | \$0006            | PIM          |

| DDRD     | \$0007            | PIM          |

| PORTE    | \$0008            | PIM          |

| DDRE     | \$0009            | PIM          |

| MMCCTL0  | \$000A            | MMC          |

| MODE     | \$000B            | MMC          |

| PUCR     | \$000C            | PIM          |

| RDRIV    | \$000D            | PIM          |

| EBICTL0  | \$000E            | EBI          |

| EBICTL1  | \$000F            | EBI          |

| Reserved | \$0012            | MMC          |

| MMCCTL1  | \$0013            | MMC          |

| ECLKCTL  | \$001C            | PIM          |

| Reserved | \$001D            | PIM          |

| PORTK    | \$0032            | PIM          |

| DDRK     | \$0033            | PIM          |

Table 17-22. PRR Listing

I

| Field | Description                                                                                                                                                           |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>Program Page Index Bits 7–0</b> — These page index bits are used to select which of the 256 FLASH or ROM array pages is to be accessed in the Program Page Window. |

#### Table 18-14. PPAGE Field Descriptions

The fixed 16K page from 0x4000-0x7FFF (when ROMHM = 0) is the page number 0xFD.

The reset value of 0xFE ensures that there is linear Flash space available between addresses 0x4000 and 0xFFFF out of reset.

The fixed 16K page from 0xC000-0xFFFF is the page number 0xFF.

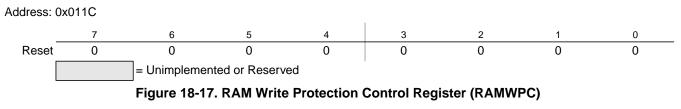

# **18.3.2.9** RAM Write Protection Control Register (RAMWPC)

Read: Anytime

Write: Anytime

### Table 18-15. RAMWPC Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>RWPE | <ul> <li>RAM Write Protection Enable — This bit enables the RAM write protection mechanism. When the RWPE bit is cleared, there is no write protection and any memory location is writable by the CPU module and the XGATE module. When the RWPE bit is set the write protection mechanism is enabled and write access of the CPU or to the XGATE RAM region. Write access performed by the XGATE module to outside of the XGATE RAM region or the shared region is suppressed as well in this case.</li> <li>RAM write protection check is disabled, region boundary registers can be written.</li> <li>RAM write protection check is enabled, region boundary registers cannot be written.</li> </ul> |

| 1<br>AVIE | <ul> <li>CPU Access Violation Interrupt Enable — This bit enables the Access Violation Interrupt. If AVIE is set and AVIF is set, an interrupt is generated.</li> <li>0 CPU Access Violation Interrupt Disabled.</li> <li>1 CPU Access Violation Interrupt Enabled.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0<br>AVIF | <ul> <li>CPU Access Violation Interrupt Flag — When set, this bit indicates that the CPU has tried to write a memory location inside the XGATE RAM region. This flag can be reset by writing '1' to the AVIF bit location.</li> <li>0 No access violation by the CPU was detected.</li> <li>1 Access violation by the CPU was detected.</li> </ul>                                                                                                                                                                                                                                                                                                                                                      |

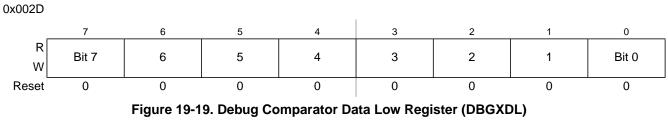

### 19.3.1.11.6 Debug Comparator Data Low Register (DBGXDL)

### Read: Anytime

Write: Anytime when DBG not armed.

#### Table 19-33. DBGXDL Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–0<br>Bits [7:0] | <ul> <li>Comparator Data Low Compare Bits — The comparator data low compare bits control whether the selected comparator compares the data bus bits [7:0] to a logic 1 or logic 0. The comparator data compare bits are only used in comparison if the corresponding data mask bit is logic 1. This register is available only for comparators A and C.</li> <li>0 Compare corresponding data bit to a logic 0</li> <li>1 Compare corresponding data bit to a logic 1</li> </ul> |

### 19.3.1.11.7 Debug Comparator Data High Mask Register (DBGXDHM)

### Figure 19-20. Debug Comparator Data High Mask Register (DBGXDHM)

### Read: Anytime

Write: Anytime when DBG not armed.

### Table 19-34. DBGXDHM Field Descriptions

| Field              | Description                                                                                                                                                                                                                                                                                                                          |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–0<br>Bits [15:8] | Comparator Data High Mask Bits — The comparator data high mask bits control whether the selected<br>comparator compares the data bus bits [15:8] to the corresponding comparator data compare bits. This register<br>is available only for comparators A and C.0Do not compare corresponding data bit1Compare corresponding data bit |

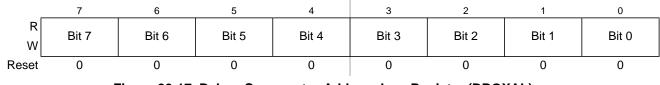

### 20.3.2.8.4 Debug Comparator Address Low Register (DBGXAL)

Address: 0x002B

Figure 20-17. Debug Comparator Address Low Register (DBGXAL)

Read: Anytime

Write: Anytime when S12XDBG not armed.

### Table 20-31. DBGXAL Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                              |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–0<br>Bits[7:0] | <ul> <li>Comparator Address Low Compare Bits — The Comparator address low compare bits control whether the selected comparator will compare the address bus bits [7:0] to a logic one or logic zero.</li> <li>0 Compare corresponding address bit to a logic zero</li> <li>1 Compare corresponding address bit to a logic one</li> </ul> |

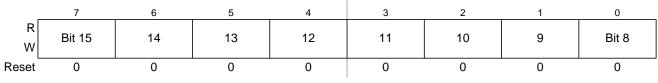

### 20.3.2.8.5 Debug Comparator Data High Register (DBGXDH)

Address: 0x002C

|        | 7      | 6      | 5      | 4      | 3      | 2      | 1     | 0     |

|--------|--------|--------|--------|--------|--------|--------|-------|-------|

| R<br>W | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 |

| Reset  | 0      | 0      | 0      | 0      | 0      | 0      | 0     | 0     |

### Figure 20-18. Debug Comparator Data High Register (DBGXDH)

### Read: Anytime

Write: Anytime when S12XDBG not armed.

### Table 20-32. DBGXAH Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 7–0<br>Bits[15:8] | <ul> <li>Comparator Data High Compare Bits — The Comparator data high compare bits control whether the selected comparator compares the data bus bits [15:8] to a logic one or logic zero. The comparator data compare bits are only used in comparison if the corresponding data mask bit is logic 1. This register is available only for comparators A and C.</li> <li>0 Compare corresponding data bit to a logic zero</li> <li>1 Compare corresponding data bit to a logic one</li> </ul> |  |  |  |  |  |  |  |  |

# 23.0.5.15 Port K Data Register (PORTK)

| _             | 7                     | 6                      | 5      | 4      | 3                        | 2                        | 1                        | 0                        |

|---------------|-----------------------|------------------------|--------|--------|--------------------------|--------------------------|--------------------------|--------------------------|

| R<br>W        | PK7                   | PK6                    | PK5    | PK4    | PK3                      | PK2                      | PK1                      | PK0                      |

| Alt.<br>Func. | ROMCTL<br>or<br>EWAIT | ADDR22<br>mux<br>NOACC | ADDR21 | ADDR20 | ADDR19<br>mux<br>IQSTAT3 | ADDR18<br>mux<br>IQSTAT2 | ADDR17<br>mux<br>IQSTAT1 | ADDR16<br>mux<br>IQSTAT0 |

| Reset         | 0                     | 0                      | 0      | 0      | 0                        | 0                        | 0                        | 0                        |

### Figure 23-17. Port K Data Register (PORTK)

Read: Anytime. In emulation modes, read operations will return the data from the external bus, in all other modes the data source is depending on the data direction value.

Write: Anytime. In emulation modes, write operations will also be directed to the external bus.

### Table 23-19. PORTK Field Descriptions

| Field          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 7–0<br>PK[7:0] | Port K — Port K pins 7–0 are associated with external bus control signals and internal memory expansion emulation pins. These include ADDR22-ADDR16, No-Access (NOACC), External Wait (EWAIT) and instruction pipe signals IQSTAT3-IQSTAT0. Bits 6-0 carry the external addresses in all expanded modes. In emulation or special test mode with internal visibility enabled the address is multiplexed with the alternate functions NOACC and IQSTAT on the respective pins. In single-chip modes the port pins can be used as general-purpose I/O. If the data direction bits of the associated I/O pins are set to logic level "1", a read returns the value of the port register, otherwise the buffered pin input state is read. |  |  |  |  |  |  |  |  |

# 23.0.5.16 Port K Data Direction Register (DDRK)

| _      | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| R<br>W | DDRK7 | DDRK6 | DDRK5 | DDRK4 | DDRK3 | DDRK2 | DDRK1 | DDRK0 |

| Reset  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

### Figure 23-18. Port K Data Direction Register (DDRK)

Read: Anytime. In emulation modes, read operations will return the data from the external bus, in all other modes the data source is depending on the data direction value.

Write: Anytime. In emulation modes, write operations will also be directed to the external bus.

This register controls the data direction for port K. When Port K is operating as a general purpose I/O port, DDRK determines whether each pin is an input or output. A logic level "1" causes the associated port pin to be an output and a logic level "0" causes the associated pin to be a high-impedance input.

| Field         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–0 <b>Po</b> | Polarity Select Port P                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1             | Falling edge on the associated port P pin sets the associated flag bit in the PIFP register. A pull-up device is connected to the associated port P pin, if enabled by the associated bit in register PERP and if the port is used as input.<br>Rising edge on the associated port P pin sets the associated flag bit in the PIFP register. A pull-down device is connected to the associated port P pin, if enabled by the associated bit in register PERP and if the port is used as input. |

### Table 23-42. PPSP Field Descriptions

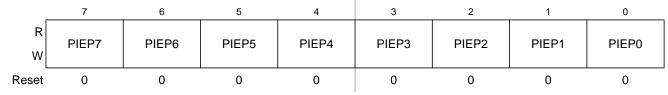

# 23.0.5.44 Port P Interrupt Enable Register (PIEP)

Figure 23-46. Port P Interrupt Enable Register (PIEP)

Read: Anytime.

Write: Anytime.

This register disables or enables on a per-pin basis the edge sensitive external interrupt associated with Port P.

| Field     | Description                                      |

|-----------|--------------------------------------------------|

| 7–0       | Interrupt Enable Port P                          |

| PIEP[7:0] | 0 Interrupt is disabled (interrupt flag masked). |

|           | 1 Interrupt is enabled.                          |

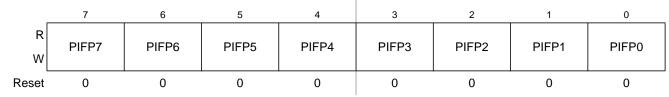

# 23.0.5.45 Port P Interrupt Flag Register (PIFP)

Figure 23-47. Port P Interrupt Flag Register (PIFP)

Read: Anytime.

Write: Anytime.

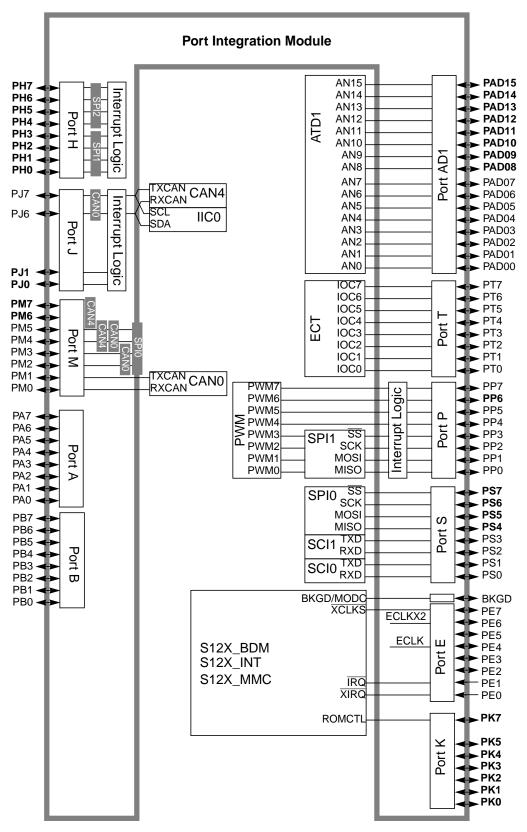

Figure 24-1. PIM\_9XDG128 Block Diagram

Chapter 24 DG128 Port Integration Module (S12XDG128PIMV2)

| Register<br>Name |        | Bit 7 | 6           | 5              | 4     | 3     | 2     | 1     | Bit 0 |

|------------------|--------|-------|-------------|----------------|-------|-------|-------|-------|-------|

| PTIP             | R      | PTIP7 | PTIP6       | PTIP5          | PTIP4 | PTIP3 | PTIP2 | PTIP1 | PTIP0 |

|                  | W      |       |             |                |       |       |       |       |       |

| DDRP             | R<br>W | DDRP7 | DDRP6       | DDRP5          | DDRP4 | DDRP3 | DDRP2 | DDRP1 | DDRP0 |

| RDRP             | R<br>W | RDRP7 | RDRP6       | RDRP5          | RDRP4 | RDRP3 | RDRP2 | RDRP1 | RDRP0 |

| PERP             | R<br>W | PERP7 | PERP6       | PERP5          | PERP4 | PERP3 | PERP2 | PERP1 | PERP0 |

| PPSP             | R<br>W | PPSP7 | PPSP6       | PPSP5          | PPSP4 | PPSP3 | PPSP2 | PPSP1 | PPSP0 |

| PIEP             | R<br>W | PIEP7 | PIEP6       | PIEP5          | PIEP4 | PIEP3 | PIEP2 | PIEP1 | PIEP0 |

| PIFP             | R<br>W | PIFP7 | PIFP6       | PIFP5          | PIFP4 | PIFP3 | PIFP2 | PIFP1 | PIFP0 |

| PTH              | R<br>W | PTH7  | PTH6        | PTH5           | PTH4  | PTH3  | PTH2  | PTH1  | PTH0  |

| PTIH             | R      | PTIH7 | PTIH6       | PTIH5          | PTIH4 | PTIH3 | PTIH2 | PTIH1 | PTIH0 |

|                  | w      |       |             |                |       |       |       |       |       |

| DDRH             | R<br>W | DDRH7 | DDRH6       | DDRH5          | DDRH4 | DDRH3 | DDRH2 | DDRH1 | DDRH0 |

| RDRH             | R<br>W | RDRH7 | RDRH6       | RDRH5          | RDRH4 | RDRH3 | RDRH2 | RDRH1 | RDRH0 |

| PERH             | R<br>W | PERH7 | PERH6       | PERH5          | PERH4 | PERH3 | PERH2 | PERH1 | PERH0 |

| PPSH             | R<br>W | PPSH7 | PPSH6       | PPSH5          | PPSH4 | PPSH3 | PPSH2 | PPSH1 | PPSH0 |

| PIEH             | R<br>W | PIEH7 | PIEH6       | PIEH5          | PIEH4 | PIEH3 | PIEH2 | PIEH1 | PIEH0 |

| PIFH             | R<br>W | PIFH7 | PIFH6       | PIFH5          | PIFH4 | PIFH3 | PIFH2 | PIFH1 | PIFH0 |

|                  |        |       | = Unimpleme | ented or Reser | ved   |       |       |       |       |

### Figure 24-2. PIM Register Summary (Sheet 5 of 7)

#### Chapter 24 DG128 Port Integration Module (S12XDG128PIMV2)

| Field           | Description                                                                                                                                                                                              |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3–2<br>PTM[3:2] | The routed CAN0 function (TXCAN0 and RXCAN0) takes precedence over the routed SPI0 and the general purpose I/O function if the routed CAN0 module is enabled. <i>Refer to MSCAN section for details.</i> |

|                 | The routed SPI0 function (SS0 and MISO0) takes precedence of the general purpose I/O function if the routed SPI0 is enabled and not in bidirectional mode. <i>Refer to SPI section for details.</i>      |

| 1–0<br>PTM[1:0] | The CAN0 function (TXCAN0 and RXCAN0) takes precedence over the general purpose I/O function if the CAN0 module is enabled. <i>Refer to MSCAN section for details.</i>                                   |

### Table 24-28. PTM Field Descriptions (continued)

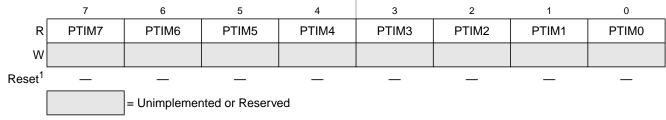

# 24.0.5.27 Port M Input Register (PTIM)

### Figure 24-29. Port M Input Register (PTIM)

1. These registers are reset to zero. Two bus clock cycles after reset release the register values are updated with the associated pin values.

Read: Anytime.

Write: Never, writes to this register have no effect.

This register always reads back the buffered state of the associated pins. This can also be used to detect overload or short circuit conditions on output pins.

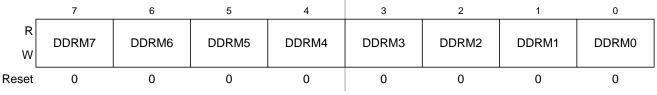

# 24.0.5.28 Port M Data Direction Register (DDRM)

Figure 24-30. Port M Data Direction Register (DDRM)

Read: Anytime.

Write: Anytime.

This register configures each port M pin as either input or output.

The CAN forces the I/O state to be an output for each port line associated with an enabled output (TXCAN). It also forces the I/O state to be an input for each port line associated with an enabled input (RXCAN). In those cases the data direction bits will not change.

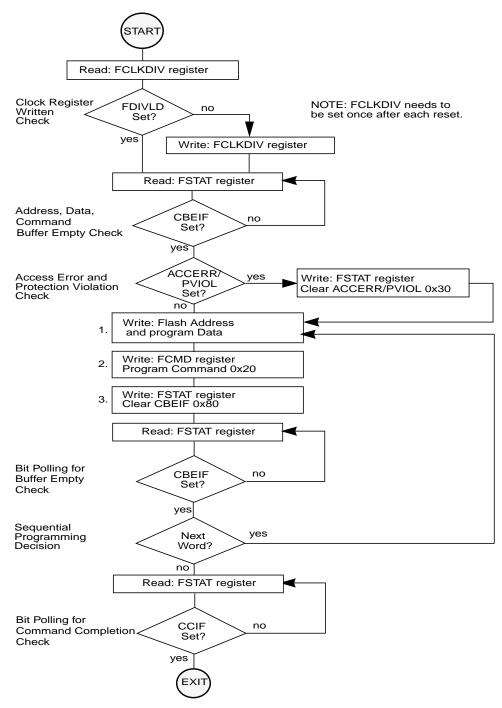

# 25.4.2.2 Program Command

The program operation will program a previously erased word in the EEPROM memory using an embedded algorithm.

An example flow to execute the program operation is shown in Figure 25-19. The program command write sequence is as follows:

- 1. Write to an EEPROM block address to start the command write sequence for the program command. The data written will be programmed to the address written.

- 2. Write the program command, 0x20, to the ECMD register.

- 3. Clear the CBEIF flag in the ESTAT register by writing a 1 to CBEIF to launch the program command.

If a word to be programmed is in a protected area of the EEPROM memory, the PVIOL flag in the ESTAT register will set and the program command will not launch. Once the program command has successfully launched, the CCIF flag in the ESTAT register will set after the program operation has completed unless a new command write sequence has been buffered.

Chapter 28 256 Kbyte Flash Module (S12XFTX256K2V1)

- Security feature to prevent unauthorized access to the Flash memory

- Code integrity check using built-in data compression

# 28.1.3 Modes of Operation

Program, erase, erase verify, and data compress operations (please refer to Section 28.4.1, "Flash Command Operations" for details).

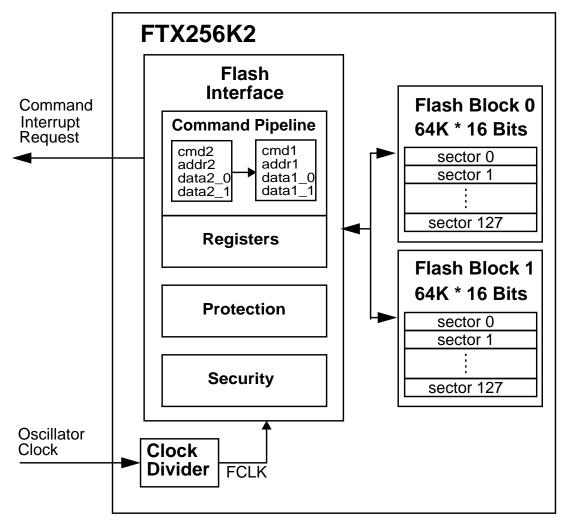

# 28.1.4 Block Diagram

A block diagram of the Flash module is shown in Figure 28-1.

Figure 28-1. FTX256K2 Block Diagram

# 28.2 External Signal Description

The Flash module contains no signals that connect off-chip.

Figure 29-26. Example Program Command Flow

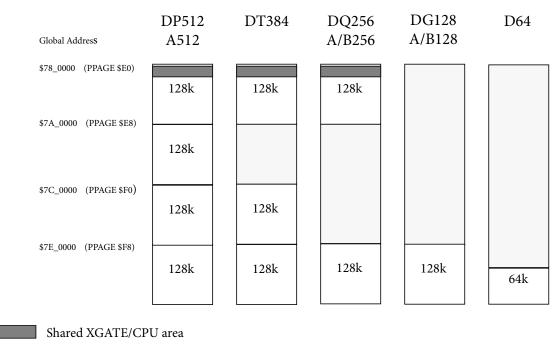

# E.3 MC9S12XD-Family Flash Configuration<sup>1 2 3 4 5</sup>

Figure E-1. MC9S12XD Family Flash Configuration

Not implemented

<sup>1.</sup> XGATE read access to Flash not possible on DG128/D128/A128/B128 and D64

<sup>2.</sup> Program Pages available on DT384 are \$E0 - \$E7 and \$F0 - \$FF

<sup>3.</sup> Program Pages available on B256/A256/DQ256/DT256/D256 are \$E0 - \$E7 and \$F8 - \$FF

<sup>4.</sup> Shared XGATE/CPU area on A512/DP512/DT512/DT384 at global address \$78\_0800 to \$78\_7FFF (30Kbyte)

<sup>5.</sup> Shared XGATE/CPU area on A256/B256/DT256/DQ256/D256 at global address \$78\_0800 to \$78\_7FFF (30Kbyte)