Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | HCS12X                                                                  |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 80MHz                                                                   |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, SCI, SPI                             |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 119                                                                     |

| Program Memory Size        | 256KB (256K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 4K x 8                                                                  |

| RAM Size                   | 16K × 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 5.5V                                                            |

| Data Converters            | A/D 8x10b, 16x10b                                                       |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 144-LQFP                                                                |

| Supplier Device Package    | 144-LQFP (20x20)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s912xdq256f1mag |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- 10-bit resolution

- External and internal conversion trigger capabilityFiveFourTwo 1M bit per second, CAN 2.0 A, B software compatible modules

- Five receive and three transmit buffers

- Flexible identifier filter programmable as 2 x 32 bit, 4 x 16 bit, or 8 x 8 bit

- Four separate interrupt channels for Rx, Tx, error, and wake-up

- Low-pass filter wake-up function

- Loop-back for self-test operation

- ECT (enhanced capture timer)

- 16-bit main counter with 7-bit prescaler

- 8 programmable input capture or output compare channels

- Four 8-bit or two 16-bit pulse accumulators

- 8 PWM (pulse-width modulator) channels

- Programmable period and duty cycle

- 8-bit 8-channel or 16-bit 4-channel

- Separate control for each pulse width and duty cycle

- Center-aligned or left-aligned outputs

- Programmable clock select logic with a wide range of frequencies

- Fast emergency shutdown input

- Serial interfaces

- SixFourTwo asynchronous serial communication interfaces (SCI) with additional LIN support and selectable IrDA 1.4 return-to-zero-inverted (RZI) format with programmable pulse width

- ThreeTwo Synchronous Serial Peripheral Interfaces (SPI)

- TwoOne IIC (Inter-IC bus) Modules

- Compatible with IIC bus standard

- Multi-master operation

- Software programmable for one of 256 different serial clock frequencies

- On-Chip Voltage Regulator

- Two parallel, linear voltage regulators with bandgap reference

- Low-voltage detect (LVD) with low-voltage interrupt (LVI)

- Power-on reset (POR) circuit

- 3.3-V–5.5-V operation

- Low-voltage reset (LVR)

- Ultra low-power wake-up timer

- 144-pin LQFP, 112-pin LQFP, and 80-pin QFP packages

- I/O lines with 5-V input and drive capability

- Input threshold on external bus interface inputs switchable for 3.3-V or 5-V operation

- 5-V A/D converter inputs

- Operation at 80 MHz equivalent to 40-MHz bus speed

# 1.6.2 Effects of Reset

When a reset occurs, MCU registers and control bits are changed to known start-up states. Refer to the respective module Block Guides for register reset states.

## 1.6.2.1 I/O Pins

Refer to the PIM Block Guide for reset configurations of all peripheral module ports.

## 1.6.2.2 Memory

The RAM array is not initialized out of reset.

# **1.7 COP Configuration**

The COP timeout rate bits CR[2:0] and the WCOP bit in the COPCTL register are loaded on rising edge of RESET from the Flash control register FCTL (\$0107) located in the Flash EEPROM block. See Table 1-13 and Table 1-14 for coding. The FCTL register is loaded from the Flash configuration field byte at global address \$7FFF0E during the reset sequence

## NOTE

If the MCU is secured the COP timeout rate is always set to the longest period (CR[2:0] = 111) after COP reset.

| NV[2:0] in<br>FCTL Register | CR[2:0] in<br>COPCTL Register |

|-----------------------------|-------------------------------|

| 000                         | 111                           |

| 001                         | 110                           |

| 010                         | 101                           |

| 011                         | 100                           |

| 100                         | 011                           |

| 101                         | 010                           |

| 110                         | 001                           |

| 111                         | 000                           |

### Table 1-13. Initial COP Rate Configuration

#### Table 1-14. Initial WCOP Configuration

| NV[3] in<br>FCTL Register | WCOP in<br>COPCTL Register |

|---------------------------|----------------------------|

| 1                         | 0                          |

| 0                         | 1                          |

Chapter 4 Analog-to-Digital Converter (ATD10B16CV4) Block Description

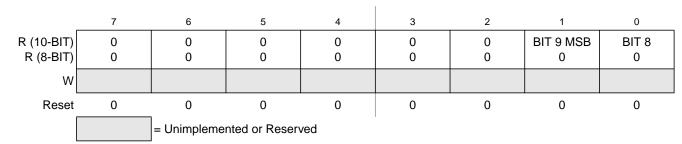

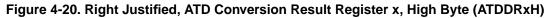

4.3.2.16.2 Right Justified Result Data

Figure 4-21. Right Justified, ATD Conversion Result Register x, Low Byte (ATDDRxL)

# 4.4 Functional Description

The ATD10B16C is structured in an analog and a digital sub-block.

# 4.4.1 Analog Sub-block

The analog sub-block contains all analog electronics required to perform a single conversion. Separate power supplies  $V_{DDA}$  and  $V_{SSA}$  allow to isolate noise of other MCU circuitry from the analog sub-block.

# 4.4.1.1 Sample and Hold Machine

The sample and hold (S/H) machine accepts analog signals from the external world and stores them as capacitor charge on a storage node.

The sample process uses a two stage approach. During the first stage, the sample amplifier is used to quickly charge the storage node. The second stage connects the input directly to the storage node to complete the sample for high accuracy.

When not sampling, the sample and hold machine disables its own clocks. The analog electronics continue drawing their quiescent current. The power down (ADPU) bit must be set to disable both the digital clocks and the analog power consumption.

The input analog signals are unipolar and must fall within the potential range of  $V_{SSA}$  to VDDA.

#### Chapter 4 Analog-to-Digital Converter (ATD10B16CV4) Block Description

In either level or edge triggered modes, the first conversion begins when the trigger is received. In both cases, the maximum latency time is one bus clock cycle plus any skew or delay introduced by the trigger circuitry.

After ETRIGE is enabled, conversions cannot be started by a write to ATDCTL5, but rather must be triggered externally.

If the level mode is active and the external trigger both de-asserts and re-asserts itself during a conversion sequence, this does not constitute an overrun. Therefore, the flag is not set. If the trigger remains asserted in level mode while a sequence is completing, another sequence will be triggered immediately.

# 4.4.2.2 General-Purpose Digital Input Port Operation

The input channel pins can be multiplexed between analog and digital data. As analog inputs, they are multiplexed and sampled to supply signals to the A/D converter. As digital inputs, they supply external input data that can be accessed through the digital port registers (PORTAD0 & PORTAD1) (input-only).

The analog/digital multiplex operation is performed in the input pads. The input pad is always connected to the analog inputs of the ATD10B16C. The input pad signal is buffered to the digital port registers. This buffer can be turned on or off with the ATDDIEN0 & ATDDIEN1 register. This is important so that the buffer does not draw excess current when analog potentials are presented at its input.

# 4.4.3 Operation in Low Power Modes

The ATD10B16C can be configured for lower MCU power consumption in three different ways:

• Stop Mode

Stop Mode: This halts A/D conversion. Exit from Stop mode will resume A/D conversion, But due to the recovery time the result of this conversion should be ignored.

Entering stop mode causes all clocks to halt and thus the system is placed in a minimum power standby mode. This halts any conversion sequence in progress. During recovery from stop mode, there must be a minimum delay for the stop recovery time  $t_{SR}$  before initiating a new ATD conversion sequence.

## • Wait Mode

Wait Mode with AWAI = 1: This halts A/D conversion. Exit from Wait mode will resume A/D conversion, but due to the recovery time the result of this conversion should be ignored. Entering wait mode, the ATD conversion either continues or halts for low power depending on the logical value of the AWAIT bit.

• Freeze Mode

Writing ADPU = 0 (Note that all ATD registers remain accessible.): This aborts any A/D conversion in progress.

In freeze mode, the ATD10B16C will behave according to the logical values of the FRZ1 and FRZ0 bits. This is useful for debugging and emulation.

## NOTE

The reset value for the ADPU bit is zero. Therefore, when this module is reset, it is reset into the power down state.

#### MC9S12XDP512 Data Sheet, Rev. 2.21

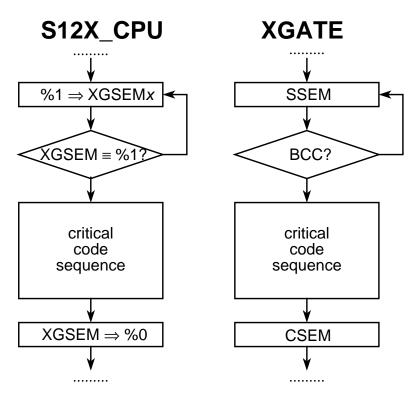

Figure 6-22 gives an example of the typical usage of the XGATE hardware semaphores.

Two concurrent threads are running on the system. One is running on the S12X\_CPU and the other is running on the RISC core. They both have a critical section of code that accesses the same system resource. To guarantee that the system resource is only accessed by one thread at a time, the critical code sequence must be embedded in a semaphore lock/release sequence as shown.

Figure 6-22. Algorithm for Locking and Releasing Semaphores

# 6.4.5 Software Error Detection

The XGATE module will immediately terminate program execution after detecting an error condition caused by erratic application code. There are three error conditions:

- Execution of an illegal opcode

- Illegal vector or opcode fetches

- Illegal load or store accesses

All opcodes which are not listed in section Section 6.8, "Instruction Set" are illegal opcodes. Illegal vector and opcode fetches as well as illegal load and store accesses are defined on chip level. Refer to the **S12X\_MMC Section** for a detailed information.

# ANDH

## Logical AND Immediate 8 bit Constant (High Byte)

## Operation

$RD.H \& IMM8 \Rightarrow RD.H$

Performs a bit wise logical AND between the high byte of register RD and an immediate 8 bit constant and stores the result in the destination register RD.H. The low byte of RD is not affected.

## **CCR Effects**

| Ν | Ζ | V | С |

|---|---|---|---|

|   |   |   |   |

| Δ | Δ | 0 | — |

|---|---|---|---|

|---|---|---|---|

- N: Set if bit 15 of the result is set; cleared otherwise.

- Z: Set if the 8 bit result is \$00; cleared otherwise.

- V: 0; cleared.

- C: Not affected.

## Code and CPU Cycles

| Source Form    | Address<br>Mode |   | Machine Code |   |   |   |    |      | Cycles |

|----------------|-----------------|---|--------------|---|---|---|----|------|--------|

| ANDH RD, #IMM8 | IMM8            | 1 | 0            | 0 | 0 | 1 | RD | IMM8 | Р      |

# BCC

Branch if Carry Cleared (Same as BHS)

## Operation

If C = 0, then PC +  $0002 + (REL9 \le 1) \Rightarrow PC$

Tests the Carry flag and branches if C = 0.

## **CCR Effects**

| Ν | Ζ | V | С |

|---|---|---|---|

|   |   |   |   |

- N: Not affected.

- Z: Not affected.

- V: Not affected.

- C: Not affected.

## Code and CPU Cycles

| Source Form | Address<br>Mode |   | Machine Code |   |   |   |   |   | Cycles |      |

|-------------|-----------------|---|--------------|---|---|---|---|---|--------|------|

| BCC REL9    | REL9            | 0 | 0            | 1 | 0 | 0 | 0 | 0 | REL9   | PP/P |

# 7.3.2.2 Timer Compare Force Register (CFORC)

|       | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-------|------|------|------|------|------|------|------|------|

| R     | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| W     | FOC7 | FOC6 | FOC5 | FOC4 | FOC3 | FOC2 | FOC1 | FOC0 |

| Reset | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

#### Figure 7-4. Timer Compare Force Register (CFORC)

Read or write: Anytime but reads will always return 0x0000 (1 state is transient).

All bits reset to zero.

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>FOC[7:0] | <ul> <li>Force Output Compare Action for Channel 7:0 — A write to this register with the corresponding data bit(s) set causes the action which is programmed for output compare "x" to occur immediately. The action taken is the same as if a successful comparison had just taken place with the TCx register except the interrupt flag does not get set.</li> <li>Note: A successful channel 7 output compare overrides any channel 6:0 compares. If a forced output compare on any channel occurs at the same time as the successful output compare, then the forced output compare action will take precedence and the interrupt flag will not get set.</li> </ul> |

# 7.3.2.3 Output Compare 7 Mask Register (OC7M)

| _      | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| R<br>W | OC7M7 | OC7M6 | OC7M5 | OC7M4 | OC7M3 | OC7M2 | OC7M1 | OC7M0 |

| Reset  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Figure 7-5. Output Compare 7 Mask Register (OC7M)

Read or write: Anytime

All bits reset to zero.

#### Table 7-4. OC7M Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>OC7M[7:0] | <ul> <li>Output Compare Mask Action for Channel 7:0</li> <li>The corresponding OC7Dx bit in the output compare 7 data register will not be transferred to the timer port on a successful channel 7 output compare, even if the corresponding pin is setup for output compare.</li> <li>The corresponding OC7Dx bit in the output compare 7 data register will be transferred to the timer port on a successful channel 7 output compare.</li> <li>Note: The corresponding channel must also be setup for output compare (IOSx = 1) for data to be transferred from the output compare 7 data register to the timer port.</li> </ul> |

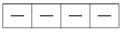

Figure 17-23. Local to Implemented Global Address Mapping (Without GPAGE)

MC9S12XDP512 Data Sheet, Rev. 2.21

I

#### Chapter 20 S12X Debug (S12XDBGV3) Module

| DBGBRK[1]<br>(DBGC1[3]) | BDM Bit<br>(DBGC1[4]) | BDM<br>Enabled | BDM<br>Active | S12X Breakpoint<br>Mapping |

|-------------------------|-----------------------|----------------|---------------|----------------------------|

| 0                       | X                     | X              | Х             | No Breakpoint              |

| 1                       | 0                     | Х              | 0             | Breakpoint to SWI          |

| 1                       | 0                     | Х              | 1             | No Breakpoint              |

| 1                       | 1                     | 0              | Х             | Breakpoint to SWI          |

| 1                       | 1                     | 1              | 0             | Breakpoint to BDM          |

| 1                       | 1                     | 1              | 1             | No Breakpoint              |

#### Table 20-45. Breakpoint Mapping Summary

BDM cannot be entered from a breakpoint unless the ENABLE bit is set in the BDM. If entry to BDM via a BGND instruction is attempted and the ENABLE bit in the BDM is cleared, the S12XCPU actually executes the BDM firmware code. It checks the ENABLE and returns if ENABLE is not set. If not serviced by the monitor then the breakpoint is re-asserted when the BDM returns to normal S12XCPU flow.

If the comparator register contents coincide with the SWI/BDM vector address then an SWI in user code and DBG breakpoint could occur simultaneously. The S12XCPU ensures that BDM requests have a higher priority than SWI requests. Returning from the BDM/SWI service routine care must be taken to avoid re triggering a breakpoint.

### NOTE

When program control returns from a tagged breakpoint using an RTI or BDM GO command without program counter modification it will return to the instruction whose tag generated the breakpoint. To avoid re triggering a breakpoint at the same location reconfigure the S12XDBG module in the SWI routine, if configured for an SWI breakpoint, or over the BDM interface by executing a TRACE command before the GO to increment the program flow past the tagged instruction.

An XGATE software breakpoint is forced immediately, the tracing session terminated and the XGATE module execution stops. The user can thus determine if an XGATE breakpoint has occurred by reading out the XGATE program counter over the BDM interface.

Chapter 22 DP512 Port Integration Module (S12XDP512PIMV2)

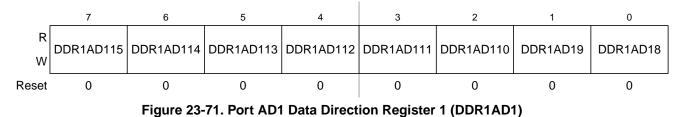

# 23.0.5.69 Port AD1 Data Direction Register 1 (DDR1AD1)

Read: Anytime.

Write: Anytime.

This register configures pins PAD as either input or output.

#### Table 23-62. DDR1AD1 Field Descriptions

| Field         | Description                                                                                                                                                                                                                                                                                           |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7–0           | Data Direction Port AD1 Register 1                                                                                                                                                                                                                                                                    |  |  |  |

| DDR1AD1[15:8] | <ul> <li>0 Associated pin is configured as input.</li> <li>1 Associated pin is configured as output.</li> <li>Note: Due to internal synchronization circuits, it can take up to 2 bus clock cycles until the correct value is read on PTAD11 register, when changing the DDR1AD1 register.</li> </ul> |  |  |  |

|               | <b>Note:</b> To use the digital input function on port AD1 the ATD1 digital input enable register (ATD1DIEN1) has to be set to logic level "1".                                                                                                                                                       |  |  |  |

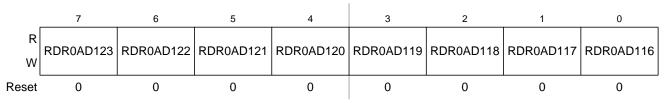

# 23.0.5.70 Port AD1 Reduced Drive Register 0 (RDR0AD1)

Figure 23-72. Port AD1 Reduced Drive Register 0 (RDR0AD1)

Read: Anytime.

Write: Anytime.

This register configures the drive strength of each PAD[23:16] output pin as either full or reduced. If the port is used as input this bit is ignored.

#### Table 23-63. RDR0AD1 Field Descriptions

| Field | Description                                                                                                                                                               |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>Reduced Drive Port AD1 Register 0</li> <li>0 Full drive strength at output.</li> <li>1 Associated pin drives at about 1/6 of the full drive strength.</li> </ul> |

| Field            | Description                                                                                                                                                                                                                                                                    |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–0<br>PK[7,5:0] | Port K — Port K pins 7–0 can be used as general-purpose I/O. If the data direction bits of the associated I/O pins are set to logic level "1", a read returns the value of the port register, otherwise the buffered pin input state is read except for bit 6 which reads "0". |

#### Table 24-15. PORTK Field Descriptions

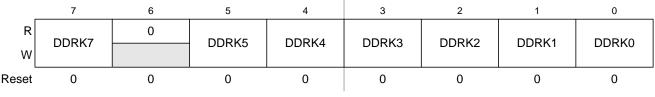

# 24.0.5.12 Port K Data Direction Register (DDRK)

Figure 24-14. Port K Data Direction Register (DDRK)

Read: Anytime.

Write: Anytime.

This register controls the data direction for port K. DDRK determines whether each pin (except PK6) is an input or output. A logic level "1" causes the associated port pin to be an output and a logic level "0" causes the associated pin to be a high-impedance input.

#### Table 24-16. DDRK Field Descriptions

| Field       | Description                                                                                                          |  |  |  |  |

|-------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7–0         | Data Direction Port K                                                                                                |  |  |  |  |

| DDRK[7,5:0] | 0 Associated pin is configured as input.                                                                             |  |  |  |  |

|             | 1 Associated pin is configured as output.                                                                            |  |  |  |  |

|             | Note: Due to internal synchronization circuits, it can take up to 2 bus clock cycles until the correct value is read |  |  |  |  |

|             | on PORTK after changing the DDRK register.                                                                           |  |  |  |  |

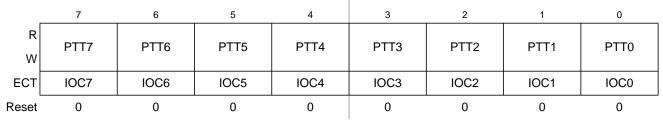

# 24.0.5.13 Port T Data Register (PTT)

## Figure 24-15. Port T Data Register (PTT)

Read: Anytime.

Write: Anytime.

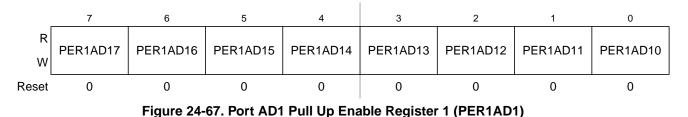

# 24.0.5.65 Port AD1 Pull Up Enable Register 1 (PER1AD1)

Read: Anytime.

Write: Anytime.

This register activates a pull-up device on the respective PAD[7:0] pin if the port is used as input. This bit has no effect if the port is used as output. Out of reset no pull-up device is enabled.

Table 24-59. PER1AD1 Field Descriptions

| Field               | Description                                                                                                                   |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------|

| 7–0<br>PER1AD1[7:0] | Pull Device Enable Port AD1 Register 1         0       Pull-up device is disabled.         1       Pull-up device is enabled. |

## **Functional Description**

Each pin except PE0, PE1, and BKGD can act as general purpose I/O. In addition each pin can act as an output from the external bus interface module or a peripheral module or an input to the external bus interface module.

A set of configuration registers is common to all ports with exceptions in the expanded bus interface and ATD ports (Table 24-60). All registers can be written at any time; however a specific configuration might not become active.

Example: Selecting a pull-up device

This device does not become active while the port is used as a push-pull output.

Table 24-60. Register Availability per Port<sup>1</sup>

| Port | Data | Data<br>Direction | Input | Reduced<br>Drive | Pull<br>Enable | Polarity<br>Select | Wired-OR<br>Mode | Interrupt<br>Enable | Interrupt<br>Flag |

|------|------|-------------------|-------|------------------|----------------|--------------------|------------------|---------------------|-------------------|

| А    | yes  | yes               | _     | yes              | yes            | —                  | —                | _                   | _                 |

| В    | yes  | yes               | _     |                  |                | —                  | —                | _                   | _                 |

| Е    | yes  | yes               | _     |                  |                | —                  | —                | _                   | _                 |

| K    | yes  | yes               | _     |                  |                | —                  | —                | _                   | _                 |

| Т    | yes  | yes               | yes   | yes              | yes            | —                  | —                | _                   | _                 |

| S    | yes  | yes               | yes   | yes              | yes            | yes                | yes              |                     | —                 |

| М    | yes  | yes               | yes   | yes              | yes            | yes                | yes              | _                   | _                 |

| Р    | yes  | yes               | yes   | yes              | yes            | yes                | —                | yes                 | yes               |

| Н    | yes  | yes               | yes   | yes              | yes            | yes                | —                | yes                 | yes               |

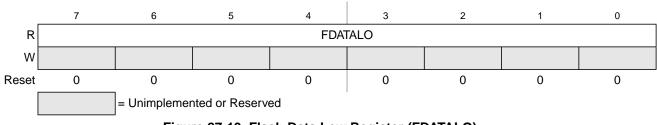

Figure 27-19. Flash Data Low Register (FDATALO)

All FDATAHI and FDATALO bits are readable but are not writable. At the completion of a data compress operation, the resulting 16-bit signature is stored in the FDATA registers. The data compression signature is readable in the FDATA registers until a new command write sequence is started.

# 27.3.2.11 RESERVED1

This register is reserved for factory testing and is not accessible.

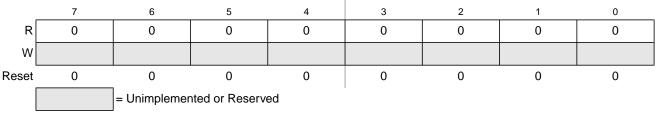

Figure 27-20. RESERVED1

All bits read 0 and are not writable.

## 27.3.2.12 RESERVED2

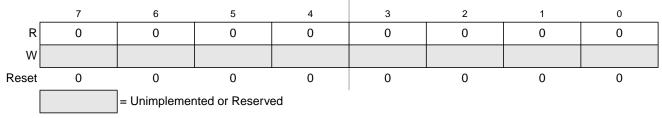

This register is reserved for factory testing and is not accessible.

Figure 27-21. RESERVED2

All bits read 0 and are not writable.

# 27.3.2.13 RESERVED3

This register is reserved for factory testing and is not accessible.

MC9S12XDP512 Data Sheet, Rev. 2.21

# 27.4.2.3 Program Command

The program operation will program a previously erased word in the Flash memory using an embedded algorithm.

An example flow to execute the program operation is shown in Figure 27-28. The program command write sequence is as follows:

- 1. Write to a Flash block address to start the command write sequence for the program command. The data written will be programmed to the address written. Multiple Flash blocks can be simultaneously programmed by writing to the same relative address in each Flash block.

- 2. Write the program command, 0x20, to the FCMD register.

- 3. Clear the CBEIF flag in the FSTAT register by writing a 1 to CBEIF to launch the program command.

If a word to be programmed is in a protected area of the Flash block, the PVIOL flag in the FSTAT register will set and the program command will not launch. Once the program command has successfully launched, the CCIF flag in the FSTAT register will set after the program operation has completed unless a new command write sequence has been buffered. By executing a new program command write sequence on sequential words after the CBEIF flag in the FSTAT register has been set, up to 55% faster programming time per word can be effectively achieved than by waiting for the CCIF flag to set after each program operation.

The meaning of the bits KEYEN[1:0] is shown in Table 30-2. Please refer to Section 30.1.5.1, "Unsecuring the MCU Using the Backdoor Key Access" for more information.

| KEYEN[1:0] | Backdoor Key<br>Access Enabled |

|------------|--------------------------------|

| 00         | 0 (disabled)                   |

| 01         | 0 (disabled)                   |

| 10         | 1 (enabled)                    |

| 11         | 0 (disabled)                   |

The meaning of the security bits SEC[1:0] is shown in Table 30-3. For security reasons, the state of device security is controlled by two bits. To put the device in unsecured mode, these bits must be programmed to SEC[1:0] = `10`. All other combinations put the device in a secured mode. The recommended value to put the device in secured state is the inverse of the unsecured state, i.e. SEC[1:0] = `01`.

| SEC[1:0] | Security State |

|----------|----------------|

| 00       | 1 (secured)    |

| 01       | 1 (secured)    |

| 10       | 0 (unsecured)  |

| 11       | 1 (secured)    |

## NOTE

Please refer to the Flash block guide (FTX) for actual security configuration (in section "Flash Module Security").

# 30.1.4 Operation of the Secured Microcontroller

By securing the device, unauthorized access to the EEPROM and Flash memory contents can be prevented. However, it must be understood that the security of the EEPROM and Flash memory contents also depends on the design of the application program. For example, if the application has the capability of downloading code through a serial port and then executing that code (e.g. an application containing bootloader code), then this capability could potentially be used to read the EEPROM and Flash memory contents even when the microcontroller is in the secure state. In this example, the security of the application could be enhanced by requiring a challenge/response authentication before any code can be downloaded.

Secured operation has the following effects on the microcontroller:

#### Chapter 30 Security (S12X9SECV2)

If all four 16-bit words match the Flash contents at 0xFF00–0xFF07 (0x7F\_FF00–0x7F\_FF07), the microcontroller will be unsecured and the security bits SEC[1:0] in the Flash Security register FSEC will be forced to the unsecured state ('10'). The contents of the Flash options/security byte are not changed by this procedure, and so the microcontroller will revert to the secure state after the next reset unless further action is taken as detailed below.

If any of the four 16-bit words does not match the Flash contents at 0xFF00–0xFF07 (0x7F\_FF00–0x7F\_FF07), the microcontroller will remain secured.

# 30.1.6 Reprogramming the Security Bits

In normal single chip mode (NS), security can also be disabled by erasing and reprogramming the security bits within Flash options/security byte to the unsecured value. Because the erase operation will erase the entire sector from 0xFE00-0xFFFF ( $0x7F_FE00-0x7F_FFFF$ ), the backdoor key and the interrupt vectors will also be erased; this method is not recommended for normal single chip mode. The application software can only erase and program the Flash options/security byte if the Flash sector containing the Flash options/security byte is not protected (see Flash protection). Thus Flash protection is a useful means of preventing this method. The microcontroller will enter the unsecured state after the next reset following the programming of the security bits to the unsecured value.

This method requires that:

- The application software previously programmed into the microcontroller has been designed to have the capability to erase and program the Flash options/security byte, or security is first disabled using the backdoor key method, allowing BDM to be used to issue commands to erase and program the Flash options/security byte.

- The Flash sector containing the Flash options/security byte is not protected.

# 30.1.7 Complete Memory Erase (Special Modes)

The microcontroller can be unsecured in special modes by erasing the entire EEPROM and Flash memory contents.

When a secure microcontroller is reset into special single chip mode (SS), the BDM firmware verifies whether the EEPROM and Flash memory are erased. If any EEPROM or Flash memory address is not erased, only BDM hardware commands are enabled. BDM hardware commands can then be used to write to the EEPROM and Flash registers to mass erase the EEPROM and all Flash memory blocks.

When next reset into special single chip mode, the BDM firmware will again verify whether all EEPROM and Flash memory are erased, and this being the case, will enable all BDM commands, allowing the Flash options/security byte to be programmed to the unsecured value. The security bits SEC[1:0] in the Flash security register will indicate the unsecure state following the next reset.

#### **Appendix A Electrical Characteristics**

#### Table A-6. 3.3-V I/O Characteristics

| Conditions are 3.15 V < V <sub>DD35</sub> < 3.6 V temperature from –40°C to +140°C, unless otherwise noted I/O Characteristics for all I/O pins except EXTAL, XTAL,XFC,TEST, VREGEN and supply pins. |   |                                                          |                    |    |   |   |    |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------------------------------------------------|--------------------|----|---|---|----|--|--|--|

| 17                                                                                                                                                                                                   | С | Port H, J, P interrupt input pulse filtered <sup>3</sup> | t <sub>PULSE</sub> | _  | _ | 3 | μs |  |  |  |

| 18                                                                                                                                                                                                   | С | Port H, J, P interrupt input pulse passed <sup>3</sup>   | t <sub>PULSE</sub> | 10 | _ | _ | μs |  |  |  |

<sup>1</sup> Maximum leakage current occurs at maximum operating temperature. Current decreases by approximately one-half for each 8 C to 12 C in the temperature range from 50°C to 125°C.

<sup>2</sup> Refer to Section A.1.4, "Current Injection" for more details

<sup>3</sup> Parameter only applies in stop or pseudo stop mode.

#### Appendix G Detailed Register Map

## 0x0240–0x027F Port Integration Module PIM\_9DX (PIM) Map (Sheet 2 of 4)

| Address | Name     |        | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|---------|----------|--------|-------|--------|--------|--------|--------|--------|--------|--------|

| 0x0248  | PTS      | R<br>W | PTS7  | PTS6   | PTS5   | PTS4   | PTS3   | PTS2   | PTS1   | PTS0   |

| 0x0249  | PTIS     | R      | PTIS7 | PTIS6  | PTIS5  | PTIS4  | PTIS3  | PTIS2  | PTIS1  | PTIS0  |

|         |          | W<br>R |       |        |        |        |        |        |        |        |

| 0x024A  | DDRS     | W      | DDRS7 | DDRS7  | DDRS5  | DDRS4  | DDRS3  | DDRS2  | DDRS1  | DDRS0  |

| 0x024B  | RDRS     | R<br>W | RDRS7 | RDRS6  | RDRS5  | RDRS4  | RDRS3  | RDRS2  | RDRS1  | RDRS0  |

| 0x024C  | PERS     | R<br>W | PERS7 | PERS6  | PERS5  | PERS4  | PERS3  | PERS2  | PERS1  | PERS0  |

| 0x024D  | PPSS     | R<br>W | PPSS7 | PPSS6  | PPSS5  | PPSS4  | PPSS3  | PPSS2  | PPSS1  | PPSS0  |

| 0x024E  | WOMS     | R<br>W | WOMS7 | WOMS6  | WOMS5  | WOMS4  | WOMS3  | WOMS2  | WOMS1  | WOMS0  |

| 0x024F  | Reserved | R<br>W | 0     | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| 00050   |          | R      |       | DTMO   | DTM    | DTMA   | DTMO   | DTMO   | DTM    | DTMO   |

| 0x0250  | PTM      | W      |       | PTM6   | PTM5   | PTM4   | PTM3   | PTM2   | PTM1   | PTM0   |

| 0x0251  | PTIM     | R<br>W | PTIM7 | PTIM6  | PTIM5  | PTIM4  | PTIM3  | PTIM2  | PTIM1  | PTIM0  |

| 0x0252  | DDRM     | R<br>W | DDRM7 | DDRM7  | DDRM5  | DDRM4  | DDRM3  | DDRM2  | DDRM1  | DDRM0  |

| 0x0253  | RDRM     | R<br>W | RDRM7 | RDRM6  | RDRM5  | RDRM4  | RDRM3  | RDRM2  | RDRM1  | RDRM0  |

| 0x0254  | PERM     | R<br>W | PERM7 | PERM6  | PERM5  | PERM4  | PERM3  | PERM2  | PERM1  | PERM0  |

| 0x0255  | PPSM     | R<br>W | PPSM7 | PPSM6  | PPSM5  | PPSM4  | PPSM3  | PPSM2  | PPSM1  | PPSM0  |

| 0x0256  | WOMM     | R<br>W | WOMM7 | WOMM6  | WOMM5  | WOMM4  | WOMM3  | WOMM2  | WOMM1  | WOMM0  |

| 0x0257  | MODRR    | R<br>W | 0     | MODRR6 | MODRR5 | MODRR4 | MODRR3 | MODRR2 | MODRR1 | MODRR0 |

| 0x0258  | PTP      | R<br>W | PTP7  | PTP6   | PTP5   | PTP4   | PTP3   | PTP2   | PTP1   | PTP0   |

| 0x0259  | PTIP     | R<br>W | PTIP7 | PTIP6  | PTIP5  | PTIP4  | PTIP3  | PTIP2  | PTIP1  | PTIP0  |

| 0x025A  | DDRP     | R<br>W |       | DDRP7  | DDRP5  | DDRP4  | DDRP3  | DDRP2  | DDRP1  | DDRP0  |

| 0x025B  | RDRP     | R<br>W |       | RDRP6  | RDRP5  | RDRP4  | RDRP3  | RDRP2  | RDRP1  | RDRP0  |

| 0x025C  | PERP     | R<br>W | PERP7 | PERP6  | PERP5  | PERP4  | PERP3  | PERP2  | PERP1  | PERP0  |

| 0x025D  | PPSP     | R<br>W | PPSP7 | PPSP6  | PPSP5  | PPSP4  | PPSP3  | PPSP2  | PPSP1  | PPSS0  |

| 0x025E  | PIEP     | R<br>W | PIEP7 | PIEP6  | PIEP5  | PIEP4  | PIEP3  | PIEP2  | PIEP1  | PIEP0  |

| 0x025F  | PIFP     | R<br>W | PIFP7 | PIFP6  | PIFP5  | PIFP4  | PIFP3  | PIFP2  | PIFP1  | PIFP0  |

MC9S12XDP512 Data Sheet, Rev. 2.21