# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | HC05                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 2.1MHz                                                                  |

| Connectivity               | SIO                                                                     |

| Peripherals                | POR, Temp Sensor, WDT                                                   |

| Number of I/O              | 22                                                                      |

| Program Memory Size        | 6KB (6K x 8)                                                            |

| Program Memory Type        | ОТР                                                                     |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 224 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | A/D 4x12b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                          |

| Supplier Device Package    | 28-SOIC                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc705jp7cdw |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Memory

### 6.3.2 Wait Mode

The WAIT instruction puts the MCU in a low-power wait mode which consumes more power than the stop mode and affects the MCU as follows:

- Enables interrupts by clearing the I bit in the condition code register

- Enables external interrupts by setting the IRQE bit in the IRQ status and control register

- Stops the CPU clock which drives the address and data buses, but allows the selected oscillator to continue to clock the core timer, programmable timer, analog subsystem, and SIOP

The WAIT instruction does not affect any other bits, registers, or I/O lines.

These conditions restart the CPU bus clock and bring the MCU out of wait mode:

- An external interrupt signal on the IRQ/V<sub>PP</sub> pin A high-to-low transition on the IRQ/V<sub>PP</sub> pin loads the program counter with the contents of locations \$1FFA and \$1FFB.

- An external interrupt signal on a port A external interrupt pin If selected by PIRQ bit in the MOR, a low-to-high transition on a PA3–PA0 pin loads the program counter with the contents of locations \$1FFA and \$1FFB.

- A core timer interrupt A core timer overflow or a real-time interrupt loads the program counter with the contents of locations \$1FF8 and \$1FF9.

- A programmable timer interrupt A programmable timer interrupt driven by an input capture, output compare, or timer overflow loads the program counter with the contents of locations \$1FF6 and \$1FF7.

- An SIOP interrupt An SIOP interrupt driven by the completion of transmitted or received 8-bit data loads the program counter with the contents of locations \$1FF4 and \$1FF5.

- An analog subsystem interrupt An analog subsystem interrupt driven by a voltage comparison loads the program counter with the contents of locations \$1FF2 and \$1FF3.

- A COP watchdog reset A timeout of the COP watchdog resets the MCU and loads the program counter with the contents of locations \$1FFE and \$1FFF. Software can enable real-time interrupts so that the MCU can periodically exit the wait mode to reset the COP watchdog.

- An external reset A logic 0 on the RESET pin resets the MCU and loads the program counter with the contents of locations \$1FFE and \$1FFF.

When the MCU exits the wait mode, there is no delay before code executes like occurs when exiting the stop or halt modes.

#### 6.3.3 Halt Mode

The STOP instruction puts the MCU in halt mode if selected by the SWAIT bit in the MOR. Halt mode is identical to wait mode, except that a variable recovery delay occurs when the MCU exits halt mode. A recovery time of from 1 to 16 or from 1 to 4064 internal bus cycles can be selected by the DELAY bit in the MOR.

If the SWAIT bit is set in the MOR to put the MCU in halt mode, the COP watchdog cannot be turned off inadvertently by a STOP instruction.

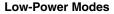

Figure 8-5. Analog Control Register (ACR)

#### CHG

The CHG enable bit allows direct control of the charge current source and the discharge device and also reflects the state of the discharge device. This bit is cleared by a reset of the device.

- 1 = If the ISEN bit is also set, the charge current source is sourcing current out of the PB0/AN0 pin. Writing a logic 1 enables the charging current out of the PB0/AN0 pin.

- 0 = The discharge device is sinking current into the PB0/AN0 pin. Writing a logic 0 disables the charging current and enables the discharging current into the PB0/AN0 pin, if the ISEN bit is also set.

#### ATD1-ATD2

The ATD1–ATD2 enable bits select one of the four operating modes used for making A/D conversions via the single-slope method. These four modes are given in Table 8-3. These bits have no effect if the ISEN enable bit is cleared. These bits are cleared by a reset of the device and thereby return the analog subsystem to the manual A/D conversion method.

| A/D            | Charge                                         |      | A/D O | ptions | Current Flow |                                                                                                                         |

|----------------|------------------------------------------------|------|-------|--------|--------------|-------------------------------------------------------------------------------------------------------------------------|

| Option<br>Mode | Control                                        | ISEN | ATD2  | ATD1   | CHG          | to/from PB0/AN0                                                                                                         |

| Disabled       | Current<br>source and<br>discharge<br>disabled | 0    | х     | х      | х            | Current control disabled,<br>no source or sink current                                                                  |

|                |                                                | 1    | 0     | 0      | 1            | Begin sourcing current<br>when the CHG bit is set<br>and continue to source<br>current until the CHG bit is<br>cleared. |

|                |                                                | 1    | 1     | 0      | 1            | The CHG bit remains set<br>until the next time ICF<br>occurs.                                                           |

| 3              | Automatic<br>charge and<br>discharge           | 1    | 1     | 1      | 0            | The CHG bit remains<br>cleared until the next time<br>OCF occurs.                                                       |

| 5              | (OCF–ICF)<br>synchronized<br>to timer          | 1    | 1     | 1      | 1            | The CHG bit remains set<br>until the next time ICF<br>occurs.                                                           |

#### Analog Subsystem

#### ICEN

This is a read/write bit that enables a voltage comparison to trigger the input capture register of the programmable timer when the CPF2 flag bit is set. Therefore, an A/D conversion could be started by receiving an OCF or TOF from the programmable timer and then terminated when the voltage on the external ramping capacitor reaches the level of the unknown voltage. The time of termination will be stored in the 16-bit buffer located at \$0014 and \$0015. This bit is automatically set whenever mode 2 or 3 is selected by setting the ATD2 control bit. This bit is cleared by a reset of the device.

1 = Connects the CPF2 flag bit to the timer input capture register

0 = Connects the PB3/AN3 pin to the timer input capture register

#### NOTE

For the input capture to occur when the output of comparator 2 goes high, the IEDG bit in the TCR must also be set.

When the ICEN bit is set, the input capture function of the programmable timer is not connected to the PB3/AN3/TCAP pin but is driven by the CPF2 output flag from comparator 2. To return to capturing times from external events, the ICEN bit must first be cleared before the timed event occurs.

#### CPIE

This is a read/write bit that enables an analog interrupt when either of the CPF1 or CPF2 flag bits is set to a logic 1. This bit is cleared by a reset of the device.

1 = Enables analog interrupts when comparator flag bits are set

0 = Disables analog interrupts when comparator flag bits are set

#### NOTE

If both the ICEN and CPIE bits are set, they will both generate an interrupt by different paths. One will be the programmable timer interrupt due to the input capture and the other will be the analog interrupt due to the output of comparator 2 going high. In this case, the input capture interrupt will be entered first due to its higher priority. The analog interrupt will then need to be serviced even if the comparator 2 output has been reset or the input capture flag (ICF) has been cleared.

#### **CP2EN**

The CP2EN enable bit controls power to voltage comparator 2 in the analog subsystem. Powering down a comparator will drop the supply current. This bit is cleared by a reset of the device.

1 = Writing a logic 1 powers up voltage comparator 2.

0 = Writing a logic 0 powers down voltage comparator 2.

#### NOTE

Voltage comparators power up slower than digital logic and their outputs may go through indeterminate states which might set their respective flags (CPF1, CPF2). It is therefore recommended to power up the charge current source first (ISEN), then to power up any comparators, and finally clear the flag bits by writing a logic 1 to the respective CPFR1 or CPFR2 bits in the ACR.

#### CP1EN

The CP1EN enable bit will power down the voltage comparator 1 in the analog subsystem. Powering down a comparator will drop the supply current. This bit is cleared by a reset of the device.

1 = Writing a logic 1 powers up voltage comparator 1

0 = Writing a logic 0 powers down voltage comparator 1

Analog Subsystem

### 8.7 Voltage Comparator Features

The two internal comparators can be used as simple voltage comparators if set up as described in Table 8-8. Both comparators can be active in the wait mode and can directly restart the part by means of the analog interrupt. Both comparators can also be active in the stop mode, but cannot directly restart the part. However, the comparators can directly drive PB4 which can then be connected externally to activate either a port interrupt on the PA0:3 pins or the IRQ/V<sub>PP</sub> pin.

| Comparator | Current<br>Source<br>Enable | Discharge<br>Device<br>Disable | Port B Pin<br>as Inputs | Port B Pin<br>Pulldowns<br>Disabled | Prog. Timer Input<br>Capture<br>Source |

|------------|-----------------------------|--------------------------------|-------------------------|-------------------------------------|----------------------------------------|

| 1          | Not<br>affected             | Not<br>affected                | DDRB2 = 0<br>DDRB3 = 0  | PDIB2 = 1<br>PDIB3 = 1              | Not<br>affected                        |

| 2          | ISEN = 0                    | ISEN = 0                       | DDRB0 = 0<br>DDRB1 = 0  | PDIB0 = 1<br>PDIB1 = 1              | ICEN = 0<br>IEDG = 1                   |

| Table 8-8. | Voltage | Comparator | Setup | Conditions  |

|------------|---------|------------|-------|-------------|

|            | Tonago  | oomparator | ootap | 00110110110 |

### 8.7.1 Voltage Comparator 1

Voltage comparator 1 is always connected to two of the port B I/O pins. These pins should be configured as inputs and have their software programmable pulldowns disabled. Also, the negative input of voltage comparator 1 is connected to the PB3/AN3/TCAP and shared with the input capture function of the 16-bit programmable timer. Therefore, the timer input capture interrupt should be disabled so that changes in the voltage on the PB3/AN3/TCAP pin do not cause unwanted input capture interrupts.

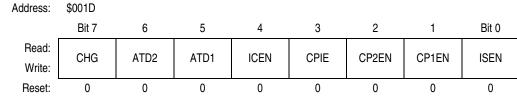

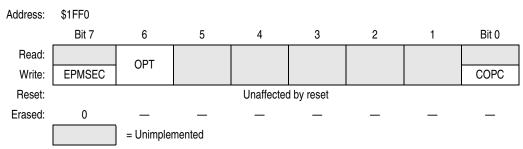

The output of comparator 1 can be connected to the port logic driving the PB4/AN4/TCMP/CMP1 pin such that the output of the comparator is ORed with the PB4 data bit and the OLVL bit from the 16-bit timer. This capability requires that the OPT bit is set in the COPR at location \$1FF0 as in Figure 8-12, and the COE1 bit is set in the ASR at location \$001E.

Figure 8-12. COP and Security Register (COPR)

#### **OPT** — Optional Features Bit

The OPT bit enables two additional features: direct drive by comparator 1 output to PB4 and voltage offset capability to sample capacitor in analog subsystem.

1 = Optional features enabled

0 = Optional features disabled

# Chapter 9 Simple Synchronous Serial Interface

### 9.1 Introduction

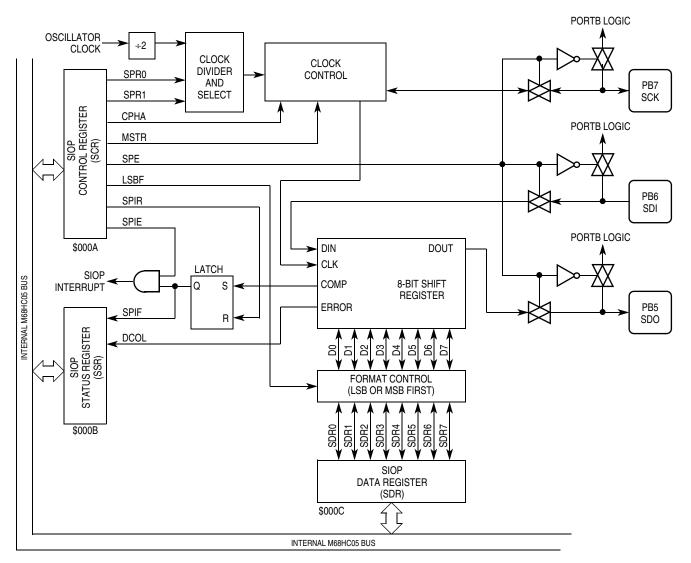

The simple synchronous serial I/O port (SIOP) subsystem is designed to provide efficient serial communications with peripheral devices or other MCUs. SIOP is implemented as a 3-wire master/slave system with serial clock (SCK), serial data input (SDI), and serial data output (SDO). A block diagram of the SIOP is shown in Figure 9-1.

Figure 9-1. SIOP Block Diagram

#### Simple Synchronous Serial Interface

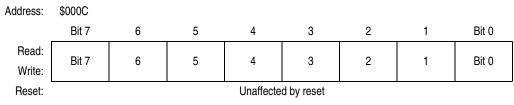

### 9.3.3 SIOP Data Register

The SIOP data register (SDR) is located at address \$000C and serves as both the transmit and receive data register. Writing to this register will initiate a message transmission if the node is in master mode. The SIOP subsystem is not double buffered and any write to this register will destroy the previous contents. The SDR can be read at any time. However, if a transfer is in progress the results may be ambiguous. Writing to the SDR while a transfer is in progress can cause invalid data to be transmitted and/or received. Figure 9-6 shows the position of each bit in the register. This register is not affected by reset.

Figure 9-6. SIOP Data Register (SDR)

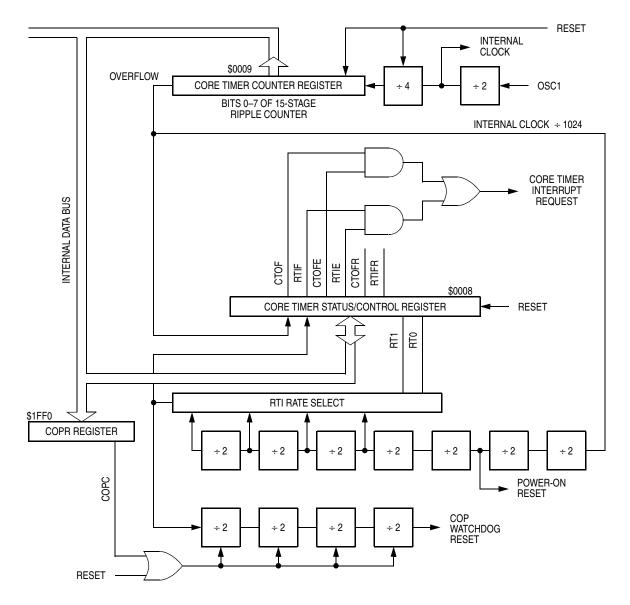

# Chapter 10 Core Timer

### **10.1 Introduction**

This section describes the operation of the core timer and the computer operating properly (COP) watchdog as shown by the block diagram in Figure 10-1.

# Chapter 11 Programmable Timer

### **11.1 Introduction**

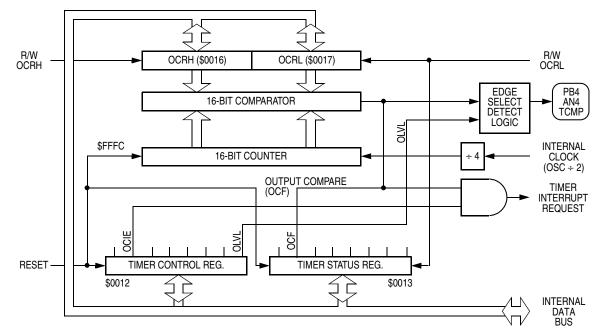

The MC68HC705JJ7/MC68HC705JP7 MCU contains a 16-bit programmable timer with an input capture function and an output compare function as shown by the block diagram in Figure 11-1.

The basis of the capture/compare timer is a 16-bit free-running counter which increases in count with every four internal bus clock cycles. The counter is the timing reference for the input capture and output compare functions. The input capture and output compare functions provide a means to latch the times at which external events occur, to measure input waveforms, and to generate output waveforms and timing delays. Software can read the value in the 16-bit free-running counter at any time without affecting the counter sequence.

The input/output (I/O) registers for the input capture and output compare functions are pairs of 8-bit registers, because of the 16-bit timer architecture used. Each register pair contains the high and low bytes of that function. Generally, accessing the low byte of a specific timer function allows full control of that function; however, an access of the high byte inhibits that specific timer function until the low byte is also accessed.

Because the counter is 16 bits long and preceded by a fixed divide-by-four prescaler, the counter rolls over every 262,144 internal clock cycles (every 524,288 oscillator clock cycles). Timer resolution with a 4-MHz crystal oscillator is 2 microseconds/count.

The interrupt capability, the input capture edge, and the output compare state are controlled by the timer control register (TCR) located at \$0012, and the status of the interrupt flags can be read from the timer status register (TSR) located at \$0013.

#### **Output Compare Registers**

Figure 11-8. Timer Output Compare Block Diagram

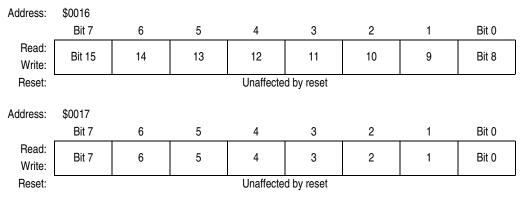

Figure 11-9. Output Compare Registers (OCRH and OCRL)

Writing to the OCRH before writing to the OCRL inhibits timer compares until the OCRL is written. Reading or writing to the OCRL after reading the TCR will clear the output compare flag bit (OCF). The output compare OLVL state will be clocked to its output latch regardless of the state of the OCF.

To prevent OCF from being set between the time it is read and the time the output compare registers are updated, use this procedure:

- 1. Disable interrupts by setting the I bit in the condition code register.

- 2. Write to the OCRH. Compares are now inhibited until OCRL is written.

- 3. Read the TSR to arm the OCF for clearing.

- 4. Enable the output compare registers by writing to the OCRL. This also clears the OCF flag bit in the TSR.

- 5. Enable interrupts by clearing the I bit in the condition code register.

A software example of this procedure is shown in Table 11-1.

#### Programmable Timer

#### **TOF** — Timer Overflow Flag

The TOF bit is automatically set when the 16-bit timer counter rolls over from \$FFFF to \$0000. Clear the TOF bit by reading the timer status register with the TOF set and then accessing the low byte (TMRL, \$0019) of the timer registers. Resets have no effect on TOF.

### 11.8 Timer Operation during Wait Mode

During wait mode, the 16-bit timer continues to operate normally and may generate an interrupt to trigger the MCU out of wait mode.

### 11.9 Timer Operation during Stop Mode

When the MCU enters stop mode, the free-running counter stops counting (the internal processor clock is stopped). It remains at that particular count value until stop mode is exited by applying a low signal to the  $\overline{IRQ}/V_{PP}$  pin, at which time the counter resumes from its stopped value as if nothing had happened. If stop mode is exited via an external reset (logic low applied to the RESET pin), the counter is forced to \$FFFC.

If a valid input capture edge occurs during stop mode, the input capture detect circuitry will be armed. This action does not set any flags or wake up the MCU, but when the MCU does wake up there will be an active input capture flag (and data) from the first valid edge. If the stop mode is exited by an external reset, no input capture flag or data will be present even if a valid input capture edge was detected during stop mode.

### 11.10 Timer Operation during Halt Mode

When the MCU enters halt mode, the functions and states of the 16-bit programmable timer are the same as for wait mode described in 11.8 Timer Operation during Wait Mode.

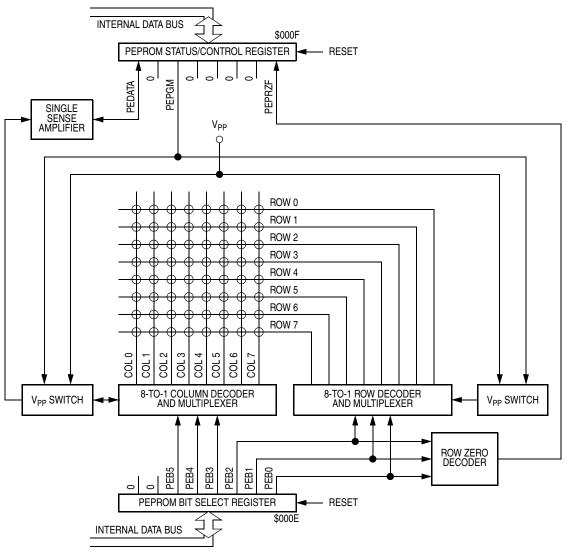

# Chapter 12 Personality EPROM (PEPROM)

### 12.1 Introduction

This section describes how to program the 64-bit personality erasable programmable read-only memory (PEPROM). Figure 12-1 shows the structure of the PEPROM subsystem.

**NOTE** In packages with no quartz window, the PEPROM functions as one-time programmable ROM (OTPROM).

EPROM/OTPROM

### 13.2.3 EPROM Security Bit

An EPROM programmable bit is provided at the location of the COP watchdog register at \$1FF0 as shown in Figure 13-3. This bit allows control of access to the EPROM array. Any accesses of the EPROM locations will return undefined results when the EPMSEC bit is set. Refer to 13.3.2 EPMSEC Programming for programming instructions.

Figure 13-3. EPROM Security in COP and Security Register (COPR)

#### EPMSEC — EPROM Security<sup>(1)</sup>

This EPROM write-only bit enables the access to the EPROM array.

- 1 = Access to the EPROM array in non-user modes is denied.

- 0 = Access to the EPROM array in non-user modes is enabled.

### **13.3 EPROM Programming**

A programming board is available from Freescale to download to the on-chip EPROM/OTPROM using the factory-provided programming software. Factory-provided software for programming the PEPROM is available on the World Wide Web at:

http://www.freescale.com

The programming software copies to the 6144-byte space located at EPROM addresses \$0700–\$1EFF and to the 16-byte space at addresses \$1FF0–\$1FFF which includes the mask option register at address \$1FF1, and the security bit at address \$1FF0.

#### NOTE

To program the EPROM/OTPROM, MOR, or EPMSEC bits properly, the  $V_{DD}$  voltage must be greater than 4.5 volts.

<sup>1.</sup> No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the EPROM/OTPROM difficult for unauthorized users.

Instruction Set

### 14.3.2 Read-Modify-Write Instructions

These instructions read a memory location or a register, modify its contents, and write the modified value back to the memory location or to the register.

#### NOTE

Do not use read-modify-write operations on write-only registers.

#### Table 14-2. Read-Modify-Write Instructions

| Instruction                         | Mnemonic            |

|-------------------------------------|---------------------|

| Arithmetic Shift Left (Same as LSL) | ASL                 |

| Arithmetic Shift Right              | ASR                 |

| Bit Clear                           | BCLR <sup>(1)</sup> |

| Bit Set                             | BSET <sup>(1)</sup> |

| Clear Register                      | CLR                 |

| Complement (One's Complement)       | COM                 |

| Decrement                           | DEC                 |

| Increment                           | INC                 |

| Logical Shift Left (Same as ASL)    | LSL                 |

| Logical Shift Right                 | LSR                 |

| Negate (Two's Complement)           | NEG                 |

| Rotate Left through Carry Bit       | ROL                 |

| Rotate Right through Carry Bit      | ROR                 |

| Test for Negative or Zero           | TST <sup>(2)</sup>  |

1. Unlike other read-modify-write instructions, BCLR and BSET use only direct addressing.

2. TST is an exception to the read-modify-write sequence because it does not write a replacement value.

## 14.4 Instruction Set Summary

| Source                                                                | Operation                                | Description                                            |   |   | ffe<br>n C( |   |   | Address<br>Mode                                                                                          | Opcode                                       | Operand                                      | Cycles                     |

|-----------------------------------------------------------------------|------------------------------------------|--------------------------------------------------------|---|---|-------------|---|---|----------------------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------|

| Form                                                                  | oporation                                |                                                        |   | I | Ν           | Z | С | Add<br>Mc                                                                                                | opq                                          | Ope                                          | Š                          |

| ADC #opr<br>ADC opr<br>ADC opr<br>ADC opr,X<br>ADC opr,X<br>ADC opr,X | Add with Carry                           | $A \gets (A) + (M) + (C)$                              | ţ |   | ţ           | ţ | ţ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX                                                                    | A9<br>B9<br>C9<br>D9<br>E9<br>F9             | ii<br>dd<br>hh II<br>ee ff<br>ff             | 2<br>3<br>4<br>5<br>4<br>3 |

| ADD #opr<br>ADD opr<br>ADD opr<br>ADD opr,X<br>ADD opr,X<br>ADD ,X    | Add without Carry                        | $A \gets (A) + (M)$                                    | ţ |   | ţ           | ţ | ţ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX                                                                    | AB<br>BB<br>CB<br>DB<br>EB<br>FB             | ii<br>dd<br>hh II<br>ee ff<br>ff             | 2<br>3<br>4<br>5<br>4<br>3 |

| AND #opr<br>AND opr<br>AND opr<br>AND opr,X<br>AND opr,X<br>AND ,X    | Logical AND                              | $A \gets (A) \land (M)$                                |   |   | ţ           | ţ |   | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX                                                                    | A4<br>B4<br>C4<br>D4<br>E4<br>F4             | ii<br>dd<br>hh II<br>ee ff<br>ff             | 2<br>3<br>4<br>5<br>4<br>3 |

| ASL <i>opr</i><br>ASLA<br>ASLX<br>ASL <i>opr</i> ,X<br>ASL ,X         | Arithmetic Shift Left<br>(Same as LSL)   | C - 0<br>b7 b0                                         |   |   | ţ           | ţ | ţ | DIR<br>INH<br>INH<br>IX1<br>IX                                                                           | 38<br>48<br>58<br>68<br>78                   | dd<br>ff                                     | 5<br>3<br>3<br>6<br>5      |

| ASR opr<br>ASRA<br>ASRX<br>ASR opr,X<br>ASR ,X                        | Arithmetic Shift Right                   | b7 b0                                                  |   |   | ţ           | ţ | ţ | DIR<br>INH<br>INH<br>IX1<br>IX                                                                           | 37<br>47<br>57<br>67<br>77                   | dd<br>ff                                     | 5<br>3<br>3<br>6<br>5      |

| BCC rel                                                               | Branch if Carry Bit<br>Clear             | $PC \leftarrow (PC) + 2 + \mathit{rel} ? C = 0$        | — | _ |             | _ |   | REL                                                                                                      | 24                                           | rr                                           | 3                          |

| BCLR n opr                                                            | Clear Bit n                              | Mn ← 0                                                 |   |   |             |   |   | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 11<br>13<br>15<br>17<br>19<br>1B<br>1D<br>1F | dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd | 5 5 5 5 5 5 5 5            |

| BCS rel                                                               | Branch if Carry Bit Set<br>(Same as BLO) | PC ← (PC) + 2 + <i>rel</i> ? C = 1                     | — | _ | _           | _ |   | REL                                                                                                      | 25                                           | rr                                           | 3                          |

| BEQ rel                                                               | Branch if Equal                          | $PC \leftarrow (PC) + 2 + \mathit{rel} ? Z = 1$        | — | _ | _           | — | _ | REL                                                                                                      | 27                                           | rr                                           | 3                          |

| BHCC rel                                                              | Branch if Half-Carry<br>Bit Clear        | PC ← (PC) + 2 + <i>rel</i> ? H = 0                     | _ | _ | —           | _ | _ | REL                                                                                                      | 28                                           | rr                                           | 3                          |

| BHCS rel                                                              | Branch if Half-Carry<br>Bit Set          | PC ← (PC) + 2 + <i>rel</i> ? H = 1                     | _ | _ | —           | _ | _ | REL                                                                                                      | 29                                           | rr                                           | 3                          |

| BHI <i>rel</i>                                                        | Branch if Higher                         | $PC \leftarrow (PC) + 2 + \mathit{rel} ? C \lor Z = 0$ | - | — | —           | — | _ | REL                                                                                                      | 22                                           | rr                                           | 3                          |

### Table 14-6. Instruction Set Summary (Sheet 1 of 6)

|                                                                    |                                                           |                                                                                                                                                                                                                                                                                                                                                                             |   |    | ffe  |   |   | s a                                   | de                               | pu                               | S                          |

|--------------------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|------|---|---|---------------------------------------|----------------------------------|----------------------------------|----------------------------|

| Source<br>Form                                                     | Operation                                                 | Description                                                                                                                                                                                                                                                                                                                                                                 |   | or | n C( | 1 | 1 | Address<br>Mode                       | Opcode                           | Operand                          | Cycles                     |

| -                                                                  |                                                           |                                                                                                                                                                                                                                                                                                                                                                             | Н | Ι  | Ν    | Z | С |                                       | _                                | op                               |                            |

| ROR <i>opr</i><br>RORA<br>RORX<br>ROR <i>opr</i> ,X<br>ROR ,X      | Rotate Byte Right through Carry Bit                       | b7 b0                                                                                                                                                                                                                                                                                                                                                                       | _ | _  | ţ    | ţ | ţ | DIR<br>INH<br>INH<br>IX1<br>IX        | 36<br>46<br>56<br>66<br>76       | dd<br>ff                         | 5<br>3<br>6<br>5           |

| RSP                                                                | Reset Stack Pointer                                       | $SP \leftarrow \$00FF$                                                                                                                                                                                                                                                                                                                                                      | — | —  | —    | — | — | INH                                   | 9C                               |                                  | 2                          |

| RTI                                                                | Return from Interrupt                                     | $\begin{array}{l} SP \leftarrow (SP) + 1;  Pull  (CCR) \\ & SP \leftarrow (SP) + 1;  Pull  (A) \\ & SP \leftarrow (SP) + 1;  Pull  (X) \\ & SP \leftarrow (SP) + 1;  Pull  (PCH) \\ & SP \leftarrow (SP) + 1;  Pull  (PCL) \end{array}$                                                                                                                                     | ţ | ţ  | ţ    | ţ | Þ | INH                                   | 80                               |                                  | 6                          |

| RTS                                                                | Return from<br>Subroutine                                 | $SP \leftarrow (SP) + 1$ ; Pull (PCH)<br>$SP \leftarrow (SP) + 1$ ; Pull (PCL)                                                                                                                                                                                                                                                                                              |   |    |      |   |   | INH                                   |                                  |                                  |                            |

| SBC #opr<br>SBC opr<br>SBC opr<br>SBC opr,X<br>SBC opr,X<br>SBC ,X | Subtract Memory Byte<br>and Carry Bit from<br>Accumulator | $A \gets (A) - (M) - (C)$                                                                                                                                                                                                                                                                                                                                                   |   |    | ţ    | ţ | ţ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX | A2<br>B2<br>C2<br>D2<br>E2<br>F2 | ii<br>dd<br>hh II<br>ee ff<br>ff | 2<br>3<br>4<br>5<br>4<br>3 |

| SEC                                                                | Set Carry Bit                                             | C ← 1                                                                                                                                                                                                                                                                                                                                                                       | — | —  | —    | — | 1 | INH                                   | 99                               |                                  | 2                          |

| SEI                                                                | Set Interrupt Mask                                        | l ← 1                                                                                                                                                                                                                                                                                                                                                                       | — | 1  | —    | — | — | INH                                   | 9B                               |                                  | 2                          |

| STA opr<br>STA opr<br>STA opr,X<br>STA opr,X<br>STA ,X             | Store Accumulator in<br>Memory                            | M ← (A)                                                                                                                                                                                                                                                                                                                                                                     | _ |    | ţ    | ţ |   | DIR<br>EXT<br>IX2<br>IX1<br>IX        | B7<br>C7<br>D7<br>E7<br>F7       | dd<br>hh II<br>ee ff<br>ff       | 4<br>5<br>6<br>5<br>4      |

| STOP                                                               | Stop Oscillator and<br>Enable IRQ Pin                     |                                                                                                                                                                                                                                                                                                                                                                             | - | 0  | —    | — | — | INH                                   | 8E                               |                                  | 2                          |

| STX opr<br>STX opr<br>STX opr,X<br>STX opr,X<br>STX ,X             | Store Index<br>Register In Memory                         | M ← (X)                                                                                                                                                                                                                                                                                                                                                                     |   |    | ţ    | ţ |   | DIR<br>EXT<br>IX2<br>IX1<br>IX        | BF<br>CF<br>DF<br>EF<br>FF       | dd<br>hh ll<br>ee ff<br>ff       | 4<br>5<br>6<br>5<br>4      |

| SUB #opr<br>SUB opr<br>SUB opr<br>SUB opr,X<br>SUB opr,X<br>SUB ,X | Subtract Memory Byte<br>from<br>Accumulator               | $A \gets (A) - (M)$                                                                                                                                                                                                                                                                                                                                                         |   |    | ţ    | ţ | ţ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX | A0<br>B0<br>C0<br>D0<br>E0<br>F0 | ii<br>dd<br>hh II<br>ee ff<br>ff | 2<br>3<br>4<br>5<br>4<br>3 |

| SWI                                                                | Software Interrupt                                        | $\begin{array}{l} PC \leftarrow (PC) + 1;  Push  (PCL) \\ SP \leftarrow (SP) - 1;  Push  (PCH) \\ SP \leftarrow (SP) - 1;  Push  (X) \\ SP \leftarrow (SP) - 1;  Push  (A) \\ SP \leftarrow (SP) - 1;  Push  (CCR) \\ SP \leftarrow (SP) - 1;  I \leftarrow 1 \\ PCH \leftarrow  Interrupt  Vector  High  Byte \\ PCL \leftarrow  Interrupt  Vector  Low  Byte \end{array}$ |   | 1  |      |   |   | INH                                   | 83                               |                                  | 10                         |

### Table 14-6. Instruction Set Summary (Sheet 5 of 6)

Instruction Set

**Electrical Specifications**

### 15.5 Supply Current Characteristics (V<sub>DD</sub> = 4.5 to 5.5 Vdc)

| Characteristic <sup>(1)</sup>                                                                                                                                                   | Symbol          | Min | Typ <sup>(2)</sup> | Max                 | Unit           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|--------------------|---------------------|----------------|

| RUN <sup>(3)</sup> (analog and LVR disabled)<br>Internal low-power oscillator at 100 kHz<br>Internal low-power oscillator at 500 kHz<br>External oscillator running at 4.2 MHz  | I <sub>DD</sub> | —   | 150<br>375<br>3.00 | 568<br>1100<br>5.20 | μΑ<br>μΑ<br>mA |

| WAIT <sup>(4)</sup> (analog and LVR disabled)<br>Internal low-power oscillator at 100 kHz<br>Internal low-power oscillator at 500 kHz<br>External oscillator running at 4.2 MHz | I <sub>DD</sub> |     | 45<br>75<br>1.00   | 85<br>375<br>2.20   | μA<br>μA<br>mA |

| <b>STOP</b> <sup>(5)</sup> (analo <b>g and LVR</b> disabled)<br>Typical<br>-40°C to 85°C                                                                                        | I <sub>DD</sub> |     | 2<br>4             | 10<br>20            | μA             |

| Incremental I <sub>DD</sub> for enabled modules<br>LVR<br>Analog subsystem                                                                                                      | I <sub>DD</sub> |     | 5<br>380           | 15<br>475           | μA             |

1.  $V_{DD}$  = 4.5 to 5.5 Vdc,  $V_{SS}$  = 0 V,  $T_L \le T_A \le T_H$ , unless otherwise noted. All values shown reflect average measurements.

2. Typical values at midpoint of voltage range, 25°C only

3. Run (Operating) IDD, Wait IDD: Measured using external square wave clock source to OSC1 pin or internal oscillator, all inputs 0.2 Vdc from either supply rail ( $V_{DD}$  or  $V_{SS}$ ); no dc loads, less than 50 pF on all outputs,  $C_L = 20$  pF on OSC2. 4. Wait  $I_{DD}$  is affected linearly by the OSC2 capacitance.

5. Stop  $I_{DD}$ : All ports configured as inputs,  $V_{IL} = 0.2$  Vdc,  $V_{IH} = V_{DD} - 0.2$  Vdc, OSC1 =  $V_{DD}$ .

### 15.6 Supply Current Characteristics ( $V_{DD}$ = 2.7 to 3.3 Vdc)

| Characteristic <sup>(1)</sup>                                                                                                                                                   | Symbol          | Min | Typ <sup>(2)</sup> | Max                | Unit           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|--------------------|--------------------|----------------|

| RUN <sup>(3)</sup> (analog and LVR disabled)<br>Internal low-power oscillator at 100 kHz<br>Internal low-power oscillator at 500 kHz<br>External oscillator running at 2.1 MHz  | I <sub>DD</sub> |     | 70<br>320<br>1.25  | 320<br>800<br>2.60 | μΑ<br>μΑ<br>mA |

| WAIT <sup>(4)</sup> (analog and LVR disabled)<br>Internal low-power oscillator at 100 kHz<br>Internal low-power oscillator at 500 kHz<br>External oscillator running at 2.1 MHz | I <sub>DD</sub> |     | 20<br>40<br>0.50   | 65<br>250<br>1.10  | μΑ<br>μΑ<br>mA |

| STOP <sup>(5)</sup> (analog and LVR disabled)<br>25°C<br>-40°C to 85°C                                                                                                          | I <sub>DD</sub> |     | 1<br>2             | 5<br>10            | μA             |

| Incremental I <sub>DD</sub> for enabled modules<br>LVR<br>Analog subsystem                                                                                                      | I <sub>DD</sub> |     | 5<br>380           | 15<br>475          | μA             |

1.  $V_{DD}$  = 2.7 to 3.3 Vdc,  $V_{SS}$  = 0 V,  $T_L \le T_A \le T_H$ , unless otherwise noted. All values shown reflect average measurements. 2. Typical values at midpoint of voltage range, 25°C only.

3. Run (Operating) IDD, Wait IDD: Measured using external square wave clock source to OSC1 pin or internal oscillator, all inputs 0.2 Vdc from either supply rail ( $V_{DD}$  or  $V_{SS}$ ); no dc loads, less than 50 pF on all outputs,  $C_L = 20$  pF on OSC2.

4. Wait IDD is affected linearly by the OSC2 capacitance.

5. Stop  $I_{DD}$ : All ports configured as inputs,  $V_{IL} = 0.2$  Vdc,  $V_{IH} = V_{DD} - 0.2$  Vdc, OSC1 =  $V_{DD}$ .

Supply Current Characteristics (V<sub>DD</sub> = 2.7 to 3.3 Vdc)

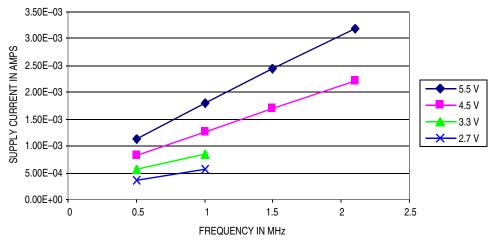

Figure 15-1. Typical Run I<sub>DD</sub> versus Internal Clock Frequency at 25°C

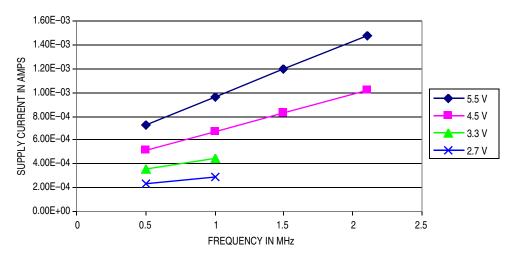

Figure 15-2. Typical Wait I<sub>DD</sub> versus Internal Clock Frequency at 25°C

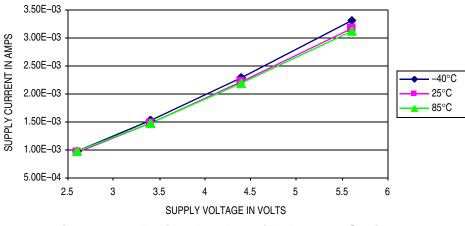

Figure 15-3. Typical Run I<sub>DD</sub> with External Oscillator

### 15.12 Control Timing (3.0 Vdc)

| Characteristic <sup>(1)</sup>                                                                                                                                                                                                                                                        | Symbol                                                           | Min                         | Max                               | Unit                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-----------------------------|-----------------------------------|---------------------------------|

| Frequency of oscillation (OSC)<br>RC oscillator option<br>Crystal oscillator option<br>External clock source<br>Internal low-power oscillator                                                                                                                                        | fosc                                                             | <br>0.1<br>dc               | 2.1<br>2.1<br>2.1                 | MHz<br>MHz<br>MHz               |

| Standard product (100 kHz nominal)<br>Mask option (500 kHz nominal, see Note 3))                                                                                                                                                                                                     |                                                                  | 60<br>300                   | 140<br>700                        | kHz<br>kHz                      |

| Internal operating frequency, crystal, or external clock (f <sub>OSC</sub> /2)<br>RC oscillator option<br>Crystal oscillator option<br>External clock source<br>Internal low-power oscillator<br>Standard product (100 kHz nominal)<br>Mask option (500 kHz nominal <sup>(2)</sup> ) | f <sub>OP</sub>                                                  | <br>0.05<br>dc<br>30<br>150 | 1.05<br>1.05<br>1.05<br>70<br>350 | MHz<br>MHz<br>MHz<br>kHz<br>kHz |

| Cycle time (1/f <sub>OP</sub> )<br>External oscillator or clock source<br>Internal low-power oscillator<br>Standard product (100 kHz nominal)<br>Mask option (500 kHz nominal <sup>(2)</sup> )                                                                                       | t <sub>cyc</sub>                                                 | 952<br>14.29<br>2.86        | —<br>33.33<br>6.67                | ns<br>μs<br>μs                  |

| 16-bit timer<br>Resolution<br>Input capture (TCAP) pulse width                                                                                                                                                                                                                       | t <sub>RESL</sub><br>t <sub>TH</sub> , t <sub>TL</sub>           | 4.0<br>284                  |                                   | t <sub>cyc</sub><br>ns          |

| Interrupt pulse width low (edge-triggered)                                                                                                                                                                                                                                           | t <sub>ILIH</sub>                                                | 284                         | —                                 | ns                              |

| Interrupt pulse period                                                                                                                                                                                                                                                               | t <sub>ILIL</sub>                                                | (3)                         | —                                 | t <sub>cyc</sub>                |

| OSC1 pulse width (external clock input)                                                                                                                                                                                                                                              | t <sub>OH</sub> , t <sub>OL</sub>                                | 110                         | —                                 | ns                              |

| Analog subsystem response<br>Voltage comparators<br>Switching time (10 mV overdrive, either input)<br>Comparator power-up delay (bias circuit already powered up)<br>External current source (PB0/AN0)<br>Switching time (I <sub>DIS</sub> to I <sub>RAMP</sub> )                    | <sup>t</sup> CPROP<br><sup>t</sup> CDELAY<br><sup>t</sup> ISTART |                             | 2<br>2<br>1                       | μs<br>μs<br>μs                  |

| Power-up delay (bias circuit already powered up)<br>Bias circuit power-up delay                                                                                                                                                                                                      | t <sub>IDELAY</sub><br>t <sub>BDELAY</sub>                       | _                           | 2<br>2                            | μs<br>μs                        |

1. +2.7  $\leq$  V<sub>DD</sub>  $\leq$  +3.3 V, V<sub>SS</sub> = 0 V, T<sub>L</sub>  $\leq$  T<sub>A</sub>  $\leq$  T<sub>H</sub>, unless otherwise noted 2. The 500 kHz nominal mask option is available through special order only. Contact your local Freescale sales representative for detailed ordering information. Not offered with the RC oscillator option.

3. The minimum period, t<sub>ILIL</sub>, should not be less than the number of cycle times it takes to execute the interrupt service routine plus 21 t<sub>cyc</sub>.