Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Active                                                                 |

| Core Processor             | S08                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 40MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                                     |

| Peripherals                | LCD, LVD, POR, PWM, WDT                                                |

| Number of I/O              | 39                                                                     |

| Program Memory Size        | 18KB (18K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 1.9K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 9x12b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 48-LQFP                                                                |

| Supplier Device Package    | 48-LQFP (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s08lg16j0vlf |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

2

## **Table of Contents**

| 1  | Pin Assig   | gnments4                                                | Figure 17.Internal Oscillator Deviation from Trimmed Frequency | 25 |

|----|-------------|---------------------------------------------------------|----------------------------------------------------------------|----|

| 2  |             | ll Characteristics                                      | Figure 18.ADC Input Impedance Equivalency Diagram              |    |

|    |             | troduction                                              | Figure 19.Reset Timing                                         |    |

|    |             | rameter Classification                                  | Figure 20.IRQ/KBIPx Timing                                     | 30 |

|    |             | osolute Maximum Ratings10                               | Figure 21.Timer External Clock                                 |    |

|    |             | ermal Characteristics                                   | Figure 22.Timer Input Capture Pulse                            |    |

|    |             | SD Protection and Latch-Up Immunity                     | Figure 23.SPI Master Timing (CPHA = 0)                         |    |

|    | 2.6 DC      | Characteristics                                         | Figure 24.SPI Master Timing (CPHA =1)                          | 32 |

|    | 2.7 Su      | ipply Current Characteristics                           | Figure 25.SPI Slave Timing (CPHA = 0)                          | 33 |

|    | 2.8 Ex      | ternal Oscillator (XOSC) Characteristics                | Figure 26.SPI Slave Timing (CPHA = 1)                          | 33 |

|    | 2.9 Int     | ternal Clock Source (ICS) Characteristics               | Figure 27.4 MHz, Positive Polarity Pins 1 – 41                 | 36 |

|    | 2.10 AE     | DC Characteristics                                      | Figure 28.4 MHz, Positive Polarity Pins 42 – 80                | 36 |

|    | 2.11 AC     | C Characteristics                                       | Figure 29.4 MHz, Negative Polarity Pins 1 – 41                 | 37 |

|    | 2.1         | 11.1 Control Timing                                     | Figure 30.4 MHz, Negative Polarity Pins 42 – 80                | 37 |

|    | 2.1         | 11.2 TPM Module Timing                                  | Figure 31.Device Number Example for Auto Parts                 | 39 |

|    | 2.1         | 11.3 SPI Timing31                                       | Figure 32.Device Number Example for IMM Parts                  | 39 |

|    | 2.12 LC     | CD Specifications                                       | Figure 33.80-pin LQFP Package Drawing                          |    |

|    | 2.13 Fla    | ash Specifications                                      | (Case 917A, Doc #98ASS23237W)                                  | 42 |

|    | 2.14 EN     | MC Performance35                                        | Figure 34.64-pin LQFP Package Drawing                          |    |

|    | 2.1         | 14.1 Radiated Emissions35                               | (Case 840F, Doc #98ASS23234W)                                  | 45 |

|    | 2.1         | 14.2 Conducted Transient Susceptibility                 | Figure 35.48-pin LQFP Package Drawing                          |    |

| 3  | Ordering    | Information38                                           | (Case 932, Doc #98ASH00962A)                                   | 47 |

|    | _           | evice Numbering System                                  |                                                                |    |

| 4  |             | Information39                                           | List of Tables                                                 |    |

|    |             | echanical Drawings                                      | Table 1. MC9S08LG32 Series Features by MCU and Package .       | 4  |

|    |             | 1.1 80-pin LQFP                                         | Table 2. Pin Availability by Package Pin-Count                 | 8  |

|    |             | 1.2 64-pin LQFP                                         | Table 3. Parameter Classifications                             | 10 |

|    |             | 1.3 48-pin LQFP                                         | Table 4. Absolute Maximum Ratings                              | 11 |

| 5  |             | History                                                 | Table 5. Thermal Characteristics                               | 11 |

|    |             | •                                                       | Table 6. ESD and Latch-Up Test Conditions                      | 12 |

| LI | st of Fig   | gures                                                   | Table 7. ESD and Latch-Up Protection Characteristics           | 13 |

| Fi | gure 1.M0   | C9S08LG32 Series Block Diagram 3                        | Table 8. DC Characteristics                                    | 13 |

| Fi | gure 2.80   | -Pin LQFP                                               | Table 9. Supply Current Characteristics                        | 17 |

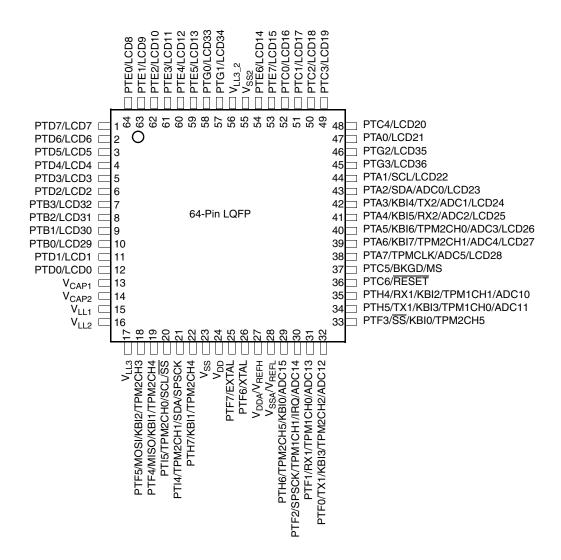

| Fi | gure 3.64   | -Pin LQFP 6                                             | Table 10.Oscillator Electrical Specifications                  |    |

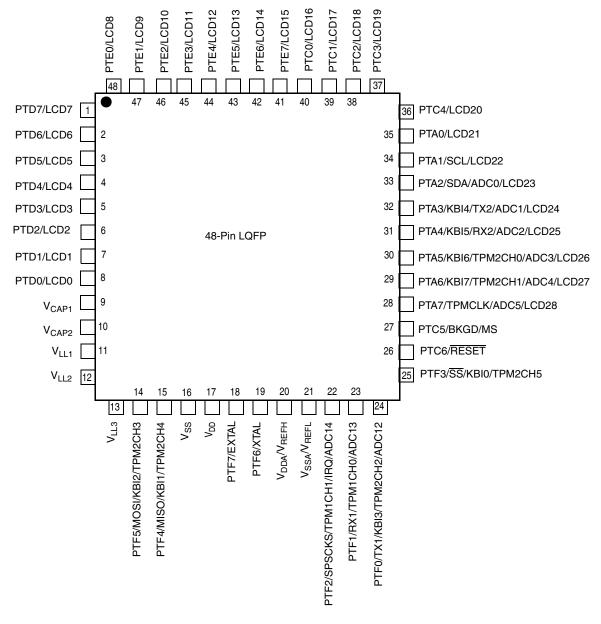

| Fi | gure 4.48   | -Pin LQFP                                               | (Temperature Range = -40 °C to 105 °C Ambient)                 | 22 |

| Fi | gure 5. Tyr | pical Low-side Drive (sink) characteristics –           | Table 11.ICS Frequency Specifications                          |    |

| Н  | gh Drive (  | (PTxDSn = 1)                                            | (Temperature Range = -40 °C to 105 °C Ambient)                 | 24 |

| Fi | gure 6. Tyr | pical Low-side Drive (sink) characteristics –           | Table 12.12-bit ADC Operating Conditions                       | 25 |

| Lo | ow Drive (  | PTxDSn = 0)                                             | Table 13.12-bit ADC Characteristics                            |    |

| Fi | gure 7. Ty  | pical High-side Drive (source) characteristics -        | $(V_{REFH} = V_{DDAD}, V_{REFL} = V_{SSAD})$                   | 27 |

| Н  | gh Drive (  | (PTxDSn = 1)                                            | Table 14.Control Timing                                        | 29 |

| Fi | gure 8. Ty  | pical High-side Drive (source) characteristics –        | Table 15.TPM Input Timing                                      | 30 |

| Lo | ow Drive (  | PTxDSn = 0)                                             | Table 16.SPI Timing                                            | 31 |

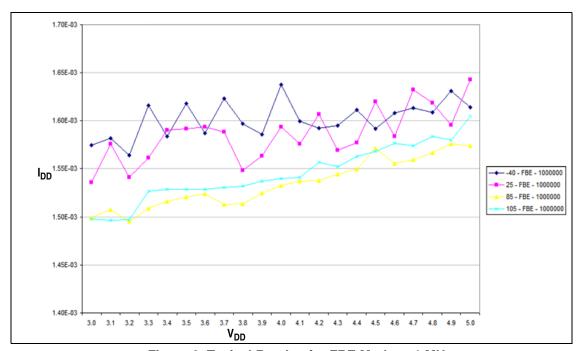

|    |             | pical Run IDD for FBE Mode at 1 MHz 19                  | Table 17.LCD Electricals, 3 V Glass                            | 34 |

|    | -           | ypical Run I <sub>DD</sub> for FBE Mode at 20 MHz 20    | Table 18.Flash Characteristics                                 |    |

|    |             | ypical Run I <sub>DD</sub> for FEE Mode at 1 MHz        | Table 19.Radiated Emissions, Electric Field                    |    |

|    | -           | ypical Run I <sub>DD</sub> for FEE Mode at 20 MHz 21    | Table 20.Conducted Susceptibility, EFT/B                       |    |

|    |             | ypical Stop2 I <sub>DD</sub>                            | Table 21. Susceptibility Performance Classification            |    |

|    |             | ypical Stop3 I <sub>DD</sub>                            | Table 22.Device Numbering System                               |    |

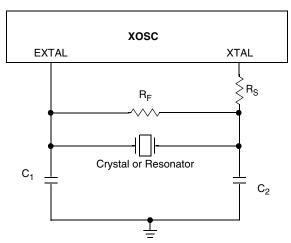

| Fi | gure 15.Ti  | ypical Crystal or Resonator Circuit: High Range and Low | Table 23. Package Descriptions                                 |    |

|    |             | ange/High Gain                                          | Table 24.Revision History.                                     |    |

| Fi |             | vpical Crystal or Resonator Circuit: Low Range/Low      | ,                                                              | -  |

MC9S08LG32 Series Data Sheet, Rev. 9

## **Pin Assignments**

Table 1. MC9S08LG32 Series Features by MCU and Package

| Feature            | MC9S08LG32       |                  |                  | MC9S08LG16       |                  |  |

|--------------------|------------------|------------------|------------------|------------------|------------------|--|

| Flash size (bytes) | 32,768 18,432    |                  |                  |                  |                  |  |

| RAM size (bytes)   | 1984             |                  |                  |                  |                  |  |

| Pin quantity       | 80               | 64               | 48               | 64               | 48               |  |

| ADC                | 16 ch            | 12 ch            | 9 ch             | 12 ch            | 9 ch             |  |

| LCD                | 8 x 37<br>4 x 41 | 8 x 29<br>4 x 33 | 8 x 21<br>4 x 25 | 8 x 29<br>4 x 33 | 8 x 21<br>4 x 25 |  |

| ICE + DBG          |                  |                  | yes              |                  |                  |  |

| ICS                |                  |                  | yes              |                  |                  |  |

| IIC                |                  |                  | yes              |                  |                  |  |

| IRQ                |                  |                  | yes              |                  |                  |  |

| KBI                |                  |                  | 8 pin            |                  |                  |  |

| GPIOs              | 69               | 53               | 39               | 53               | 39               |  |

| RTC                |                  |                  | yes              |                  |                  |  |

| MTIM               |                  |                  | yes              |                  |                  |  |

| SCI1               |                  |                  | yes              |                  |                  |  |

| SCI2               |                  |                  | yes              |                  |                  |  |

| SPI                |                  |                  | yes              |                  |                  |  |

| TPM1 channels      |                  |                  | 2                |                  |                  |  |

| TPM2 channels      |                  |                  | 6                |                  |                  |  |

| XOSC               |                  |                  | yes              |                  |                  |  |

# 1 Pin Assignments

This section shows the pin assignments for the MC9S08LG32 series devices. The priority of functions on a pin is in ascending order from left to right and bottom to top. Another view of pinouts and function priority is given in Table 2.

### **Pin Assignments**

Figure 3. 64-Pin LQFP

## **NOTE**

$V_{REFH}/V_{REFL}$  are internally connected to  $V_{DDA}/V_{SSA}$ .

Figure 4. 48-Pin LQFP

## **NOTE**

$V_{REFH}/V_{REFL}$  are internally connected to  $V_{DDA}/V_{SSA}.$

Table 2. Pin Availability by Package Pin-Count (continued)

|    | Packages |    | < Lowest Priority> Highest |         |                 |         |       |  |  |  |

|----|----------|----|----------------------------|---------|-----------------|---------|-------|--|--|--|

| 80 | 64       | 48 | Port Pin                   | Alt 1   | Alt 2           | Alt 3   | Alt 4 |  |  |  |

| 39 | 31       | 23 | PTF1                       | RX1     | TPM1CH0         | ADC13   | _     |  |  |  |

| 40 | 32       | 24 | PTF0                       | TX1     | X1 KBI3 TPM2CH2 |         | ADC12 |  |  |  |

| 41 | 33       | 25 | PTF3                       | SS      | KBI0            | TPM2CH5 | _     |  |  |  |

| 42 | 34       | _  | PTH5                       | TX1     | KBI3            | TPM1CH0 | ADC11 |  |  |  |

| 43 | 35       | _  | PTH4                       | RX1     | KBI2            | TPM1CH1 | ADC10 |  |  |  |

| 44 | _        | _  | PTH3                       | KBI7    | ADC9            | _       | _     |  |  |  |

| 45 | _        | _  | PTH2                       | KBI6    | ADC8            | _       | _     |  |  |  |

| 46 | _        | _  | PTH1                       | KBI5    | ADC7            | _       | _     |  |  |  |

| 47 | _        | _  | PTH0                       | KBI4    | ADC6            | _       | _     |  |  |  |

| 48 | 36       | 26 | PTC6                       | RESET   | _               | _       | _     |  |  |  |

| 49 | 37       | 27 | PTC5                       | BKGD/MS | _               | _       | _     |  |  |  |

| 50 | 38       | 28 | PTA7                       | TPMCLK  | ADC5            | LCD28   | _     |  |  |  |

| 51 | 39       | 29 | PTA6                       | KBI7    | TPM2CH1         | ADC4    | LCD27 |  |  |  |

| 52 | 40       | 30 | PTA5                       | KBI6    | TPM2CH0         | ADC3    | LCD26 |  |  |  |

| 53 | 41       | 31 | PTA4                       | KBI5    | RX2             | ADC2    | LCD25 |  |  |  |

| 54 | 42       | 32 | PTA3                       | KBI4    | TX2             | ADC1    | LCD24 |  |  |  |

| 55 | 43       | 33 | PTA2                       | SDA     | ADC0            | LCD23   | _     |  |  |  |

| 56 | 44       | 34 | PTA1                       | SCL     | LCD22           | _       | _     |  |  |  |

| 57 | 45       | _  | PTG3                       | LCD36   | _               | _       | _     |  |  |  |

| 58 | 46       | _  | PTG2                       | LCD35   | _               | _       | _     |  |  |  |

| 59 | 47       | 35 | PTA0                       | LCD21   | _               | _       | _     |  |  |  |

| 60 | 48       | 36 | PTC4                       | LCD20   | _               | _       | _     |  |  |  |

| 61 | 49       | 37 | PTC3                       | LCD19   | _               | _       | _     |  |  |  |

| 62 | 50       | 38 | PTC2                       | LCD18   | _               | _       | _     |  |  |  |

| 63 | 51       | 39 | PTC1                       | LCD17   | _               | _       | _     |  |  |  |

| 64 | 52       | 40 | PTC0                       | LCD16   | _               | _       | _     |  |  |  |

| 65 | 53       | 41 | PTE7                       | LCD15   | _               | _       | _     |  |  |  |

| 66 | 54       | 42 | PTE6                       | LCD14   | _               | _       | _     |  |  |  |

| 67 | 55       | _  | V <sub>SS2</sub>           | _       | _               | _       | _     |  |  |  |

| 68 | 56       | _  | V <sub>LL3_2</sub>         | _       | _               | _       | _     |  |  |  |

| 69 | _        | _  | PTG7                       | LCD44   | _               | _       | _     |  |  |  |

| 70 | _        | _  | PTG6                       | LCD43   | _               | _       | _     |  |  |  |

| 71 | _        | _  | PTG5                       | LCD42   | _               | _       | _     |  |  |  |

| 72 | _        | _  | PTG4                       | LCD41   | _               | _       | _     |  |  |  |

| 73 | 57       | _  | PTG1                       | LCD34   | _               | _       | _     |  |  |  |

| 74 | 58       | _  | PTG0                       | LCD33   | _               | _       | _     |  |  |  |

| 75 | 59       | 43 | PTE5                       | LCD13   | _               | _       | _     |  |  |  |

| 76 | 60       | 44 | PTE4                       | LCD12   | _               |         | _     |  |  |  |

Table 2. Pin Availability by Package Pin-Count (continued)

|    | Packages |    |          | < Lowest Priority> Highest |       |       |       |  |  |  |

|----|----------|----|----------|----------------------------|-------|-------|-------|--|--|--|

| 80 | 64       | 48 | Port Pin | Alt 1                      | Alt 2 | Alt 3 | Alt 4 |  |  |  |

| 77 | 61       | 45 | PTE3     | LCD11                      | _     | _     | _     |  |  |  |

| 78 | 62       | 46 | PTE2     | LCD10                      | _     | _     | _     |  |  |  |

| 79 | 63       | 47 | PTE1     | LCD9                       | _     | _     | _     |  |  |  |

| 80 | 64       | 48 | PTE0     | LCD8                       | _     | _     | _     |  |  |  |

## 2 Electrical Characteristics

## 2.1 Introduction

This section contains electrical and timing specifications for the MC9S08LG32 series of microcontrollers available at the time of publication.

## 2.2 Parameter Classification

The electrical parameters shown in this supplement are guaranteed by various methods. To give the customer a better understanding the following classification is used and the parameters are tagged accordingly in the tables where appropriate:

**Table 3. Parameter Classifications**

| Р | Those parameters are guaranteed during production testing on each individual device.                                                                                                                                   |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| С | Those parameters are achieved by the design characterization by measuring a statistically relevant sample size across process variations.                                                                              |

| Т | Those parameters are achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted. All values shown in the typical column are within this category. |

| D | Those parameters are derived mainly from simulations.                                                                                                                                                                  |

## NOTE

The classification is shown in the column labeled "C" in the parameter tables where appropriate.

## 2.3 Absolute Maximum Ratings

Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Stress beyond the limits specified in Table 4 may affect device reliability or cause permanent damage to the device. For functional operating conditions, refer to the remaining tables in this section.

This device contains circuitry that protects against damage due to high static voltage or electrical fields. However, it is advised that normal precautions should be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (for instance, either  $V_{SS}$  or  $V_{DD}$ ) or the programmable pull-up resistor associated with the pin is enabled.

MC9S08LG32 Series Data Sheet, Rev. 9

Eqn. 1

| Rating                                                                                       | Symbol           | Value                    | Unit |

|----------------------------------------------------------------------------------------------|------------------|--------------------------|------|

| Supply voltage                                                                               | $V_{DD}$         | -0.3 to +5.8             | V    |

| Maximum current into V <sub>DD</sub>                                                         | I <sub>DD</sub>  | 120                      | mA   |

| Digital input voltage                                                                        | V <sub>In</sub>  | $-0.3$ to $V_{DD} + 0.3$ | V    |

| Instantaneous maximum current Single pin limit (applies to all port pins) <sup>1, 2, 3</sup> | I <sub>D</sub>   | ±25<br>±2                | mA   |

| Storage temperature range                                                                    | T <sub>stg</sub> | -55 to 150               | °C   |

**Table 4. Absolute Maximum Ratings**

## 2.4 Thermal Characteristics

This section provides information about operating temperature range, power dissipation, and package thermal resistance. Power dissipation on I/O pins is usually small compared to the power dissipation in On-Chip logic and voltage regulator circuits, and it is user-determined rather than being controlled by the MCU design. To take  $P_{\rm I/O}$  into account in power calculations, determine the difference between actual pin voltage and  $V_{\rm SS}$  or  $V_{\rm DD}$  and multiply by the pin current for each I/O pin. Except in cases of unusually high pin current (heavy loads), the difference between pin voltage and  $V_{\rm SS}$  or  $V_{\rm DD}$  will be very small.

| Rating                                                                              | Symbol            | Value                                           | Unit |

|-------------------------------------------------------------------------------------|-------------------|-------------------------------------------------|------|

| Operating temperature range (packaged)                                              | T <sub>A</sub>    | T <sub>L</sub> to T <sub>H</sub><br>-40 to +105 | °C   |

| Maximum junction temperature                                                        | $T_J$             | 125                                             | °C   |

| Thermal resistance Single-layer board 80-pin LQFP 64-pin LQFP 48-pin LQFP           | $\theta_{\sf JA}$ | 61<br>71<br>80                                  | °C/W |

| Thermal resistance<br>Four-layer board<br>80-pin LQFP<br>64-pin LQFP<br>48-pin LQFP | $\theta_{\sf JA}$ | 48<br>52<br>56                                  | °C/W |

**Table 5. Thermal Characteristics**

The average chip-junction temperature (T<sub>I</sub>) in °C can be obtained from:

$$T_{J} = T_{A} + (P_{D} \times \theta_{JA})$$

MC9S08LG32 Series Data Sheet, Rev. 9

Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive (V<sub>DD</sub>) and negative (V<sub>SS</sub>) clamp voltages and use the largest of the two resistance values.

$<sup>^{2}\,</sup>$  All functional non-supply pins are internally clamped to  $\rm V_{SS}$  and  $\rm V_{DD}.$

Power supply must maintain regulation within operating V<sub>DD</sub> range during instantaneous and operating maximum current conditions. If positive injection current (V<sub>In</sub> > V<sub>DD</sub>) is greater than I<sub>DD</sub>, the injection current may flow out of V<sub>DD</sub> and could result in an external power supply going out of regulation. Ensure that the external V<sub>DD</sub> load will shunt current greater than maximum injection current, this will be of greater risk when the MCU is not consuming power. For instance, if no system clock is present, or if the clock rate is very low (which would reduce overall power consumption).

where:

$T_A = Ambient temperature, °C$

$\theta_{JA}$  = Package thermal resistance, junction-to-ambient, °C/W

$P_D = P_{int} + P_{I/O}$

$P_{int} = I_{DD} \times V_{DD}$ , Watts — chip internal power

$P_{I/O}$  = Power dissipation on input and output pins — user determined

For most applications,  $P_{I/O} \ll P_{int}$  and can be neglected. An approximate relationship between  $P_D$  and  $T_J$  (if  $P_{I/O}$  is neglected) is:

$$P_D = K \div (T_1 + 273 \, ^{\circ}C)$$

Eqn. 2

Solving Equation 1 and Equation 2 for K gives:

$$K = P_D \times (T_\Delta + 273 \,^{\circ}C) + \theta_{A\Delta} \times (P_D)^2$$

Eqn. 3

where K is a constant pertaining to the particular part. K can be determined from equation 3 by measuring  $P_D$  (at equilibrium) for a known  $T_A$ . Using this value of K, the values of  $P_D$  and  $T_J$  can be obtained by solving Equation 1 and Equation 2 iteratively for any value of  $T_A$ .

## 2.5 ESD Protection and Latch-Up Immunity

Although damage from electrostatic discharge (ESD) is much less common on these devices than on early CMOS circuits, normal handling precautions should be taken to avoid exposure to static discharge. Qualification tests are performed to ensure that these devices can withstand exposure to reasonable levels of static without suffering any permanent damage.

All ESD testing is in conformity with AEC-Q100 Stress Test Qualification for automotive grade integrated circuits. During the device qualification, ESD stresses were performed for the human body model (HBM), the machine model (MM) and the charge device model (CDM).

A device is defined as a failure if after exposure to ESD pulses the device no longer meets the device specification. Complete DC parametric and functional testing is performed per the applicable device specification at room temperature followed by hot temperature, unless instructed otherwise in the device specification.

Table 6. ESD and Latch-Up Test Conditions

| Model      | Description                 | Symbol | Value | Unit |

|------------|-----------------------------|--------|-------|------|

| Human Body | Series resistance           | R1     | 1500  | Ω    |

| Model      | Storage capacitance         | С      | 100   | pF   |

|            | Number of pulses per pin    | _      | 3     | _    |

| Latch-up   | Minimum input voltage limit | _      | -2.5  | V    |

|            | Maximum input voltage limit | _      | 7.5   | V    |

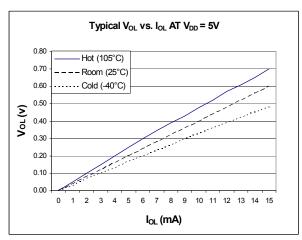

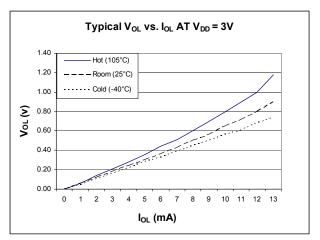

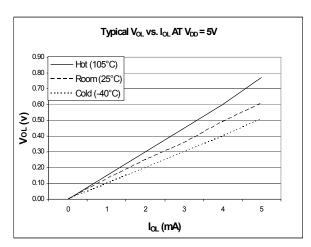

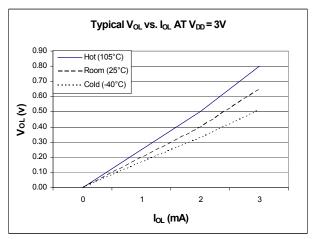

Figure 5. Typical Low-side Drive (sink) characteristics - High Drive (PTxDSn = 1)

Figure 6. Typical Low-side Drive (sink) characteristics – Low Drive (PTxDSn = 0)

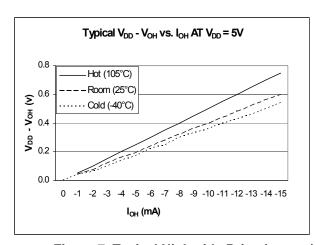

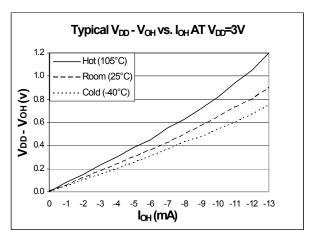

Figure 7. Typical High-side Drive (source) characteristics – High Drive (PTxDSn = 1)

Table 9. Supply Current Characteristics (continued)

| Num | С | Par           | ameter                                       | Symbol | Bus<br>Freq | V <sub>DD</sub><br>(V) | Typ <sup>1</sup>  | Max | Unit | Temp<br>(°C)     |

|-----|---|---------------|----------------------------------------------|--------|-------------|------------------------|-------------------|-----|------|------------------|

| 6   | Т | Stop2 adders: | RTC using LPO                                |        | n/a         | 3                      | 210               | _   | nA   | -40 °C to 105 °C |

|     |   |               | RTC using low power crystal oscillator       |        |             |                        | 4.25              | _   | μА   |                  |

|     |   |               | LCD <sup>2</sup> with rbias<br>(Low Gain)    |        |             |                        | 1.2 <sup>3</sup>  | _   |      |                  |

|     |   |               | LCD <sup>2</sup> with rbias<br>(High Gain)   |        |             |                        | 18 <sup>4</sup>   | _   |      |                  |

|     |   |               | LCD <sup>2</sup> with Cpump                  |        |             |                        | 4.05 <sup>3</sup> | _   |      | -40 °C to 85 °C  |

|     |   |               | RTC using LPO                                |        |             | 5                      | 210               | _   | nA   | -40 °C to 105 °C |

|     |   |               | RTC using low power crystal oscillator       |        |             |                        | 4.22              | _   | μА   |                  |

|     |   |               | LCD <sup>2</sup> with rbias<br>(Low Gain)    |        |             |                        | 1.5 <sup>3</sup>  | _   |      |                  |

|     |   |               | LCD <sup>2</sup> with rbias<br>(High Gain)   |        |             |                        | 32 <sup>4</sup>   | _   |      |                  |

|     |   |               | LCD <sup>2</sup> with Cpump                  |        |             |                        | 7.12 <sup>3</sup> | _   |      | -40 °C to 85 °C  |

| 7   | Т | Stop3 adders: | RTC using LPO                                | _      | n/a         | 3                      | 210               | _   | nA   | -40 °C to 105 °C |

|     |   |               | RTC using low<br>power crystal<br>oscillator |        |             |                        | 4.75              | _   | μА   |                  |

|     |   |               | LCD <sup>2</sup> with rbias<br>(Low Gain)    |        |             |                        | 1.2 <sup>3</sup>  | _   | •    |                  |

|     |   |               | LCD <sup>2</sup> with rbias<br>(High Gain)   |        |             |                        | 18 <sup>4</sup>   | _   |      |                  |

|     |   |               | LCD <sup>2</sup> with Cpump                  |        |             |                        | 4.35 <sup>3</sup> | _   |      | -40 °C to 85 °C  |

|     |   |               | RTC using LPO                                |        |             | 5                      | 230               | _   | nA   | -40 °C to 105 °C |

|     |   |               | RTC using low power crystal oscillator       |        |             |                        | 4.74              | _   | μА   |                  |

|     |   |               | LCD <sup>2</sup> with rbias<br>(Low Gain)    |        |             |                        | 1.5 <sup>3</sup>  | _   |      |                  |

|     |   |               | LCD <sup>2</sup> with rbias<br>(High Gain)   |        |             |                        | 32 <sup>4</sup>   | _   | •    |                  |

|     |   |               | LCD <sup>2</sup> with Cpump                  |        |             |                        | 7.49 <sup>3</sup> | _   | 1    | -40 °C to 85 °C  |

| Table 9. | Supply | / Current  | Characteristics                         | (continued)   | ١ |

|----------|--------|------------|-----------------------------------------|---------------|---|

| IUDIC U. | CUPPI  | , our crit | O I I I I I I I I I I I I I I I I I I I | (OOIILIIIGOA) | , |

| Num | С | Parameter                  |              | Symbol | Bus<br>Freq | V <sub>DD</sub><br>(V) | Typ <sup>1</sup> | Max | Unit | Temp<br>(°C)     |

|-----|---|----------------------------|--------------|--------|-------------|------------------------|------------------|-----|------|------------------|

| 8   | Т | Stop3 adders: EREFSTEN = 1 |              | _      | n/a         | 3                      | 4.58             | _   | μΑ   | -40 °C to 105 °C |

|     |   |                            | IREFSTEN = 1 |        |             |                        | 71.7             | _   |      |                  |

|     |   |                            | LVD          |        |             |                        | 94.35            | _   |      |                  |

|     |   | EREFSTEN = 1               |              |        |             | 5                      | 4.61             | _   | μΑ   |                  |

|     |   |                            | IREFSTEN = 1 |        |             |                        | 71.69            | _   |      |                  |

|     |   |                            | LVD          |        |             |                        | 107.34           | _   |      |                  |

<sup>&</sup>lt;sup>1</sup> Typical values are measured at 25 °C. Characterized, not tested.

<sup>&</sup>lt;sup>4</sup> This is the maximum current when all LCD inputs/outputs are used.

Figure 9. Typical Run  $I_{DD}$  for FBE Mode at 1 MHz

$<sup>^2</sup>$  LCD configured for Charge Pump Enabled  $\rm V_{LL3}$  connected to  $\rm V_{DD}$

<sup>&</sup>lt;sup>3</sup> This does not include current required for 32 kHz oscillator.

Table 10. Oscillator Electrical Specifications (Temperature Range = -40 °C to 105 °C Ambient) (continued)

| Num | С | Characteristic                                                                                                                                            | Symbol                                                                                         | Min              | Typ <sup>1</sup>      | Max              | Unit |

|-----|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------|-----------------------|------------------|------|

| 3   | D | Feedback resistor  • Low range (32 kHz to 100 kHz)  • High range (1 MHz to 16 MHz)                                                                        | R <sub>F</sub>                                                                                 |                  | 10<br>1               | _                | ΜΩ   |

| 4   | D | Series resistor  • Low range, low gain (RANGE = 0, HGO = 0)  • Low range, high gain (RANGE = 0, HGO = 1)                                                  | R <sub>S</sub>                                                                                 |                  | 0<br>100              |                  | kΩ   |

| 5   | D | Series resistor  • High range, low gain (RANGE = 1, HGO = 0)  • High range, high gain (RANGE = 1, HGO = 1)  ≥8 MHz 4 MHz 1 MHz                            | R <sub>S</sub>                                                                                 |                  | 0 0                   | 0<br>10<br>20    | kΩ   |

| 6   | Т | Crystal start-up time <sup>3, 4</sup> • Low range (HGO = 0) • Low range (HGO = 1) • High range (HG0 = 0) <sup>5</sup> • High range (HG0 = 1) <sup>5</sup> | t <sub>CSTL-LP</sub><br>t <sub>CSTL-HGO</sub><br>t <sub>CSTH-LP</sub><br>t <sub>CSTH-HGO</sub> | _<br>_<br>_<br>_ | 500<br>3570<br>4<br>4 | _<br>_<br>_<br>_ | ms   |

| 7   | D | Square wave input clock frequency (EREFS = 0, ERCLKEN = 1)  • FEE or FBE mode  • BLPE mode                                                                | f <sub>extal</sub>                                                                             | 0.03125<br>0     |                       | 5<br>40          | MHz  |

Data in Typical column was characterized at 5.0 V, 25 °C or is typical recommended value.

Figure 15. Typical Crystal or Resonator Circuit: High Range and Low Range/High Gain

When ICS is configured for FEE or FBE mode, input clock source must be divisible using RDIV to within the range of 31.25 kHz to 39.0625 kHz.

<sup>&</sup>lt;sup>3</sup> This parameter is characterized and not tested on each device.

<sup>&</sup>lt;sup>4</sup> Proper PC board layout procedures must be followed to achieve specifications.

<sup>&</sup>lt;sup>5</sup> 4 MHz crystal

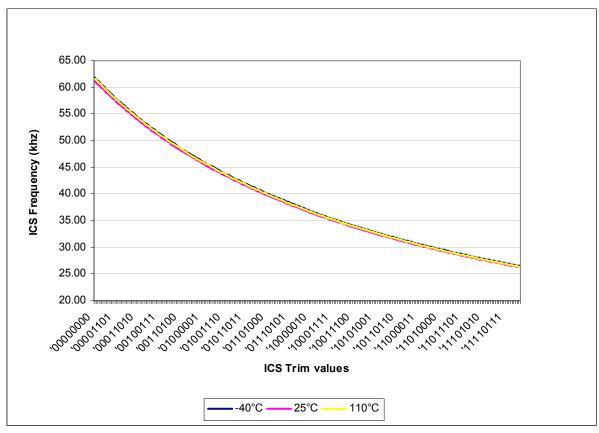

Figure 17. Internal Oscillator Deviation from Trimmed Frequency

## 2.10 ADC Characteristics

**Table 12. 12-bit ADC Operating Conditions**

| Characteristic       | Conditions                                                                   | Symb               | Min               | Typ <sup>1</sup> | Max               | Unit | Comment                                           |

|----------------------|------------------------------------------------------------------------------|--------------------|-------------------|------------------|-------------------|------|---------------------------------------------------|

| Supply voltage       | Absolute                                                                     | $V_{DDAD}$         | 2.7               | _                | 5.5               | V    | _                                                 |

|                      | Delta to V <sub>DD</sub> (V <sub>DD</sub> – V <sub>DDAD</sub> ) <sup>2</sup> | $\Delta V_{DDAD}$  | -100              | 0                | +100              | mV   | _                                                 |

| Ground voltage       | Delta to V <sub>SS</sub> (V <sub>SS</sub> – V <sub>SSAD</sub> ) <sup>2</sup> | ΔV <sub>SSAD</sub> | -100              | 0                | +100              | mV   | _                                                 |

| Ref Voltage<br>High  | _                                                                            | V <sub>REFH</sub>  | _                 | _                | _                 | V    | V <sub>REFH</sub> shorted to V <sub>DDAD</sub>    |

| Ref Voltage<br>Low   | _                                                                            | V <sub>REFL</sub>  | _                 | _                | _                 | V    | V <sub>REFL</sub> shorted to<br>V <sub>SSAD</sub> |

| Input Voltage        | _                                                                            | V <sub>ADIN</sub>  | V <sub>REFL</sub> | _                | V <sub>REFH</sub> | V    | _                                                 |

| Input<br>Capacitance | _                                                                            | C <sub>ADIN</sub>  | _                 | 4.5              | 5.5               | pF   | _                                                 |

## 2.14 EMC Performance

Electromagnetic compatibility (EMC) performance is highly dependant on the environment in which the MCU resides. Board design and layout, circuit topology choices, location and characteristics of external components as well as MCU software operation all play a significant role in EMC performance. The system designer should consult Freescale applications notes such as AN2321, AN1050, AN1263, AN2764, and AN1259 for advice and guidance specifically targeted at optimizing EMC performance.

## 2.14.1 Radiated Emissions

Microcontroller radiated RF emissions are measured from 150 kHz to 1 GHz using the TEM/GTEM cell method in accordance with the IEC 61967-2 and SAE J1752/3 standards. The measurement is performed with the microcontroller installed on a custom EMC evaluation board while running specialized EMC test software. The radiated emissions from the microcontroller are measured in a TEM cell in two package orientations (North and East).

The maximum radiated RF emissions of the tested configuration in all orientations are less than or equal to the reported emissions levels.

| Parameter           | Symbol                | Conditions                                | Frequency      | f <sub>osc</sub> /f <sub>Bus</sub> | Level <sup>1</sup><br>(Max) | Unit |  |  |  |  |   |  |

|---------------------|-----------------------|-------------------------------------------|----------------|------------------------------------|-----------------------------|------|--|--|--|--|---|--|

| Radiated emissions, | V <sub>RE_TEM</sub>   | $V_{DD} = 5.5$                            | 0.15 – 50 MHz  | 4 MHz crystal                      | 10                          | dBμV |  |  |  |  |   |  |

| electric field      |                       | T <sub>A</sub> = +25 °C<br>Package type = | 50 – 150 MHz   | 16 MHz bus                         | 14                          |      |  |  |  |  |   |  |

|                     | 80 LQFP 150 – 500 MHz |                                           |                |                                    | 8                           |      |  |  |  |  |   |  |

|                     |                       |                                           | 500 – 1000 MHz |                                    |                             |      |  |  |  |  | 5 |  |

|                     | IEC Level             |                                           | IEC Level      |                                    | L                           | _    |  |  |  |  |   |  |

|                     |                       |                                           | SAE Level      |                                    | 2                           | _    |  |  |  |  |   |  |

Table 19. Radiated Emissions, Electric Field

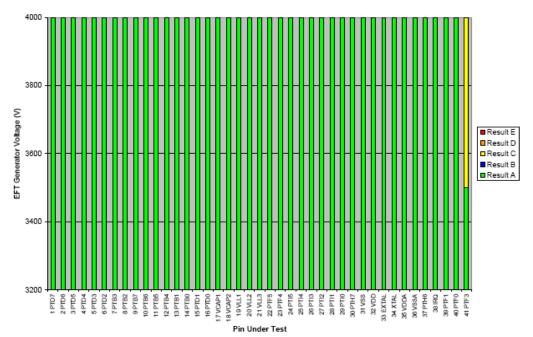

## 2.14.2 Conducted Transient Susceptibility

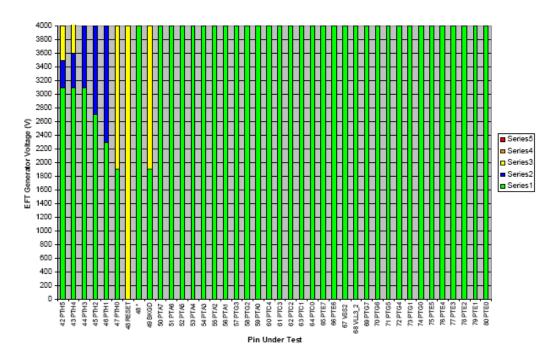

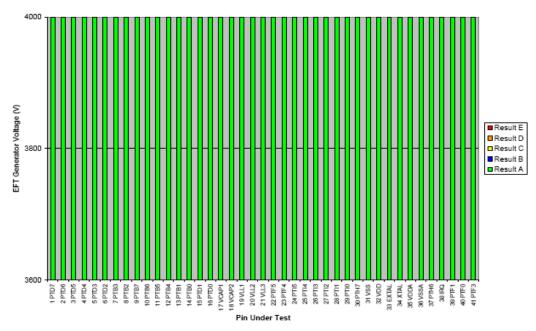

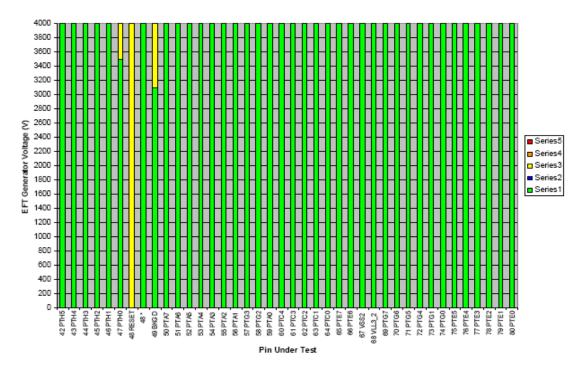

Microcontroller transient conducted susceptibility is measured in accordance with an internal Freescale test method. The measurement is performed with the microcontroller installed on a custom EMC evaluation board and running specialized EMC test software designed in compliance with the test method. The conducted susceptibility is determined by injecting the transient susceptibility signal on each pin of the microcontroller. The transient waveform and injection methodology is based on IEC 61000-4-4 (EFT/B). The transient voltage required to cause performance degradation on any pin in the tested configuration is greater than or equal to the reported levels unless otherwise indicated by footnotes below Table 20.

| Parameter                                                         | Symbol              | Conditions                                                     | f <sub>OSC</sub> /f <sub>BUS</sub> | Result  | Amplitude <sup>1</sup><br>(Min)                                     | Unit |

|-------------------------------------------------------------------|---------------------|----------------------------------------------------------------|------------------------------------|---------|---------------------------------------------------------------------|------|

| Conducted susceptibility, electrical fast transient/burst (EFT/B) | V <sub>CS_EFT</sub> | $V_{DD} = 5.5$<br>$T_A = +25$ °C<br>Package type = 80-pin LQFP | 4 kHz crystal<br>4 MHz bus         | A B C D | >4.0 <sup>2</sup><br>>4.0 <sup>3</sup><br>>4.0 <sup>4</sup><br>>4.0 | kV   |

Table 20. Conducted Susceptibility, EFT/B

## MC9S08LG32 Series Data Sheet, Rev. 9

Data based on qualification test results.

<sup>&</sup>lt;sup>1</sup> Data based on qualification test results. Not tested in production.

<sup>&</sup>lt;sup>2</sup> Exceptions as covered in footnotes 3 and 4.

- <sup>3</sup> Except pins PHT1, PTH2, PTH3, PTH4, PTH5. See figures below for values.

- <sup>4</sup> Except pins PTF3, PTH5, PTH4, PHT0, Reset, and BKGD. See figures below for values.

Individual performance of each pin is shown in Figure 27, Figure 28, Figure 29, and Figure 30.

Figure 27. 4 MHz, Positive Polarity Pins 1 - 41

#### Note:

RESET retested with 0.1 μF capacitor from pin to ground is Class A compliant as shown by 48\*.

Figure 28. 4 MHz, Positive Polarity Pins 42 – 80

MC9S08LG32 Series Data Sheet, Rev. 9

Figure 29. 4 MHz, Negative Polarity Pins 1 - 41

### Note:

RESET retested with 0.1 μF capacitor from pin to ground is Class A compliant as shown by 48\*.

Figure 30. 4 MHz, Negative Polarity Pins 42 – 80

# \*\* freescale

© FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.

ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED

IRECTLY FROM THE DOCUMENT CONTROL REPOSITORY. PRINTED VERSIONS

RE UNCONTROLLED EXCEPT WHEN STAMPED "CONTROLLED COPY" IN RED

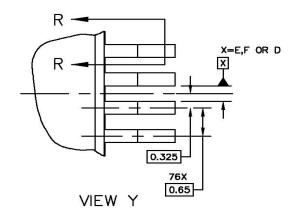

# MECHANICAL OUTLINES DICTIONARY

DO NOT SCALE THIS DRAWING

| DOCUMENT | NO: | 98ASS23237W |

|----------|-----|-------------|

|----------|-----|-------------|

PAGE: 917A REV: E

SECTION R-R ROTATED 90' CW

TITLE:

80 LD LQFP, 14 X 14 PKG, 0.65 MM PITCH, 1.4 THICK

CASE NUMBER: 917A-03

STANDARD: FREESCALE

PACKAGE CODE: 8258 SHEET: 2 OF 3

#### **Package Information**

| All transports                                                                                                                                                                                                                                           | MECHANICAL OUTLINES       | DOCUMENT NO: 98ASS23237W |      |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------------------|------|--|

| ** freescale semiconductor                                                                                                                                                                                                                               | DICTIONARY                | PAGE:                    | 917A |  |

| ◆ FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.<br>ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHICH ACCESSED<br>DIRECTLY FROM THE DOCUMENT CONTROL REPOSITORY. PRINTED VERSIONS<br>ARE UNCONTROLLED EXCEPT WHICH STAMPLE "CONTROLLED COPY" IN RED. | DO NOT SCALE THIS DRAWING | REV:                     | Е    |  |

#### NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 2. CONTROLLING DIMENSION: MILIMETER.

- 3. DATUM PLANE H IS LOCATED AT THE BOTTOM OF LEAD AND IS COINCIDENT WITH THE LEAD WHERE THE LEAD EXITS THE PLASTIC BODY AT THE BOTTOM OF THE PARTING LINE.

- 4. DATUM E, F AND D TO BE DETERMINED AT DATUM PLANE H.

5. DIMENSIONS TO BE DETERMINED AT SEATING PLANE C.

- DIMENSIONS DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25 PER SIDE. DIMENSIONS DO INCLUDE MOLD MISMATCH AND ARE DETERMINED AT DATUM PLANE H.

- DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED 0.46. MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD OR PROTRUSION 0.07.

TITLE:

80 LD LQFP, 14 X 14 PKG,

0.65 MM PITCH, 1.4 THICK

CASE NUMBER: 917A-03

STANDARD: FREESCALE

PACKAGE CODE: 8258 SHEET: 3 OF 3

Figure 33. 80-pin LQFP Package Drawing (Case 917A, Doc #98ASS23237W)

## **Package Information**

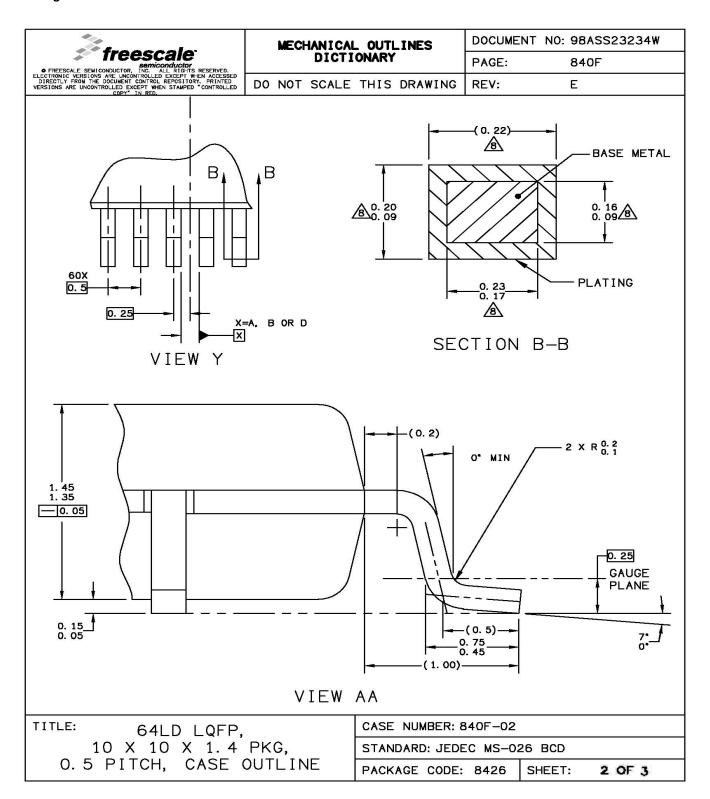

| fuences                                                                                                                                                                                                                     | MECHANICAL OUTLINES       | DOCUMENT NO: 98ASS23234W |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------------------|--|--|

| freescale   semiconductor  o Freescale Semiconductor, INC. ALL RIGHTS RESERVED.                                                                                                                                             | DICTIONARY                | PAGE: 840F               |  |  |

| ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED<br>DIRECTLY FROM THE DOCUMENT CONTROL REPOSITORY, PRINTED<br>VERSIONS ARE UNCONTROLLED EXCEPT WHEN STAMPED "CONTROLLED<br>DOWN TO BE STAMPED "CONTROLLED EXCEPT". | DO NOT SCALE THIS DRAWING | REV: E                   |  |  |

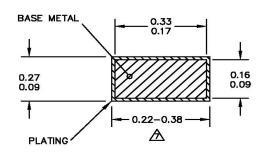

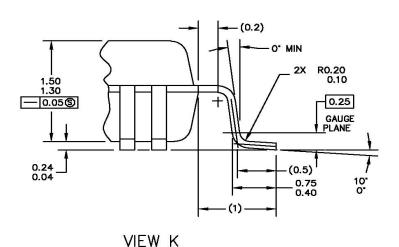

#### NOTES:

- 1. DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 3. DATUMS A, B AND D TO BE DETERMINED AT DATUM PLANE H.

A DIMENSIONS TO BE DETERMINED AT SEATING PLANE C.

THIS DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED THE UPPER LIMIT BY MORE THAN 0.08 mm AT MAXIMUM MATERIAL CONDITION. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD SHALL NOT BE LESS THAN 0.07 mm.

THIS DIMENSION DOES NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25 mm PER SIDE. THIS DIMENSION IS MAXIMUM PLASTIC BODY SIZE DIMENSION INCLUDING MOLD MISMATCH.

A EXACT SHAPE OF EACH CORNER IS OPTIONAL.

A THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.1 mm AND 0.25 mm FROM THE LEAD TIP.

TITLE: 64LD LQFP,

10 X 10 X 1. 4 PKG,

0. 5 PITCH, CASE OUTLINE

CASE NUMBER: 840F-02

STANDARD: JEDEC MS-026 BCD

PACKAGE CODE: 8426 SHEET: 3 OF 3

Figure 34. 64-pin LQFP Package Drawing (Case 840F, Doc #98ASS23234W)