Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                      |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | S08                                                         |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 40MHz                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                          |

| Peripherals                | LCD, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 53                                                          |

| Program Memory Size        | 32KB (32K x 8)                                              |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 1.9К х 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                 |

| Data Converters            | A/D 12x12b                                                  |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 105°C (TA)                                          |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 64-LQFP                                                     |

| Supplier Device Package    | 64-LQFP (10x10)                                             |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=s9s08lg32j0vlh |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Freescale Semiconductor, Inc. Data Sheet Addendum

Document Number: MC9S08LG32AD Rev. 0, 04/2015

# Addendum to Rev. 9 of the MC9S08LG32 Series Covers: MC9S08LG32 and MC9S08LG16

This addendum identifies changes to Rev. 9 of the MC9S08LG32 Series data sheet (covering MC9S08LG32 and MC9S08LG16). The changes described in this addendum have not been implemented in the specified pages.

# 1 Add min values for I<sub>IC</sub> (DC injection current)

Location: Table 8. DC Characteristics, Page 14

In Table 8, "DC Characteristics," add min values for  $I_{IC}$  (row number 14) as follows:

| Num | С |                                                                                    | Characteristic                                     | Symbol          | Min  | Typ <sup>1</sup> | Мах | Unit |

|-----|---|------------------------------------------------------------------------------------|----------------------------------------------------|-----------------|------|------------------|-----|------|

| 14  |   | DC injection<br>current <sup>5, 6, 7</sup>                                         | Single pin limit                                   | I <sub>IC</sub> | -0.2 |                  | 2   | mA   |

|     |   | V <sub>IN</sub> < V <sub>SS</sub> (min)<br>V <sub>IN</sub> > V <sub>DD</sub> (max) | Total MCU limit, includes sum of all stressed pins |                 | -5   | —                | 25  | mA   |

# 2 Change the max value of t<sub>LPO</sub> (low power oscillator period)

Location: Table 14. Control Timing, Page 29

In Table 14, "Control Timing," change the max value of  $t_{LPO}$  (row number 2) from 1300 to 1500 µs.

© 2015 Freescale Semiconductor, Inc. All rights reserved.

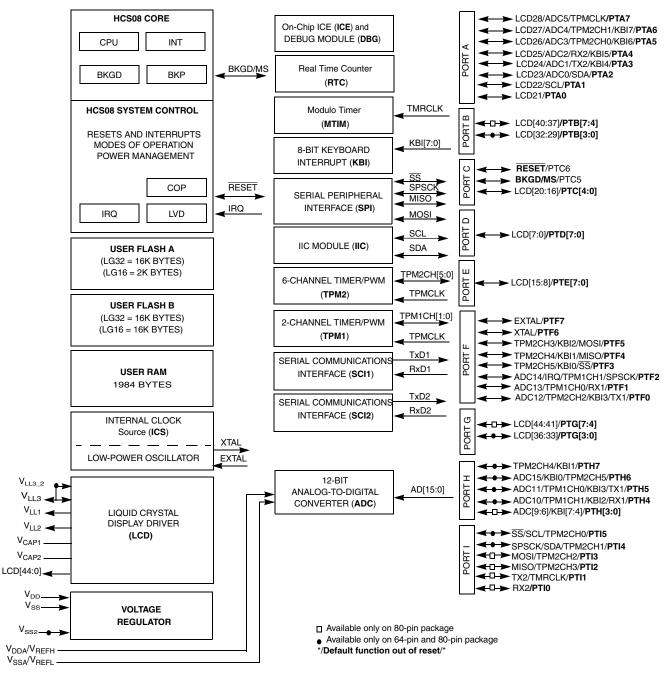

Figure 1. MC9S08LG32 Series Block Diagram

| Feature            | 1                | MC9S08LG32 MC9S08LG |                  |                  | 08LG16           |  |  |

|--------------------|------------------|---------------------|------------------|------------------|------------------|--|--|

| Flash size (bytes) |                  | 32,768              |                  | 18,              | 432              |  |  |

| RAM size (bytes)   |                  | 1984                |                  |                  |                  |  |  |

| Pin quantity       | 80               | 64                  | 48               | 64               | 48               |  |  |

| ADC                | 16 ch            | 12 ch               | 9 ch             | 12 ch            | 9 ch             |  |  |

| LCD                | 8 x 37<br>4 x 41 | 8 x 29<br>4 x 33    | 8 x 21<br>4 x 25 | 8 x 29<br>4 x 33 | 8 x 21<br>4 x 25 |  |  |

| ICE + DBG          |                  | •                   | yes              |                  |                  |  |  |

| ICS                | yes              |                     |                  |                  |                  |  |  |

| IIC                |                  | yes                 |                  |                  |                  |  |  |

| IRQ                |                  |                     | yes              |                  |                  |  |  |

| KBI                |                  |                     | 8 pin            |                  |                  |  |  |

| GPIOs              | 69               | 53                  | 39               | 53               | 39               |  |  |

| RTC                |                  |                     | yes              |                  |                  |  |  |

| MTIM               |                  |                     | yes              |                  |                  |  |  |

| SCI1               |                  |                     | yes              |                  |                  |  |  |

| SCI2               |                  |                     | yes              |                  |                  |  |  |

| SPI                |                  |                     | yes              |                  |                  |  |  |

| TPM1 channels      |                  |                     | 2                |                  |                  |  |  |

| TPM2 channels      |                  |                     | 6                |                  |                  |  |  |

| XOSC               |                  |                     | yes              |                  |                  |  |  |

Table 1. MC9S08LG32 Series Features by MCU and Package

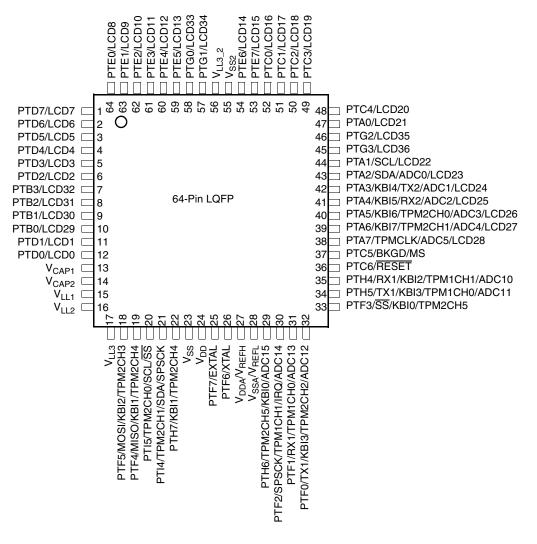

# 1 Pin Assignments

This section shows the pin assignments for the MC9S08LG32 series devices. The priority of functions on a pin is in ascending order from left to right and bottom to top. Another view of pinouts and function priority is given in Table 2.

#### **Pin Assignments**

#### Figure 3. 64-Pin LQFP

## NOTE

$V_{REFH}/V_{REFL}$  are internally connected to  $V_{DDA}/V_{SSA}$ .

**Pin Assignments**

|    | Packages |    |                   | < Lov             | west Priority: | > Highest |       |

|----|----------|----|-------------------|-------------------|----------------|-----------|-------|

| 80 | 64       | 48 | Port Pin          | Alt 1             | Alt 2          | Alt 3     | Alt 4 |

| 1  | 1        | 1  | PTD7              | LCD7              | —              | —         | _     |

| 2  | 2        | 2  | PTD6              | LCD6              | —              | —         | _     |

| 3  | 3        | 3  | PTD5              | LCD5              | —              | —         | _     |

| 4  | 4        | 4  | PTD4              | LCD4              | —              | —         | _     |

| 5  | 5        | 5  | PTD3              | LCD3              | —              | —         | _     |

| 6  | 6        | 6  | PTD2              | LCD2              | —              | —         | _     |

| 7  | 7        | —  | PTB3              | LCD32             | —              | —         | _     |

| 8  | 8        | _  | PTB2              | LCD31             | —              | —         |       |

| 9  | —        | —  | PTB7              | LCD40             | —              | —         | _     |

| 10 |          | _  | PTB6              | LCD39             | —              | —         |       |

| 11 | —        | —  | PTB5              | LCD38             |                | —         | _     |

| 12 | _        | _  | PTB4              | LCD37             | —              | —         | _     |

| 13 | 9        | —  | PTB1              | LCD30             | —              | —         | _     |

| 14 | 10       | _  | PTB0              | LCD29             | —              | —         | _     |

| 15 | 11       | 7  | PTD1              | LCD1              | —              | —         | _     |

| 16 | 12       | 8  | PTD0              | LCD0              | —              | —         | _     |

| 17 | 13       | 9  | V <sub>CAP1</sub> | —                 | —              | —         | _     |

| 18 | 14       | 10 | V <sub>CAP2</sub> | —                 | _              | —         | _     |

| 19 | 15       | 11 | V <sub>LL1</sub>  |                   | —              | —         | _     |

| 20 | 16       | 12 | V <sub>LL2</sub>  |                   | —              | —         | _     |

| 21 | 17       | 13 | V <sub>LL3</sub>  |                   | —              | —         | _     |

| 22 | 18       | 14 | PTF5              | MOSI              | KBI2           | TPM2CH3   | _     |

| 23 | 19       | 15 | PTF4              | MISO              | KBI1           | TPM2CH4   | _     |

| 24 | 20       | —  | PTI5              | TPM2CH0           | SCL            | SS        | _     |

| 25 | 21       | —  | PTI4              | TPM2CH1           | SDA            | SPSCK     | _     |

| 26 | —        | —  | PTI3              | TPM2CH2           | MOSI           | —         | _     |

| 27 | —        | —  | PTI2              | TPM2CH3           | MISO           | —         | _     |

| 28 | —        | —  | PTI1              | TMRCLK            | TX2            | —         | _     |

| 29 | —        | —  | PTI0              | RX2               |                | —         |       |

| 30 | 22       | —  | PTH7              | KBI1              | TPM2CH4        | —         | _     |

| 31 | 23       | 16 | V <sub>SS</sub>   |                   | —              | —         | _     |

| 32 | 24       | 17 | V <sub>DD</sub>   |                   | —              | —         | _     |

| 33 | 25       | 18 | PTF7              | EXTAL             | —              | —         | _     |

| 34 | 26       | 19 | PTF6              | XTAL              | —              | —         | _     |

| 35 | 27       | 20 | V <sub>DDA</sub>  | V <sub>REFH</sub> |                | —         | _     |

| 36 | 28       | 21 | V <sub>SSA</sub>  | V <sub>REFL</sub> | —              | —         | _     |

| 37 | 29       | —  | PTH6              | TPM2CH5           | KBI0           | ADC15     | _     |

| 38 | 30       | 22 | PTF2              | SPSCK             | TPM1CH1        | IRQ       | ADC14 |

# Table 2. Pin Availability by Package Pin-Count

|    | Packages |    |                    | < Lo    | west <b>Priority</b> : | > Highest |       |

|----|----------|----|--------------------|---------|------------------------|-----------|-------|

| 80 | 64       | 48 | Port Pin           | Alt 1   | Alt 2                  | Alt 3     | Alt 4 |

| 39 | 31       | 23 | PTF1               | RX1     | TPM1CH0                | ADC13     |       |

| 40 | 32       | 24 | PTF0               | TX1     | KBI3                   | TPM2CH2   | ADC12 |

| 41 | 33       | 25 | PTF3               | SS      | KBI0                   | TPM2CH5   | —     |

| 42 | 34       | —  | PTH5               | TX1     | KBI3                   | TPM1CH0   | ADC11 |

| 43 | 35       | —  | PTH4               | RX1     | KBI2                   | TPM1CH1   | ADC10 |

| 44 | —        | —  | PTH3               | KBI7    | ADC9                   | _         | —     |

| 45 | —        | —  | PTH2               | KBI6    | ADC8                   | —         | —     |

| 46 | —        | _  | PTH1               | KBI5    | ADC7                   |           |       |

| 47 | —        | —  | PTH0               | KBI4    | ADC6                   | —         | —     |

| 48 | 36       | 26 | PTC6               | RESET   | —                      |           |       |

| 49 | 37       | 27 | PTC5               | BKGD/MS | —                      | _         | —     |

| 50 | 38       | 28 | PTA7               | TPMCLK  | ADC5                   | LCD28     |       |

| 51 | 39       | 29 | PTA6               | KBI7    | TPM2CH1                | ADC4      | LCD27 |

| 52 | 40       | 30 | PTA5               | KBI6    | TPM2CH0                | ADC3      | LCD26 |

| 53 | 41       | 31 | PTA4               | KBI5    | RX2                    | ADC2      | LCD25 |

| 54 | 42       | 32 | PTA3               | KBI4    | TX2                    | ADC1      | LCD24 |

| 55 | 43       | 33 | PTA2               | SDA     | ADC0                   | LCD23     | —     |

| 56 | 44       | 34 | PTA1               | SCL     | LCD22                  | —         | —     |

| 57 | 45       | —  | PTG3               | LCD36   | —                      | _         | —     |

| 58 | 46       | —  | PTG2               | LCD35   | —                      | —         | —     |

| 59 | 47       | 35 | PTA0               | LCD21   | —                      | —         | —     |

| 60 | 48       | 36 | PTC4               | LCD20   | —                      | —         | —     |

| 61 | 49       | 37 | PTC3               | LCD19   | —                      | —         | —     |

| 62 | 50       | 38 | PTC2               | LCD18   | —                      | —         | —     |

| 63 | 51       | 39 | PTC1               | LCD17   | —                      | —         | —     |

| 64 | 52       | 40 | PTC0               | LCD16   | —                      | —         | —     |

| 65 | 53       | 41 | PTE7               | LCD15   | —                      |           |       |

| 66 | 54       | 42 | PTE6               | LCD14   |                        |           |       |

| 67 | 55       | —  | V <sub>SS2</sub>   | _       | —                      | —         | —     |

| 68 | 56       | —  | V <sub>LL3_2</sub> |         |                        | —         | —     |

| 69 | —        | —  | PTG7               | LCD44   | —                      | —         | —     |

| 70 | —        | —  | PTG6               | LCD43   | —                      | _         | —     |

| 71 | —        | —  | PTG5               | LCD42   | —                      | _         | —     |

| 72 | —        | —  | PTG4               | LCD41   | —                      |           | —     |

| 73 | 57       | —  | PTG1               | LCD34   | —                      | _         | —     |

| 74 | 58       | —  | PTG0               | LCD33   | —                      |           | —     |

| 75 | 59       | 43 | PTE5               | LCD13   | —                      |           | —     |

| 76 | 60       | 44 | PTE4               | LCD12   | —                      |           | —     |

# Table 2. Pin Availability by Package Pin-Count (continued)

| No. | Rating <sup>1</sup>                        | Symbol           | Min  | Max | Unit |

|-----|--------------------------------------------|------------------|------|-----|------|

| 1   | Human body model (HBM)                     | V <sub>HBM</sub> | 2500 | _   | V    |

| 2   | Charge device model (CDM)                  | V <sub>CDM</sub> | 750  | _   | V    |

| 3   | Latch-up current at $T_A = 85 \ ^{\circ}C$ | I <sub>LAT</sub> | ±100 |     | mA   |

Table 7. ESD and Latch-Up Protection Characteristics

Parameter is achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted.

# 2.6 DC Characteristics

This section includes information about power supply requirements and I/O pin characteristics.

| Num | С | Characteristic                                                                               | Symbol             | Min                    | Typ <sup>1</sup> | Max                  | Unit |

|-----|---|----------------------------------------------------------------------------------------------|--------------------|------------------------|------------------|----------------------|------|

| 1   | — | Operating Voltage                                                                            | —                  | 2.7                    | _                | 5.5                  | V    |

| 2   | Ρ | Output high voltage — Low Drive (PTxDSn = 0)<br>5 V, ILoad = -2 mA<br>3 V, ILoad = -0.6 mA   | V <sub>OH</sub>    | Vdd - 0.8<br>Vdd - 0.8 | _                |                      | V    |

|     |   | Output high voltage — High Drive (PTxDSn = 1) V<br>5 V, ILoad = -10 mA<br>3 V, ILoad = -3 mA |                    | Vdd – 0.8<br>Vdd – 0.8 |                  |                      |      |

| 3   | Ρ | Output low voltage — Low Drive (PTxDSn = 0)<br>5 V, ILoad = 2 mA<br>3 V, ILoad = 0.6 mA      | V <sub>OL</sub>    | —                      |                  | 0.8<br>0.8           | V    |

|     |   | Output low voltage — High Drive (PTxDSn = 1)<br>5 V, ILoad = 10 mA<br>3 V, ILoad = 3 mA      |                    |                        | _                | 0.8<br>0.8           |      |

| 4   | Ρ | Output high current — Max total I <sub>OH</sub> for all ports<br>5 V<br>3 V                  | I <sub>ОНТ</sub>   | _                      | _                | 100<br>60            | mA   |

| 5   | С | Output high current — Max total I <sub>OL</sub> for all ports<br>5 V<br>3 V                  |                    | _                      | _                | 100<br>60            | mA   |

| 6   | Ρ | Bandgap voltage reference                                                                    | V <sub>BG</sub>    | —                      | 1.225            |                      | V    |

| 7   | Ρ | Input high voltage; all digital inputs                                                       | V <sub>IH</sub>    | 0.65 x V <sub>DD</sub> | _                |                      | V    |

| 8   | Ρ | Input low voltage; all digital inputs                                                        | V <sub>IL</sub>    | _                      |                  | $0.35 \times V_{DD}$ | V    |

| 9   | Ρ | Input hysteresis; all digital inputs                                                         | V <sub>hys</sub>   | 0.06 x V <sub>DD</sub> | _                |                      | mV   |

| 10  | Ρ | Input leakage current; input only pins <sup>2</sup> $V_{In} = V_{DD}$ or $V_{SS}$            | <sub>In</sub>      | —                      | 0.1              | 1                    | μA   |

| 11  | Ρ | High impedence (off-state) leakage current $V_{In} = V_{DD}$ or $V_{SS}$                     | ll <sub>oz</sub> l | —                      | 0.1              | 1                    | μA   |

| 12  | Ρ | Internal pullup resistors <sup>3</sup>                                                       | R <sub>PU</sub>    | 20                     | 45               | 65                   | kΩ   |

| 13  | Ρ | Internal pulldown resistors <sup>4</sup>                                                     | R <sub>PD</sub>    | 20                     | 45               | 65                   | kΩ   |

## Table 8. DC Characteristics

# 2.7 Supply Current Characteristics

This section includes information about power supply current in various operating modes.

| Num | с | Parameter                                  | Symbol            | Bus<br>Freq | V <sub>DD</sub><br>(V) | Typ <sup>1</sup> | Max   | Unit | Temp<br>(°C)    |

|-----|---|--------------------------------------------|-------------------|-------------|------------------------|------------------|-------|------|-----------------|

| 1   | С | Run supply current                         | RI <sub>DD</sub>  | 20 MHz      | 3                      | 16.38            | 27.85 | mA   | –40 °C to 85 °C |

|     | С | FEI mode, all modules on                   |                   |             |                        |                  | 28.05 |      | –40 °C to105 °C |

|     | С |                                            |                   | 1 MHz       |                        | 1.67             | 2.84  |      | –40 °C to 85 °C |

|     | С |                                            |                   |             |                        |                  | 2.87  |      | –40 °C to105 °C |

|     | Р |                                            |                   | 20 MHz      | 5                      | 16.55            | 28.14 | mA   | –40 °C to 85 °C |

|     | Ρ |                                            |                   |             |                        |                  | 28.35 |      | –40 °C to105 °C |

|     | С |                                            |                   | 1 MHz       |                        | 1.77             | 3.01  |      | –40 °C to 85 °C |

|     | С |                                            |                   |             |                        |                  | 3.05  |      | –40 °C to105 °C |

| 2   | Т | Run supply current                         | RI <sub>DD</sub>  | 20 MHz      | 3                      | 11.9             | 20.25 | mA   | –40 °C to 85 °C |

|     | Т | FEI mode, all modules off                  |                   |             |                        |                  | 21.72 |      | –40 °C to105 °C |

|     | Т |                                            |                   | 1 MHz       |                        | 1.16             | 1.95  |      | –40 °C to 85 °C |

|     | Т |                                            |                   |             |                        |                  | 1.98  |      | –40 °C to105 °C |

|     | Т |                                            |                   | 20 MHz      | 5                      | 12.68            | 21.56 | mA   | –40 °C to 85 °C |

|     | Т |                                            |                   |             |                        |                  | 23.12 |      | –40 °C to105 °C |

|     | Т |                                            |                   | 1 MHz       |                        | 1.4              | 2.39  |      | –40 °C to 85 °C |

|     | Т |                                            |                   |             |                        |                  | 2.41  |      | –40 °C to105 °C |

| 3   | Т | Wait mode supply current                   | WI <sub>DD</sub>  | 20 MHz      | 3                      | 7.9              | 13.42 | mA   | –40 °C to 85 °C |

|     | Т | FEI mode, all modules off                  |                   |             |                        |                  | 13.59 |      | –40 °C to105 °C |

|     | Т |                                            |                   | 1 MHz       |                        | 0.88             | 1.49  |      | –40 °C to 85 °C |

|     | Т |                                            |                   |             |                        |                  | 1.51  |      | –40 °C to105 °C |

|     | Р |                                            |                   | 20 MHz      | 5                      | 8.13             | 13.81 | mA   | –40 °C to 85 °C |

|     | Р |                                            |                   |             |                        |                  | 13.98 |      | –40 °C to105 °C |

|     | Т |                                            |                   | 1 MHz       |                        | 1.12             | 1.91  |      | –40 °C to 85 °C |

|     | Т |                                            |                   |             |                        |                  | 1.94  |      | –40 °C to105 °C |

| 4   | С | Stop2 mode supply current                  | S2I <sub>DD</sub> | n/a         | 3                      | 1.1              | 16.0  | μA   | –40 °C to 85 °C |

|     | С |                                            |                   |             |                        |                  | 39.0  |      | –40 °C to105 °C |

|     | Р |                                            |                   |             | 5                      | 1.2              | 18.7  | μA   | –40 °C to 85 °C |

|     | Р |                                            |                   |             |                        |                  | 46.1  |      | –40 °C to105 °C |

| 5   | С | Stop3 mode supply current No clocks active | S3I <sub>DD</sub> | n/a         | 3                      | 1.2              | 22.4  | μA   | –40 °C to 85 °C |

|     | С | INU GOURS ACTIVE                           |                   |             |                        |                  | 56.2  |      | –40 °C to105 °C |

|     | Р |                                            |                   |             | 5                      | 1.32             | 25.5  | μA   | –40 °C to 85 °C |

|     | Р |                                            |                   |             |                        |                  | 63.9  |      | –40 °C to105 °C |

## Table 9. Supply Current Characteristics

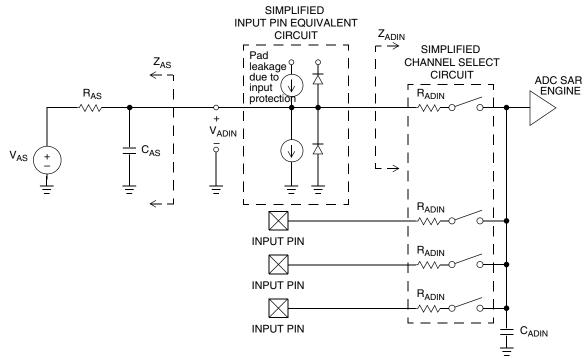

| Characteristic              | Conditions                                                          | Symb              | Min | Typ <sup>1</sup> | Max     | Unit | Comment         |

|-----------------------------|---------------------------------------------------------------------|-------------------|-----|------------------|---------|------|-----------------|

| Input<br>Resistance         | _                                                                   | R <sub>ADIN</sub> | —   | 5                | 7       | kΩ   | _               |

| Analog Source<br>Resistance | 12-bit mode<br>f <sub>ADCK</sub> > 4MHz<br>f <sub>ADCK</sub> < 4MHz | R <sub>AS</sub>   | _   |                  | 2<br>5  | kΩ   | External to MCU |

|                             | 10-bit mode<br>f <sub>ADCK</sub> > 4MHz<br>f <sub>ADCK</sub> < 4MHz |                   |     |                  | 5<br>10 |      |                 |

|                             | 8-bit mode (all valid f <sub>ADCK</sub> )                           |                   | _   |                  | 10      |      |                 |

| ADC                         | High Speed (ADLPC = 0)                                              | f <sub>ADCK</sub> | 0.4 | _                | 8.0     | MHz  | —               |

| Conversion<br>Clock Freq.   | Low Power (ADLPC = 1)                                               |                   | 0.4 | _                | 4.0     |      |                 |

Table 12. 12-bit ADC Operating Conditions (continued)

<sup>1</sup> Typical values assume V<sub>DDAD</sub> = 5.0 V, Temp = 25 °C, f<sub>ADCK</sub> = 1.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

<sup>2</sup> DC potential difference.

Figure 18. ADC Input Impedance Equivalency Diagram

|     |       |                        |                 |                     | -   |                  | -    |                  |                            |

|-----|-------|------------------------|-----------------|---------------------|-----|------------------|------|------------------|----------------------------|

| Num | с     | Characteristic         | Conditions      | Symb                | Min | Typ <sup>1</sup> | Max  | Unit             | Comment                    |

| 13  | Т     | Full-Scale             | 12-bit mode     | E <sub>FS</sub>     | _   | ±1               | _    | LSB <sup>2</sup> | $V_{ADIN} = V_{DDAD}$      |

|     | Р     | Error                  | 10-bit mode     |                     | _   | ±0.5             | ±1   |                  |                            |

|     | Т     |                        | 8-bit mode      |                     |     | ±0.5             | ±0.5 |                  |                            |

| 14  | D     | Quantization           | 12-bit mode     | EQ                  |     | -1 to 0          |      | LSB <sup>2</sup> | _                          |

|     | Error | 10-bit mode            |                 |                     |     | ±0.5             |      |                  |                            |

|     |       |                        | 8-bit mode      |                     |     |                  | ±0.5 |                  |                            |

| 15  | D     | Input Leakage          | 12-bit mode     | E <sub>IL</sub>     |     | ±1               |      | LSB <sup>2</sup> | Pad leakage <sup>4</sup> * |

|     |       | Error                  | 10-bit mode     |                     |     | ±0.2             | ±2.5 |                  | R <sub>AS</sub>            |

|     |       |                        | 8-bit mode      |                     |     | ±0.1             | ±1   |                  |                            |

| 16  | С     | Temp Sensor            | –40 °C to 25 °C | m                   | _   | 1.646            | _    | mV/°C            | —                          |

|     | Slope | Slope                  | 25 °C to 125°C  |                     | _   | 1.769            | _    |                  |                            |

| 17  | С     | Temp Sensor<br>Voltage | 25 °C           | V <sub>TEMP25</sub> | _   | 701.2            | _    | mV               |                            |

# Table 13. 12-bit ADC Characteristics ( $V_{REFH} = V_{DDAD}$ , $V_{REFL} = V_{SSAD}$ ) (continued)

<sup>1</sup> Typical values assume V<sub>DDAD</sub> = 5.0 V, Temp = 25 °C, f<sub>ADCK</sub> = 1.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

<sup>2</sup> 1 LSB =  $(V_{\text{REFH}} - V_{\text{REFL}})/2^N$

<sup>3</sup> Monotonicity and no-missing-codes guaranteed in 10-bit and 8-bit modes

<sup>4</sup> Based on input pad leakage current. Refer to pad electricals.

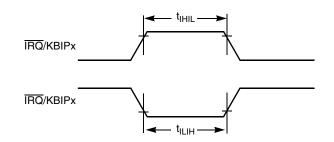

Figure 20. IRQ/KBIPx Timing

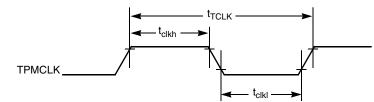

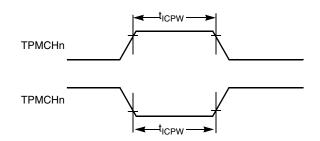

# 2.11.2 TPM Module Timing

Synchronizer circuits determine the shortest input pulses that can be recognized or the fastest clock that can be used as the optional external source to the timer counter. These synchronizers operate from the current bus rate clock.

| No. | С | Function                  | Symbol            | Min | Max                 | Unit             |

|-----|---|---------------------------|-------------------|-----|---------------------|------------------|

| 1   | D | External clock frequency  | f <sub>TCLK</sub> | 0   | f <sub>Bus</sub> /4 | Hz               |

| 2   | D | External clock period     | t <sub>TCLK</sub> | 4   | _                   | t <sub>cyc</sub> |

| 3   | D | External clock high time  | t <sub>clkh</sub> | 1.5 | _                   | t <sub>cyc</sub> |

| 4   | D | External clock low time   | t <sub>clkl</sub> | 1.5 | _                   | t <sub>cyc</sub> |

| 5   | D | Input capture pulse width | t <sub>ICPW</sub> | 1.5 | _                   | t <sub>cyc</sub> |

Table 15. TPM Input Timing

Figure 21. Timer External Clock

Figure 22. Timer Input Capture Pulse

# 2.11.3 SPI Timing

Table 16 and Figure 23 through Figure 26 describe the timing requirements for the SPI system.

| No.  | С | Function                                          | Symbol                             | Min                              | Max                                        | Unit                                   |

|------|---|---------------------------------------------------|------------------------------------|----------------------------------|--------------------------------------------|----------------------------------------|

| _    | D | Operating frequency<br>Master<br>Slave            | f <sub>op</sub>                    | f <sub>Bus</sub> /2048<br>0      | f <sub>Bus</sub> /2<br>f <sub>Bus</sub> /4 | Hz                                     |

| 1    | D | SPSCK period<br>Master<br>Slave                   | t <sub>SPSCK</sub>                 | 2<br>4                           | 2048<br>—                                  | t <sub>cyc</sub><br>t <sub>cyc</sub>   |

| 2    | D | Enable lead time<br>Master<br>Slave               | t <sub>Lead</sub>                  | 1/2<br>1                         |                                            | t <sub>SPSCK</sub><br>t <sub>cyc</sub> |

| 3    | D | Enable lag time<br>Master<br>Slave                | t <sub>Lag</sub>                   | 1/2<br>1                         |                                            | t <sub>SPSCK</sub><br>t <sub>cyc</sub> |

| 4    | D | Clock (SPSCK) high or low time<br>Master<br>Slave | twspsck                            | $t_{cyc} - 30$<br>$t_{cyc} - 30$ | 1024 t <sub>cyc</sub>                      | ns<br>ns                               |

| 5    | D | Data setup time (inputs)<br>Master<br>Slave       | t <sub>SU</sub>                    | 15<br>15                         |                                            | ns<br>ns                               |

| 6    | D | Data hold time (inputs)<br>Master<br>Slave        | t <sub>HI</sub>                    | 0<br>25                          |                                            | ns<br>ns                               |

| 7    | D | Slave access time                                 | t <sub>a</sub>                     | —                                | 1                                          | t <sub>cyc</sub>                       |

| 8    | D | Slave MISO disable time                           | t <sub>dis</sub>                   | _                                | 1                                          | t <sub>cyc</sub>                       |

| 9    | D | Data valid (after SPSCK edge)<br>Master<br>Slave  | t <sub>v</sub>                     |                                  | 25<br>25                                   | ns<br>ns                               |

| (10) | D | Data hold time (outputs)<br>Master<br>Slave       | t <sub>HO</sub>                    | 0<br>0                           |                                            | ns<br>ns                               |

| (1)  | D | Rise time<br>Input<br>Output                      | t <sub>RI</sub><br>t <sub>RO</sub> |                                  | t <sub>cyc</sub> – 25<br>25                | ns<br>ns                               |

| (12) | D | Fall time<br>Input<br>Output                      | t <sub>FI</sub><br>t <sub>FO</sub> | —                                | t <sub>cyc</sub> – 25<br>25                | ns<br>ns                               |

# Table 16. SPI Timing

# 2.12 LCD Specifications

Table 17. LCD Electricals, 3 V Glass

| С | Characteristic              | Symbol             | Min | Тур  | Мах  | Units |

|---|-----------------------------|--------------------|-----|------|------|-------|

| D | VLL3 Supply Voltage         | VLL3               | 2.7 | _    | 5.5  | V     |

| D | LCD Frame Frequency         | f <sub>Frame</sub> | 28  | 30   | 64   | Hz    |

| D | LCD Charge Pump Capacitance | C <sub>LCD</sub>   | —   | 100  | 100  | pF    |

| D | LCD Bypass Capacitance      | C <sub>BYLCD</sub> | —   | 100  | 100  |       |

| D | LCD Glass Capacitance       | C <sub>glass</sub> | _   | 2000 | 8000 |       |

# 2.13 Flash Specifications

This section provides details about program/erase times and program-erase endurance for the flash memory.

Program and erase operations do not require any special power sources other than the normal  $V_{DD}$  supply. For more detailed information about program/erase operations, see the Memory section.

| С | Characteristic                                                                                            | Symbol                  | Min     | Typical     | Мах               | Unit              |

|---|-----------------------------------------------------------------------------------------------------------|-------------------------|---------|-------------|-------------------|-------------------|

| D | Supply voltage for program/erase<br>-40 °C to 85 °C                                                       | V <sub>prog/erase</sub> | 2.7 5.5 |             | V                 |                   |

| D | Supply voltage for read operation                                                                         | V <sub>Read</sub>       | 2.7     |             | 5.5               | V                 |

| D | Internal FCLK frequency <sup>1</sup>                                                                      | f <sub>FCLK</sub>       | 150     |             | 200               | kHz               |

| D | Internal FCLK period (1/FCLK)                                                                             | t <sub>Fcyc</sub>       | 5       |             | 6.67              | μs                |

| С | C Byte program time (random location) <sup>2</sup>                                                        |                         | 9       |             |                   | t <sub>Fcyc</sub> |

| С | Byte program time (burst mode) <sup>2</sup>                                                               | t <sub>Burst</sub>      | 4       |             | t <sub>Fcyc</sub> |                   |

| С | Page erase time <sup>2</sup>                                                                              | t <sub>Page</sub>       | 4000    |             | t <sub>Fcyc</sub> |                   |

| С | Mass erase time <sup>2</sup>                                                                              | t <sub>Mass</sub>       | 20,000  |             |                   | t <sub>Fcyc</sub> |

| D | Byte program current <sup>3</sup>                                                                         | R <sub>IDDBP</sub>      | _       | 4           | —                 | mA                |

| D | Page erase current <sup>3</sup>                                                                           | R <sub>IDDPE</sub>      | _       | 6           | —                 | mA                |

| с | Program/erase endurance <sup>4</sup><br>T <sub>L</sub> to T <sub>H</sub> = -40 °C to + 85 °C<br>T = 25 °C |                         | 10,000  | <br>100,000 |                   | cycles            |

| С | Data retention <sup>5</sup>                                                                               | t <sub>D_ret</sub>      | 15      | 100         | —                 | years             |

Table 18. Flash Characteristics

<sup>1</sup> The frequency of this clock is controlled by a software setting.

<sup>2</sup> These values are hardware state machine controlled. User code does not need to count cycles. This information supplied for calculating approximate time to program and erase.

<sup>3</sup> The program and erase currents are additional to the standard run  $I_{DD}$ . These values are measured at room temperatures with  $V_{DD} = 5.0 \text{ V}$ , bus frequency = 4.0 MHz.

<sup>4</sup> Typical endurance for flash was evaluated for this product family on the 9S12Dx64. For additional information on how Freescale defines typical endurance, please refer to *Engineering Bulletin EB619, Typical Endurance for Nonvolatile Memory.*

<sup>5</sup> Typical data retention values are based on intrinsic capability of the technology measured at high temperature and de-rated to 25 °C using the Arrhenius equation. For additional information on how Freescale defines typical data retention, please refer to *Engineering Bulletin EB618, Typical Data Retention for Nonvolatile Memory.*

# 2.14 EMC Performance

Electromagnetic compatibility (EMC) performance is highly dependant on the environment in which the MCU resides. Board design and layout, circuit topology choices, location and characteristics of external components as well as MCU software operation all play a significant role in EMC performance. The system designer should consult Freescale applications notes such as AN2321, AN1050, AN1263, AN2764, and AN1259 for advice and guidance specifically targeted at optimizing EMC performance.

# 2.14.1 Radiated Emissions

Microcontroller radiated RF emissions are measured from 150 kHz to 1 GHz using the TEM/GTEM cell method in accordance with the IEC 61967-2 and SAE J1752/3 standards. The measurement is performed with the microcontroller installed on a custom EMC evaluation board while running specialized EMC test software. The radiated emissions from the microcontroller are measured in a TEM cell in two package orientations (North and East).

The maximum radiated RF emissions of the tested configuration in all orientations are less than or equal to the reported emissions levels.

| Parameter           | Symbol | Conditions    | Frequency      | f <sub>OSC</sub> /f <sub>BUS</sub> | Level <sup>1</sup><br>(Max) | Unit |

|---------------------|--------|---------------|----------------|------------------------------------|-----------------------------|------|

| Radiated emissions, |        | 4 MHz crystal | 10             | dBμV                               |                             |      |

| electric field      |        |               | 50 – 150 MHz   | 16 MHz bus                         | 14                          |      |

| 80 LQFP             |        | 150 – 500 MHz |                | 8                                  |                             |      |

|                     |        |               | 500 – 1000 MHz |                                    | 5                           |      |

|                     |        |               | IEC Level      |                                    | L                           | —    |

|                     |        | SAE Level     |                | 2                                  | —                           |      |

Table 19. Radiated Emissions, Electric Field

<sup>1</sup> Data based on qualification test results.

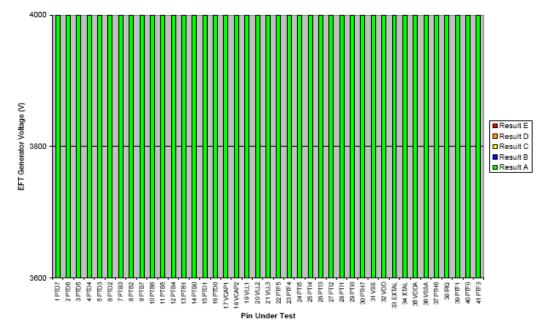

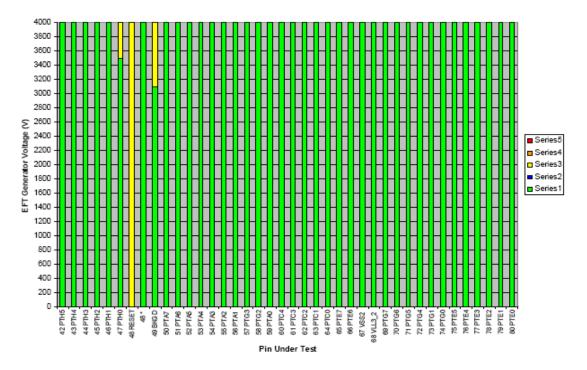

# 2.14.2 Conducted Transient Susceptibility

Microcontroller transient conducted susceptibility is measured in accordance with an internal Freescale test method. The measurement is performed with the microcontroller installed on a custom EMC evaluation board and running specialized EMC test software designed in compliance with the test method. The conducted susceptibility is determined by injecting the transient susceptibility signal on each pin of the microcontroller. The transient waveform and injection methodology is based on IEC 61000-4-4 (EFT/B). The transient voltage required to cause performance degradation on any pin in the tested configuration is greater than or equal to the reported levels unless otherwise indicated by footnotes below Table 20.

| Table 20. | Conducted | Susceptibility, | EFT/B |

|-----------|-----------|-----------------|-------|

|-----------|-----------|-----------------|-------|

| Parameter                            | Symbol              | Conditions                 | f <sub>OSC</sub> /f <sub>BUS</sub> | Result | Amplitude <sup>1</sup><br>(Min) | Unit |

|--------------------------------------|---------------------|----------------------------|------------------------------------|--------|---------------------------------|------|

| Conducted susceptibility, electrical | V <sub>CS EFT</sub> | V <sub>DD</sub> = 5.5      | 4 kHz crystal                      | А      | >4.0 <sup>2</sup>               | kV   |

| fast transient/burst (EFT/B)         |                     | $T_{A} = +25  {}^{\circ}C$ | 4 MHz bus                          | В      | >4.0 <sup>3</sup>               |      |

|                                      |                     | Package type = 80-pin LQFP |                                    | С      | >4.0 <sup>4</sup>               |      |

|                                      |                     |                            |                                    | D      | >4.0                            |      |

<sup>1</sup> Data based on qualification test results. Not tested in production.

<sup>2</sup> Exceptions as covered in footnotes 3 and 4.

#### Note:

RESET retested with 0.1  $\mu$ F capacitor from pin to ground is Class A compliant as shown by 48\*. Figure 30. 4 MHz, Negative Polarity Pins 42 – 80

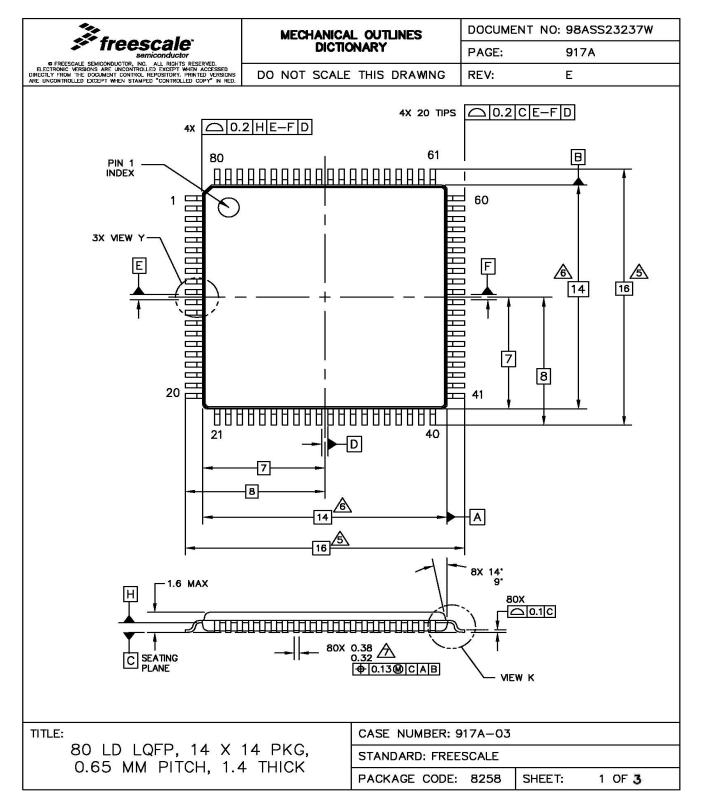

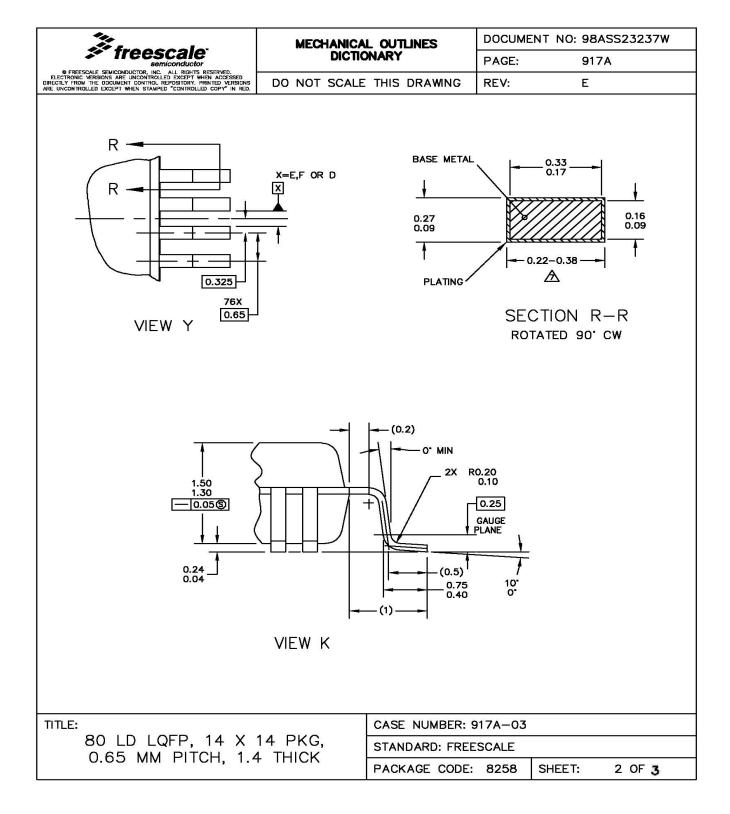

Package Information

# 4.1.1 80-pin LQFP

#### **Package Information**

**Package Information**

#### **Package Information**

|                                                                                                                                                                                                                                                           | MECHANICAL OUTLINES                                   | DOCUMENT NO: 98ASS23234W                           |                                |                                                |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------|--------------------------------|------------------------------------------------|--|--|--|--|

| • FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.                                                                                                                                                                                                      | DICTIONARY                                            |                                                    | PAGE:                          | 840F                                           |  |  |  |  |

| • FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.<br>ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED<br>DIRECTLY FROM THE DOCUMENT CONTROL REPOSITORY, FRINTED<br>VERSIONS ARE UNCONTROLLED EXCEPT WHEN STAMPED *CONTROLLED<br>COPY" IN RED. | DO NOT SCALE                                          | THIS DRAWING                                       | REV:                           | E                                              |  |  |  |  |

| NOTES:                                                                                                                                                                                                                                                    |                                                       |                                                    |                                |                                                |  |  |  |  |

| 1. DIMENSIONS ARE IN MILLIMETERS.                                                                                                                                                                                                                         |                                                       |                                                    |                                |                                                |  |  |  |  |

| 2. DIMENSIONING AND TO                                                                                                                                                                                                                                    | 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994. |                                                    |                                |                                                |  |  |  |  |

| 3. DATUMS A, B AND D TO                                                                                                                                                                                                                                   | D BE DETERMINE                                        | D AT DATUM PLA                                     | NE H.                          |                                                |  |  |  |  |

| A DIMENSIONS TO BE DE                                                                                                                                                                                                                                     | FERMINED AT SE                                        | ATING PLANE C.                                     |                                |                                                |  |  |  |  |

| THIS DIMENSION DOES<br>PROTRUSION SHALL NO<br>BY MORE THAN 0.08 mr<br>LOCATED ON THE LOWER<br>PROTRUSION AND ADJAC                                                                                                                                        | 「 CAUSE THE LE<br>n AT MAXIMUM M<br>₹ RADIUS OR TH    | AD WIDTH TO EX<br>ATERIAL CONDIT<br>E FOOT. MINIMU | CEED TH<br>ION. DA<br>JM SPACE | HE UPPER LIMIT<br>AMBAR CANNOT BE<br>E BETWEEN |  |  |  |  |

| THIS DIMENSION DOES<br>IS 0.25 mm PER SIDE.<br>DIMENSION INCLUDING                                                                                                                                                                                        | THIS DIMENSI                                          | ON IS MAXIMUM                                      |                                |                                                |  |  |  |  |

| $\triangle$ exact shape of each                                                                                                                                                                                                                           | CORNER IS OPT                                         | IONAL.                                             |                                |                                                |  |  |  |  |

| A THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN<br>0.1 mm AND 0.25 mm FROM THE LEAD TIP.                                                                                                                                                 |                                                       |                                                    |                                |                                                |  |  |  |  |

|                                                                                                                                                                                                                                                           |                                                       |                                                    |                                |                                                |  |  |  |  |

| TITLE: 64LD LQFP,                                                                                                                                                                                                                                         |                                                       | CASE NUMBER: 8                                     | 840F-02                        |                                                |  |  |  |  |

| 10 X 10 X 1.4                                                                                                                                                                                                                                             |                                                       | STANDARD: JEDE                                     | C MS-02                        |                                                |  |  |  |  |

| 0.5 PITCH, CASE                                                                                                                                                                                                                                           | JUILINE                                               | PACKAGE CODE:                                      | 8426                           | SHEET: 3 OF 3                                  |  |  |  |  |

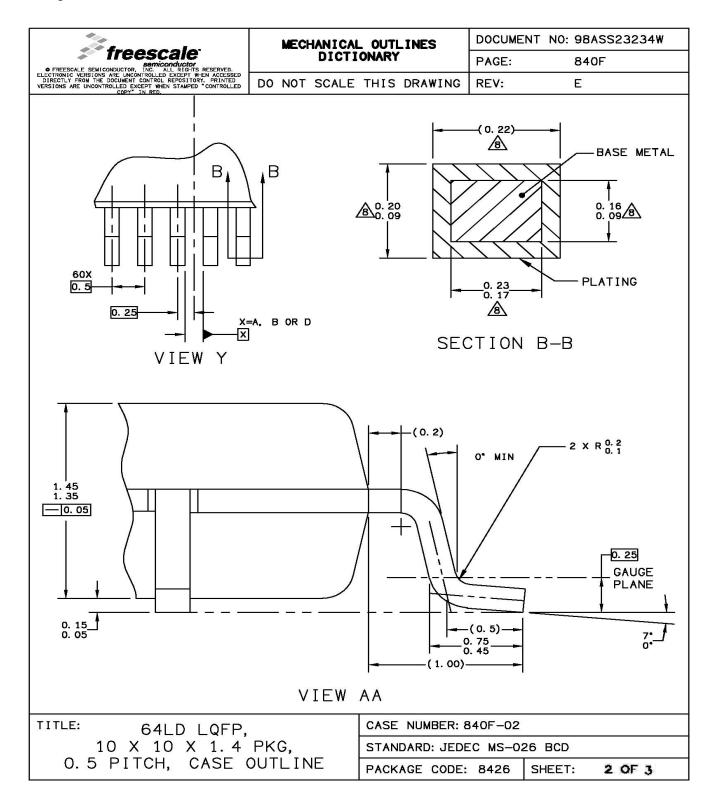

Figure 34. 64-pin LQFP Package Drawing (Case 840F, Doc #98ASS23234W)

**Revision History**

# 5 Revision History

To provide the most up-to-date information, the revision of our documents on the World Wide Web are the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

http://www.freescale.com

The following revision history table summarizes changes contained in this document.

### Table 24. Revision History

| Revision | Date    | Description of Changes                                                                                                                                                                                                                                         |

|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | 8/2008  | First Initial release.                                                                                                                                                                                                                                         |

| 2        | 9/2008  | Second Initial Release.                                                                                                                                                                                                                                        |

| 3        | 11/2008 | Alpha Customer Release.                                                                                                                                                                                                                                        |

| 4        | 2/2009  | Launch Release.                                                                                                                                                                                                                                                |

| 5        | 4/2009  | Added EMC Radiated Emission and Transient Susceptibility data in Table 19 and Table 20.                                                                                                                                                                        |

| 6        | 4/2009  | Updated EMC performance data.                                                                                                                                                                                                                                  |

| 7        | 8/2009  | Updated auto part numbers, changed TCLK, T0CH0, T0CH1, T1CH0, T1CH1, T1CH2, T1CH3, T1CH3, T1CH3, T1CH4, and T1CH5 to TPMCLK, TPM0CH0, TPM0CH1, TPM1CH0, TPM1CH1, TPM1CH2, TPM1CH3, TPM1CH4, and TPM1CH5, and changed the maximum LCD frame frequency to 64 Hz. |

| 8        | 8/2011  | Updated Table "ICS Frequency Specifications (Temperature Range = $-40 \times C$ to $105 \times C$ Ambient)". Changed the value of row 8 column C from C to P.                                                                                                  |

| 9        | 9/2011  | Updated Table "ICS Frequency Specifications (Temperature Range = $-40 \times C$ to $105 \times C$<br>Ambient)". Removed Footnote from Row 8.<br>Updated the Revision History                                                                                   |