Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡X/EI

| Product Status             | Obsolete                                                                       |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | F <sup>2</sup> MC-8FX                                                          |

| Core Size                  | 8-Bit                                                                          |

| Speed                      | 16MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, LINbus, SIO, UART/USART                                      |

| Peripherals                | LVD, POR, PWM, WDT                                                             |

| Number of I/O              | 29                                                                             |

| Program Memory Size        | 36KB (36K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 1K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                                    |

| Data Converters            | A/D 8x8/10b                                                                    |

| Oscillator Type            | External                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 32-LQFP                                                                        |

| Supplier Device Package    | 32-LQFP (7x7)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb95f636kpmc-g-sne2 |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| Features 1                                                      |

|-----------------------------------------------------------------|

| 1. Product Line-up 3                                            |

| 2. Packages And Corresponding Products                          |

| 3. Differences Among Products And Notes On<br>Product Selection |

| 4. Pin Assignment 6                                             |

| 5. Pin Functions                                                |

| 6. I/O Circuit Type 12                                          |

| <b>7. Handling Precautions</b>                                  |

| 7.2 Precautions for Package Mounting                            |

| 8. Notes On Device Handling 17                                  |

| 9. Pin Connection 18                                            |

| 10. Block Diagram 19                                            |

| 11. CPU Core 20                                                 |

| 12. Memory Space 21                                             |

| 13. Areas For Specific Applications 23                          |

| 14. I/O Map 24                                                  |

| 15. I/O Ports                                   | 30  |

|-------------------------------------------------|-----|

| 15.1 Port 0                                     | 31  |

| 15.2 Port 1                                     | 39  |

| 15.3 Port 6                                     | 46  |

| 15.4 Port F                                     | 51  |

| 15.5 Port G                                     | 53  |

| 16. Interrupt Source Table                      | 56  |

| 17. Pin States In Each Mode                     | 57  |

| 18. Electrical Characteristics                  | 61  |

| 18.1 Absolute Maximum Ratings                   | 61  |

| 18.2 Recommended Operating Conditions           |     |

| 18.3 DC Characteristics                         |     |

| 18.4 AC Characteristics                         |     |

| 18.5 A/D Converter                              | 85  |

| 18.6 Flash Memory Program/Erase Characteristics |     |

| 19. Sample Characteristics                      | 90  |

| 20. Mask Options                                | 97  |

| 21. Ordering Information                        |     |

| 22. Package Dimension                           | 98  |

| 23. Major Changes In This Edition               | 101 |

| Document History Page                           | 101 |

| Sales, Solutions, and Legal Information         | 102 |

The on-chip debug function requires that Vcc, Vss and one serial wire be connected to an evaluation tool. For details of the connection method, refer to "CHAPTER 25 EXAMPLE OF SERIAL PROGRAMMING CONNECTION" in "New 8FX MB95630H Series Hardware Manual".

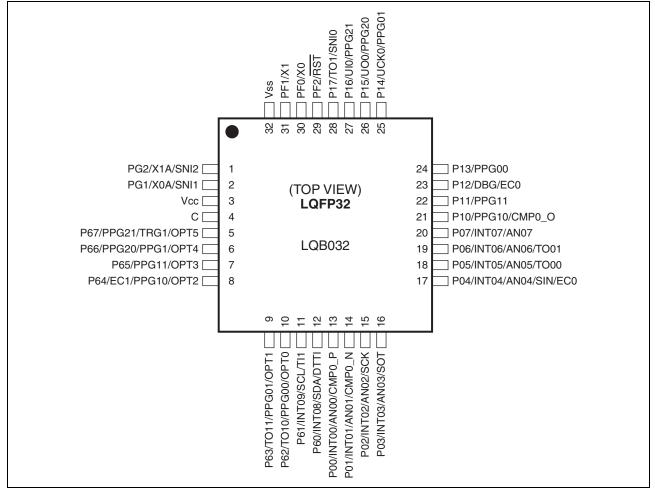

## 4. Pin Assignment

| Pin no.              |            |          | I/O               |                                                   |                       | I/O type |      |      |

|----------------------|------------|----------|-------------------|---------------------------------------------------|-----------------------|----------|------|------|

| LQFP32*1,<br>QFN32*2 | SH-DIP32*3 | Pin name | circuit<br>type*4 | Function                                          | Input                 | Output   | OD*5 | PU*6 |

|                      |            | P02      |                   | General-purpose I/O port                          |                       |          |      |      |

|                      |            | INT02    |                   | External interrupt input pin                      | Hysteresis/           |          |      |      |

| 15                   | 19         | AN02     | E                 | 8/10-bit A/D converter analog<br>input pin        | analog                | CMOS     |      | 0    |

|                      |            | SCK      |                   | LIN-UART clock I/O pin                            |                       |          |      |      |

|                      |            | P03      |                   | General-purpose I/O port                          |                       |          |      |      |

|                      |            | INT03    |                   | External interrupt input pin                      | Hysteresis/           |          |      |      |

| 16                   | 20         | AN03     | E                 | 8/10-bit A/D converter analog<br>input pin        | analog                | CMOS     |      | 0    |

|                      |            | SOT      |                   | LIN-UART data output pin                          |                       |          |      |      |

|                      |            | P04      |                   | General-purpose I/O port                          |                       |          |      |      |

|                      |            | INT04    |                   | External interrupt input pin                      |                       | CMOS     |      |      |

| 17                   | 21         | AN04     | F                 | 8/10-bit A/D converter analog<br>input pin        | CMOS/<br>analog       |          |      | 0    |

|                      |            | SIN      |                   | LIN-UART data input pin                           | analog                |          |      |      |

|                      |            | EC0      |                   | 8/16-bit composite timer ch. 0<br>clock input pin |                       |          |      |      |

|                      |            | P05      |                   | General-purpose I/O port                          |                       | CMOS     |      |      |

|                      |            | INT05    |                   | External interrupt input pin                      |                       |          | _    |      |

| 18                   | 22         | AN05     | Е                 | 8/10-bit A/D converter analog<br>input pin        | Hysteresis/<br>analog |          |      | 0    |

|                      |            | TO00     |                   | 8/16-bit composite timer ch. 0<br>output pin      |                       |          |      |      |

|                      |            | P06      |                   | General-purpose I/O port                          |                       |          |      |      |

|                      |            | INT06    |                   | External interrupt input pin                      |                       |          |      |      |

| 19                   | 23         | AN06     | Е                 | 8/10-bit A/D converter analog<br>input pin        | Hysteresis/<br>analog | CMOS     | —    | 0    |

|                      |            | TO01     |                   | 8/16-bit composite timer ch. 0<br>output pin      |                       |          |      |      |

|                      |            | P07      |                   | General-purpose I/O port                          |                       |          |      |      |

| 20                   | 24         | INT07    | Е                 | External interrupt input pin                      | Hysteresis/           | CMOS     |      | 0    |

|                      |            | AN07     | _                 | 8/10-bit A/D converter analog<br>input pin        | analog                |          |      | Ŭ    |

|                      |            | P10      |                   | General-purpose I/O port                          |                       |          |      |      |

| 21                   | 25         | PPG10    | G                 | 8/16-bit PPG ch. 1 output pin                     | Hysteresis            | CMOS     | —    | 0    |

|                      |            | CMP0_O   |                   | Comparator digital output pin                     |                       |          |      |      |

\_\_\_\_

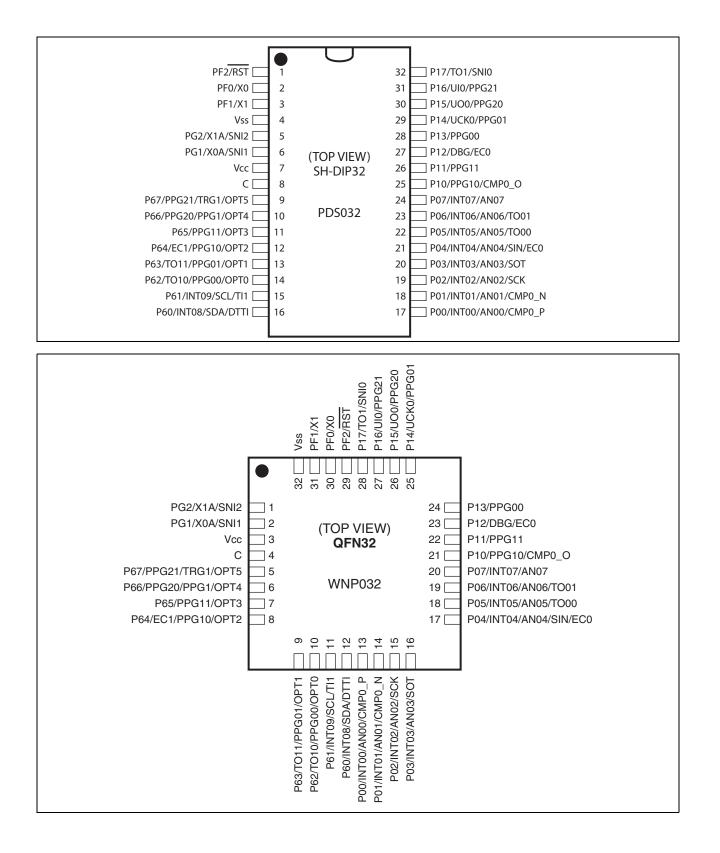

# 9. Pin Connection

#### · Treatment of unused pins

If an unused input pin is left unconnected, a component may be permanently damaged due to malfunctions or latchups. Always pull up or pull down an unused input pin through a resistor of at least 2 k $\Omega$ . Set an unused input/output pin to the output state and leave it unconnected, or set it to the input state and treat it the same as an unused input pin. If there is an unused output pin, leave it unconnected.

## Power supply pins

To reduce unnecessary electro-magnetic emission, prevent malfunctions of strobe signals due to an increase in the ground level, and conform to the total output current standard, always connect the Vcc pin and the Vss pin to the power supply and ground outside the device. In addition, connect the current supply source to the Vcc pin and the Vss pin with low impedance.

It is also advisable to connect a ceramic capacitor of approximately 0.1  $\mu$ F as a bypass capacitor between the V<sub>cc</sub> pin and the V<sub>ss</sub> pin at a location close to this device.

## DBG pin

Connect the DBG pin to an external pull-up resistor of 2 k $\Omega$  or above.

After power-on, ensure that the DBG pin does not stay at "L" level until the reset output is released.

The DBG pin becomes a communication pin in debug mode. Since the actual pull-up resistance depends on the tool used and the interconnection length, refer to the tool document when selecting a pull-up resistor.

## RST pin

Connect the  $\overline{\text{RST}}$  pin to an external pull-up resistor of 2 k $\Omega$  or above.

To prevent the device from unintentionally entering the reset mode due to noise, minimize the interconnection length between a pull-up resistor and the  $\overline{\text{RST}}$  pin and that between a pull-up resistor and the V<sub>CC</sub> pin when designing the layout of the printed circuit board.

The PF2/RST pin functions as the reset input/output pin after power-on. In addition, the reset output of the PF2/RST pin can be enabled by the RSTOE bit in the SYSC register, and the reset input function and the general-purpose I/O function can be selected by the RSTEN bit in the SYSC register.

## • C pin

Use a ceramic capacitor or a capacitor with equivalent frequency characteristics. The decoupling capacitor for the V<sub>CC</sub> pin must have a capacitance equal to or larger than the capacitance of Cs. For the connection to a decoupling capacitor Cs, see the diagram below. To prevent the device from unintentionally entering a mode to which the device is not set to transit due to noise, minimize the distance between the C pin and Cs and the distance between Cs and the Vss pin when designing the layout of a printed circuit board.

#### Note on serial communication

In serial communication, reception of wrong data may occur due to noise or other causes. Therefore, design a printed

| Address                | Register abbreviation | Register name                                              | R/W | Initial value |

|------------------------|-----------------------|------------------------------------------------------------|-----|---------------|

| 0x0F80                 | WRARH0                | Wild register address setting register (upper) ch. 0       | R/W | 0b0000000     |

| 0x0F81                 | WRARL0                | Wild register address setting register (lower) ch. 0       | R/W | 0b0000000     |

| 0x0F82                 | WRDR0                 | Wild register data setting register ch. 0                  | R/W | 0b0000000     |

| 0x0F83                 | WRARH1                | Wild register address setting register (upper) ch. 1       | R/W | 0b0000000     |

| 0x0F84                 | WRARL1                | Wild register address setting register (lower) ch. 1       | R/W | 0b0000000     |

| 0x0F85                 | WRDR1                 | Wild register data setting register ch. 1                  | R/W | 0b0000000     |

| 0x0F86                 | WRARH2                | Wild register address setting register (upper) ch. 2       | R/W | 0b0000000     |

| 0x0F87                 | WRARL2                | Wild register address setting register (lower) ch. 2       | R/W | 0b0000000     |

| 0x0F88                 | WRDR2                 | Wild register data setting register ch. 2                  | R/W | 0b0000000     |

| 0x0F89<br>to<br>0x0F91 | _                     | (Disabled)                                                 | _   |               |

| 0x0F92                 | T01CR0                | 8/16-bit composite timer 01 status control register 0      | R/W | 0b00000000    |

| 0x0F93                 | T00CR0                | 8/16-bit composite timer 00 status control register 0      | R/W | 0b0000000     |

| 0x0F94                 | T01DR                 | 8/16-bit composite timer 01 data register                  | R/W | 0b0000000     |

| 0x0F95                 | T00DR                 | 8/16-bit composite timer 00 data register                  | R/W | 0b0000000     |

| 0x0F96                 | TMCR0                 | 8/16-bit composite timer 00/01 timer mode control register | R/W | 0b00000000    |

| 0x0F97                 | T11CR0                | 8/16-bit composite timer 11 status control register 0      | R/W | 0b00000000    |

| 0x0F98                 | T10CR0                | 8/16-bit composite timer 10 status control register 0      | R/W | 0b00000000    |

| 0x0F99                 | T11DR                 | 8/16-bit composite timer 11 data register                  | R/W | 0b0000000     |

| 0x0F9A                 | T10DR                 | 8/16-bit composite timer 10 data register                  | R/W | 0b00000000    |

| 0x0F9B                 | TMCR1                 | 8/16-bit composite timer 10/11 timer mode control register | R/W | 0b00000000    |

| 0x0F9C                 | PPS01                 | 8/16-bit PPG01 cycle setting buffer register               | R/W | 0b11111111    |

| 0x0F9D                 | PPS00                 | 8/16-bit PPG00 cycle setting buffer register               | R/W | 0b11111111    |

| 0x0F9E                 | PDS01                 | 8/16-bit PPG01 duty setting buffer register                | R/W | 0b11111111    |

| 0x0F9F                 | PDS00                 | 8/16-bit PPG00 duty setting buffer register                | R/W | 0b11111111    |

| 0x0FA0                 | PPS11                 | 8/16-bit PPG11 cycle setting buffer register               | R/W | 0b11111111    |

| 0x0FA1                 | PPS10                 | 8/16-bit PPG10 cycle setting buffer register               | R/W | 0b11111111    |

| 0x0FA2                 | PDS11                 | 8/16-bit PPG11 duty setting buffer register                | R/W | 0b11111111    |

| 0x0FA3                 | PDS10                 | 8/16-bit PPG10 duty setting buffer register                | R/W | 0b11111111    |

| 0x0FA4                 | PPGS                  | 8/16-bit PPG start register                                | R/W | 0b00000000    |

| 0x0FA5                 | REVC                  | 8/16-bit PPG output inversion register                     | R/W | 0b0000000     |

| 0x0FA6                 | PPS21                 | 8/16-bit PPG21 cycle setting buffer register               | R/W | 0b11111111    |

| 0x0FA7                 | PPS20                 | 8/16-bit PPG20 cycle setting buffer register               | R/W | 0b11111111    |

| Address                | Register abbreviation | Register name                                           | R/W | Initial value |

|------------------------|-----------------------|---------------------------------------------------------|-----|---------------|

| 0x0FCE                 | OPDBRH5               | 16-bit MPG output data buffer register (upper) ch. 5    | R/W | 0b0000000     |

| 0x0FCF                 | OPDBRL5               | 16-bit MPG output data buffer register (lower) ch. 5    | R/W | 0b0000000     |

| 0x0FD0                 | OPDBRH6               | 16-bit MPG output data buffer register (upper) ch. 6    | R/W | 0b0000000     |

| 0x0FD1                 | OPDBRL6               | 16-bit MPG output data buffer register (lower) ch. 6    | R/W | 0b0000000     |

| 0x0FD2                 | OPDBRH7               | 16-bit MPG output data buffer register (upper) ch. 7    | R/W | 0b0000000     |

| 0x0FD3                 | OPDBRL7               | 16-bit MPG output data buffer register (lower) ch. 7    | R/W | 0b0000000     |

| 0x0FD4                 | OPDBRH8               | 16-bit MPG output data buffer register (upper) ch. 8    | R/W | 0b0000000     |

| 0x0FD5                 | OPDBRL8               | 16-bit MPG output data buffer register (lower) ch. 8    | R/W | 0b0000000     |

| 0x0FD6                 | OPDBRH9               | 16-bit MPG output data buffer register (upper) ch. 9    | R/W | 0b0000000     |

| 0x0FD7                 | OPDBRL9               | 16-bit MPG output data buffer register (lower) ch. 9    | R/W | 0b0000000     |

| 0x0FD8                 | OPDBRHA               | 16-bit MPG output data buffer register (upper) ch. A    | R/W | 0b0000000     |

| 0x0FD9                 | OPDBRLA               | 16-bit MPG output data buffer register (lower) ch. A    | R/W | 0b0000000     |

| 0x0FDA                 | OPDBRHB               | 16-bit MPG output data buffer register (upper) ch. B    | R/W | 0b0000000     |

| 0x0FDB                 | OPDBRLB               | 16-bit MPG output data buffer register (lower) ch. B    | R/W | 0b0000000     |

| 0x0FDC                 | OPDUR                 | 16-bit MPG output data register (upper)                 | R   | 0b0000XXXX    |

| 0x0FDD                 | OPDLR                 | 16-bit MPG output data register (lower)                 | R   | 0bXXXXXXXX    |

| 0x0FDE                 | CPCUR                 | 16-bit MPG compare clear register (upper)               | R/W | 0bXXXXXXXX    |

| 0x0FDF                 | CPCLR                 | 16-bit MPG compare clear register (lower)               | R/W | 0bXXXXXXXX    |

| 0x0FE0,<br>0x0FE1      | —                     | (Disabled)                                              | _   | —             |

| 0x0FE2                 | TMBUR                 | 16-bit MPG timer buffer register (upper)                | R   | 0bXXXXXXXX    |

| 0x0FE3                 | TMBLR                 | 16-bit MPG timer buffer register (lower)                | R   | 0bXXXXXXXX    |

| 0x0FE4                 | CRTH                  | Main CR clock trimming register (upper)                 | R/W | 0b000XXXXX    |

| 0x0FE5                 | CRTL                  | Main CR clock trimming register (lower)                 | R/W | 0b000XXXXX    |

| 0x0FE6                 |                       | (Disabled)                                              | —   | —             |

| 0x0FE7                 | CRTDA                 | Main CR clock temperature dependent adjustment register | R/W | 0b000XXXXX    |

| 0x0FE8                 | SYSC                  | System configuration register                           | R/W | 0b11000011    |

| 0x0FE9                 | CMCR                  | Clock monitoring control register                       | R/W | 0b0000000     |

| 0x0FEA                 | CMDR                  | Clock monitoring data register                          | R   | 0b0000000     |

| 0x0FEB                 | WDTH                  | Watchdog timer selection ID register (upper)            | R   | 0bXXXXXXXX    |

| 0x0FEC                 | WDTL                  | Watchdog timer selection ID register (lower)            | R   | 0bXXXXXXXX    |

| 0x0FED,<br>0x0FEE      | _                     | (Disabled)                                              | _   | _             |

| 0x0FEF                 | WICR                  | Interrupt pin selection circuit control register        | R/W | 0b01000000    |

| 0x0FF0<br>to<br>0x0FFF | _                     | (Disabled)                                              | _   | _             |

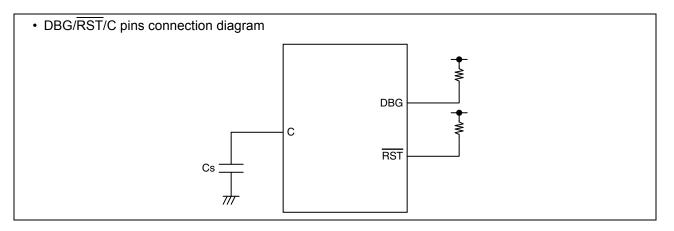

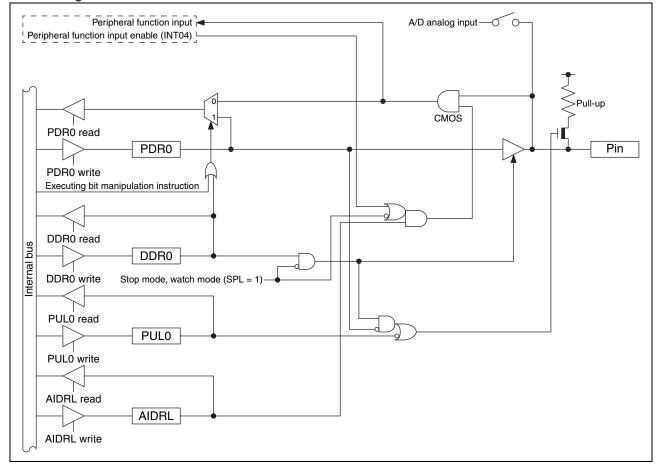

P04/INT04/AN04/SIN/EC0 pin

This pin has the following peripheral functions:

- External interrupt circuit input pin (INT04)

- 8/10-bit A/D converter analog input pin (ÁN04)

- LIN-UART data input pin (SIN)

- 8/16-bit composite timer ch. 0 clock input pin (EC0)

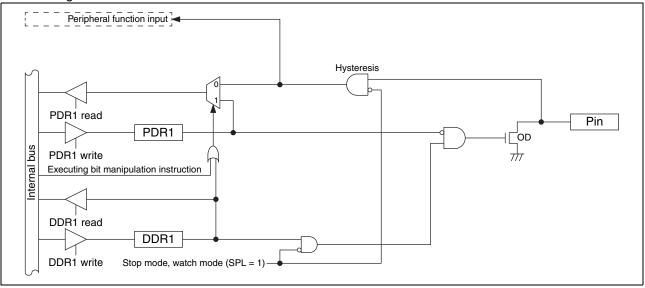

#### Block diagram of P04/INT04/AN04/SIN/EC0

## 15.2 Port 1

Port 1 is a general-purpose I/O port. This section focuses on its functions as a general-purpose I/O port. For details of peripheral functions, refer to their respective chapters in "New 8FX MB95630H Series Hardware Manual".

#### 15.2.1 Port 1 configuration

- Port 1 is made up of the following elements.

- · General-purpose I/O pins/peripheral function I/O pins

- Port 1 data register (PDR1)

- Port 1 direction register (DDR1)

- Port 1 pull-up register (PUL1)

#### 15.2.2 Block diagrams of port 1

- P10/PPG10/ČMP0\_O pin

- This pin has the following peripheral functions:

- 8/16-bit PPG ch. 1 output pin (PPG10)

- Comparator digital output pin (CMP0\_O)

- P11/PPG11 pin

- This pin has the following peripheral function:

- 8/16-bit PPG ch. 1 output pin (PPG11)

- P13/PPG00 pin

- This pin has the following peripheral function:

- 8/16-bit PPG ch. 0 output pin (PPG00)

- P15/UO0/PPG20 pin

This pin has the following peripheral functions:

- UART/SIO ch. 0 data output pin (UO0)

- 8/16-bit PPG ch. 2 output pin (PPG20)

- P12/DBG/EC0 pin

- This pin has the following peripheral functions:

- DBG input pin (DBG)

- 8/16-bit composite timer ch. 0 clock input pin (EC0)

#### Block diagram of P12/DBG/EC0

#### • P14/UCK0/PPG01 pin

- This pin has the following peripheral functions:

- UART/SIO ch. 0 clock I/O pin (UCK0)

- 8/16-bit PPG ch. 0 output pin (PPG01)

to "0".

- Reading the PDR1 register returns the pin value, regardless of whether the peripheral function uses that pin as its input pin. However, if the read-modify-write (RMW) type of instruction is used to read the PDR1 register, the PDR1 register value is returned.

- Operation at reset

If the CPU is reset, all bits in the DDR1 register are initialized to "0" and port input is enabled.

- Operation in stop mode and watch mode

- If the pin state setting bit in the standby control register (STBC:SPL) is set to "1" and the device transits to stop

mode or watch mode, the pin is compulsorily made to enter the high impedance state regardless of the DDR1 register value. The input of that pin is locked to "L" level and blocked in order to prevent leaks due to input open. However, if the interrupt input of P14/UCK0 and P16/UI0 is enabled by the external interrupt control register ch. 0

(EIC00) of the external interrupt circuit and the interrupt pin selection circuit control register (WICR) of the interrupt

pin selection circuit, the input is enabled and is not blocked.

- If the pin state setting bit is "0", the state of the port I/O or that of the peripheral function I/O remains unchanged and the output level is maintained.

## • Operation of the pull-up register

Setting the bit in the PUL1 register to "1" makes the pull-up resistor be internally connected to the pin. When the pin output is "L" level, the pull-up resistor is disconnected regardless of the value of the PUL1 register.

## 15.3 Port 6

Port 6 is a general-purpose I/O port. This section focuses on its functions as a general-purpose I/O port. For details of peripheral functions, refer to their respective chapters in "New 8FX MB95630H Series Hardware Manual".

#### 15.3.1 Port 6 configuration

Port 6 is made up of the following elements.

- General-purpose I/O pins/peripheral function I/O pins

- Port 6 data register (PDR6)

- Port 6 direction register (DDR6)

- Port 6 pull-up register (PUL6)

## 15.3.2 Block diagrams of port 6

P60/INT08/SDA/DTTI pin

This pin has the following peripheral functions:

- External interrupt circuit input pin (INT08)

- I<sup>2</sup>C bus interface ch. 0 data I/O pin (SDA)

- MPG waveform sequencer input pin (DTTI)

## P61/INT09/SCL/TI1 pin

This pin has the following peripheral functions:

- External interrupt circuit input pin (INT09)

- I<sup>2</sup>C bus interface ch. 0 clock I/O pin (SCL)

- 16-bit reload timer ch. 1 input pin (TI1)

- Operation as an input port

- A pin becomes an input port if the bit in the DDRF register corresponding to that pin is set to "0".

- For a pin shared with other peripheral functions, disable the output of such peripheral functions.

- If data is written to the PDRF register, the value is stored in the output latch but is not output to the pin set as an input port.

- Reading the PDRF register returns the pin value. However, if the read-modify-write (RMW) type of instruction is used to read the PDRF register, the PDRF register value is returned.

- · Operation at reset

If the CPU is reset, all bits in the DDRF register are initialized to "0" and port input is enabled.

- · Operation in stop mode and watch mode

- If the pin state setting bit in the standby control register (STBC:SPL) is set to "1" and the device transits to stop mode or watch mode, the pin is compulsorily made to enter the high impedance state regardless of the DDRF register value. The input of that pin is locked to "L" level and blocked in order to prevent leaks due to input open.

- If the pin state setting bit is "0", the state of the port I/O or that of the peripheral function I/O remains unchanged and the output level is maintained.

#### 15.5 Port G

Port G is a general-purpose I/O port. This section focuses on its functions as a general-purpose I/O port. For details of peripheral functions, refer to their respective chapters in "New 8FX MB95630H Series Hardware Manual".

#### 15.5.1 Port G configuration

- Port G is made up of the following elements.

- · General-purpose I/O pins/peripheral function I/O pins

- Port G data register (PDRG)

- Port G direction register (DDRG)

- Port G pull-up register (PULG)

#### 15.5.2 Block diagram of port G

PG1/X0A/SNI1 pin

This pin has the following peripheral functions:

- Subclock input oscillation pin (X0A)

- Trigger input pin for the position detection function of the MPG waveform sequencer (SNI1)

- PG2/X1A/SNI2 pin

- This pin has the following peripheral functions:

- Subclock I/O oscillation pin (X1A)

- Trigger input pin for the position detection function of the MPG waveform sequencer (SNI2)

- If data is written to the PDRG register, the value is stored in the output latch and is output to the pin set as an output port as it is.

- Reading the PDRG register returns the PDRG register value.

- Operation as an input port

- A pin becomes an input port if the bit in the DDRG register corresponding to that pin is set to "0".

- For a pin shared with other peripheral functions, disable the output of such peripheral functions.

- If data is written to the PDRG register, the value is stored in the output latch but is not output to the pin set as an input port.

- Reading the PDRG register returns the pin value. However, if the read-modify-write (RMW) type of instruction is used to read the PDRG register, the PDRG register value is returned.

- Operation as a peripheral function input pin

- To set a pin as an input port, set the bit in the DDRG register corresponding to the input pin of a peripheral function to "0".

- Reading the PDRG register returns the pin value, regardless of whether the peripheral function uses that pin as its input pin. However, if the read-modify-write (RMW) type of instruction is used to read the PDRG register, the PDRG register value is returned.

- · Operation at reset

If the CPU is reset, all bits in the DDRG register are initialized to "0" and port input is enabled.

- Operation in stop mode and watch mode

- If the pin state setting bit in the standby control register (STBC:SPL) is set to "1" and the device transits to stop mode or watch mode, the pin is compulsorily made to enter the high impedance state regardless of the DDRG register value. The input of that pin is locked to "L" level and blocked in order to prevent leaks due to input open.

- If the pin state setting bit is "0", the state of the port I/O or that of the peripheral function I/O remains unchanged and the output level is maintained.

- Operation of the pull-up register

Setting the bit in the PULG register to "1" makes the pull-up resistor be internally connected to the pin. When the pin output is "L" level, the pull-up resistor is disconnected regardless of the value of the PULG register.

# **16. Interrupt Source Table**

|                                  | Interrupt         |        | r table<br>ress |          | pt level<br>register | Priority order of interrupt sources                |

|----------------------------------|-------------------|--------|-----------------|----------|----------------------|----------------------------------------------------|

| Interrupt source                 | request<br>number | Upper  | Lower           | Register | Bit                  | of the same level<br>(occurring<br>simultaneously) |

| External interrupt ch. 0         | IRQ00             | 0xFFFA | 0xFFFB          | ILR0     | L00 [1:0]            | High                                               |

| External interrupt ch. 4         |                   |        | UNITID          | ILINU    | 200[1.0]             |                                                    |

| External interrupt ch. 1         | IRQ01             | 0xFFF8 | 0xFFF9          | ILR0     | L01 [1:0]            | T                                                  |

| External interrupt ch. 5         | integer           |        |                 |          | 201[1.0]             |                                                    |

| External interrupt ch. 2         | IRQ02             | 0xFFF6 | 0xFFF7          | ILR0     | L02 [1:0]            |                                                    |

| External interrupt ch. 6         | II (QUZ           |        |                 |          | 202 [1.0]            |                                                    |

| External interrupt ch. 3         | IRQ03             | 0xFFF4 | 0xFFF5          | ILR0     | L03 [1:0]            |                                                    |

| External interrupt ch. 7         | 11/000            |        | 0/1113          | ILINU    | 203 [1.0]            |                                                    |

| UART/SIO ch. 0                   | IRQ04             | 0xFFF2 | 0xFFF3          | ILR1     | L04 [1:0]            |                                                    |

| MPG (DTTI)                       |                   |        | 0/1113          |          | 204[1.0]             |                                                    |

| 8/16-bit composite timer ch. 0   | IRQ05             | 0xFFF0 | 0xFFF1          | ILR1     | L05 [1:0]            |                                                    |

| (lower)                          | 11/000            |        |                 |          | 203[1.0]             |                                                    |

| 8/16-bit composite timer ch. 0   | IRQ06             | 0xFFEE | 0xFFEF          | ILR1     | L06 [1:0]            |                                                    |

| (upper)                          |                   | UXFFEE | UXFFEF          |          | 200[1.0]             |                                                    |

| LIN-UART (reception)             | IRQ07             | 0xFFEC | 0xFFED          | ILR1     | L07 [1:0]            |                                                    |

| LIN-UART (transmission)          | IRQ08             | 0xFFEA | 0xFFEB          | ILR2     | L08 [1:0]            |                                                    |

| 8/16-bit PPG ch. 1 (lower)       | IRQ09             | 0xFFE8 | 0xFFE9          | ILR2     | L09 [1:0]            |                                                    |

| 8/16-bit PPG ch. 1 (upper)       | IRQ10             | 0xFFE6 | 0xFFE7          | ILR2     | L10 [1:0]            |                                                    |

| 8/16-bit PPG ch. 2 (upper)       | IRQ11             | 0xFFE4 | 0xFFE5          | ILR2     | L11 [1:0]            |                                                    |

| 8/16-bit PPG ch. 0 (upper)       | IRQ12             | 0xFFE2 | 0xFFE3          | ILR3     | L12 [1:0]            |                                                    |

| 8/16-bit PPG ch. 0 (lower)       | IRQ13             | 0xFFE0 | 0xFFE1          | ILR3     | L13 [1:0]            |                                                    |

| 8/16-bit composite timer ch. 1   |                   |        |                 |          |                      |                                                    |

| (upper)                          | IRQ14             | 0xFFDE | 0xFFDF          | ILR3     | L14 [1:0]            |                                                    |

| 8/16-bit PPG ch. 2 (lower)       | IRQ15             | 0xFFDC | 0xFFDD          | ILR3     | L15 [1:0]            |                                                    |

| 16-bit reload timer ch. 1        |                   |        |                 |          |                      |                                                    |

| MPG (write timing/compare clear) | IRQ16             | 0xFFDA | 0xFFDB          | ILR4     | L16 [1:0]            |                                                    |

| I <sup>2</sup> C bus interface   |                   |        |                 |          |                      |                                                    |

| 16-bit PPG timer ch. 1           |                   |        |                 |          |                      |                                                    |

| MPG (position detection/compare  | IRQ17             | 0xFFD8 | 0xFFD9          | ILR4     | L17 [1:0]            |                                                    |

| interrupt)                       |                   |        |                 |          |                      |                                                    |

| 8/10-bit Á/D converter           | IRQ18             | 0xFFD6 | 0xFFD7          | ILR4     | L18 [1:0]            |                                                    |

| Time-base timer                  | IRQ19             | 0xFFD4 |                 | ILR4     | L19 [1:0]            |                                                    |

| Watch prescaler                  |                   |        |                 |          |                      |                                                    |

| Comparator                       | IRQ20             | 0xFFD2 | 0xFFD3          | ILR5     | L20 [1:0]            |                                                    |

| External interrupt ch. 8         | IDCC              |        | 0 FFD /         |          | 1.04.54.65           |                                                    |

| External interrupt ch. 9         | IRQ21             | 0xFFD0 | 0xFFD1          | ILR5     | L21 [1:0]            |                                                    |

| 8/16-bit composite timer ch. 1   | IDCCC             |        |                 |          | 1 00 14 07           |                                                    |

| (lower)                          | IRQ22             | 0xFFCE | 0xFFCF          | ILR5     | L22 [1:0]            |                                                    |

| Flash memory                     | IRQ23             | 0xFFCC | 0xFFCD          | ILR5     | L23 [1:0]            | Low                                                |

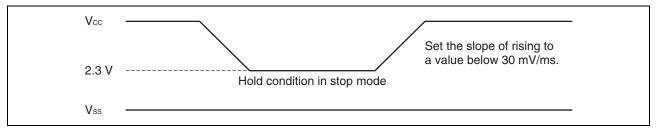

#### 18.4.4 Power-on Reset

$(V_{SS} = 0.0 V, T_A = -40^{\circ}C to +85^{\circ}C)$

| Ol Condition | Condition |     |     |      |                          |

|--------------|-----------|-----|-----|------|--------------------------|

|              |           | Min | Max | Unit | Remarks                  |

|              |           |     | 50  | ms   |                          |

|              |           | 1   |     | ms   | Wait time until power-on |

|              |           |     | 1   |      |                          |

# Note: A sudden change of power supply voltage may activate the power-on reset function. When changing the power supply voltage during the operation, set the slope of rising to a value below within 30 mV/ms as shown below.

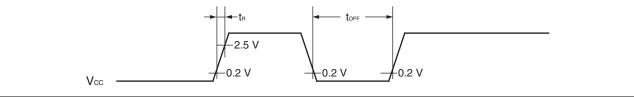

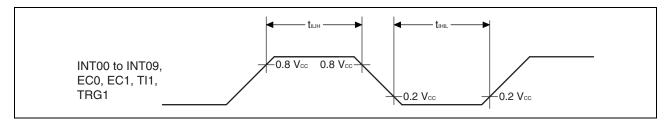

18.4.5 Peripheral Input Timing

(Vcc = 5.0 V $\pm$ 10%, Vss = 0.0 V, T<sub>A</sub> = -40°C to +85°C)

| Parameter                        | Symbol | Pin name                       | Va               | lue | Unit |

|----------------------------------|--------|--------------------------------|------------------|-----|------|

| Farameter                        | Symbol | FIII IIailie                   | Min              | Мах | Unit |

| Peripheral input "H" pulse width | tı∟ıн  | INT00 to INT09, EC0, EC1, TI1, | 2 <b>t</b> MCLK* |     | ns   |

| Peripheral input "L" pulse width | tını∟  | TRG1                           | 2 <b>t</b> MCLK* |     | ns   |

\*: See "Source Clock/Machine Clock" for tMCLK.

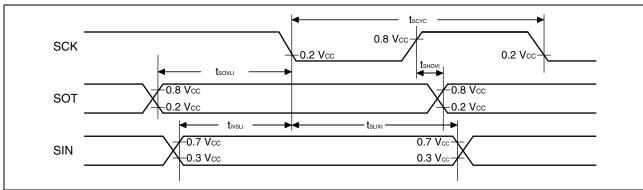

# Sampling is executed at the rising edge of the sampling clock\*1, and serial clock delay is enabled\*2. (ESCR register : SCES bit = 0, ECCR register : SCDE bit = 1)

| Parameter                                 | Symbol Pin nam |          | Condition                                                        | Va                                 | Unit |        |

|-------------------------------------------|----------------|----------|------------------------------------------------------------------|------------------------------------|------|--------|

| Parameter                                 | Symbol         | Pin name | Condition                                                        | Min                                | Max  | – Unit |

| Serial clock cycle time                   | tscyc          | SCK      |                                                                  | 5 tmclk*3                          | —    | ns     |

| $SCK^{\uparrow} \to SOT$ delay time       | <b>t</b> shovi | SCK, SOT | Internal clock                                                   | -50                                | +50  | ns     |

| Valid SIN $ ightarrow$ SCK $\downarrow$   | tivsli         |          | operation output pin:<br>$C_{L} = 80 \text{ pF} + 1 \text{ TTL}$ | tмськ*3 + 80                       | —    | ns     |

| $SCK{\downarrow}{	o}$ valid SIN hold time | tslixi         | SCK, SIN |                                                                  | 0                                  | —    | ns     |

| $SOT 	o SCK {\downarrow} delay$ time      | tsovli         | SCK, SOT |                                                                  | 3 <b>t</b> мськ* <sup>3</sup> – 70 | —    | ns     |

\*1: There is a function used to choose whether the sampling of reception data is performed at a rising edge or a falling edge of the serial clock.

\*2: The serial clock delay function is a function used to delay the output signal of the serial clock for half the clock.

\*3: See "Source Clock/Machine Clock" for tMCLK.

Sampling is executed at the falling edge of the sampling clock\*1, and serial clock delay is enabled\*2. (ESCR register : SCES bit = 1, ECCR register : SCDE bit = 1)

(Vcc = 5.0 V±10%, Vss = 0.0 V, T<sub>A</sub> = -40°C to +85°C)

$(V_{CC} = 5.0 V \pm 10\%, V_{SS} = 0.0 V, T_{A} = -40^{\circ}C to +85^{\circ}C)$

| Parameter                                     | Symbol Pin name |          | Condition             | Va                    | Unit |      |

|-----------------------------------------------|-----------------|----------|-----------------------|-----------------------|------|------|

| Farameter                                     | Symbol          | Fininame | Condition             | Min                   | Мах  | Unit |

| Serial clock cycle time                       | tscyc           | SCK      |                       | 5 tмськ* <sup>3</sup> | _    | ns   |

| $SCK\!\!\downarrow  ightarrow SOT$ delay time | tslovi          | SCK, SOT | Internal clock        | -50                   | +50  | ns   |

| Valid SIN $ ightarrow$ SCK $\uparrow$         | <b>t</b> ivshi  |          | operation output pin: | tмськ*3 + 80          | _    | ns   |

| $SCK^{\uparrow} \to valid SIN hold time$      | <b>t</b> shixi  | SCK, SIN | C∟ = 80 pF + 1 TTL    | 0                     | _    | ns   |

| $SOT 	o SCK^{\uparrow}delay$ time             | tsovнi          | SCK, SOT |                       | 3tMCLK*3 - 70         | _    | ns   |

\*1: There is a function used to choose whether the sampling of reception data is performed at a rising edge or a falling edge of the serial clock.

\*2: The serial clock delay function is a function used to delay the output signal of the serial clock for half the clock.

\*3: See "Source Clock/Machine Clock" for tMCLK.

## (Continued)

|                                                 | Querry Pin      |             |                                           | Value*2                                                 |     |      |                                                                                 |

|-------------------------------------------------|-----------------|-------------|-------------------------------------------|---------------------------------------------------------|-----|------|---------------------------------------------------------------------------------|

| Parameter                                       | Symbol          | name        | Condition                                 | Min                                                     | Max | Unit | Remarks                                                                         |

| START condition<br>detection                    | thd;sta         | SCL,<br>SDA |                                           | 2 tмськ – 20                                            | _   | ns   | No START<br>condition is<br>detected when 1<br>tмс∟к is used at<br>reception.   |

| STOP condition<br>detection                     | tsu;sto         | SCL,<br>SDA |                                           | 2 tмськ – 20                                            | _   | ns   | No STOP condition<br>is detected when 1<br>tMCLK is used at<br>reception.       |

| RESTART<br>condition detection<br>condition     | tsu;sta         | SCL,<br>SDA | R = 1.7 kΩ,<br>C = 50 pF*1                | 2 tмськ – 20                                            | _   | ns   | No RESTART<br>condition is<br>detected when 1<br>tmclκ is used at<br>reception. |

| Bus free time                                   | <b>t</b> BUF    | SCL,<br>SDA | C = 50 pr ·                               | 2 tmclk – 20                                            | _   | ns   | At reception                                                                    |

| Data hold time                                  | <b>t</b> hd;dat | SCL,<br>SDA | SDA<br>SCL,<br>SDA<br>SCL,<br>SDA<br>SCL, | 2 tmclk – 20                                            | _   | ns   | At slave<br>transmission mode                                                   |

| Data setup time                                 | tsu;dat         | SCL,<br>SDA |                                           | $t_{\text{LOW}} - 3 t_{\text{MCLK}} - 20$               | _   | ns   | At slave<br>transmission mode                                                   |

| Data hold time                                  | <b>t</b> hd;dat | SCL,<br>SDA |                                           | 0                                                       |     | ns   | At reception                                                                    |

| Data setup time                                 | <b>t</b> su;dat | SCL,<br>SDA |                                           | tмськ – <b>20</b>                                       | _   | ns   | At reception                                                                    |

| SDA↓ → SCL↑<br>(with wakeup<br>function in use) | twakeup         | SCL,<br>SDA |                                           | Oscillation<br>stabilization wait time<br>+2 tмськ – 20 | _   | ns   |                                                                                 |

(Vcc = 5.0 V±10%, Vss = 0.0 V, T<sub>A</sub> = -40°C to +85°C)

\*1: R represents the pull-up resistor of the SCL and SDA lines, and C the load capacitor of the SCL and SDA lines.

\*2: • See "Source Clock/Machine Clock" for tMCLK.

• m represents the CS[4:3] bits in the I<sup>2</sup>C clock control register ch. 0 (ICCR0).

• n represents the CS[2:0] bits in the I<sup>2</sup>C clock control register ch. 0 (ICCR0).

- The actual timing of the I<sup>2</sup>C bus interface is determined by the values of m and n set by the machine clock (tmcLk) and the CS[4:0] bits in the ICCR0 register.

- Standard-mode:

m and n can be set to values in the following range:  $0.9 \text{ MHz} < t_{\text{MCLK}}$  (machine clock) < 16.25 MHz. The usable frequencies of the machine clock are determined by the settings of m and n as shown below.

|   | (m, n) = (1, 8)                                  | : 0.9 MHz < t <sub>MCLK</sub> $\leq$ 1 MHz                |

|---|--------------------------------------------------|-----------------------------------------------------------|

|   | (m, n) = (1, 22), (5, 4), (6, 4), (7, 4), (8, 4) | : 0.9 MHz < t <sub>MCLK</sub> $\leq$ 2 MHz                |

|   | (m, n) = (1, 38), (5, 8), (6, 8), (7, 8), (8, 8) | : 0.9 MHz < t <sub>MCLK</sub> $\leq$ 4 MHz                |

|   | (m, n) = (1, 98), (5, 22), (6, 22), (7, 22)      | : 0.9 MHz < t <sub>MCLK</sub> $\leq$ 10 MHz               |

|   | (m, n) = (8, 22)                                 | : 0.9 MHz < tмс∟к ≤ 16.25 MHz                             |

| • | Fast-mode:                                       |                                                           |

|   | m and n can be set to values in the following    | range: 3.3 MHz < tMCLK (machine clock) < 16.25 MHz.       |

|   | The usable frequencies of the machine clock      | are determined by the settings of m and n as shown below. |

|   | (m, n) = (1, 8)                                  | : 3.3 MHz < t <sub>MCLK</sub> $\leq$ 4 MHz                |

|   | (m, n) = (1, 22), (5, 4)                         | : 3.3 MHz < tмс∟к ≤ 8 MHz                                 |

|   | (m, n) = (1, 38), (6, 4), (7, 4), (8, 4)         | : 3.3 MHz < tмс∟к ≤ 10 MHz                                |

|   | (m, n) = (5, 8)                                  | : 3.3 MHz < tмс∟к ≤ 16.25 MHz                             |

|   |                                                  |                                                           |

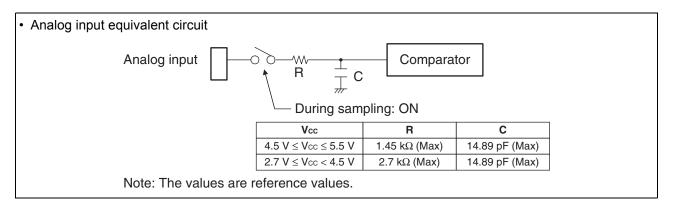

## 18.5 A/D Converter

18.5.1 A/D Converter Electrical Characteristics

| _                               |        | Value         |               |               |     | Remarks                                                                                                             |

|---------------------------------|--------|---------------|---------------|---------------|-----|---------------------------------------------------------------------------------------------------------------------|

| Parameter                       | Symbol | Min Typ Max   |               | Unit          |     |                                                                                                                     |

| Resolution                      |        | —             |               | 10            | bit |                                                                                                                     |

| Total error                     |        | -3            |               | +3            | LSB |                                                                                                                     |

| Linearity error                 | —      | -2.5          | —             | +2.5          | LSB |                                                                                                                     |

| Differential linearity<br>error |        | -1.9          | —             | +1.9          | LSB |                                                                                                                     |

| Zero transition<br>voltage      | Vот    | Vss – 1.5 LSB | Vss + 0.5 LSB | Vss + 2.5 LSB | V   |                                                                                                                     |

| Full-scale transition voltage   | Vfst   | Vcc – 4.5 LSB | Vcc – 2 LSB   | Vcc + 0.5 LSB | V   |                                                                                                                     |

| Compare time                    | —      | 3             | —             | 10            | μs  | $2.7~V \le Vcc \le 5.5~V$                                                                                           |

| Sampling time                   | _      | 0.941         | _             | œ             | μs  | $2.7 V \le V_{CC} \le 5.5 V$ ,<br>with external<br>impedance < $3.3 k\Omega$<br>and external<br>capacitance = 10 pF |

| Analog input current            | Iain   | -0.3          |               | +0.3          | μA  |                                                                                                                     |

| Analog input voltage            | VAIN   | Vss           |               | Vcc           | V   |                                                                                                                     |

## 18.5.2 Notes on Using A/D Converter

• External impedance of analog input and its sampling time

The A/D converter of the MB95630H Series has a sample and hold circuit. If the external impedance is too high to keep sufficient sampling time, the analog voltage charged to the capacitor of the internal sample and hold circuit is insufficient, adversely affecting A/D conversion precision. Therefore, to satisfy the A/D conversion precision standard, considering the relationship between the external impedance and minimum sampling time, either adjust the register value and operating frequency or decrease the external impedance so that the sampling time is longer than the minimum value. In addition, if sufficient sampling time cannot be secured, connect a capacitor of about 0.1  $\mu$ F to the analog input pin.

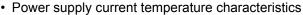

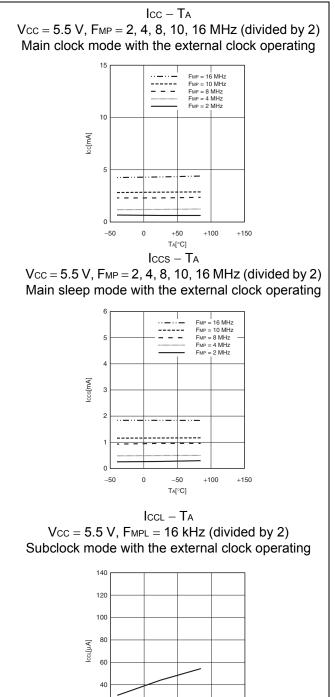

# 19. Sample Characteristics

20

0

-50

0

+50

T<sub>A</sub>[°C]

+100

+150

60

40

20

0

1 2 3 4 5 6 7

Vcc[V]

# **Document History Page**

| Revision | ECN     | 002-04627<br>Orig. of | Submission | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|----------|---------|-----------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|          | 2011    | Change                | Date       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| **       | -       | AKIH                  | 06/07/2013 | Migrated to Cypress and assigned document number 002-04627.<br>No change to document contents or format.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| *A       | 5193921 | AKIH                  | 03/29/2016 | Updated to Cypress template<br>Added "MB95F636KPMC-G-UNE2" in "Ordering Information"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| *В       | 5443796 | HTER                  | 02/06/2017 | Changed three package codes as the following<br>from "FPT-32P-M30" to "LQB032"<br>from "LCC-32P-M19" to "WNP032"<br>in chapter:<br>1.Product Line-up (Page 5)<br>2.Packages And Corresponding Products (Page 5)<br>4.Pin Assignment (Page 6, 7)<br>5.Pin Functions (Page 11)<br>21.Ordering Information (Page 97)<br>28.Package Dimensions (Page 98 to 100).<br>Added three Part numbers<br>- MB95F633KPMC-G-UNE2<br>- MB95F633KPMC-G-UNE2<br>in chapter 21.Ordering Information (Page 97).<br>Deleted four Part numbers<br>- MB95F632KPMC-G-SNE2<br>- MB95F633KPMC-G-SNE2<br>- MB95F634KPMC-G-SNE2<br>- MB95F634KPMC-G-SNE2<br>- MB95F636KPMC-G-SNE2<br>- MB95F636KPMC-G-SNE2<br>in chapter 21.Ordering Information (Page 97). |  |

| *C       | 5746267 | AESATP12              | 05/23/2017 | Updated logo and copyright.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| *D       | 5895915 | HUAL                  | 09/27/2017 | Added Part number "MB95F633HPMC-G-UNERE2" and Packing information<br>Modified from "MB95F634HPMC-G-SNE2" to "MB95F634HPMC-G-UNE2" in 21.Ordering<br>Information (Page 97)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |