Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                |

|----------------------------|----------------------------------------------------------------|

| Product Status             | Active                                                         |

| Core Processor             | 8052                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 12.58MHz                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                              |

| Peripherals                | PSM, Temp Sensor, WDT                                          |

| Number of I/O              | 34                                                             |

| Program Memory Size        | 8KB (8K x 8)                                                   |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | 640 x 8                                                        |

| RAM Size                   | 256 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                    |

| Data Converters            | A/D 7x16b; D/A 1x12b                                           |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 52-QFP                                                         |

| Supplier Device Package    | 52-MQFP (10×10)                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/aduc816bsz |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Parameter                                      | ADuC816BS        | Unit                       | Test Conditions/Comments                                                                                                     |

|------------------------------------------------|------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------|

| TRANSDUCER BURNOUT CURRENT SO                  | OURCES           |                            |                                                                                                                              |

| AIN+ Current                                   | -100             | nA typ                     | AIN+ is the Selected Positive Input to                                                                                       |

|                                                |                  |                            | the Primary ADC                                                                                                              |

| AIN- Current                                   | +100             | nA typ                     | AIN- is the Selected Negative Input                                                                                          |

| Initial Tolerance @ 25°C Drift                 | ±10              | % typ                      | the Auxiliary ADC                                                                                                            |

| Drift                                          | 0.03             | % typ<br>%/°C typ          |                                                                                                                              |

|                                                | 0.03             | 70/ C typ                  |                                                                                                                              |

| EXCITATION CURRENT SOURCES                     | 200              | 4                          | Associable from Each Comment Service                                                                                         |

| Output Current Initial Tolerance @ 25°C        | -200<br>  ±10    | μA typ<br>% typ            | Available from Each Current Source                                                                                           |

| Drift                                          | 200              | ppm/°C typ                 |                                                                                                                              |

| Initial Current Matching @ 25°C                | ±1               | % typ                      | Matching Between Both Current Sources                                                                                        |

| Drift Matching                                 | 20               | ppm/°C typ                 | Traceming Between Boar Current Sources                                                                                       |

| Line Regulation (AV <sub>DD</sub> )            | 1                | μA/V typ                   | $AV_{DD} = 5 V + 5\%$                                                                                                        |

| Load Regulation                                | 0.1              | μA/V typ                   |                                                                                                                              |

| Output Compliance                              | $AV_{DD} - 0.6$  | V max                      |                                                                                                                              |

|                                                | AGND             | min                        |                                                                                                                              |

| LOGIC INPUTS                                   |                  |                            |                                                                                                                              |

| All Inputs Except SCLOCK, RESET,               |                  |                            |                                                                                                                              |

| and XTAL1                                      |                  |                            |                                                                                                                              |

| V <sub>INL</sub> , Input Low Voltage           | 0.8              | V max                      | $DV_{DD} = 5 V$                                                                                                              |

|                                                | 0.4              | V max                      | $DV_{DD} = 3 V$                                                                                                              |

| V <sub>INH</sub> , Input High Voltage          | 2.0              | V min                      |                                                                                                                              |

| SCLOCK and RESET Only                          |                  |                            |                                                                                                                              |

| (Schmitt-Triggered Inputs) <sup>2</sup>        | 1 2/2            | V /V o                     | DV - 5 V                                                                                                                     |

| $ m V_{T^+}$                                   | 1.3/3 0.95/2.5   | V min/V max<br>V min/V max | $ \begin{aligned} DV_{DD} &= 5 V \\ DV_{DD} &= 3 V \end{aligned} $                                                           |

| $ m V_{T-}$                                    | 0.93/2.3         | V min/V max                | $DV_{DD} = 5 V$ $DV_{DD} = 5 V$                                                                                              |

| *T=                                            | 0.4/1.1          | V min/V max                | $DV_{DD} = 3 V$                                                                                                              |

| $V_{T+} - V_{T-}$                              | 0.3/0.85         | V min/V max                | $DV_{DD} = 5 V$                                                                                                              |

|                                                | 0.3/0.85         | V min/V max                | $DV_{DD} = 3 V$                                                                                                              |

| Input Currents                                 |                  |                            |                                                                                                                              |

| Port 0, P1.2–P1.7, <del>EA</del>               | ±10              | μA max                     | $V_{IN} = 0 \text{ V or } V_{DD}$                                                                                            |

| SCLOCK, SDATA/MOSI, MISO, $\overline{SS}^{11}$ | −10 min, −40 max | μA min/μA max              | $V_{IN} = 0 \text{ V}, DV_{DD} = 5 \text{ V}, Internal Pull-Up}$                                                             |

| D-10-1-1                                       | ±10              | μA max                     | $V_{IN} = V_{DD}$ , $DV_{DD} = 5 V$                                                                                          |

| RESET                                          | ±10              | μA max                     | $V_{IN} = 0 \text{ V}, DV_{DD} = 5 \text{ V}$                                                                                |

|                                                | 35 min, 105 max  | μA min/μA max              | $V_{IN} = V_{DD}$ , $DV_{DD} = 5 V$ ,<br>Internal Pull-Down                                                                  |

| P1.0, P1.1, Ports 2 and 3                      | ±10              | μA max                     | $V_{IN} = V_{DD}, DV_{DD} = 5 V$                                                                                             |

| 1 1.0, 1 1.1, 1 ofts 2 and 3                   | -180             | μA min                     | $V_{\text{IN}} = V_{\text{DD}}, DV_{\text{DD}} = 5 \text{ V}$<br>$V_{\text{IN}} = 2 \text{ V}, DV_{\text{DD}} = 5 \text{ V}$ |

|                                                | -660             | μA max                     | VIN - Z V, D VDD - 3 V                                                                                                       |

|                                                | -20              | μA min                     | $V_{IN} = 450 \text{ mV}, DV_{DD} = 5 \text{ V}$                                                                             |

|                                                | <b>-75</b>       | μA max                     |                                                                                                                              |

| Input Capacitance                              | 5                | pF typ                     | All Digital Inputs                                                                                                           |

| CRYSTAL OSCILLATOR (XTAL1 AND X                | TAL2)            |                            |                                                                                                                              |

| Logic Inputs, XTAL1 Only                       |                  |                            |                                                                                                                              |

| V <sub>INL</sub> , Input Low Voltage           | 0.8              | V max                      | $DV_{DD} = 5 V$                                                                                                              |

|                                                | 0.4              | V max                      | $DV_{DD} = 3 V$                                                                                                              |

| V <sub>INH</sub> , Input High Voltage          | 3.5              | V min                      | $DV_{DD} = 5 V$                                                                                                              |

|                                                | 2.5              | V min                      | $DV_{DD} = 3 V$                                                                                                              |

| XTAL1 Input Capacitance                        | 18               | pF typ                     |                                                                                                                              |

| XTAL2 Output Capacitance                       | 18               | pF typ                     |                                                                                                                              |

Rev. B -5-

| Parameter                                               | ADuC816BS | Unit   | Test Conditions/Comments                                                           |

|---------------------------------------------------------|-----------|--------|------------------------------------------------------------------------------------|

| POWER REQUIREMENTS (continued)                          |           |        |                                                                                    |

| Power Supply Currents Normal Mode <sup>16, 17</sup>     |           |        |                                                                                    |

| DV <sub>DD</sub> Current                                | 4         | mA max | $DV_{DD} = 4.75 \text{ V to } 5.25 \text{ V}$ , Core CLK = 1.57 MHz                |

|                                                         | 2.1       | mA max | $DV_{DD} = 2.7 \text{ V to } 3.6 \text{ V}, \text{ Core CLK} = 1.57 \text{ MHz}$   |

| AV <sub>DD</sub> Current                                | 170       | μA max | $AV_{DD} = 5.25 \text{ V}$ , Core CLK = 1.57 MHz                                   |

| DV <sub>DD</sub> Current                                | 15        | mA max | $DV_{DD} = 4.75 \text{ V}$ to 5.25 V, Core CLK = 12.58 MHz                         |

|                                                         | 8         | mA max | $DV_{DD} = 2.7 \text{ V}$ to 3.6 V, Core CLK = 12.58 MHz                           |

| AV <sub>DD</sub> Current                                | 170       | μA max | $AV_{DD} = 5.25 \text{ V}$ , Core CLK = 12.58 MHz                                  |

| Power Supply Currents Idle Mode <sup>16, 17</sup>       |           |        |                                                                                    |

| DV <sub>DD</sub> Current                                | 1.2       | mA max | $DV_{DD} = 4.75 \text{ V to } 5.25 \text{ V}, \text{ Core CLK} = 1.57 \text{ MHz}$ |

|                                                         | 750       | μA typ | $DV_{DD} = 2.7 \text{ V to } 3.6 \text{ V}, \text{ Core CLK} = 1.57 \text{ MHz}$   |

| AV <sub>DD</sub> Current                                | 140       | μA typ | Measured @ $AV_{DD}$ = 5.25 V, Core CLK = 1.57 MHz                                 |

| DV <sub>DD</sub> Current                                | 2         | mA typ | $DV_{DD} = 4.75 \text{ V}$ to 5.25 V, Core CLK = 12.58 MHz                         |

|                                                         | 1         | mA typ | $DV_{DD} = 2.7 \text{ V}$ to 3.6 V, Core CLK = 12.58 MHz                           |

| AV <sub>DD</sub> Current                                | 140       | μA typ | Measured at $AV_{DD} = 5.25 \text{ V}$ , Core CLK = 12.58 MHz                      |

| Power Supply Currents Power-Down Mode <sup>16, 17</sup> |           |        | Core CLK = 1.57 MHz or 12.58 MHz                                                   |

| DV <sub>DD</sub> Current                                | 50        | μA max | $DV_{DD}$ = 4.75 V to 5.25 V, Osc. On, TIC On                                      |

|                                                         | 20        | μA max | $DV_{DD}$ = 2.7 V to 3.6 V, Osc. On, TIC On                                        |

| AV <sub>DD</sub> Current                                | 1         | μA max | Measured at $AV_{DD} = 5.25 \text{ V}$ , Osc. On or Osc. Off                       |

| DV <sub>DD</sub> Current                                | 20        | μA max | $DV_{DD} = 4.75 \text{ V to } 5.25 \text{ V, Osc. Off}$                            |

|                                                         | 5         | μA typ | $DV_{DD}$ = 2.7 V to 3.6 V, Osc. Off                                               |

| Typical Additional Power Supply Currents                |           |        | Core CLK = 1.57 MHz, $AV_{DD} = DV_{DD} = 5 \text{ V}$                             |

| $(AI_{DD}$ and $DI_{DD})$                               |           |        |                                                                                    |

| PSM Peripheral                                          | 50        | μA typ |                                                                                    |

| Primary ADC                                             | 1         | mA typ |                                                                                    |

| Auxiliary ADC                                           | 500       | μA typ |                                                                                    |

| DAC                                                     | 150       | μA typ |                                                                                    |

| Dual Current Sources                                    | 400       | μA typ |                                                                                    |

#### NOTES

reduced code range of 48 to 4095, 0 to  $V_{REF}$

reduced code range of 48 to 3995, 0 to V<sub>DD</sub>.

$V_{REF}$  = REFIN(+) to REFIN(-) voltage and  $V_{REF}$  = 1.25 V when internal ADC  $V_{REF}$  is selected.

$RN = decimal\ equivalent\ of\ RN2,\ RN1,\ RN0,\ e.g.,\ V_{REF} = 2.5\ V\ and\ RN2,\ RN1,\ RN0 = 1,\ 1,\ 0\ the\ Range_{ADC} = \pm 1.28\ V.$

In unipolar mode the effective range is 0 V to 1.28 V in our example.

Rev. B -7-

<sup>&</sup>lt;sup>1</sup>Temperature Range −40°C to +85°C.

<sup>&</sup>lt;sup>2</sup>These numbers are not production tested but are guaranteed by Design and/or Characterization data on production release.

$<sup>^{3}</sup>$ The primary ADC is factory-calibrated at 25  $^{\circ}$ C with AV<sub>DD</sub> = DV<sub>DD</sub> = 5 V yielding this full-scale error. If user power supply or temperature conditions are significantly different from these, an Internal Full-Scale Calibration will restore this error to this level.

<sup>&</sup>lt;sup>4</sup>Gain Error Drift is a span drift. To calculate Full-Scale Error Drift, add the Offset Error Drift to the Gain Error Drift times the full-scale input.

$<sup>^5</sup>$ The auxiliary ADC is factory-calibrated at 25 °C with AV<sub>DD</sub> = DV<sub>DD</sub> = 5 V yielding this full-scale error of -2.5 LSB. A system zero-scale and full-scale calibration will remove this error altogether.

<sup>&</sup>lt;sup>6</sup>DAC linearity and AC Specifications are calculated using:

<sup>&</sup>lt;sup>7</sup>Gain Error is a measure of the span error of the DAC.

<sup>&</sup>lt;sup>8</sup>In general terms, the bipolar input voltage range to the primary ADC is given by Range ADC =  $\pm (V_{REF} 2^{RN})/125$ , where:

$<sup>^{9}1.25~\</sup>mathrm{V}$  is used as the reference voltage to the ADC when internal  $\mathrm{V}_{\mathrm{REF}}$  is selected via XREF0 and XREF1 bits in ADC0CON and ADC1CON respectively.

<sup>&</sup>lt;sup>10</sup>In bipolar mode, the Auxiliary ADC can only be driven to a minimum of A<sub>GND</sub> – 30 mV as indicated by the Auxiliary ADC absolute AIN voltage limits. The bipolar range is still –V<sub>REF</sub> to +V<sub>REF</sub>; however, the negative voltage is limited to –30 mV.

<sup>&</sup>lt;sup>11</sup>Pins configured in I<sup>2</sup>C-compatible mode or SPI mode, pins configured as digital inputs during this test.

<sup>&</sup>lt;sup>12</sup>Pins configured in I<sup>2</sup>C-compatible mode only.

<sup>&</sup>lt;sup>13</sup>Flash/EE Memory Reliability Characteristics apply to both the Flash/EE program memory and Flash/EE data memory.

<sup>14</sup>Endurance is qualified to 100 Kcycles as per JEDEC Std. 22 method A117 and measured at -40°C, +25°C and +85°C, typical endurance at 25°C is 700 Kcycles.

<sup>&</sup>lt;sup>15</sup>Retention lifetime equivalent at junction temperature (T<sub>J</sub>) = 55°C as per JEDEC Std. 22, Method A117. Retention lifetime based on an activation energy of 0.6eV will derate with junction temperature as shown in Figure 27 in the Flash/EE Memory description section of this data sheet.

<sup>&</sup>lt;sup>16</sup>Power Supply current consumption is measured in Normal, Idle, and Power-Down Modes under the following conditions:

Normal Mode: Reset = 0.4 V, Digital I/O pins = open circuit, Core Clk changed via CD bits in PLLCON, Core Executing internal software loop.

Idle Mode: Reset = 0.4 V, Digital I/O pins = open circuit, Core Clk changed via CD bits in PLLCON, PCON.0 = 1, Core Execution suspended in idle mode.

Power-Down Mode: Reset = 0.4 V, All P0 pins and P1.2-P1.7 pins = 0.4 V, All other digital I/O pins are open circuit, Core Clk changed via CD bits in PLLCON, PCON.1 = 1, Core Execution suspended in power-down mode, OSC turned ON or OFF via OSC\_PD bit (PLLCON.7) in PLLCON SFR.

<sup>&</sup>lt;sup>17</sup>DV<sub>DD</sub> power supply current will typically increase by 3 mA (3 V operation) and 10 mA (5 V operation) during a Flash/EE memory program or erase cycle. Specifications subject to change without notice

| Paramete                                     | r                                  | Min | Max | Unit | Figure |

|----------------------------------------------|------------------------------------|-----|-----|------|--------|

| I <sup>2</sup> C-COMPATIBLE INTERFACE TIMING |                                    |     |     |      |        |

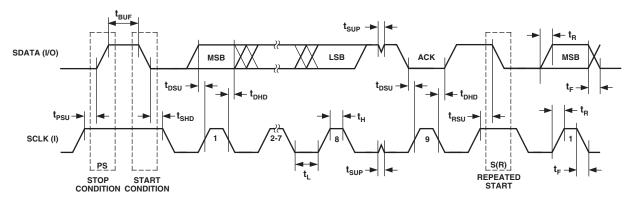

| $t_{\mathrm{L}}$                             | SCLOCK Low Pulsewidth              | 4.7 |     | μs   | 7      |

| t <sub>H</sub>                               | SCLOCK High Pulsewidth             | 4.0 |     | μs   | 7      |

| $t_{ m SHD}$                                 | Start Condition Hold Time          | 0.6 |     | μs   | 7      |

| $t_{DSU}$                                    | Data Setup Time                    | 100 |     | μs   | 7      |

| $t_{ m DHD}$                                 | Data Hold Time                     |     | 0.9 | μs   | 7      |

| $t_{RSU}$                                    | Setup Time for Repeated Start      | 0.6 |     | μs   | 7      |

| $t_{PSU}$                                    | Stop Condition Setup Time          | 0.6 |     | μs   | 7      |

| $t_{ m BUF}$                                 | Bus Free Time between a STOP       | 1.3 |     | μs   | 7      |

|                                              | Condition and a START Condition    |     |     | '    |        |

| $t_R$                                        | Rise Time of Both SCLOCK and SDATA |     | 300 | ns   | 7      |

| $t_{\rm F}$                                  | Fall Time of Both SCLOCK and SDATA |     | 300 | ns   | 7      |

| t <sub>SUP</sub> *                           | Pulsewidth of Spike Suppressed     |     | 50  | ns   | 7      |

<sup>\*</sup>Input filtering on both the SCLOCK and SDATA inputs suppresses noise spikes less than 50 ns.

Figure 7. 1<sup>2</sup>C-Compatible Interface Timing

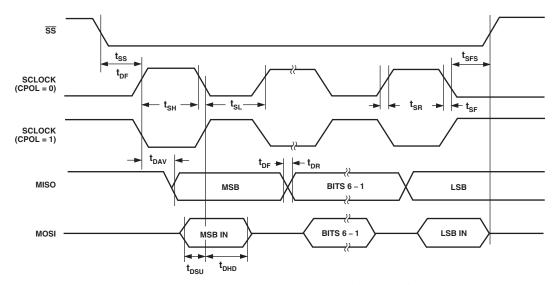

| Parameter                        |                                          |     | Тур | Max | Unit | Figure |

|----------------------------------|------------------------------------------|-----|-----|-----|------|--------|

| SPI SLAVE MODE TIMING (CPHA = 1) |                                          |     |     |     |      |        |

| $t_{SS}$                         | SS to SCLOCK Edge                        | 0   |     |     | ns   | 10     |

| $t_{SL}$                         | SCLOCK Low Pulsewidth                    |     | 330 |     | ns   | 10     |

| $t_{SH}$                         | SCLOCK High Pulsewidth                   |     | 330 |     | ns   | 10     |

| $t_{\mathrm{DAV}}$               | Data Output Valid after SCLOCK Edge      |     |     | 50  | ns   | 10     |

| $t_{DSU}$                        | Data Input Setup Time before SCLOCK Edge | 100 |     |     | ns   | 10     |

| $t_{ m DHD}$                     | Data Input Hold Time after SCLOCK Edge   | 100 |     |     | ns   | 10     |

| $t_{ m DF}$                      | Data Output Fall Time                    |     | 10  | 25  | ns   | 10     |

| $t_{DR}$                         | Data Output Rise Time                    |     | 10  | 25  | ns   | 10     |

| $t_{SR}$                         | SCLOCK Rise Time                         |     | 10  | 25  | ns   | 10     |

| $t_{SF}$                         | SCLOCK Fall Time                         |     | 10  | 25  | ns   | 10     |

| $t_{SFS}$                        | SS High after SCLOCK Edge                | 0   |     |     | ns   | 10     |

Figure 10. SPI Slave Mode Timing (CPHA = 1)

## **ABSOLUTE MAXIMUM RATINGS**

$(T_A = 25^{\circ}C \text{ unless otherwise noted})$

| (1 <sub>A</sub> = 23 C unless otherwise noted)        |                                       |

|-------------------------------------------------------|---------------------------------------|

| Parameter                                             | Ratings                               |

| AV <sub>DD</sub> to AGND                              | −0.3 V to +7 V                        |

| AV <sub>DD</sub> to DGND                              | −0.3 V to +7 V                        |

| DV <sub>DD</sub> to AGND                              | −0.3 V to +7 V                        |

| DV <sub>DD</sub> to DGND                              | −0.3 V to +7 V                        |

| AGND to DGND <sup>1</sup>                             | -0.3 V to +0.3 V                      |

| AV <sub>DD</sub> to DV <sub>DD</sub>                  | −2 V to +5 V                          |

| Analog Input Voltage to AGND <sup>2</sup>             | -0.3 V to AV <sub>DD</sub> $+0.3$ V   |

| Reference Input Voltage to AGND                       | -0.3 V to AV <sub>DD</sub> +0.3 V     |

| AIN/REFIN Current (Indefinite)                        | 30 mA                                 |

| Digital Input Voltage to DGND                         | -0.3 V to DV <sub>DD</sub> +0.3 V     |

| Digital Output Voltage to DGND                        | -0.3  V to DV <sub>DD</sub> $+0.3  V$ |

| Operating Temperature Range                           | -40°C to +85°C                        |

| Storage Temperature Range                             | −65°C to +150°C                       |

| Junction Temperature                                  | 150°C                                 |

| $\theta_{JA}$ Thermal Impedance (MQFP)                | 90°C/W                                |

| $\theta_{JA}$ Thermal Impedance (LFCSP Base Floating) | 52°C/W                                |

| Lead Temperature, Soldering                           |                                       |

| Vapor Phase (60 sec)                                  | 215°C                                 |

| Infrared (15 sec)                                     | 220°C                                 |

|                                                       |                                       |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

-18- Rev. B

<sup>&</sup>lt;sup>1</sup> AGND and DGND are shorted internally on the ADuC816.

<sup>&</sup>lt;sup>2</sup> Applies to P1.2 to P1.7 pins operating in analog or digital input modes.

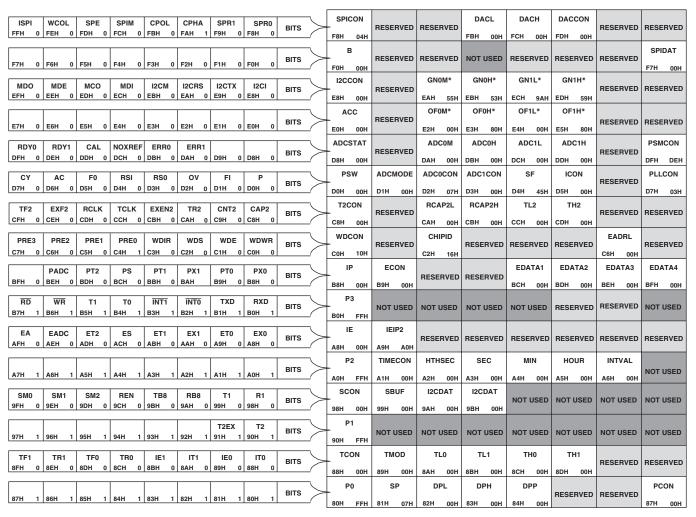

#### SPECIAL FUNCTION REGISTERS

All registers except the program counter and the four generalpurpose register banks, reside in the SFR area. The SFR registers include control, configuration, and data registers that provide an interface between the CPU and all on-chip peripherals. Figure 17 shows a full SFR memory map and SFR contents on RESET; NOT USED indicates unoccupied SFR locations. Unoccupied locations in the SFR address space are not implemented; i.e., no register exists at this location. If an unoccupied location is read, an unspecified value is returned. SFR locations reserved for future use are shaded (RESERVED) and should not be accessed by user software.

\*CALIBRATION COEFFICIENTS ARE PRECONFIGURED AT POWER-UP TO FACTORY-CALIBRATED VALUES.

# THESE BITS ARE CONTAINED IN THIS BYTE. BIT MNEMONIC BIT BIT ADDRESS BIT MNEMONIC BIT BIT VALUE SFR ADDRESS

SFR NOTE: SFRs WHOSE ADDRESSES END IN 0H OR 8H ARE BIT-ADDRESSABLE.

Figure 17. Special Function Register Locations and Reset Values

**-24**- Rev. B

#### ICON (Current Sources Control Register)

Used to control and configure the various excitation and burnout current source options available on-chip.

SFR Address D5H

Power-On Default Value 00H

Bit Addressable No

|  | ВО | ADC1IC | ADC0IC | I2PIN | I1PIN | I2EN | I1EN |  |

|--|----|--------|--------|-------|-------|------|------|--|

|  |    |        |        |       |       |      |      |  |

#### Table VIII. ICON SFR Bit Designations

| Bit | Name   | Description                                                                                       |

|-----|--------|---------------------------------------------------------------------------------------------------|

| 7   |        | Reserved for Future Use.                                                                          |

| 6   | BO     | Burnout Current Enable Bit.                                                                       |

|     |        | Set by user to enable both transducer burnout current sources in the primary ADC signal paths.    |

|     |        | Cleared by user to disable both transducer burnout current sources.                               |

| 5   | ADC1IC | Auxiliary ADC Current Correction Bit.                                                             |

|     |        | Set by user to allow scaling of the Auxiliary ADC by an internal current source calibration word. |

| 4   | ADC0IC | Primary ADC Current Correction Bit.                                                               |

|     |        | Set by user to allow scaling of the Primary ADC by an internal current source calibration word.   |

| 3   | I2PIN* | Current Source-2 Pin Select Bit.                                                                  |

|     |        | Set by user to enable current source-2 (200 μA) to external Pin 3 (P1.2/DAC/IEXC1).               |

|     |        | Cleared by user to enable current source-2 (200 µA) to external Pin 4 (P1.3/AIN5/IEXC2).          |

| 2   | I1PIN* | Current Source-1 Pin Select Bit.                                                                  |

|     |        | Set by user to enable current source-1 (200 μA) to external Pin 4 (P1.3/AIN5/IEXC2).              |

|     |        | Cleared by user to enable current source-1 (200 µA) to external Pin 3 (P1.2/DAC/IEXC1).           |

| 1   | I2EN   | Current Source-2 Enable Bit.                                                                      |

|     |        | Set by user to turn on excitation current source-2 (200 $\mu$ A).                                 |

|     |        | Cleared by user to turn off excitation current source-2 (200 μA).                                 |

| 0   | I1EN   | Current Source-1 Enable Bit.                                                                      |

|     |        | Set by user to turn on excitation current source-1 (200 $\mu$ A).                                 |

|     |        | Cleared by user to turn off excitation current source-1 (200 μA).                                 |

<sup>\*</sup>Both current sources can be enabled to the same external pin, yielding a 400  $\mu A$  current source.

#### ADC0H/ADC0M (Primary ADC Conversion Result Registers)

These two 8-bit registers hold the 16-bit conversion result from the Primary ADC.

| SFR Address            | ADC0H | High Data Byte   | DBH |

|------------------------|-------|------------------|-----|

|                        | ADC0M | Middle Data Byte | DAH |

| Power-On Default Value | 00H   | Both Registers   |     |

| Bit Addressable        | No    | Both Registers   |     |

#### ADC1H/ADC1L (Auxiliary ADC Conversion Result Registers)

These two 8-bit registers hold the 16-bit conversion result from the Auxiliary ADC.

| SFR Address            | ADC1H | High Data Byte | DDH |

|------------------------|-------|----------------|-----|

|                        | ADC1L | Low Data Byte  | DCH |

| Power-On Default Value | 00H   | Both Registers |     |

| Bit Addressable        | No    | Both Registers |     |

Rev. B —29—

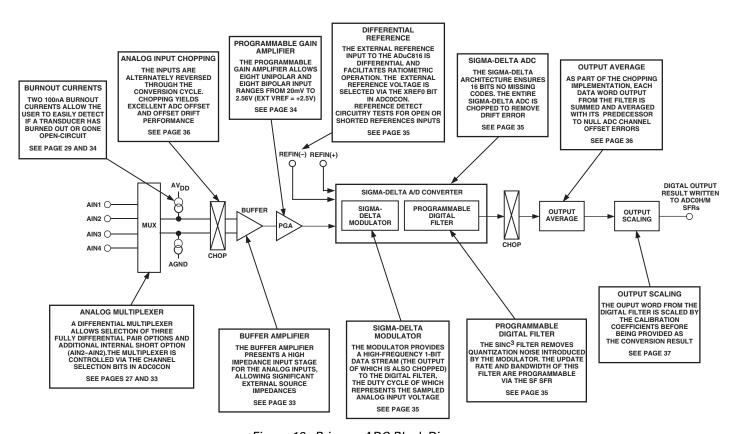

# PRIMARY AND AUXILIARY ADC CIRCUIT DESCRIPTION OVERVIEW

The ADuC816 incorporates two independent sigma-delta ADCs (Primary and Auxiliary) with on-chip digital filtering intended for the measurement of wide dynamic range, low frequency signals such as those in weigh-scale, strain-gauge, pressure transducer or temperature measurement applications.

#### **Primary ADC**

This ADC is intended to convert the primary sensor input. The input is buffered and can be programmed for one of 8 input ranges from  $\pm 20$  mV to  $\pm 2.56$  V being driven from one of three differential input channel options AIN1/2, AIN3/4, or AIN3/2. The input channel is internally buffered allowing the part to handle significant source impedances on the analog input, allowing R/C filtering (for noise rejection or RFI reduction) to be placed on

the analog inputs if required. On-chip burnout currents can also be turned on. These currents can be used to check that a transducer on the selected channel is still operational before attempting to take measurements.

The ADC employs a sigma-delta conversion technique to realize up to 16 bits of no missing codes performance. The sigma-delta modulator converts the sampled input signal into a digital pulse train whose duty cycle contains the digital information. A Sinc3 programmable low-pass filter is then employed to decimate the modulator output data stream to give a valid data conversion result at programmable output rates from 5.35 Hz (186.77 ms) to 105.03 Hz (9.52 ms). A Chopping scheme is also employed to minimize ADC offset errors. A block diagram of the Primary ADC is shown in Figure 18.

Figure 18. Primary ADC Block Diagram

Rev. B -31-

mended. Deriving the reference input voltage across an external resistor, as shown in Figure 52, will mean that the reference input sees a significant external source impedance. External decoupling on the REFIN(+) and REFIN(-) pins would not be recommended in this type of circuit configuration.

#### Reference Detect

The ADuC816 includes on-chip circuitry to detect if the part has a valid reference for conversions or calibrations. If the voltage between the external REFIN(+) and REFIN(-) pins goes below 0.3 V or either the REFIN(+) or REFIN(-) inputs is open circuit, the ADuC816 detects that it no longer has a valid reference. In this case, the NOXREF bit of the ADCSTAT SFR is set to a 1. If the ADuC816 is performing normal conversions and the NOXREF bit becomes active, the conversion results revert to all 1s. Therefore, it is not necessary to continuously monitor the status of the NOXREF bit when performing conversions. It is only necessary to verify its status if the conversion result read from the ADC Data Register is all 1s.

If the ADuC816 is performing either an offset or gain calibration and the NOXREF bit becomes active, the updating of the respective calibration registers is inhibited to avoid loading incorrect coefficients to these registers, and the appropriate ERR0 or ERR1 bits in the ADCSTAT SFR are set. If the user is concerned about verifying that a valid reference is in place every time a calibration is performed, the status of the ERR0 or ERR1 bit should be checked at the end of the calibration cycle.

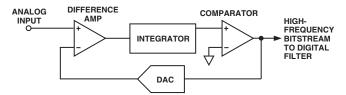

#### Sigma-Delta Modulator

A sigma-delta ADC generally consists of two main blocks, an analog modulator and a digital filter. In the case of the ADuC816 ADCs, the analog modulators consist of a difference amplifier, an integrator block, a comparator, and a feedback DAC as illustrated in Figure 20.

Figure 20. Sigma-Delta Modulator Simplified Block Diagram

In operation, the analog signal sample is fed to the difference amplifier along with the output of the feedback DAC. The difference between these two signals is integrated and fed to the comparator. The output of the comparator provides the input to the feedback DAC so the system functions as a negative feedback loop that tries to minimize the difference signal. The digital data that represents the analog input voltage is contained in the duty cycle of the pulse train appearing at the output of the comparator. This duty cycle data can be recovered as a data word using a subsequent digital filter stage. The sampling frequency of the modulator loop is many times higher than the bandwidth of the input signal. The integrator in the modulator shapes the quantization noise (which results from the analog-to-digital conversion) so that the noise is pushed toward one-half of the modulator frequency.

#### **Digital Filter**

The output of the sigma-delta modulator feeds directly into the digital filter. The digital filter then band-limits the response to a frequency significantly lower than one-half of the modulator

frequency. In this manner, the 1-bit output of the comparator is translated into a band-limited, low noise output from the ADuC816 ADCs.

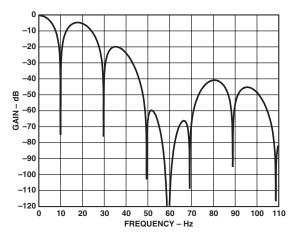

The ADuC816 filter is a low-pass, Sinc<sup>3</sup> or (sinx/x)<sup>3</sup> filter whose primary function is to remove the quantization noise introduced at the modulator. The cutoff frequency and decimated output data rate of the filter are programmable via the SF (Sinc Filter) SFR as described in Table VII.

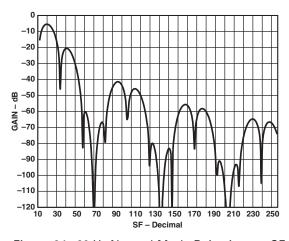

Figure 21 shows the frequency response of the ADC channel at the default SF word of 69 dec or 45 hex, yielding an overall output update rate of just under 20 Hz.

It should be noted that this frequency response allows frequency components higher than the ADC Nyquist frequency to pass through the ADC, in some cases without significant attenuation. These components may, therefore, be aliased and appear in-band after the sampling process.

It should also be noted that rejection of mains-related frequency components, i.e., 50 Hz and 60 Hz, is seen to be at level of >65 dB at 50 Hz and >100 dB at 60 Hz. This confirms the data sheet specifications for 50 Hz/60 Hz Normal Mode Rejection (NMR) at a 20 Hz update rate.

Figure 21. Filter Response, SF = 69 dec

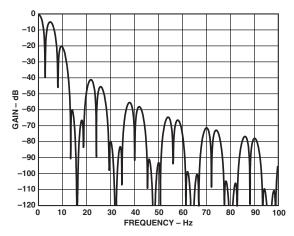

The response of the filter, however, will change with SF word as can be seen in Figure 22, which shows >90 dB NMR at 50 Hz and >70 dB NMR at 60 Hz when SF = 255 dec.

Figure 22. Filter Response, SF = 255 dec

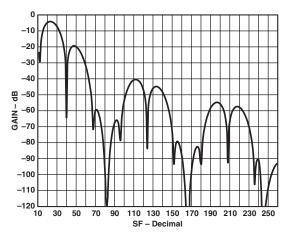

Figures 23 and 24 show the NMR for 50 Hz and 60 Hz across the full range of SF word, i.e., SF = 13 dec to SF = 255 dec.

Figure 23. 50 Hz Normal Mode Rejection vs. SF

Figure 24. 60 Hz Normal Mode Rejection vs. SF

#### **ADC Chopping**

Both ADCs on the ADuC816 implement a chopping scheme whereby the ADC repeatability reverses its inputs. The decimated digital output words from the Sinc<sup>3</sup> filters therefore have a positive offset and negative offset term included.

As a result, a final summing stage is included in each ADC so that each output word from the filter is summed and averaged with the previous filter output to produce a new valid output result to be written to the ADC data SFRs. In this way, while the ADC throughput or update rate is as discussed earlier and illustrated in Table VII, the full settling time through the ADC (or the time to a first conversion result), will actually be given by  $2 \times t_{ADC}$ .

The chopping scheme incorporated in the ADuC816 ADC results in excellent dc offset and offset drift specifications and is extremely beneficial in applications where drift, noise rejection, and optimum EMI rejection are important factors.

#### Calibration

The ADuC816 provides four calibration modes that can be programmed via the mode bits in the ADCMODE SFR detailed in Table IV. In fact, every ADuC816 has already been factory calibrated. The resultant Offset and Gain calibration coefficients for both the primary and auxiliary ADCs are stored on-chip in manufacturing-specific Flash/EE memory locations. At poweron, these factory calibration coefficients are automatically downloaded to the calibration registers in the ADuC816 SFR space. Each ADC (primary and auxiliary) has dedicated calibration SFRs, these have been described earlier as part of the general ADC SFR description. However, the factory calibration values in the ADC calibration options are initiated and that ADC is enabled via the ADC enable bits in ADCMODE.

Even though an internal offset calibration mode is described below, it should be recognized that both ADCs are chopped. This chopping scheme inherently minimizes offset and means that an internal offset calibration should never be required. Also, because factory 5 V/25°C gain calibration coefficients are automatically present at power-on, an internal full-scale calibration will only be required if the part is being operated at 3 V or at temperatures significantly different from 25°C.

The ADuC816 offers "internal" or "system" calibration facilities. For full calibration to occur on the selected ADC, the calibration logic must record the modulator output for two different input conditions. These are "zero-scale" and "full-scale" points. These points are derived by performing a conversion on the different input voltages provided to the input of the modulator during calibration. The result of the "zero-scale" calibration conversion is stored in the Offset Calibration Registers for the appropriate ADC. The result of the "full-scale" calibration conversion is stored in the Gain Calibration Registers for the appropriate ADC. With these readings, the calibration logic can calculate the offset and the gain slope for the input-to-output transfer function of the converter.

During an "internal" zero-scale or full-scale calibration, the respective "zero" input and "full-scale" input are automatically connected to the ADC input pins internally to the device. A "system" calibration, however, expects the system zero-scale and system full-scale voltages to be applied to the external ADC pins before the calibration mode is initiated. In this way external ADC errors are taken into account and minimized as a result of system calibration. It should also be noted that to optimize calibration accuracy, all ADuC816 ADC calibrations are carried out automatically at the slowest update rate.

Internally in the ADuC816, the coefficients are normalized before being used to scale the words coming out of the digital filter. The offset calibration coefficient is subtracted from the result prior to the multiplication by the gain coefficient. All ADuC816 ADC specifications will only apply after a zero-scale and full-scale calibration at the operating point (supply voltage/temperature) of interest.

From an operational point of view, a calibration should be treated like another ADC conversion. A zero-scale calibration (if required) should always be carried out before a full-scale calibration. System software should monitor the relevant ADC RDY0/1 bit in the ADCSTAT SFR to determine end of calibration via a polling sequence or interrupt driven routine.

**-36**- Rev. B

#### Serial Safe Mode

This mode disables serial download capability on the device. If Serial Safe mode is activated and an attempt is made to reset the part into serial download mode, i.e., RESET asserted and deasserted with PSEN low, the part will interpret the serial download reset as a normal reset only. It will, therefore, not enter serial download mode but only execute a normal reset sequence. Serial Safe mode can only be disabled by initiating a code-erase command in parallel programming mode.

#### Using the Flash/EE Data Memory

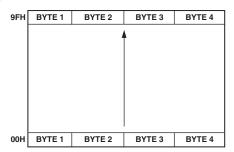

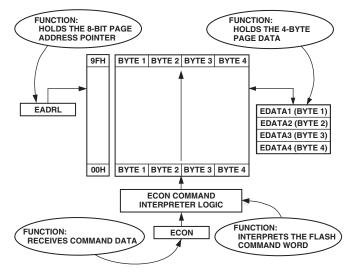

The user Flash/EE data memory array consists of 640 bytes that are configured into 160 (00H to 9FH) 4-byte pages as shown in Figure 29.

Figure 29. Flash/EE Data Memory Configuration

As with other ADuC816 user-peripheral circuits, the interface to this memory space is via a group of registers mapped in the SFR space. A group of four data registers (EDATA1-4) are used to hold 4-byte page data just accessed. EADRL is used to hold the 8-bit address of the page to be accessed. Finally, ECON is an 8-bit control register that may be written with one of five Flash/EE memory access commands to trigger various read, write, erase, and verify functions. These registers can be summarized as follows:

B9H

SFR Address:

Function: Controls access to 640 Bytes Flash/EE Data Space. Default: 00H EADRL: SFR Address: C<sub>6</sub>H Function: Holds the Flash/EE Data Page Address. (640 Bytes => 160 Page Addresses.) Default: 00H EDATA 1-4: SFR Address: BCH to BFH respectively Function: Holds Flash/EE Data memory page write or page read data bytes. EDATA1-2 -> 00H Default: EDATA3-4 -> 00H

A block diagram of the SFR interface to the Flash/EE Data Memory array is shown in Figure 30.

Figure 30. Flash/EE Data Memory Control and Configuration

#### ECON-Flash/EE Memory Control SFR

This SFR acts as a command interpreter and may be written with one of five command modes to enable various read, program and erase cycles as detailed in Table XIII:

Table XIII. ECON-Flash/EE Memory Control Register Command Modes

| Command<br>Byte | Command Mode                                                                                                                                                                                                                                           |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01H             | READ COMMAND.                                                                                                                                                                                                                                          |

|                 | Results in four bytes being read into EDATA1–4                                                                                                                                                                                                         |

| 02H             | from memory page address contained in EADRL. PROGRAM COMMAND.                                                                                                                                                                                          |

| 0211            | Results in four bytes (EDATA1–4) being written                                                                                                                                                                                                         |

|                 | to memory page address in EADRL. This write                                                                                                                                                                                                            |

|                 | command assumes the designated "write" page has                                                                                                                                                                                                        |

|                 | been pre-erased.                                                                                                                                                                                                                                       |

| 03H             | RESERVED FOR INTERNAL USE.                                                                                                                                                                                                                             |

|                 | 03H should not be written to the ECON SFR.                                                                                                                                                                                                             |

| 04H             | VERIFY COMMAND.                                                                                                                                                                                                                                        |

|                 | Allows the user to verify if data in EDATA1–4 is contained in page address designated by EADRL. A subsequent read of the ECON SFR will result in a "zero" being read if the verification is valid, a nonzero value will be read to indicate an invalid |

| 05H             | verification. ERASE COMMAND.                                                                                                                                                                                                                           |

| USH             |                                                                                                                                                                                                                                                        |

|                 | Results in an erase of the 4-byte page designated in EADRI.                                                                                                                                                                                            |

| 06H             | ERASE-ALL COMMAND.                                                                                                                                                                                                                                     |

| 0011            | Results in erase of the full Flash/EE Data memory                                                                                                                                                                                                      |

|                 | 160-page (640 bytes) array.                                                                                                                                                                                                                            |

| 07H to FFH      | RESERVED COMMANDS.                                                                                                                                                                                                                                     |

|                 | Commands reserved for future use.                                                                                                                                                                                                                      |

ECON:

# USER INTERFACE TO OTHER ON-CHIP ADuC816 PERIPHERALS

The following section gives a brief overview of the various peripherals also available on-chip. A summary of the SFRs used to control and configure these peripherals is also given.

#### DAC

The ADuC816 incorporates a 12-bit, voltage output DAC on-chip. It has a rail-to-rail voltage output buffer capable of

DACCON DAC Control Register

SFR Address FDH

Power-On Default Value 00H

Bit Addressable No

driving 10 k $\Omega$ /100 pF. It has two selectable ranges, 0 V to  $V_{REF}$  (the internal bandgap 2.5 V reference) and 0 V to  $AV_{DD}$ . It can operate in 12-bit or 8-bit mode. The DAC has a control register, DACCON, and two data registers, DACH/L. The DAC output can be programmed to appear at Pin 3 or Pin 12. It should be noted that in 12-bit mode, the DAC voltage output will be updated as soon as the DACL data SFR has been written; therefore, the DAC data registers should be updated as DACH first followed by DACL.

|  |  |  | DACPIN | DAC8 | DACRN | DACCLR | DACEN |

|--|--|--|--------|------|-------|--------|-------|

|--|--|--|--------|------|-------|--------|-------|

**Table XIV. DACCON SFR Bit Designations**

| Bit | Name   | Description                                                                                  |

|-----|--------|----------------------------------------------------------------------------------------------|

| 7   |        | Reserved for Future Use.                                                                     |

| 6   |        | Reserved for Future Use.                                                                     |

| 5   |        | Reserved for Future Use.                                                                     |

| 4   | DACPIN | DAC Output Pin Select.                                                                       |

|     |        | Set by the user to direct the DAC output to Pin 12 (P1.7/AIN4/DAC).                          |

|     |        | Cleared by user to direct the DAC output to Pin 3 (P1.2/DAC/IEXC1).                          |

| 3   | DAC8   | DAC 8-bit Mode Bit.                                                                          |

|     |        | Set by user to enable 8-bit DAC operation. In this mode the 8-bits in DACL SFR are routed to |

|     |        | the 8 MSBs of the DAC and the 4 LSBs of the DAC are set to zero.                             |

|     |        | Cleared by user to operate the DAC in its normal 12-bit mode of operation.                   |

| 2   | DACRN  | DAC Output Range Bit.                                                                        |

|     |        | Set by user to configure DAC range of $0 - AV_{DD}$ .                                        |

|     |        | Cleared by user to configure DAC range of $0 - 2.5 \text{ V}$ .                              |

| 1   | DACCLR | DAC Clear Bit.                                                                               |

|     |        | Set to "1" by user to enable normal DAC operation.                                           |

|     |        | Cleared to "0" by user to reset DAC data registers DACI/H to zero.                           |

| 0   | DACEN  | DAC Enable Bit.                                                                              |

|     |        | Set to "1" by user to enable normal DAC operation.                                           |

|     |        | Cleared to "0" by user to power-down the DAC.                                                |

DACH/L DAC Data Registers

Function DAC Data Registers, written by user to update the DAC output.

SFR Address DACL (DAC Data Low Byte) ->FBH

DACH (DAC Data High Byte) ->FCH

Power-On Default Value 00H ->Both Registers

Bit Addressable No ->Both Registers

The 12-bit DAC data should be written into DACH/L right-justified such that DACL contains the lower eight bits, and the lower nibble of DACH contains the upper four bits.

Rev. B —41—

TIMECON TIC CONTROL REGISTER

SFR Address A1H

Power-On Default Value 00H

Bit Addressable No

| <br> | ITS1 | ITS0 | STI | TII | TIEN | TCEN |   |

|------|------|------|-----|-----|------|------|---|

|      |      |      |     |     |      |      | 1 |

#### Table XVI. TIMECON SFR Bit Designations

| Bit | Name | Description                                                                                            |  |  |  |  |  |

|-----|------|--------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7   |      | Reserved for Future Use.                                                                               |  |  |  |  |  |

| 6   |      | Reserved for Future Use. For future product code compatibility this bit should be written as a '1.'    |  |  |  |  |  |

| 5   | ITS1 | Interval Timebase Selection Bits.                                                                      |  |  |  |  |  |

| 4   | ITS0 | Written by user to determine the interval counter update rate.                                         |  |  |  |  |  |

|     |      | ITS1 ITS0 Interval Timebase                                                                            |  |  |  |  |  |

|     |      | 0 0 1/128 Second                                                                                       |  |  |  |  |  |

|     |      | 0 1 Seconds                                                                                            |  |  |  |  |  |

|     |      | 1 0 Minutes                                                                                            |  |  |  |  |  |

|     |      | 1 Hours                                                                                                |  |  |  |  |  |

| 3   | STI  | Single Time Interval Bit.                                                                              |  |  |  |  |  |

|     |      | Set by user to generate a single interval timeout. If set, a timeout will clear the TIEN bit.          |  |  |  |  |  |

|     |      | Cleared by user to allow the interval counter to be automatically reloaded and start counting again at |  |  |  |  |  |

|     |      | each interval timeout.                                                                                 |  |  |  |  |  |

| 2   | TII  | TIC Interrupt Bit.                                                                                     |  |  |  |  |  |

|     |      | Set when the 8-bit Interval Counter matches the value in the INTVAL SFR.                               |  |  |  |  |  |

|     |      | Cleared by user software.                                                                              |  |  |  |  |  |

| 1   | TIEN | Time Interval Enable Bit.                                                                              |  |  |  |  |  |

|     |      | Set by user to enable the 8-bit time interval counter.                                                 |  |  |  |  |  |

|     |      | Cleared by user to disable and clear the contents of the interval counter.                             |  |  |  |  |  |

| 0   | TCEN | Time Clock Enable Bit.                                                                                 |  |  |  |  |  |

|     |      | Set by user to enable the time clock to the time interval counters.                                    |  |  |  |  |  |

|     |      | Cleared by user to disable the clock to the time interval counters and clear the time interval SFRs.   |  |  |  |  |  |

|     |      | The time registers (HTHSEC, SEC, MIN and HOUR) can be written while TCEN is low.                       |  |  |  |  |  |

**-44-** Rev. B

#### **Power Supply Monitor**

As its name suggests, the Power Supply Monitor, once enabled, monitors both supplies (AVDD or DVDD) on the ADuC816. It will indicate when any of the supply pins drop below one of four user-selectable voltage trip points from 2.63 V to 4.63 V. For correct operation of the Power Supply Monitor function,  $AV_{\rm DD}$  must be equal to or greater than 2.7 V. Monitor function is controlled via the PSMCON SFR. If enabled via the IEIP2 SFR, the monitor will interrupt the core using the PSMI bit in the

PSMCON SFR. This bit will not be cleared until the failing power supply has returned above the trip point for at least 250 ms. This monitor function allows the user to save working registers to avoid possible data loss due to the low supply condition, and also ensures that normal code execution will not resume until a safe supply level has been well established. The supply monitor is also protected against spurious glitches triggering the interrupt circuit.

PSMCON Power Supply Monitor Control Register

SFR Address DFH

Power-On Default Value DEH

Bit Addressable No

| СМРО | СМРА | PSMI | TPD1 | TPD0 | TPA1 | TPA0 | PSMEN |

|------|------|------|------|------|------|------|-------|

|      |      |      |      |      |      |      |       |

#### Table XVIII. PSMCON SFR Bit Designations

| Bit | Name  | Description                                                                                       |

|-----|-------|---------------------------------------------------------------------------------------------------|

| 7   | CMPD  | DVDD Comparator Bit.                                                                              |

|     |       | This is a read-only bit and directly reflects the state of the DVDD comparator.                   |

|     |       | Read "1" indicates the DVDD supply is above its selected trip point.                              |

|     |       | Read "0" indicates the DVDD supply is below its selected trip point.                              |

| 6   | CMPA  | AVDD Comparator Bit.                                                                              |

|     |       | This is a read-only bit and directly reflects the state of the AVDD comparator.                   |

|     |       | Read "1" indicates the AVDD supply is above its selected trip point.                              |

|     |       | Read "0" indicates the AVDD supply is below its selected trip point.                              |

| 5   | PSMI  | Power Supply Monitor Interrupt Bit.                                                               |

|     |       | This bit will be set high by the MicroConverter if either CMPA or CMPD are low, indicating        |

|     |       | low analog or digital supply. The PSMI bit can be used to interrupt the processor. Once CMPD      |

|     |       | and/or CMPA return (and remain) high, a 250 ms counter is started. When this counter times        |

|     |       | out, the PSMI interrupt is cleared. PSMI can also be written by the user. However, if either com- |

|     |       | parator output is low, it is not possible for the user to clear PSMI.                             |

| 4   | TPD1  | DVDD Trip Point Selection Bits.                                                                   |

| 3   | TPD0  | These bits select the DVDD trip-point voltage as follows:                                         |

|     |       | TPD1 TPD0 Selected DVDD Trip Point (V)                                                            |

|     |       | 0 0 4.63                                                                                          |

|     |       | 0 1 3.08                                                                                          |

|     |       | 1 0 2.93                                                                                          |

|     |       | 1 1 2.63                                                                                          |

| 2   | TPA1  | AVDD Trip Point Selection Bits.                                                                   |

| 1   | TPA0  | These bits select the AVDD trip-point voltage as follows:                                         |

|     |       | TPA1 TPA0 Selected AVDD Trip Point (V)                                                            |

|     |       | 0 0 4.63                                                                                          |

|     |       | 0 1 3.08                                                                                          |

|     |       | 1 0 2.93                                                                                          |

|     |       | 1 1 2.63                                                                                          |

| 0   | PSMEN | Power Supply Monitor Enable Bit.                                                                  |

|     |       | Set to "1" by the user to enable the Power Supply Monitor Circuit.                                |

|     |       | Cleared to "0" by the user to disable the Power Supply Monitor Circuit.                           |

Rev. B —47—

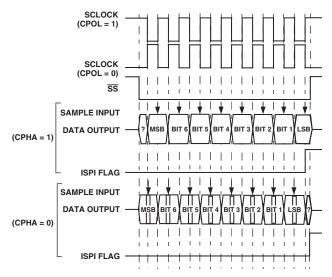

#### SERIAL PERIPHERAL INTERFACE

The ADuC816 integrates a complete hardware Serial Peripheral Interface (SPI) interface on-chip. SPI is an industry standard synchronous serial interface that allows eight bits of data to be synchronously transmitted and received simultaneously, i.e., full duplex. It should be noted that the SPI physical interface is shared with the I<sup>2</sup>C interface and therefore the user can only enable one or the other interface at any given time (see SPE in SPICON below). The system can be configured for Master or Slave operation and typically consists of four pins, namely:

#### MISO (Master In, Slave Out Data I/O Pin), Pin 14

The MISO (master in slave out) pin is configured as an input line in master mode and an output line in slave mode. The MISO line on the master (data in) should be connected to the MISO line in the slave device (data out). The data is transferred as byte wide (8-bit) serial data, MSB first.

#### MOSI (Master Out, Slave In Pin), Pin 27

The MOSI (master out slave in) pin is configured as an output line in master mode and an input line in slave mode. The MOSI line on the master (data out) should be connected to the MOSI line in the slave device (data in). The data is transferred as byte wide (8-bit) serial data, MSB first.

#### SCLOCK (Serial Clock I/O Pin), Pin 26

The master clock (SCLOCK) is used to synchronize the data being transmitted and received through the MOSI and MISO data lines. A single data bit is transmitted and received in each SCLOCK period. Therefore, a byte is transmitted/received after eight SCLOCK periods. The SCLOCK pin is configured as an output in master mode and as an input in slave mode. In master mode the bit-rate, polarity and phase of the clock are controlled by the CPOL, CPHA, SPR0 and SPR1 bits in the SPICON SFR (see Table XIX below). In slave mode the SPICON register will have to be configured with the phase and polarity (CPHA and CPOL) of the expected input clock. In both master and slave mode the data is transmitted on one edge of the SCLOCK signal and sampled on the other. It is important therefore that the CPHA and CPOL are configured the same for the master and slave devices.

#### SS (Slave Select Input Pin), Pin 13

The Slave Select  $(\overline{SS})$  input pin is only used when the ADuC816 is configured in slave mode to enable the SPI peripheral. This line is active low. Data is only received or transmitted in slave mode when the  $\overline{SS}$  pin is low, allowing the ADuC816 to be used in single master, multislave SPI configurations. If CPHA = 1 then the  $\overline{SS}$  input may be permanently pulled low. With CPHA = 0 then the  $\overline{SS}$  input must be driven low before the first bit in a byte wide transmission or reception and return high again after the last bit in that byte wide transmission or reception. In SPI Slave Mode, the logic level on the external  $\overline{SS}$  pin (Pin 13), can be read via the SPR0 bit in the SPICON SFR.

The following SFR registers are used to control the SPI interface.

SPICON: SPI Control Register

SFR Address F8H

Power-On Default Value 04H

Bit Addressable Yes

| ISPI WCOL SPE SPIM CPOL CPHA SPR1 SPR0 |

|----------------------------------------|

|----------------------------------------|

#### Table XIX. SPICON SFR Bit Designations

| Bit | Name | Description                                                                         |

|-----|------|-------------------------------------------------------------------------------------|

| 7   | ISPI | SPI Interrupt Bit.                                                                  |

|     |      | Set by MicroConverter at the end of each SPI transfer.                              |

|     |      | Cleared directly by user code or indirectly by reading the SPIDAT SFR               |

| 6   | WCOL | Write Collision Error Bit.                                                          |

|     |      | Set by MicroConverter if SPIDAT is written to while an SPI transfer is in progress. |

|     |      | Cleared by user code.                                                               |

| 5   | SPE  | SPI Interface Enable Bit.                                                           |

|     |      | Set by user to enable the SPI interface.                                            |

|     |      | Cleared by user to enable the I <sup>2</sup> C interface.                           |

| 4   | SPIM | SPI Master/Slave Mode Select Bit.                                                   |

|     |      | Set by user to enable Master Mode operation (SCLOCK is an output).                  |

|     |      | Cleared by user to enable Slave Mode operation (SCLOCK is an input).                |

| 3   | CPOL | Clock Polarity Select Bit.                                                          |

|     |      | Set by user if SCLOCK idles high.                                                   |

|     |      | Cleared by user if SCLOCK idles low.                                                |

| 2   | СРНА | Clock Phase Select Bit.                                                             |

|     |      | Set by user if leading SCLOCK edge is to transmit data.                             |

|     |      | Cleared by user if trailing SCLOCK edge is to transmit data.                        |

**-48-** Rev. B

Table XIX. SPICON SFR Bit Designations (continued)

| Bit | Name         | Description                                                                                                                                                                                                                                                                                                                                                              |

|-----|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 0 | SPR1<br>SPR0 | SPI Bit-Rate Select Bits.  These bits select the SCLOCK rate (bit-rate) in Master Mode as follows:  SPR1 SPR0 Selected Bit Rate  0 0 f <sub>CORE</sub> /2  0 1 f <sub>CORE</sub> /4  1 0 f <sub>CORE</sub> /8  1 1 f <sub>CORE</sub> /16  In SPI Slave Mode, i.e., SPIM = 0, the logic level on the external $\overline{SS}$ pin (Pin 13), can be read via the SPR0 bit. |

NOTE

The CPOL and CPHA bits should both contain the same values for master and slave devices.

| SPIDAT | SPI Data Register |

|--------|-------------------|

|--------|-------------------|

Function The SPIDAT SFR is written by the user to transmit data over the SPI interface or read by user

code to read data just received by the SPI interface.

SFR Address F7H

Power-On Default Value 00H

Bit Addressable No

#### Using the SPI Interface

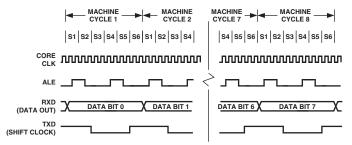

Depending on the configuration of the bits in the SPICON SFR shown in Table XIX, the ADuC816 SPI interface will transmit or receive data in a number of possible modes. Figure 32 shows all possible ADuC816 SPI configurations and the timing relationships and synchronization between the signals involved. Also shown in this figure is the SPI interrupt bit (ISPI) and how it is triggered at the end of each byte-wide communication.

Figure 32. SPI Timing, All Modes

#### SPI Interface—Master Mode

In master mode, the SCLOCK pin is always an output and generates a burst of eight clocks whenever user code writes to the SPIDAT register. The SCLOCK bit rate is determined by SPR0 and SPR1 in SPICON. It should also be noted that the  $\overline{SS}$  pin is not used in master mode. If the ADuC816 needs to assert the  $\overline{SS}$  pin on an external slave device, a Port digital output pin should be used.

In master mode a byte transmission or reception is initiated by a write to SPIDAT. Eight clock periods are generated via the SCLOCK pin and the SPIDAT byte being transmitted via MOSI. With each SCLOCK period a data bit is also sampled via MISO. After eight clocks, the transmitted byte will have been completely transmitted and the input byte will be waiting in the input shift register. The ISPI flag will be set automatically and an interrupt will occur if enabled. The value in the shift register will be latched into SPIDAT.

#### SPI Interface—Slave Mode

In slave mode the SCLOCK is an input. The  $\overline{SS}$  pin must also be driven low externally during the byte communication.

Transmission is also initiated by a write to SPIDAT. In slave mode, a data bit is transmitted via MISO and a data bit is received via MOSI through each input SCLOCK period. After eight clocks, the transmitted byte will have been completely transmitted and the input byte will be waiting in the input shift register. The ISPI flag will be set automatically and an interrupt will occur if enabled. The value in the shift register will be latched into SPIDAT only when the transmission/reception of a byte has been completed. The end of transmission occurs after the eighth clock has been received, if CPHA = 1 or when  $\overline{SS}$  returns high if CPHA = 0.

Rev. B —49—

T2CON Timer/Counter 2 Control Register

SFR Address C8H

Power-On Default Value 00H

Bit Addressable Yes

| TF2 EXF2 | RCLK TCLK | EXEN2 TR2 | CNT2 CAP2 |

|----------|-----------|-----------|-----------|

|----------|-----------|-----------|-----------|

#### Table XXV. T2CON SFR Bit Designations

| Bit | Name  | Description                                                                                               |

|-----|-------|-----------------------------------------------------------------------------------------------------------|

| 7   | TF2   | Timer 2 Overflow Flag.                                                                                    |

|     |       | Set by hardware on a timer 2 overflow. TF2 will not be set when either RCLK or TCLK = 1.                  |

|     |       | Cleared by user software.                                                                                 |

| 6   | EXF2  | Timer 2 External Flag.                                                                                    |