Welcome to E-XFL.COM

Embedded - Microcontrollers - Application Specific: Tailored Solutions for Precision and Performance

#### Embedded - Microcontrollers - Application Specific

represents a category of microcontrollers designed with unique features and capabilities tailored to specific application needs. Unlike general-purpose microcontrollers, application-specific microcontrollers are optimized for particular tasks, offering enhanced performance, efficiency, and functionality to meet the demands of specialized applications.

#### What Are <u>Embedded - Microcontrollers -</u> <u>Application Specific</u>?

Application enacific microcontrollars are analyzared to

#### Details

| Details                 |                                                                             |

|-------------------------|-----------------------------------------------------------------------------|

| Product Status          | Active                                                                      |

| Applications            | USB Type C                                                                  |

| Core Processor          | ARM® Cortex®-M0                                                             |

| Program Memory Type     | FLASH (128kB)                                                               |

| Controller Series       | -                                                                           |

| RAM Size                | 8K x 8                                                                      |

| Interface               | I <sup>2</sup> C, SPI, UART/USART, USB                                      |

| Number of I/O           | 16                                                                          |

| Voltage - Supply        | 2.7V ~ 21.5V                                                                |

| Operating Temperature   | -40°C ~ 85°C (TA)                                                           |

| Mounting Type           | Surface Mount                                                               |

| Package / Case          | 40-UFQFN Exposed Pad                                                        |

| Supplier Device Package | 40-QFN (6x6)                                                                |

| Purchase URL            | https://www.e-xfl.com/product-detail/infineon-technologies/cypd3123-40lqxit |

|                         |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Logic Block Diagram

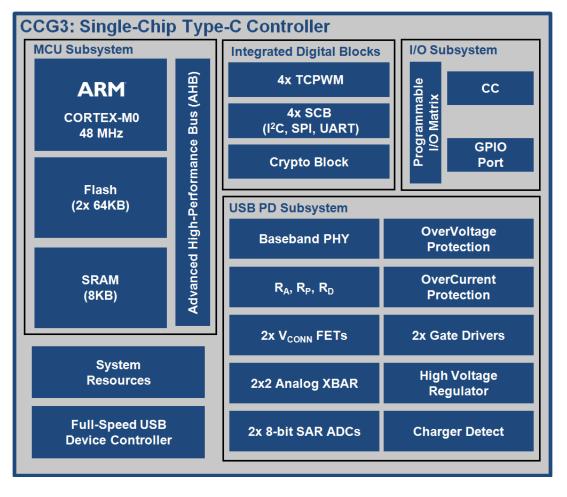

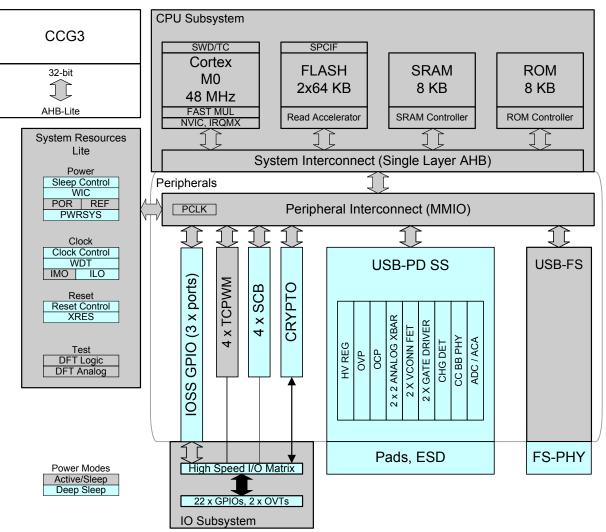

### EZ-PD CCG3 Block Diagram

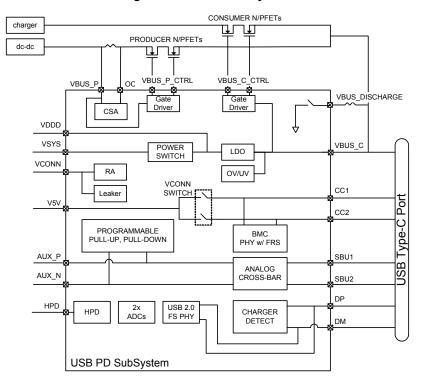

The OV/UV (Over-Voltage/Under-Voltage) block monitors the VBUS\_C supply for programmable over-voltage and under-voltage conditions. The CSA amplifies the voltage across an external sense resistor, which is proportional to the current being drawn from the external DC-DC VBUS supply converter. The CSA output can either be measured with an ADC or configured to detect an over-current condition. The VBUS\_P and VBUS\_C gate drivers control the gates of external power FETs for the VBUS\_C and VBUS\_P supplies. The gate drivers can be configured to support both P and N type external power FETs. The gate drivers are configured by default for nFET devices. In applications using pFETs, the gate drivers must be appropriately configured. The OV/UV and CSA blocks can generate interrupts to automatically turn off the power FETs for the VBUS\_C

discharge switch allows for discharging the VBUS\_C line through an external resistor.

The USB-PD sub-system also contains two 8-bit Successive Approximation Register (SAR) ADCs for analog to digital conversions. Each ADC includes an 8-bit DAC and a comparator. The DAC output forms the positive input of the comparator. The negative input of the comparator is from a 4-input multiplexer. The four inputs of the multiplexer are a pair of global analog multiplex busses, an internal bandgap voltage and an internal voltage proportional to the absolute temperature. Each GPIO pin can be connected to the global Analog Multiplex Busses through a switch, which allows either ADC to sample the pin voltage. When sensing the GPIO pin voltage with an ADC, the pin voltage cannot exceed the VDDD or VDDIO supply values.

#### Figure 2. USB-PD Subsystem

### Full-Speed USB Subsystem

The FSUSB subsystem contains a full speed USB device controller as described in the Integrated Billboard Device section.

### Peripherals

### Serial Communication Blocks (SCB)

EZ-PD CCG3 has four SCBs, which can be configured to implement an I<sup>2</sup>C, SPI, or UART interface. The hardware I<sup>2</sup>C blocks implement full multi-master and slave interfaces capable of multimaster arbitration. In the SPI mode, the SCB blocks can be configured to act as master or slave.

In the I<sup>2</sup>C mode, the SCB blocks are capable of operating at speeds of up to 1 Mbps (Fast Mode Plus) and have flexible buffering options to reduce interrupt overhead and latency for the CPU. These blocks also support I<sup>2</sup>C that creates a mailbox address range in the memory of EZ-PD CCG3 and effectively reduce I<sup>2</sup>C communication to reading from and writing to an array in memory. In addition, the blocks support 8-deep FIFOs for receive and transmit which, by increasing the time given for the CPU to read data, greatly reduce the need for clock stretching caused by the CPU not having read data on time.

The  $I^2C$  peripherals are compatible with the  $I^2C$  Standard-mode, Fast-mode, and Fast-mode Plus devices as defined in the NXP  $I^2C$ -bus specification and user manual (UM10204).

The I<sup>2</sup>C bus I/Os are implemented with GPIO in open-drain modes.

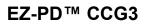

### Pinouts

### Table 2. CCG3 Pin Description for 42-CSP, 32-QFN and 40-QFN Devices

| Pin Map<br>42-CSP | Pin Map<br>32-QFN | Pin Map<br>40-QFN | Name         | Description                                                                              |

|-------------------|-------------------|-------------------|--------------|------------------------------------------------------------------------------------------|

| A5                | N/A               | 1                 | VBUS_P_CTRL1 | VBUS Gate Driver Control 1 for Producer Switch                                           |

| A6                | 1                 | 2                 | VBUS_P_CTRL0 | VBUS Gate Driver Control 0 for Producer Switch                                           |

| B6                | 2                 | 3                 | CC2          | USB PD connector detect/Configuration Channel 2                                          |

| C5                | N/A               | N/A               | CC2          | USB PD connector detect/Configuration Channel 2                                          |

| D4                | 3                 | 4                 | V5V          | 5.0V – 5.5V supply for VCONN FETs                                                        |

| C6                | 4                 | 5                 | CC1          | USB PD connector detect/Configuration Channel 1                                          |

| D6                | N/A               | N/A               | CC1          | USB PD connector detect/Configuration Channel 1                                          |

| E6                | N/A               | 6                 | VCONN        | VCONN Input - provides Ra termination for cable applications                             |

| F6                | 5                 | 7                 | P1.0         | GPIO/UART_2_TX / SPI_2_MISO                                                              |

| D5                | N/A               | 8                 | P1.1         | GPIO/UART_2_RX / SPI_2_SEL                                                               |

| E5                | 6                 | 9                 | P1.2         | GPIO/UART_0_RX/ UART_3_CTS/ SPI_3_MOSI/<br>I2C_3_SCL / HPD                               |

| G6                | 7                 | 10                | P1.3         | GPIO/UART_0_TX/ UART_3_RTS/ SPI_3_CLK/<br>I2C_3_SDA                                      |

| E4                | N/A               | 11                | AUX_P / P1.6 | DisplayPort AUX_P signal / GPIO / UART_1_TX /<br>SPI_1_MISO                              |

| F5                | 8                 | 12                | SBU1 / P1.4  | USB Type-C SBU1 signal / GPIO / UART_3_TX/<br>SPI_3_MISO/ SWD_1_CLK                      |

| G5                | 9                 | 13                | SBU2 / P1.5  | USB Type-C SBU2 signal / GPIO / UART_3_RX/<br>SPI_3_SEL/ SWD_1_DAT                       |

| G4                | N/A               | 14                | AUX_N / P1.7 | DisplayPort AUX_N signal / GPIO / UART_1_RX /<br>SPI_1_SEL                               |

| F4                | 10                | 15                | P2.0         | GPIO / UART_1_CTS / SPI_1_CLK/ I2C_1_SCL /<br>SWD_0_DAT                                  |

| G3                | 11                | 16                | P2.1         | GPIO / UART_1_RTS / SPI_1_MOSI/ I2C_1_SDA /<br>SWD_0_CLK                                 |

| G2                | 13                | 17                | VDDD         | VDDD Supply Input / Output (2.7 V–5.5 V)                                                 |

| F3                | 14                | 18                | VDDIO        | 1.71 V–5.5 V supply for I/Os. This supply also powers the global analog multiplex buses. |

| F2                | 15                | 19                | VCCD         | 1.8V regulator output for filter capacitor                                               |

| G1                | 16                | 20                | VSYS         | System Power Supply (2.7 V–5.5 V)                                                        |

| F1                | 17                | 21                | DPLUS        | USB 2.0 DP                                                                               |

| E1                | 18                | 22                | DMINUS       | USB 2.0 DM                                                                               |

| E2                | 19                | 23                | P2.4         | GPIO                                                                                     |

| D3                | 20                | 24                | P2.5         | GPIO / UART_0_TX/ SPI_0_MOSI                                                             |

| D2                | N/A               | 25                | P2.6         | GPIO / UART_0_RX/ SPI_0_CLK                                                              |

| D1                | 21                | 26                | XRES         | External Reset Input. Internally pulled-up to VDDIO.                                     |

| C3                | 22                | 27                | P0.0         | I2C_0_SDA / GPIO_OVT / UART_0_CTS / SPI_0_SEL/<br>TCPWM0                                 |

| C2                | 23                | 28                | P0.1         | I2C_0_SCL / GPIO_OVT / UART_0_RTS / SPI_0_MISO/<br>TCPWM1                                |

Figure 6. Pinout of 42-WLCSP Bottom (Balls Up) View

### **Available Firmware and Software Tools**

### **EZ-PD** Configuration Utility

The EZ-PD Configuration Utility is a GUI-based Microsoft Windows application developed by Cypress to guide a CCGx user through the process of configuring and programming the chip. The utility allows users to:

1. Select and configure the parameters they want to modify

2. Program the resulting configuration onto the target CCGx device.

The utility works with the Cypress supplied CCG1, CCG2, CCG3, and CCG4 kits, which host the CCGx controllers along with a USB interface. This version of the EZ-PD Configuration Utility supports configuration and firmware update operations on CCGx controllers implementing EMCA and Display Dongle applications. Support for other applications, such as Power Adapters and Notebook port controllers, will be provided in later versions of the utility.

You can download the EZ-PD Configuration Utility and its associated documentation at the following link:

http://www.cypress.com/documentation/software-and-drivers/ez-pd-configuration-utility

### **CCG3 Programming and Bootloading**

There are two ways to program application firmware into a CCG3 device:

- 1. Programming the device flash over SWD Interface

- 2. Application firmware update over specific interfaces (CC, USB, I<sup>2</sup>C)

Generally, the CCG3 devices are programmed over SWD interface only during development or during the manufacturing process of the end product. Once the end product is manufactured, the CCG3 device's application firmware can be updated via the appropriate bootloader interface.

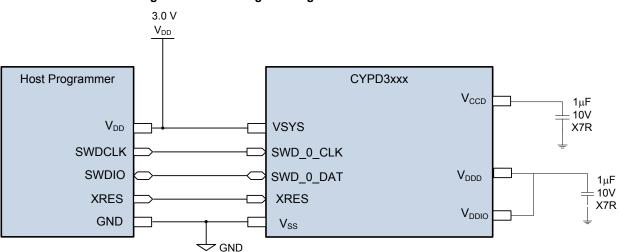

### Programming the Device Flash over SWD Interface

CCG3 family of devices can be programmed using the SWD interface. Cypress provides a programming kit (CY8CKIT-002 MiniProg3 Kit) called MiniProg3 which can be used to program the flash as well as debug firmware. The flash is programmed by downloading the information from a hex file. This hex file is a binary file generated as an output of building the firmware project in PSoC Creator Software. Click here for more information on how to use the MiniProg3 programmer. There are many third party programmers that support mass programming in a manufacturing environment. As shown in the block diagram in Figure 7, the SWD\_0\_DAT and SWD\_0\_CLK pins are connected to the host programmer's SWDIO (data) and SWDCLK (clock) pins respectively. During SWD programming, the device can be powered by the host programmer by connecting its VTARG (power supply to the target device) to VSYS pin of CCG3 device. If the CCG3 device is powered using an on-board power supply, it can be programmed using the "Reset Programming" option. For more details, refer to the CYPD3XXX Programming Specifications.

The CYPD3105 device for Thunderbolt cable applications is pre-programmed with a micro-bootloader that allows users to program the flash using the alternate SWD pins (SBU1 for SWD\_1\_CLK and SBU2 for SWD\_1\_DAT) that can be connected to the SBU interface of a Type-C connector. Note that this interface can be used to program the flash only once. Subsequent re-programming of this device can be done through the primary SWD interface (SWD\_0\_CLK and SWD\_0\_DAT pins). Irrespective of which SWD interface is used for programming the device, once the device is programmed with the hex file provided by Cypress for thunderbolt cable application, subsequent updates to the application firmware can be done over the CC line. Refer to Application Firmware Update over Specific Interfaces (I2C, CC, USB) for more details.

Figure 7. Connecting the Programmer to CYPD3xxx Device

# Application Firmware Update over Specific Interfaces (I<sup>2</sup>C, CC, USB)

The application firmware can be updated over three different interfaces depending on the default firmware programmed into the CCG3 device. Refer to Table 38 for more details on default firmware that various part numbers of the CCG3 family of devices are pre-programmed with (Note that some of the devices have bootloader only and some have bootloader plus application firmware). The application firmware provided by Cypress for all CCG3 applications have dual images. This allows fail-safe update of the alternate image while executing from the current image. For more information, refer to the EZ-PD Configuration Utility User Manual.

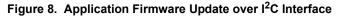

#### Application Firmware Update over I<sup>2</sup>C Interface

This method primarily applies to CYPD3122, CYPD3125 and CYPD3126 devices of the CCG3 family. In these applications, the CCG3 device interfaces to an on-board application processor or an embedded controller over I<sup>2</sup>C interface. Refer to Figure 8 for more details. Cypress provides pseudo-code for the host processor for updating the CCG3 device firmware.

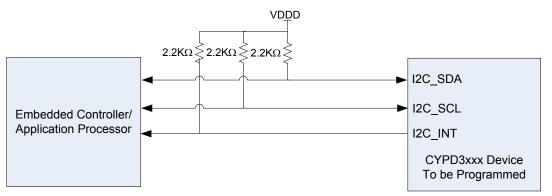

Application Firmware Update over CC Line

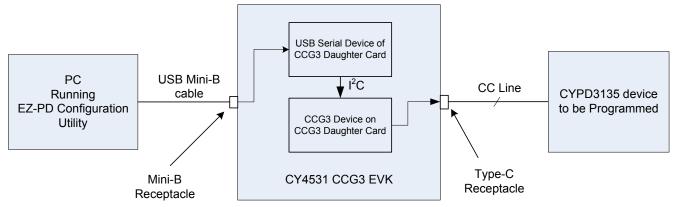

This method primarily applies to CYPD3135 device of the CCG3 family. In these applications, the CY4531 CCG3 EVK can be used to send programming and configuration data as Cypress specific Vendor Defined Messages (VDMs) over the CC line. The

CY4531 CCG3 EVK is connected to the system containing CCG3 device on one end and a Windows PC running the EZ-PDTM Configuration Utility as shown in Figure 9 on the other end to program the CCG3 device.

#### Application Firmware Update over USB

This method primarily applies to the CYPD3120 and CYPD3121 devices of the CCG3 family. In these applications, the firmware update can be performed over the D+/D- lines (USB2.0) using various possible options as shown in Figure 10. Option 1 is to have a Windows PC running EZ-PD<sup>TM</sup> Configuration Utility connected to the device to be programmed via the CY4531

CCG3 EVK. This setup can be avoided using option 2, where the user has a Type-A to Type-C cable. This option requires that the system contain the CCG3 device to be programmed to have a Type-C receptacle. The other option (Option 3) is to have a Windows PC with a native Type-C connector as shown in Figure 10.

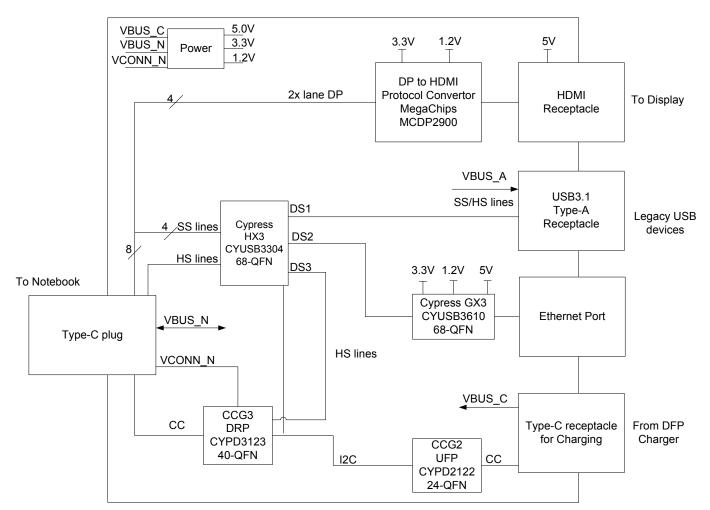

Figure 16 illustrates a CCG3 device based Charge-through Dongle application block diagram. This Charge-through dongle application also implements Cypress's USB SuperSpeed Hub controller HX3 (CYUSB3304-68LTXI) available in 68-QFN package, Low-power single chip USB 3.0 to Gigabit Ethernet Bridge Controller GX3 (CYUSB3610-68LTXC) available in 68-QFN package and the CCG2 (CYPD2122-24LQXI) which acts as an Upstream Facing Port (UFP) and sinks power when connected to USB Type-C chargers. This application enables connectivity between a USB Type-C Notebook and HDMI Display, legacy USB device and Gigabit Ethernet while also connecting a USB Type-C charging cable. The Charge-Through Dongle solution allows simultaneous HDMI display, Superspeed data transfers, Ethernet connection and charging of a USB Type-C Notebook. Charge-Through Dongle is also widely known as Multiport Adapter. More details including the schematic of the CCG3 device based Charge-through Dongle reference design can be found here.

### **Electrical Specifications**

### Absolute Maximum Ratings

### Table 3. Absolute Maximum Ratings

| Parameter                   | Description                                                                          | Min   | Тур | Мах       | Units | Details/Conditions                                                     |

|-----------------------------|--------------------------------------------------------------------------------------|-------|-----|-----------|-------|------------------------------------------------------------------------|

| V <sub>SYS_MAX</sub>        | Digital supply relative to $V_{SS}$                                                  | -0.5  | -   | 6         | V     |                                                                        |

| V <sub>5V</sub>             | Max supply voltage relative to $V_{SS}$                                              | -     | -   | 6         | V     |                                                                        |

| V <sub>BUS_MAX_ON</sub>     | Max supply voltage relative to $V_{SS}$ , $V_{BUS}$ regulator enabled                | -     | -   | 26        | V     |                                                                        |

| V                           | Max supply voltage relative to $V_{SS}, V_{BUS}$ regulator enabled 100% of the time  | _     | _   | 24.5      | V     |                                                                        |

| V <sub>BUS_MAX_OFF</sub>    | Max supply voltage relative to $V_{SS},$ $V_{BUS}$ regulator enabled 25% of the time | _     | _   | 26        | V     | Absolute max                                                           |

| V <sub>DDIO_MAX</sub>       | Max supply voltage relative to $V_{SS}$                                              | -     | -   | 6         | V     |                                                                        |

| V <sub>GPIO_ABS</sub>       | GPIO voltage                                                                         | -0.5  | -   | VDDIO+0.5 | V     |                                                                        |

| V <sub>GPIO_OVT_ABS</sub>   | OVT GPIO voltage                                                                     | -0.5  | -   | 6         | V     |                                                                        |

| I <sub>GPIO_ABS</sub>       | Maximum current per GPIO                                                             | -25   | -   | 25        | mA    |                                                                        |

| V <sub>CONN_MAX</sub>       | Max voltage relative to $V_{SS}$                                                     | -     | -   | 6         | V     |                                                                        |

| V <sub>CC_ABS</sub>         | Max voltage on CC1 and CC2 pins                                                      | -     | -   | 6         | V     |                                                                        |

| I <sub>GPIO_INJECTION</sub> | GPIO injection current, Max for $V_{IH}$ > VDDD, and Min for $V_{IL}$ < $V_{SS}$     | -0.5  | -   | 0.5       | mA    | Absolute max, current injected per pin                                 |

| ESD_HBM                     | Electrostatic discharge human body model                                             | 2200  | _   | -         | V     | -                                                                      |

| ESD_CDM                     | Electrostatic discharge charged device model                                         | 500   | -   | -         | V     | -                                                                      |

| LU                          | Pin current for latch-up                                                             | -100  | -   | 100       | mA    | Tested at 125 °C                                                       |

| ESD_IEC_CON                 | Electrostatic discharge IEC61000-4-2                                                 | 8000  | -   | -         | V     | Contact discharge on CC1, CC2, VBUS, DPLUS, DMINUS, SBU1 and SBU2 pins |

| ESD_IEC_AIR                 | Electrostatic discharge IEC61000-4-2                                                 | 15000 | _   | -         | V     | Air discharge for CC1, CC2, VBUS,<br>DPLUS, DMINUS, SBU1 and SBU2 pins |

### **Device-Level Specifications**

All specifications are valid for –40  $^{\circ}C \leq TA \leq$  105  $^{\circ}C$  and TJ  $\leq$  120  $^{\circ}C,$  except where noted.

### Table 4. DC Specifications

| SID.PWR#1<br>SID.PWR#1_A<br>SID.PWR#23<br>SID.PWR#13<br>SID.PWR#13_A | VSYS<br>VSYS<br>VCONN<br>VDDIO<br>VDDIO<br>VCCD | –<br>Power Supply Input<br>Voltage<br>IO Supply Voltage<br>IO Supply Voltage for<br>ADC operation                                 | 2.7<br>3<br>2.7<br>1.71 | _<br><br>          | 5.5<br>5.5         | V<br>V  | UFP Mode.<br>DFP/DRP or Gate Driver Modes                                                                                                                                             |

|----------------------------------------------------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------|--------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SID.PWR#23<br>SID.PWR#13                                             | VCONN<br>VDDIO<br>VDDIO                         | Voltage<br>IO Supply Voltage<br>IO Supply Voltage for                                                                             | 2.7                     | -                  |                    | V       | DFP/DRP or Gate Driver Modes                                                                                                                                                          |

| SID.PWR#13                                                           | VDDIO<br>VDDIO                                  | Voltage<br>IO Supply Voltage<br>IO Supply Voltage for                                                                             |                         |                    |                    |         |                                                                                                                                                                                       |

|                                                                      | VDDIO                                           | IO Supply Voltage for                                                                                                             | 1.71                    |                    | 5.5                | V       | _                                                                                                                                                                                     |

| SID PWR#13 A                                                         |                                                 |                                                                                                                                   |                         | -                  | 5.5 <sup>[2]</sup> | V       | 2.7V < VDDD < 5.5 V                                                                                                                                                                   |

|                                                                      | VCCD                                            |                                                                                                                                   | 2.7                     | -                  | 5.5                | V       | 2.7V < VDDD < 5.5 V                                                                                                                                                                   |

| SID.PWR24                                                            |                                                 | Output Voltage for core<br>Logic                                                                                                  | _                       | 1.8                | -                  | V       | -                                                                                                                                                                                     |

| SID.PWR#4                                                            | IDD                                             | Supply current                                                                                                                    | _                       | 25                 | _                  | mA      | From VSYS or VBUS<br>VBUS = 5V,<br>$T_A = 25 \degree C / VSYS = 5 V$ , TA = 25 $\degree C$<br>FS USB, CC IO in Tx or Rx, no I/O sourcing<br>current, 2 SCBs at 1 Mbps, CPU at 24 MHz. |

| SID.PWR#1_B                                                          | VSYS                                            | Power supply for USB operation                                                                                                    | 4.5                     | _                  | 5.5                | V       | USB configured, USB Regulator enabled                                                                                                                                                 |

| SID.PWR#1_C                                                          | VSYS                                            | Power supply for USB operation                                                                                                    | 3.15                    | _                  | 3.45               | V       | USB configured, USB Regulator disabled                                                                                                                                                |

| SID.PWR#1_D                                                          | VSYS                                            | Power supply for charger detect/emulation operation                                                                               | 3.15                    | -                  | 5.5                | V       | –40 °C to +85 °C T <sub>A</sub>                                                                                                                                                       |

| SID.PWR#27                                                           | VBUS                                            | Power supply input voltage                                                                                                        | 3.5                     | -                  | 21.5               | V       | FS USB disabled. Total current consumption<br>from VBUS <15 mA.                                                                                                                       |

| SID.PwR#28                                                           | VBUS                                            | Power supply input voltage for USB operation                                                                                      | 4.5                     | _                  | 21.5               | V       | FS USB configured, USB Regulator disabled                                                                                                                                             |

| SID.PWR#30                                                           | VBUS_P                                          | Power supply input voltage                                                                                                        | 4.00                    | -                  | 21.5               | V       |                                                                                                                                                                                       |

| SID.PWR#15                                                           | C <sub>efc</sub>                                | External regulator voltage bypass for VCCD                                                                                        | 1                       | 1.3                | 1.6                | μF      | X5R ceramic or better                                                                                                                                                                 |

| SID.PWR#16                                                           | C <sub>exc</sub>                                | Power supply decoupling<br>capacitor for VSYS                                                                                     | 0.8                     | 1                  | _                  | μF      | X5R ceramic or better                                                                                                                                                                 |

| Sleep Mode. VS                                                       | YS = 2.7 V to                                   | o 5.5 V. Typical values me                                                                                                        | asured                  | at V <sub>DD</sub> | ) = 3.3 \          | / and T |                                                                                                                                                                                       |

| SID25A                                                               | I <sub>DD20A</sub>                              | CC, I <sup>2</sup> C, WDT wakeup<br>on.<br>IMO at 48 MHz.                                                                         | -                       | 3.5                | _                  | mA      | VSYS = 3.3 V, T <sub>A</sub> = 25 °C, All blocks except<br>CPU are on, CC IO on, USB in Suspend<br>Mode, no I/O sourcing current                                                      |

| Deep Sleep Mod                                                       | le                                              |                                                                                                                                   |                         |                    |                    |         |                                                                                                                                                                                       |

| SID_DS                                                               | I <sub>DD_DS</sub>                              | VSYS = 3.0 to 3.6 V. CC<br>Attach, $l^2$ C, WDT<br>Wakeup on.                                                                     | -                       | 30                 | -                  | μA      | Power Source = VSYS, DFP Mode, Type-C<br>Not Attached. CC Attach, I <sup>2</sup> C and WDT<br>enabled for Wakeup.                                                                     |

| XRES Current                                                         | 1                                               | 1                                                                                                                                 |                         | 1                  |                    | 1       |                                                                                                                                                                                       |

| SID307                                                               | I <sub>DD_XR</sub>                              | Supply current while<br>XRES asserted.<br>This does not include<br>current drawn due to the<br>XRES internal pull-up<br>resistor. | _                       | 30                 | -                  | μA      | Power Source = VSYS = 3.3 V, Type-C<br>device not attached,<br>T <sub>A</sub> = 25 °C                                                                                                 |

Note

2. If VDDIO > VDDD, GPIO P2.4 cannot be used. It must be left unconnected. See Table 2 for pin numbers.

### Table 5. AC Specifications (Guaranteed by Characterization)

| Spec ID    | Parameter              | Description                                                  | Min | Тур | Мах | Units | Details/Conditions |

|------------|------------------------|--------------------------------------------------------------|-----|-----|-----|-------|--------------------|

| SID.CLK#4  | F <sub>CPU</sub>       | CPU input frequency                                          | DC  | -   | 48  | MHz   | All VDDD           |

| SID.PWR#20 | T <sub>SLEEP</sub>     | Wakeup from sleep mode                                       | -   | 0   | -   | μs    | -                  |

| SID.PWR#21 | T <sub>DEEPSLEEP</sub> | Wakeup from Deep Sleep mode                                  | -   | -   | 35  | μs    | _                  |

| SID.XRES#5 | T <sub>XRES</sub>      | External reset pulse width                                   | 5   | -   | -   | μs    | All VDDIO          |

| SYS.FES#1  | T_ <sub>PWR_RDY</sub>  | Power-up to "Ready to accept I <sup>2</sup> C/CC<br>command" | -   | 5   | 25  | ms    | _                  |

I/O

### Table 6. I/O DC Specifications

| Spec ID     | Parameter                 | Description                                   | Min          | Тур | Max         | Units | Details/Conditions                                                                             |

|-------------|---------------------------|-----------------------------------------------|--------------|-----|-------------|-------|------------------------------------------------------------------------------------------------|

| SID.GIO#37  | V <sub>IH_CMOS</sub>      | Input voltage HIGH threshold                  | 0.7 × VDDIO  | _   | _           | V     | CMOS input                                                                                     |

| SID.GIO#38  | V <sub>IL_CMOS</sub>      | Input voltage LOW threshold                   | _            | 1   | 0.3 × VDDIO | V     | CMOS input                                                                                     |

| SID.GIO#39  | VIH_VDDIO2.7-             | LVTTL input, VDDIO < 2.7 V                    | 0.7× VDDIO   | 1   | _           | V     | -                                                                                              |

| SID.GIO#40  | VIL_VDDIO2.7-             | LVTTL input, VDDIO < 2.7 V                    | _            | 1   | 0.3 × VDDIO | V     | -                                                                                              |

| SID.GIO#41  | VIH_VDDIO2.7+             | LVTTL input, VDDIO $\ge 2.7$ V                | 2.0          | Ι   | _           | V     | -                                                                                              |

| SID.GIO#42  | V <sub>IL_VDDIO2.7+</sub> | LVTTL input, VDDIO $\ge$ 2.7 V                | _            | I   | 0.8         | V     | -                                                                                              |

| SID.GIO#33  | V <sub>OH_3V</sub>        | Output voltage HIGH level                     | VDDIO –0.6   | I   | _           | V     | I <sub>OH</sub> = 4 mA at 3V VDDIO                                                             |

| SID.GIO#34  | V <sub>OH_1.8V</sub>      | Output voltage HIGH level                     | VDDIO –0.5   | I   | _           | V     | I <sub>OH</sub> = 1 mA at 1.8V VDDIO                                                           |

| SID.GIO#35  | V <sub>OL_1.8V</sub>      | Output voltage LOW level                      | -            | I   | 0.6         | V     | I <sub>OL</sub> = 4 mA at 1.8V VDDIO                                                           |

| SID.GIO#36  | V <sub>OL_3V</sub>        | Output voltage LOW level                      | _            | -   | 0.6         | V     | I <sub>OL</sub> = 4 mA at 3V VDDIO<br>for SBU and AUX pins                                     |

| SID.GIO#5   | R <sub>PU</sub>           | Pull-up resistor value                        | 3.5          | 5.6 | 8.5         | kΩ    | +25 °C T <sub>A</sub> , all VDDIO                                                              |

| SID.GIO#6   | R <sub>PD</sub>           | Pull-down resistor value                      | 3.5          | 5.6 | 8.5         | kΩ    | +25 °C T <sub>A</sub> , all VDDIO                                                              |

| SID.GIO#16  | ILL                       | Input leakage current<br>(absolute value)     | _            | _   | 2           | nA    | +25 °C T <sub>A</sub> , all VDDIO.<br>Guaranteed by<br>characterization.                       |

| SID.GIO#17  | C <sub>PIN</sub>          | Max pin capacitance                           | _            | 3.0 | 7           | pF    | All VDDIO, all packages,<br>all I/Os except SBU and<br>AUX. Guaranteed by<br>characterization. |

| SID.GIO#17A | C <sub>PIN_SBU</sub>      | Max pin capacitance                           | -            | 16  | 18          | pF    | All VDDIO, all packages,<br>SBU pins only. Guaranteed<br>by characterization.                  |

| SID.GIO#17B | C <sub>PIN_AUX</sub>      | Max pin capacitance                           | -            | 12  | 14          | pF    | All VDDIO, all packages,<br>AUX pins only. Guaranteed<br>by characterization.                  |

| SID.GIO#43  | V <sub>HYSTTL</sub>       | Input hysteresis, LVTTL<br>VDDIO > 2.7 V      | 15           | 40  | -           | mV    | Guaranteed by characterization                                                                 |

| SID.GIO#44  | V <sub>HYSCMOS</sub>      | Input hysteresis CMOS                         | 0.05 × VDDIO | -   | -           | mV    | VDDIO < 4.5 V.<br>Guaranteed by character-<br>ization.                                         |

| SID69       | IDIODE                    | Current through protection diode to VDDIO/Vss | _            | -   | 100         | μA    | Guaranteed by character-<br>ization                                                            |

| SID.GIO#45  | I <sub>TOT_GPIO</sub>     | Maximum total sink chip current               | -            | _   | 85          | mA    | Guaranteed by character-<br>ization                                                            |

### Table 17. Fixed SPI Slave Mode AC Specifications

(Guaranteed by Characterization)

| Spec ID | Parameter            | Description                                             | Min | Тур | Мах                       | Units | Details/Conditions                    |

|---------|----------------------|---------------------------------------------------------|-----|-----|---------------------------|-------|---------------------------------------|

| SID170  | T <sub>DMI</sub>     | MOSI Valid before Sclock capturing<br>edge              | 40  | -   | _                         | ns    | -                                     |

| SID171  | T <sub>DSO</sub>     | MISO Valid after Sclock driving edge                    | -   | -   | 42 + 3 × T <sub>CPU</sub> | ns    | T <sub>CPU</sub> = 1/F <sub>CPU</sub> |

| SID171A | T <sub>DSO_EXT</sub> | MISO Valid after Sclock driving edge<br>in Ext Clk mode | -   | -   | 48                        | ns    | -                                     |

| SID172  | T <sub>HSO</sub>     | Previous MISO data hold time                            | 0   | -   | -                         | ns    | -                                     |

| SID172A | T <sub>SSELSCK</sub> | SSEL Valid to first SCK Valid edge                      | 100 | -   | _                         | ns    | _                                     |

### **System Resources**

#### Power-on-Reset (POR) with Brown Out SWD Interface

### Table 18. Imprecise Power On Reset (PRES) (Guaranteed by Characterization)

| Spec ID | Parameter             | Description                              | Min  | Тур | Мах  | Units | Details/Conditions |

|---------|-----------------------|------------------------------------------|------|-----|------|-------|--------------------|

| SID185  | VDIOFIDOD             | Power-on Reset (POR) rising trip voltage | 0.80 | -   | 1.50 | V     | -                  |

| SID186  | V <sub>FALLIPOR</sub> | POR falling trip voltage                 | 0.70 | -   | 1.4  | V     | -                  |

### Table 19. Precise Power On Reset (POR) (Guaranteed by Characterization)

| Spec ID | Parameter              | Description                                                  | Min  | Тур | Max  | Units | Details/Conditions |

|---------|------------------------|--------------------------------------------------------------|------|-----|------|-------|--------------------|

| SID190  | V <sub>FALLPPOR</sub>  | Brown-out Detect (BOD) trip voltage<br>in active/sleep modes | 1.48 | -   | 1.62 | V     | -                  |

| SID192  | V <sub>FALLDPSLP</sub> | BOD trip voltage in Deep Sleep mode                          | 1.1  | -   | 1.5  | V     | _                  |

#### Table 20. SWD Interface Specifications

| Spec ID   | Parameter    | Description                                          | Min      | Тур | Max      | Units | Details/Conditions                    |

|-----------|--------------|------------------------------------------------------|----------|-----|----------|-------|---------------------------------------|

| SID.SWD#1 | F_SWDCLK1    | $3.3 \text{ V} \le \text{VDDIO} \le 5.5 \text{ V}$   | -        | _   | 14       | MHz   | SWDCLK $\leq$ 1/3 CPU clock frequency |

| SID.SWD#2 | F_SWDCLK2    | $1.8 \text{ V} \leq \text{VDDIO} \leq 3.3 \text{ V}$ | _        | _   | 7        | MHz   | SWDCLK $\leq$ 1/3 CPU clock frequency |

| SID.SWD#3 | T_SWDI_SETUP | T = 1/f SWDCLK                                       | 0.25 × T | _   | -        | ns    | Guaranteed by characterization        |

| SID.SWD#4 | T_SWDI_HOLD  | T = 1/f SWDCLK                                       | 0.25 × T | _   | -        | ns    | Guaranteed by characterization        |

| SID.SWD#5 | T_SWDO_VALID | T = 1/f SWDCLK                                       | _        | _   | 0.50 × T | ns    | Guaranteed by characterization        |

| SID.SWD#6 | T_SWDO_HOLD  | T = 1/f SWDCLK                                       | 1        | -   | -        | ns    | Guaranteed by characterization        |

### Table 25. PD DC Specifications (continued)

| Spec ID   | Parameter           | Description                                     | Min  | Тур | Max  | Units | Details/Conditions                                                      |

|-----------|---------------------|-------------------------------------------------|------|-----|------|-------|-------------------------------------------------------------------------|

| SID.PD.8  | R <sub>leak_1</sub> | VCONN leaker for 0.1-µF load                    | -    | -   | 216  | kΩ    |                                                                         |

| SID.PD.9  | R <sub>leak_2</sub> | VCONN leaker for 0.5-µF load                    | -    | -   | 43.2 | kΩ    |                                                                         |

| SID.PD.10 | R <sub>leak_3</sub> | VCONN leaker for 1.0-µF load                    | -    | -   | 21.6 | kΩ    | Managed Active Cable (MAC)                                              |

| SID.PD.11 | R <sub>leak_4</sub> | VCONN leaker for 2.0-µF load                    | -    | -   | 10.8 | kΩ    | discharge.                                                              |

| SID.PD.12 | R <sub>leak_5</sub> | VCONN leaker for 5.0-µF load                    | -    | -   | 4.32 | kΩ    |                                                                         |

| SID.PD.13 | R <sub>leak_6</sub> | VCONN leaker for 10-µF load                     | -    | -   | 2.16 | kΩ    |                                                                         |

| SID.PD.14 | I <sub>leak</sub>   | Leaker on VCONN for discharge upon cable detach | 150  | -   | 550  | μA    | -                                                                       |

| SID.PD.15 | Vgndoffset          | Ground offset tolerated by BMC receiver         | -400 | _   | 400  | mV    | Relative to the remote BMC transmitter. Guaranteed by characterization. |

#### Table 26. CSA Specifications

| Spec ID   | Parameter        | Description                                                               | Min    | Тур | Мах   | Units | <b>Details/Conditions</b>       |

|-----------|------------------|---------------------------------------------------------------------------|--------|-----|-------|-------|---------------------------------|

| SID.CSA.1 | Out_E_Trim_15_DS | Overall Error at Av = 15 using deep sleep reference                       | -7.00  | _   | 7.00  | %     | Guaranteed by characterization. |

| SID.CSA.2 | Out_E_Trim_15_BG | Overall Error at Av = 15 using bandgap reference                          | -4.50  | -   | 4.50  | %     | Guaranteed by characterization. |

| SID.CSA.3 | Out_E_Trim_100   | Overall Error at Av = 100 using either<br>bandgap or deep sleep reference | -24.50 | -   | 24.50 | %     | -                               |

### Table 27. UV/OV Specifications

| Spec ID    | Parameter            | Description                                       | Min | Тур | Мах | Units       | Details/Conditions                                    |

|------------|----------------------|---------------------------------------------------|-----|-----|-----|-------------|-------------------------------------------------------|

| SID.UVOV.1 | V <sub>THUVOV1</sub> | Voltage threshold Accuracy, $V_{BUS} \leq 16 \ V$ | -6  |     | 6   | <b>V</b> /2 | Tested at VBUS = 3.75 V,<br>4.5 V, 5.25 V, 12 V, 16 V |

| SID.UVOV.2 | V <sub>THUVOV2</sub> | Voltage threshold Accuracy, $V_{BUS} > 16 V$      | -10 |     | 10  | %           | Tested at VBUS = 20 V                                 |

### Gate Driver Specifications

### Table 28. Gate Driver DC Specifications

| Spec ID   | Parameter       | Description                            | Min  | Тур | Max  | Units | Details/Conditions                                                                                                                                                                                                                                                                                 |

|-----------|-----------------|----------------------------------------|------|-----|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DC.NGDO.1 | VGS1            | Gate to Source<br>Overdrive            | 5    | -   | 16.5 | V     | <ol> <li>Gate driver Supply Voltage ≥ 5V, where<br/>Gate driver supply voltage = VBUS _P for<br/>VBUS_P_CTRL_outputs, and VBUS_C<br/>for VBUS_C_CTRL_outputs.</li> <li>Gate driver current = 0</li> <li>Gate driver configuration = NFET</li> <li>Gate driver pump clock divider = 1</li> </ol>    |

| DC.NGDO.2 | VGS2            | Gate to Source<br>Overdrive            | 3.75 | _   | 16.5 | V     | <ol> <li>Gate driver Supply Voltage ≥ 3.75V, where<br/>Gate driver supply voltage = VBUS _P for<br/>VBUS_P_CTRL_outputs, and VBUS_C<br/>for VBUS_C_CTRL_outputs.</li> <li>Gate driver current = 0</li> <li>Gate driver configuration = NFET</li> <li>Gate driver pump clock divider = 1</li> </ol> |

| DC.NGDO.6 | R <sub>PD</sub> | Resistance when "pull<br>down" enabled | _    | -   | 5    | kΩ    | -                                                                                                                                                                                                                                                                                                  |

### Table 29. Gate Driver AC Specifications

| Spec ID   | Parameter       | Description                                                                                                            |   | Тур | Мах | Units | Details/Conditions                                                                                       |

|-----------|-----------------|------------------------------------------------------------------------------------------------------------------------|---|-----|-----|-------|----------------------------------------------------------------------------------------------------------|

| AC.NGDO.1 | T <sub>ON</sub> | Gate turn-on time to gate_driver_supply_voltage + 5V for supply voltage $\geq$ 5V and VBUS * 2 for supply voltage < 5V | Ι | _   | 1   | ms    | <ol> <li>Gate driver configuration =<br/>NFET</li> <li>Load = The gate of a SI9936<br/>MOSFET</li> </ol> |

SBU

### Table 30. Analog Crossbar Switch Specifications

| Spec ID   | Parameter | Description                         | Min  | Тур | Max  | Units | Details/Conditions              |

|-----------|-----------|-------------------------------------|------|-----|------|-------|---------------------------------|

| SID.SBU.1 | Ron_sw    | Switch ON Resistance                | -    | -   | 10   | Ω     | Voltage input from 0 V to 3.6 V |

| SID.SBU.2 | Rpu_aux_1 | AUX_P/N Pull-up Resistance – 100k   | 80   | _   | 120  | kΩ    | -                               |

| SID.SBU.3 | Rpu_aux_2 | AUX_P/N Pull-up Resistance – 1M     | 0.8  | _   | 1.2  | MΩ    | -                               |

| SID.SBU.4 | Rpd_aux_1 | AUX_P/N Pull-down Resistance – 100k | 80   | _   | 120  | kΩ    | -                               |

| SID.SBU.5 | Rpd_aux_2 | AUX_P/N Pull-down Resistance – 1M   | 0.8  | _   | 1.2  | MΩ    | -                               |

| SID.SBU.6 | Rpd_aux_3 | AUX_P/N Pull-down Resistance – 470k | 329  | _   | 611  | kΩ    | -                               |

| SID.SBU.7 | Rpd_aux_4 | AUX_P/N Pull-down Resistance – 4.7M | 3.29 | -   | 6.11 | MΩ    | -                               |

Charger Detect

### Table 31. Charger Detect Specifications

| Spec ID   | Parameter | Description                                    | Min   | Тур | Max   | Units | Details/Conditions                                            |

|-----------|-----------|------------------------------------------------|-------|-----|-------|-------|---------------------------------------------------------------|

| SID.CD.1  | VDAT_REF  | BC1.2 Data Detect Voltage Threshold            | 250   | -   | 400   | mV    | -                                                             |

| SID.CD.2  | VDM_SRC   | BC1.2 DM Voltage Source                        | 500   | -   | 700   | mV    | With current sink of<br>25 μΑ–175 μΑ                          |

| SID.CD.3  | VDP_SRC   | BC1.2 DP Voltage Source                        | 500   | -   | 700   | mV    | With current sink of<br>25 μΑ–175 μΑ                          |

| SID.CD.4  | IDM_SINK  | BC1.2 DM Current Sink                          | 25    | -   | 175   | μA    | -                                                             |

| SID.CD.5  | IDP_SINK  | BC1.2 DP Current Sink                          | 25    | -   | 175   | μA    | -                                                             |

| SID.CD.6  | IDP_SRC   | BC1.2 DP DCD Current Source                    | 7     | -   | 13    | μA    | -                                                             |

| SID.CD.7  | RDP_UP    | USB FS DP Pull-up Termination                  | 0.9   | -   | 1.575 | kΩ    | -                                                             |

| SID.CD.8  | RDM_UP    | USB FS DM Pull-up Termination                  | 0.9   | -   | 1.575 | kΩ    | -                                                             |

| SID.CD.9  | RDP_DWN   | USB FS DP Pull-down Termination                | 14.25 | -   | 24.8  | kΩ    | -                                                             |

| SID.CD.10 | RDM_DWN   | USB FS DM Pull-down Termination                | 14.25 | -   | 24.8  | kΩ    | -                                                             |

| SID.CD.11 | RDAT_LKG  | DP/DM Data Line Leakage Termination            | 300   | -   | 500   | kΩ    | The charger detect function and data line leakage is enabled. |

| SID.CD.12 | RDCP_DAT  | BC1.2 DCP Port Resistance between<br>DP and DM | -     | -   | 40    | Ω     | _                                                             |

| SID.CD.13 | VSETH     | USB FS Logic Threshold                         | 1.26  | -   | 1.54  | V     | -                                                             |

#### Memory

### Table 37. Flash AC Specifications

| Spec ID   | Parameter     | Description                                                  | Min | Тур | Max  | Units | Details/Conditions             |

|-----------|---------------|--------------------------------------------------------------|-----|-----|------|-------|--------------------------------|

| SID.MEM#3 | FLASH_ERASE   | Row erase time                                               | -   | Ι   | 15.5 | ms    | _                              |

| SID.MEM#4 | FLASH_WRITE   | Row (Block) write time (erase and program)                   | -   | -   | 20   | ms    | _                              |

| SID.MEM#8 | FLASH_ROW_PGM | Row program time after erase                                 | -   | -   | 7    | ms    | _                              |

| SID178    | TBULKERASE    | Bulk erase time (64k Bytes)                                  | _   | _   | 35   | ms    | _                              |

| SID180    | TDEVPROG      | Total device program time                                    | _   | -   | 7.5  | S     | Guaranteed by characterization |

| SID182    | FRET1         | Flash retention, T <sub>A</sub> ≤ 55 °C,<br>100 K P/E cycles | 20  | -   | -    | years | Guaranteed by characterization |

| SID182A   | FRET2         | Flash retention, T <sub>A</sub> ≤ 85 °C,<br>10 K P/E cycles  | 10  | -   | -    | years | Guaranteed by characterization |

| SID182B   | FRET3         | Flash retention, T <sub>A</sub> ≤ 105 °C,<br>10 K P/E cycles | 3   | -   | -    | years | Guaranteed by characterization |

# **Document History Page**

| Revision | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                   |

|----------|---------|--------------------|--------------------|-------------------------------------------------------------------------|

| **       | 4905678 | VGT                | 09/11/2015         | New data sheet.                                                         |

|          |         |                    |                    | Updated General Description:                                            |

|          |         |                    |                    | Updated the number of GPIOs to 20.                                      |

|          |         |                    |                    | Updated Functional Overview:                                            |

|          |         |                    |                    | Updated GPIO:                                                           |

| *A       | 4953333 | VGT                | 10/08/2015         | Updated the number of GPIOs to 20.                                      |

|          |         |                    |                    | Updated Pinouts:                                                        |

|          |         |                    |                    | Updated Table 2.                                                        |

|          |         |                    |                    | Updated Figure 4.                                                       |

|          |         |                    |                    | Added Figure 6.                                                         |

|          |         |                    |                    | Changed status from Advance to Preliminary.                             |

|          |         |                    |                    | Updated Features.                                                       |

|          |         |                    |                    | Added EZ-PD CCG3 Block Diagram.                                         |

|          |         |                    |                    | Updated Functional Overview:                                            |

|          |         |                    |                    | Updated USB-PD Subsystem (USBPD SS) (Updated description).              |

|          |         |                    |                    | Added Full-Speed USB Subsystem.                                         |

|          |         |                    |                    | Updated Pinouts:                                                        |

|          |         |                    |                    | Updated Table 2.                                                        |

|          |         |                    |                    | Updated Figure 4.                                                       |

|          |         |                    |                    | Updated Figure 6.                                                       |

|          |         |                    |                    | Added Applications.                                                     |

|          |         |                    |                    | Updated Electrical Specifications:<br>Updated Absolute Maximum Ratings: |

|          |         |                    |                    | Updated Table 3.                                                        |

|          |         |                    |                    | Updated Device-Level Specifications:                                    |

|          |         |                    |                    | Updated Table 4.                                                        |

| *B       | 5007726 | VGT                | 11/25/2015         | Updated Table 5.                                                        |

|          | 0007720 |                    | 11/20/2010         | Updated I/O:                                                            |

|          |         |                    |                    | Updated Table 6.                                                        |

|          |         |                    |                    | Updated XRES:                                                           |

|          |         |                    |                    | Updated Table 8.                                                        |

|          |         |                    |                    | Updated System Resources:                                               |

|          |         |                    |                    | Updated Power-on-Reset (POR) with Brown Out SWD Interface:              |

|          |         |                    |                    | Updated Table 18.                                                       |

|          |         |                    |                    | Updated Table 19.                                                       |

|          |         |                    |                    | Updated Table 20.                                                       |

|          |         |                    |                    | Updated Internal Main Oscillator:                                       |

|          |         |                    |                    | Updated Table 22.                                                       |

|          |         |                    |                    | Updated Internal Low-Speed OscillatorPower Down:                        |

|          |         |                    |                    | Updated Table 23.                                                       |

|          |         |                    |                    | Updated Table 24.                                                       |

|          |         |                    |                    | Updated Internal Low-Speed OscillatorPower Down:                        |

|          |         |                    |                    | Updated Table 25.                                                       |

# Document History Page (continued)

| Document   | Number: 00 | 02-03288           | SB Type-C Po       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------|------------|--------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision   | ECN        | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| *B (cont.) | 5007726    | VGT                | 11/25/2015         | Updated Analog to Digital Converter:<br>Updated Table 32.<br>Updated Table 33.<br>Updated Packaging:<br>Added Figure 18 (spec 002-04062 *A).                                                                                                                                                                                                                                                                                                                                                                                |

| *C         | 5080470    | VGT                | 01/11/2016         | Updated General Description.<br>Updated Features.<br>Updated Logic Block Diagram.<br>Updated Power Systems Overview.<br>Updated Pinouts:<br>Updated Table 2.<br>Added table "CCG3 Pin Description for 16-SOIC Device".<br>Added figure "Pinout of 16-SOIC Package (Top View)".<br>Updated Applications:<br>Updated Applications:<br>Updated Figure 11.<br>Updated Figure 11.<br>Updated Figure 15.<br>Updated Figure 15.<br>Updated Ordering Information.<br>Updated Packaging:<br>Added spec 51-85022 *E.<br>Added Errata. |

| *D         | 5137796    | VGT                | 03/09/2016         | Updated Pinouts:<br>Updated table "CCG3 Pin Description for 16-SOIC Device".<br>Updated figure "Pinout of 16-SOIC Package (Top View)".<br>Updated Applications:<br>Updated Figure 11.<br>Updated Figure 12.<br>Updated Ordering Information<br>Updated Errata.<br>Updated to new template.                                                                                                                                                                                                                                  |

| *E         | 5240836    | VGT                | 04/28/2016         | Updated General Description:<br>Updated description.<br>Updated Features:<br>Updated Type-C and USB-PD Support:<br>Updated description.<br>Updated Packages:<br>Updated description.<br>Updated Logic Block Diagram.<br>Updated Logic Block Diagram.<br>Updated Functional Overview:<br>Updated Integrated Billboard Device:<br>Updated description.<br>Updated USB-PD Subsystem (USBPD SS):<br>Updated description.<br>Added Figure 2 and Figure 5.                                                                        |

# Document History Page (continued)

| Revision               | ECN            | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------|----------------|--------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision<br>*E (cont.) | ECN<br>5240836 |                    |                    | Description of Change           Updated Power Systems Overview: Updated description.           Updated Figure 3.           Updated Pinouts:           Updated Table 2:           Updated details in "Description" column corresponding to VDDIO pin.           Removed table "CCG3 Pin Description for 16-SOIC Device".           Removed figure "Pinout of 16-SOIC Package (Top View)".           Updated Applications: Removed figure "Power Adapter Application Diagram (16-SOIC Device)".           Added Figure 12.           Updated Table 4.           Updated details in "Details/Conditions" column corresponding to "SID.PWR#1_A" Spec ID and "V <sub>SYS</sub> " parameter.           Replaced "V <sub>DDD</sub> " with "5.5" in "Max" column corresponding to "SID.PWR#13"           Spec ID and "V <sub>DDIO</sub> " parameter.           Added "SID.PWR#1_C" and "SID.PWR#1_D" Spec IDs corresponding to "V <sub>SYS</sub> " parameter and its details.           Added "SID.PWR#1_C" and "SID.PWR#1_D" Spec IDs corresponding to "V <sub>SYS</sub> " parameter.           Updated details in "Description" and "Details/Conditions" column corresponding to "SID.PwR#28" Spec ID and "V <sub>BUS</sub> " parameter.           Updated details in "Description" and "Details/Conditions" column corresponding to "SID.9wR#28" Spec ID and "U <sub>D_D_XR</sub> " parameter.           Updated details in "Description" and "Details/Conditions" column corresponding to "SID.9wR#28" Spec ID and "U <sub>D_XR</sub> " parameter.           Updated details in "Description" and "Details/Conditions" columns corresponding to "SID.9wR#28" Spec ID and "U <sub>D_XR</sub> " pa |

|                        |                |                    |                    | Updated Ordering Code Definitions<br>Updated Packaging: Removed spec 51-85022 *E.<br>Removed Errata.<br>Added Available Firmware and Software Tools, CCG3 Programming and<br>Bootloading, and References and Links to Applications Collaterals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| *F                     | 5342389        | VGT                | 07/28/2016         | Added descriptive notes for the application diagrams.<br>Updated Features, Applications and Timer/Counter/PWM Block (TCPWM).<br>Updated Table 2 through Table 6, Table 18, Table 19, Table 22, Table 23,<br>Table 25, and Table 31 through Table 38.<br>Updated Figure 7, Figure 8, Figure , Figure 11, and Figure 19 (package<br>diagram spec 001-42168 *E).<br>Added Figure 5, Figure 13, and Figure 14.<br>Added Table 26, Table 27, Table 37, and Table 39 through Table 41.<br>Added VDM in Acronyms.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| *G                     | 5449433        | VGT                | 09/26/2016         | Updated Cypress logo and copyright information.<br>Added Table 34 through Table 36.<br>Updated Table 3, Table 4, Table 6, and Table 37.<br>Updated Copyright and Disclaimer.<br>Added Compliance information in Sales, Solutions, and Legal Information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

# Document History Page (continued)