Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Not For New Designs                                                              |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | RX                                                                               |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 100MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                                               |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                          |

| Number of I/O              | 61                                                                               |

| Program Memory Size        | 256КВ (256К х 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | ·                                                                                |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                        |

| Data Converters            | A/D 12x10b, 8x12b                                                                |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

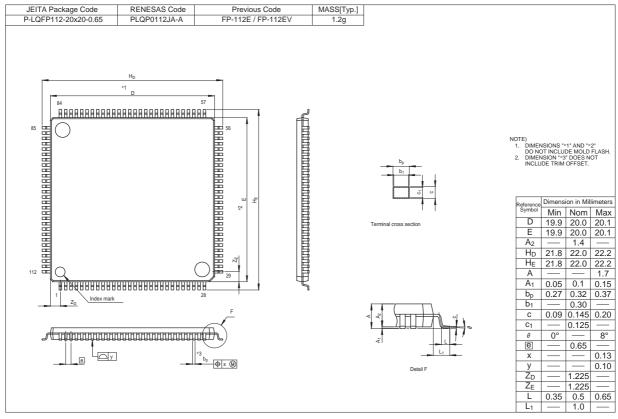

| Package / Case             | 112-LQFP                                                                         |

| Supplier Device Package    | 112-LQFP (20x20)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f562gaddfh-v1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 1.1 | Outline of Specifications (3 / 5) |

|-----------|-----------------------------------|

|-----------|-----------------------------------|

| Classification | Module/Function                              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|----------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Timers         | General PWM timer<br>(GPT/GPTa)              | <ul> <li>16 bits x 4 channels</li> <li>Counting up or down (saw-wave), counting up and down (triangle-wave) selectable for all channels</li> <li>Clock sources independently selectable for all channels</li> <li>2 input/output pins per channel</li> <li>2 output compare/input capture registers per channel</li> <li>For the 2 output compare/input capture registers of each channel, 4 registers are provided as buffer registers and are capable of operating as comparison registers wher buffering is not in use.</li> <li>In output compare operation, buffer switching can be at peaks or troughs, enabling the generation of laterally asymmetrically PWM waveforms.</li> <li>Registers for setting up frame intervals on each channel (with capability for generating interrupts on overflow or underflow)</li> <li>Synchronizable operation of the several counters</li> <li>Modes of synchronized operation (synchronized, or displaced by desired times for phase shifting)</li> <li>Generation of dead times in PWM operation</li> <li>Through combination of three counters, generation of automatic three-phase PWM waveforms incorporating dead times</li> <li>Starting, clearing, and stopping counters in response to external or internal triggers</li> <li>Internal trigger sources: output of the internal comparator detection, software, and compare-match</li> <li>The frequency-divided system clock (ICLK) can be used as a counter clock for measuring timing of the edges of signals produced by frequency-dividing the low-speed on-chip oscillator clock signal dedicated to IWDT (to detect abnormal oscillation).</li> <li>PWM delay generation can control the timing with which signals on the two PWM outpur pins for each channel rise and fall with an accuracy of up to 1/32 times the period of the system clock (ICLK) (only for GPTa).</li> </ul> |  |  |  |  |  |  |

|                | Compare match timer (CMT)                    | <ul> <li>(16 bits x 2 channels) x 2 units</li> <li>Select from among four internal clock signals (PCLK/8, PCLK/32, PCLK/128, PCLK/512</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|                | Watchdog timer<br>(WDT)                      | <ul> <li>8 bits x 1 channel</li> <li>Select from among eight counter-input clock signals (PCLK/4, PCLK/64, PCLK/128, PCLK/512, PCLK/2048, PCLK/8192, PCLK/32768, PCLK/131072)</li> <li>Switchable between watchdog timer mode and interval timer mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|                | Independent<br>watchdog<br>timer (IWDT)      | <ul> <li>14 bits x 1 channel</li> <li>Counter-input clock: low-speed on-chip oscillator dedicated to IWDT</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| Communications | Serial<br>communications<br>interface (SCIb) | <ul> <li>3 channels</li> <li>Serial communications modes:<br/>Asynchronous, clock synchronous, and smart-card interface</li> <li>Multiprocessor communications</li> <li>On-chip baud rate generator allows selection of the desired bit rate</li> <li>Choice of LSB-first or MSB-first transfer</li> <li>Noise cancellation (only available in asynchronous mode)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|                | I <sup>2</sup> C bus interface<br>(RIIC)     | <ul> <li>1 channel</li> <li>Communications formats<br/>I<sup>2</sup>C bus format/SMBus format<br/>Master/slave selectable</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

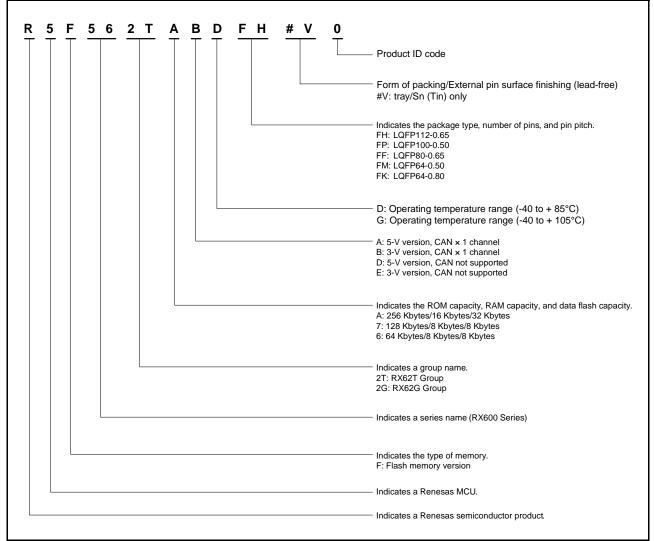

Figure 1.1 How to Read the Product Part No.

Page 11 of 134

### Table 1.4 List of Pins and Pin Functions (112-Pin LQFP) (3 / 3)

| Pin No.<br>(112-Pin | Power Supply<br>Clock |          | Angle -          | Time     | Communi- | <b>I</b>  | 005 | Debury    |

|---------------------|-----------------------|----------|------------------|----------|----------|-----------|-----|-----------|

| LQFP)               | System Control        | I/O Port | Analog           | Timer    | cation   | Interrupt | POE | Debugging |

| 80                  | AVCC                  |          |                  |          |          |           |     |           |

| 81                  | VREF                  |          |                  |          |          |           |     |           |

| 82                  | AVSS                  |          |                  |          |          |           |     |           |

| 83                  |                       | P63      | AN3              |          |          |           |     |           |

| 84                  |                       | P62      | AN2              |          |          |           |     |           |

| 85                  |                       | P61      | AN1              |          |          |           |     |           |

| 86                  |                       | P60      | AN0              |          |          |           |     |           |

| 87                  |                       | P55      | AN11             |          |          |           |     |           |

| 88                  |                       | P54      | AN10             |          |          |           |     |           |

| 89                  |                       | P53      | AN9              |          |          |           |     |           |

| 90                  |                       | P52      | AN8              |          |          |           |     |           |

| 91                  |                       | P51      | AN7              |          |          |           |     |           |

| 92                  |                       | P50      | AN6              |          |          |           |     |           |

| 93                  |                       | P47      | AN103/<br>CVREFH |          |          |           |     |           |

| 94                  |                       | P46      | AN102            |          |          |           |     |           |

| 95                  |                       | P45      | AN101            |          |          |           |     |           |

| 96                  |                       | P44      | AN100            |          |          |           |     |           |

| 97                  |                       | P43      | AN003/<br>CVREFL |          |          |           |     |           |

| 98                  |                       | P42      | AN002            |          |          |           |     |           |

| 99                  |                       | P41      | AN001            |          |          |           |     |           |

| 100                 |                       | P40      | AN000            |          |          |           |     |           |

| 101                 | AVCC0                 |          |                  |          |          |           |     |           |

| 102                 | VREFH0                |          |                  |          |          |           |     |           |

| 103                 | VREFL0                |          |                  |          |          |           |     |           |

| 104                 | AVSS0                 |          |                  |          |          |           |     |           |

| 105                 |                       | P82      |                  | MTIC5U   | SCK2-B   |           |     |           |

| 106                 |                       | P81      |                  | MTIC5V   | TXD2-B   |           |     |           |

| 107                 |                       | P80      |                  | MTIC5W   | RXD2-B   |           |     |           |

| 108                 |                       |          |                  | WDTOVF#  |          |           |     |           |

| 109                 |                       | P11      |                  | MTCLKC-B |          | IRQ1-A    |     |           |

| 110                 |                       | P10      |                  | MTCLKD-B |          | IRQ0-A    |     |           |

| 111                 |                       |          |                  |          |          |           |     | TRST#     |

| 112                 |                       |          |                  |          |          |           |     | TMS       |

|                             | LIST OF FILLS a                         | ina Fin Fu |           | -III LQFF) (3 | / 3)               |           |     |           |

|-----------------------------|-----------------------------------------|------------|-----------|---------------|--------------------|-----------|-----|-----------|

| Pin No.<br>(80-Pin<br>LQFP) | Power Supply<br>Clock<br>System Control | I/O Port   | Analog    | Timer         | Communi-<br>cation | Interrupt | POE | Debugging |

| 76                          | AVSS0                                   |            |           |               |                    |           |     |           |

| 77                          |                                         | P11        |           | MTCLKC-B      |                    | IRQ1-A    |     |           |

| 78                          |                                         | P10        |           | MTCLKD-B      |                    | IRQ0-A    |     |           |

| 79                          |                                         | PA5        | ADTRG1#-A | MTIOC1A       | MISO-B             |           |     |           |

| 80                          |                                         | PA4        | ADTRG0#-A | MTIOC1B       | RSPCK-B            |           |     |           |

## Table 1.6 List of Pins and Pin Functions (80-Pin LQFP) (3 / 3)

## Table 1.7 List of Pins and Pin Functions (80-Pin LQFP: R5F562TxGDFF) (3 / 3)

| Pin No.<br>(80-Pin<br>LQFP) | Power Supply<br>Clock<br>System Control | I/O Port | Analog | Timer    | Communication | Interrupt | POE | Debugging |

|-----------------------------|-----------------------------------------|----------|--------|----------|---------------|-----------|-----|-----------|

| 76                          | AVSS0                                   |          |        |          |               |           |     |           |

| 77                          |                                         | P82      |        | MTIC5U   | SCK2-B        |           |     |           |

| 78                          |                                         | P81      |        | MTIC5V   | TXD2-B        |           |     |           |

| 79                          |                                         | P80      |        | MTIC5W   | RXD2-B        |           |     |           |

| 80                          |                                         | P10      |        | MTCLKD-B |               | IRQ0-A    |     |           |

# 4. I/O Registers

This section gives information on the on-chip I/O register addresses and bit configurations. The information is given as shown below. Notes on writing to registers are also given at the end.

## (1) I/O register addresses (address order)

- Registers are listed from the lower allocation addresses.

- Registers are classified according to functional modules (abbreviations).

- The number of access cycles indicates the number of states based on the specified reference clock.

- Among the I/O register area, addresses not listed in the list of registers are reserved. Reserved addresses must not be accessed. Do not access these addresses; otherwise, the operation when accessing these bits and subsequent operations cannot be guaranteed.

- A unit of access is specified for each register. Access other than in the specified unit is prohibited.

## (2) I/O register bits

- Bit configurations of the registers are listed in the same order as the register addresses.

- Reserved bits are indicated by "—" in the bit name column.

- Space in the bit name field indicates that the entire register is allocated to either the counter or data.

- For the registers of 16 or 32 bits, the MSB is listed first.

## (3) Notes on writing to I/O registers

When writing to an I/O register, the CPU starts executing the subsequent instruction before completing I/O register write. This may cause the subsequent instruction to be executed before the post-update I/O register value is reflected on the operation.

As described in the following examples, special care is required for the cases in which the subsequent instruction must be executed after the post-update I/O register value is actually reflected.

[Examples of cases requiring special care]

- The subsequent instruction must be executed while an interrupt request is disabled with the IENj bit in IERm of the ICU (interrupt request enable bit)\*1 cleared to 0.

- A WAIT instruction is executed immediately after the preprocessing for causing a transition to the low power consumption state.

- Note 1. See section 11.2.2, Interrupt Request Enable Register m (IERm) (m = 02h to 1Fh) in the User's manual: Hardware.

In the above cases, after writing to an I/O register, wait until the write operation is completed using the following procedure and then execute the subsequent instruction.

### Table 4.1 List of I/O Registers (Address Order) (5 / 25)

| Address    | Module<br>Abbreviation | Register Name                      | Register<br>Abbreviation | Number<br>of Bits | Access<br>Size | Number o<br>Access<br>Cycles |

|------------|------------------------|------------------------------------|--------------------------|-------------------|----------------|------------------------------|

| 0008 7172h | ICU                    | DTC activation enable register 114 | DTCER114                 | 8                 | 8              | 2 ICLK                       |

| 0008 7173h | ICU                    | DTC activation enable register 115 | DTCER115                 | 8                 | 8              | 2 ICLK                       |

| 0008 7174h | ICU                    | DTC activation enable register 116 | DTCER116                 | 8                 | 8              | 2 ICLK                       |

| 0008 7175h | ICU                    | DTC activation enable register 117 | DTCER117                 | 8                 | 8              | 2 ICLK                       |

| 0008 7179h | ICU                    | DTC activation enable register 121 | DTCER121                 | 8                 | 8              | 2 ICLK                       |

| 0008 717Ah | ICU                    | DTC activation enable register 122 | DTCER122                 | 8                 | 8              | 2 ICLK                       |

| 0008 717Dh | ICU                    | DTC activation enable register 125 | DTCER125                 | 8                 | 8              | 2 ICLK                       |

| 0008 717Eh | ICU                    | DTC activation enable register 126 | DTCER126                 | 8                 | 8              | 2 ICLK                       |

| 0008 7181h | ICU                    | DTC activation enable register 129 | DTCER129                 | 8                 | 8              | 2 ICLK                       |

| 0008 7182h | ICU                    | DTC activation enable register 130 | DTCER130                 | 8                 | 8              | 2 ICLK                       |

| 0008 7183h | ICU                    | DTC activation enable register 131 | DTCER131                 | 8                 | 8              | 2 ICLK                       |

| 0008 7184h | ICU                    | DTC activation enable register 132 | DTCER132                 | 8                 | 8              | 2 ICLK                       |

| 0008 7186h | ICU                    | DTC activation enable register 134 | DTCER134                 | 8                 | 8              | 2 ICLK                       |

| 0008 7187h | ICU                    | DTC activation enable register 135 | DTCER135                 | 8                 | 8              | 2 ICLK                       |

| 0008 7188h | ICU                    | DTC activation enable register 136 | DTCER136                 | 8                 | 8              | 2 ICLK                       |

| 0008 7189h | ICU                    | DTC activation enable register 137 | DTCER137                 | 8                 | 8              | 2 ICLK                       |

| 0008 718Ah | ICU                    | DTC activation enable register 138 | DTCER138                 | 8                 | 8              | 2 ICLK                       |

| 0008 718Bh | ICU                    | DTC activation enable register 139 | DTCER139                 | 8                 | 8              | 2 ICLK                       |

| 0008 718Ch | ICU                    | DTC activation enable register 140 | DTCER140                 | 8                 | 8              | 2 ICLK                       |

| 0008 718Dh | ICU                    | DTC activation enable register 141 | DTCER141                 | 8                 | 8              | 2 ICLK                       |

| 0008 718Eh | ICU                    | DTC activation enable register 142 | DTCER142                 | 8                 | 8              | 2 ICLK                       |

| 0008 718Fh | ICU                    | DTC activation enable register 143 | DTCER143                 | 8                 | 8              | 2 ICLK                       |

| 0008 7190h | ICU                    | DTC activation enable register 144 | DTCER144                 | 8                 | 8              | 2 ICLK                       |

| 0008 7191h | ICU                    | DTC activation enable register 145 | DTCER145                 | 8                 | 8              | 2 ICLK                       |

| 0008 7195h | ICU                    | DTC activation enable register 149 | DTCER149                 | 8                 | 8              | 2 ICLK                       |

| 0008 7196h | ICU                    | DTC activation enable register 150 | DTCER150                 | 8                 | 8              | 2 ICLK                       |

| 0008 7197h | ICU                    | DTC activation enable register 151 | DTCER151                 | 8                 | 8              | 2 ICLK                       |

| 0008 7198h | ICU                    | DTC activation enable register 152 | DTCER152                 | 8                 | 8              | 2 ICLK                       |

| 0008 7199h | ICU                    | DTC activation enable register 153 | DTCER153                 | 8                 | 8              | 2 ICLK                       |

| 0008 71AEh | ICU                    | DTC activation enable register 174 | DTCER174                 | 8                 | 8              | 2 ICLK                       |

| 0008 71AFh | ICU                    | DTC activation enable register 175 | DTCER175                 | 8                 | 8              | 2 ICLK                       |

| 0008 71B0h | ICU                    | DTC activation enable register 176 | DTCER176                 | 8                 | 8              | 2 ICLK                       |

| 0008 71B1h | ICU                    | DTC activation enable register 177 | DTCER177                 | 8                 | 8              | 2 ICLK                       |

| 0008 71B2h | ICU                    | DTC activation enable register 178 | DTCER178                 | 8                 | 8              | 2 ICLK                       |

| 0008 71B3h | ICU                    | DTC activation enable register 179 | DTCER179                 | 8                 | 8              | 2 ICLK                       |

| 0008 71B4h | ICU                    | DTC activation enable register 180 | DTCER180                 | 8                 | 8              | 2 ICLK                       |

| 0008 71B5h | ICU                    | DTC activation enable register 181 | DTCER181                 | 8                 | 8              | 2 ICLK                       |

| 0008 71B6h | ICU                    | DTC activation enable register 182 | DTCER182                 | 8                 | 8              | 2 ICLK                       |

| 0008 71B7h | ICU                    | DTC activation enable register 183 | DTCER183                 | 8                 | 8              | 2 ICLK                       |

| 0008 71B8h | ICU                    | DTC activation enable register 184 | DTCER184                 | 8                 | 8              | 2 ICLK                       |

| 0008 71BAh | ICU                    | DTC activation enable register 186 | DTCER186                 | 8                 | 8              | 2 ICLK                       |

| 0008 71BBh | ICU                    | DTC activation enable register 187 | DTCER187                 | 8                 | 8              | 2 ICLK                       |

| 0008 71BCh | ICU                    | DTC activation enable register 188 | DTCER188                 | 8                 | 8              | 2 ICLK                       |

| 0008 71BDh | ICU                    | DTC activation enable register 189 | DTCER189                 | 8                 | 8              | 2 ICLK                       |

### Table 4.1 List of I/O Registers (Address Order) (15 / 25)

| Address                        | Module<br>Abbreviation | Register Name                          | Register<br>Abbreviation | Number<br>of Bits | Access<br>Size | Number of<br>Access<br>Cycles |

|--------------------------------|------------------------|----------------------------------------|--------------------------|-------------------|----------------|-------------------------------|

| 0009 041Ch                     | CAN0*2                 | Mask register 7                        | MKR7                     | 32                | 8, 16, 32      | 2, 3 PCLK*                    |

| 0009 0420h                     | CAN0*2                 | FIFO received ID compare register 0    | FIDCR0                   | 32                | 8, 16, 32      | 2, 3 PCLK*                    |

| 0009 0424h                     | CAN0 <sup>*2</sup>     | FIFO received ID compare register 1    | FIDCR1                   | 32                | 8, 16, 32      | 2, 3 PCLK*                    |

| 0009 0428h                     | CAN0*2                 | Mask invalid register                  | MKIVLR                   | 32                | 8, 16, 32      | 2, 3 PCLK*                    |

| 0009 042Ch                     | CAN0 <sup>*2</sup>     | Mailbox interrupt enable register      | MIER                     | 32                | 8, 16, 32      | 2, 3 PCLK*                    |

| 0009 0820h<br>to<br>0009 083Fh | CAN0*2                 | Message control registers 0 to 31      | MCTL0<br>to<br>MCTL31    | 8                 | 8              | 2, 3 PCLK*                    |

| 0009 0840h                     | CAN0*2                 | Control register                       | CTLR                     | 16                | 8, 16          | 2, 3 PCLK*                    |

| 0009 0842h                     | CAN0 <sup>*2</sup>     | Status register                        | STR                      | 16                | 8, 16          | 2, 3 PCLK*                    |

| 0009 0844h                     | CAN0 <sup>*2</sup>     | Bit configuration register             | BCR                      | 32                | 8, 16, 32      | 2, 3 PCLK*                    |

| 0009 0848h                     | CAN0 <sup>*2</sup>     | Receive FIFO control register          | RFCR                     | 8                 | 8              | 2, 3 PCLK*                    |

| 0009 0849h                     | CAN0 <sup>*2</sup>     | Receive FIFO pointer control register  | RFPCR                    | 8                 | 8              | 2, 3 PCLK*                    |

| 0009 084Ah                     | CAN0 <sup>*2</sup>     | Transmit FIFO control register         | TFCR                     | 8                 | 8              | 2, 3 PCLK*                    |

| 0009 084Bh                     | CAN0*2                 | Transmit FIFO pointer control register | TFPCR                    | 8                 | 8              | 2, 3 PCLK*                    |

| 0009 084Ch                     | CAN0 <sup>*2</sup>     | Error interrupt enable register        | EIER                     | 8                 | 8              | 2, 3 PCLK*                    |

| 0009 084Dh                     | CAN0*2                 | Error interrupt factor judge register  | EIFR                     | 8                 | 8              | 2, 3 PCLK*                    |

| 0009 084Eh                     | CAN0*2                 | Receive error count register           | RECR                     | 8                 | 8              | 2, 3 PCLK*                    |

| 0009 084Fh                     | CAN0*2                 | Transmit error count register          | TECR                     | 8                 | 8              | 2, 3 PCLK*                    |

| 0009 0850h                     | CAN0*2                 | Error code store register              | ECSR                     | 8                 | 8              | 2, 3 PCLK*                    |

| 0009 0851h                     | CAN0*2                 | Channel search support register        | CSSR                     | 8                 | 8              | 2, 3 PCLK*                    |

| 0009 0852h                     | CAN0*2                 | Mailbox search status register         | MSSR                     | 8                 | 8              | 2, 3 PCLK*                    |

| 0009 0853h                     | CAN0*2                 | Mailbox search mode register           | MSMR                     | 8                 | 8              | 2, 3 PCLK*                    |

| 0009 0854h                     | CAN0*2                 | Time stamp register                    | TSR                      | 16                | 8, 16          | 2, 3 PCLK*                    |

| 0009 0856h                     | CAN0*2                 | Acceptance filter support register     | AFSR                     | 16                | 8, 16          | 2, 3 PCLK*                    |

| 0009 0858h                     | CAN0*2                 | Test control register                  | TCR                      | 8                 | 8              | 2, 3 PCLK*                    |

| 0009 4001h                     | LIN0                   | LIN wake-up baud rate select register  | LWBR                     | 8                 | 8              | 2, 3 PCLK*                    |

| 0009 4002h                     | LIN0                   | LIN baud rate prescaler 0 register     | LBRP0                    | 8                 | 8, 16          | 2, 3 PCLK*                    |

| 0009 4003h                     | LIN0                   | LIN baud rate prescaler 1 register     | LBRP1                    | 8                 | 8, 16          | 2, 3 PCLK*                    |

| 0009 4004h                     | LIN0                   | LIN self-test control register         | LSTC                     | 8                 | 8              | 2, 3 PCLK*                    |

| 0009 4008h                     | LIN0                   | Mode register                          | LOMD                     | 8                 | 8, 16, 32      | 2, 3 PCLK*                    |

| 0009 4009h                     | LIN0                   | Break field setting register           | L0BRK                    | 8                 | 8, 16, 32      | 2, 3 PCLK*                    |

| 0009 400Ah                     | LIN0                   | Space setting register                 | LOSPC                    | 8                 | 8, 16, 32      | 2, 3 PCLK*                    |

| 0009 400Bh                     | LIN0                   | Wake-up setting register               | LOWUP                    | 8                 | 8, 16, 32      | 2, 3 PCLK*                    |

| 0009 400Ch                     | LIN0                   | Interrupt enable register              | LOIE                     | 8                 | 8, 16          | 2, 3 PCLK*                    |

| 0009 400Dh                     | LIN0                   | Error detection enable register        | LOEDE                    | 8                 | 8, 16          | 2, 3 PCLK*                    |

| 0009 400Eh                     | LIN0                   | Control register                       | LOC                      | 8                 | 8              | 2, 3 PCLK*                    |

| 0009 4010h                     | LIN0                   | Transmission control register          | LOTC                     | 8                 | 8, 16, 32      | 2, 3 PCLK*                    |

| 0009 4011h                     | LIN0                   | Mode status register                   | LOMST                    | 8                 | 8, 16, 32      | 2, 3 PCLK*                    |

| 0009 4012h                     | LIN0                   | Status register                        | LOST                     | 8                 | 8, 16, 32      | 2, 3 PCLK*                    |

| 0009 4013h                     | LIN0                   | Error status register                  | LOEST                    | 8                 | 8, 16, 32      | 2, 3 PCLK*                    |

| 0009 4014h                     | LIN0                   | Response field set register            | LORFC                    | 8                 | 8, 16          | 2, 3 PCLK*                    |

| 0009 4015h                     | LIN0                   | Buffer register                        | LOIDB                    | 8                 | 8, 16          | 2, 3 PCLK*                    |

| 0009 4016h                     | LIN0                   | Check sum buffer register              | LOCBR                    | 8                 | 8              | 2, 3 PCLK*                    |

| 0009 4018h                     | LIN0                   | Data 1 buffer register                 | L0DB1                    | 8                 | 8, 16, 32      | 2, 3 PCLK*                    |

| Module<br>Abbreviation | Register<br>Abbreviation | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/ |

|------------------------|--------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------|

| AD0                    | ADDRB*1                  |                   | _                 | _                 | _                 | _                 | _                 |                  |                 |

| AD0                    | ADDRC*1                  | _                 | _                 | _                 | _                 | _                 | _                 |                  |                 |

| AD0                    | ADDRD <sup>*1</sup>      |                   | _                 | _                 | _                 | _                 | _                 |                  |                 |

| AD0                    | ADDRE <sup>*1</sup>      |                   | _                 | _                 | _                 | _                 | _                 |                  |                 |

| AD0                    | ADDRF*1                  |                   | _                 | _                 | _                 | _                 | _                 |                  |                 |

| AD0                    | ADDRG*1                  |                   | _                 | _                 | _                 | _                 | _                 |                  |                 |

| AD0                    | ADDRH*1                  |                   | _                 | _                 | _                 | _                 | _                 |                  |                 |

| AD0                    | ADCSR                    |                   | ADIE              | ADST              |                   |                   | Cł                | H[3:0]           |                 |

| AD0                    | ADCR                     | _                 | _                 | _                 | _                 | СК                | S[1:0]            |                  | DE[1:0]         |

| AD0                    | ADSSTR                   |                   |                   |                   |                   |                   |                   |                  | -               |

| AD0                    | ADDIAGR                  | _                 | _                 | _                 | _                 | _                 | _                 | DIA              | AG[1:0]         |

| AD0                    | ADDRI <sup>*1</sup>      |                   | _                 | _                 | _                 | _                 | _                 |                  |                 |

| AD0                    | ADDRJ*1                  |                   | _                 | _                 | _                 | _                 | _                 |                  |                 |

| AD0                    | ADDRK *1                 | _                 | _                 | _                 | _                 | _                 | _                 |                  |                 |

| AD0                    | ADDRL*1                  |                   | _                 | _                 | _                 | _                 | _                 |                  |                 |

| AD0                    | ADSTRGR                  |                   |                   |                   |                   |                   | ADSTRS[4:0]       |                  |                 |

| AD0                    | ADDPR                    | DPSEL             | _                 | _                 | _                 | _                 | _                 | _                | DPPR            |

| SCI0                   | SMR                      | СМ                | CHR               | PE                | PM                | STOP              | MP                | Cł               | (S[1:0]         |

| SCI0                   | BRR                      |                   |                   |                   |                   |                   |                   |                  |                 |

| SCI0                   | SCR                      | TIE               | RIE               | TE                | RE                | MPIE              | TEIE              | Cł               | (E[1:0]         |

| SCI0                   | TDR                      |                   |                   |                   |                   |                   |                   |                  |                 |

| SCI0                   | SSR                      | TDRE              | RDRF              | ORER              | FER               | PER               | TEND              | MPB              | MPB             |

| SCI0                   | RDR                      |                   |                   |                   |                   |                   |                   |                  |                 |

| SCI0                   | SCMR                     | BCP2              | _                 | _                 | _                 | SDIR              | SINV              | _                | SMIF            |

| SCI0                   | SEMR                     | _                 | _                 | NFEN              | ABCS              | _                 | _                 | _                | _               |

| SMCI0                  | SMR                      | GM                | BLK               | PE                | PM                | (BC               | P[1:0])           | Cł               | (S[1:0]         |

| SMCI0                  | BRR                      |                   |                   |                   |                   |                   |                   |                  |                 |

| SMCI0                  | SCR                      | TIE               | RIE               | TE                | RE                | MPIE              | TEIE              | Cł               | (E[1:0]         |

| SMCI0                  | TDR                      |                   |                   |                   |                   |                   |                   |                  |                 |

| SMCI0                  | SSR                      | TDRE              | RDRF              | ORER              | ERS               | PER               | TEND              | MPB              | MPB.            |

| SMCI0                  | RDR                      |                   |                   |                   |                   |                   |                   |                  |                 |

| SMCI0                  | SCMR                     | BCP2              | _                 | _                 | _                 | SDIR              | SINV              | _                | SMIF            |

| SCI1                   | SMR                      | CM                | CHR               | PE                | PM                | STOP              | MP                | Cł               | (S[1:0]         |

| SCI1                   | BRR                      |                   |                   |                   |                   |                   |                   |                  |                 |

| SCI1                   | SCR                      | TIE               | RIE               | TE                | RE                | MPIE              | TEIE              | Cł               | (E[1:0]         |

| SCI1                   | TDR                      |                   |                   |                   |                   |                   |                   |                  |                 |

| SCI1                   | SSR                      | TDRE              | RDRF              | ORER              | FER               | PER               | TEND              | MPB              | MPB             |

| SCI1                   | RDR                      |                   |                   |                   |                   |                   |                   |                  |                 |

| SCI1                   | SCMR                     | BCP2              | _                 | _                 | _                 | SDIR              | SINV              | _                | SMIF            |

### Table 4.2 List of I/O Registers (Bit Order) (10 / 30)

| Module<br>Abbreviation | Register<br>Abbreviation | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|------------------------|--------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| MTU7                   | TADCOBRB                 |                   |                   |                   |                   |                   |                   |                  |                  |

| MTU                    | TSYCR                    | CE0A              | CE0D              | CE0C              | CE0D              | CE1A              | CE1B              | CE2A             | CE2B             |

| MTU                    | TWCRB                    | CCE               | _                 | _                 | _                 | _                 | _                 | SCC              | WRE              |

| MTU                    | TMDR2B                   | _                 |                   |                   |                   |                   |                   | _                | DRS              |

| MTU6                   | TGRE                     |                   |                   |                   |                   |                   |                   |                  | 5.10             |

| MTU7                   | TGRE                     |                   |                   |                   |                   |                   |                   |                  |                  |

| MTU7                   | TGRF                     |                   |                   |                   |                   |                   |                   |                  |                  |

| MTU                    | TSTRB                    | CST7              | CST6              |                   |                   |                   |                   | _                |                  |

| мти                    | TSYRB                    | SYNC7             | SYNC6             |                   | _                 |                   | _                 | _                |                  |

| мто                    | TRWERB                   | _                 | _                 |                   |                   |                   |                   |                  | RWE              |

| MTU5                   | TCNTU                    |                   |                   |                   |                   |                   |                   |                  |                  |

| MTU5                   | TGRU                     |                   |                   |                   |                   |                   |                   |                  |                  |

|                        |                          |                   |                   |                   |                   |                   |                   |                  |                  |

| MTU5                   | TCRU                     | _                 | _                 | _                 | _                 | _                 | _                 | TPS              | C[1:0]           |

| MTU5                   | TIORU                    | _                 | _                 | _                 |                   |                   | IOC[4:0]          |                  |                  |

| MTU5                   | TCNTV                    |                   |                   |                   |                   |                   |                   |                  |                  |

| MTU5                   | TGRV                     |                   |                   |                   |                   |                   |                   |                  |                  |

| MTU5                   | TCRV                     |                   |                   |                   |                   |                   | _                 | TPS              | C[1:0]           |

| MTU5                   | TIORV                    | _                 | _                 | _                 |                   |                   | IOC[4:0]          |                  |                  |

| MTU5                   | TCNTW                    |                   |                   |                   |                   |                   |                   |                  |                  |

| MTU5                   | TGRW                     |                   |                   |                   |                   |                   |                   |                  |                  |

| MTU5                   | TCRW                     |                   |                   |                   |                   |                   |                   | TPS              | C[1:0]           |

| MTU5                   | TIORW                    |                   |                   |                   |                   |                   | IOC[4:0]          |                  | 0[0]             |

| MTU5                   | TSR                      |                   |                   |                   |                   |                   | CMFU5             | CMFV5            | CMFW5            |

| MTU5                   | TIER                     | _                 | _                 | _                 | _                 | _                 | TGIE5U            | TGIE5V           | TGIE5W           |

| MTU5                   | TSTR                     | _                 | _                 | _                 | _                 | _                 | CSTU5             | CSTV5            | CSTW5            |

| MTU5                   | TCNTCMPCLR               | _                 | _                 | _                 | _                 | _                 | CMPCLR5U          | CMPCLR5V         | CMPCLR5V         |

| GPT                    | GTSTR                    | _                 | _                 | _                 | _                 | _                 | _                 |                  | _                |

|                        |                          |                   | _                 |                   | _                 | CST3              | CST2              | CST1             | CST0             |

| GPT                    | GTHSCR                   | CPH               | W3[1:0]           | CPH               | IW2[1:0]          |                   | W1[1:0]           |                  | W0[1:0]          |

|                        |                          |                   | W3[1:0]           | CSH               | W2[1:0]           |                   | W1[1:0]           |                  | W0[1:0]          |

| GPT                    | GTHCCR                   | _                 | _                 | _                 | _                 | CCSW3             | CCSW2             | CCSW1            | CCSW0            |

|                        |                          | ССН               | W3[1:0]           | CCH               | IW2[1:0]          | ССН               | W1[1:0]           | CCH              | W0[1:0]          |

| GPT                    | GTHSSR                   |                   | CSH               | SL3[3:0]          |                   |                   | CSHS              | SL2[3:0]         |                  |

|                        |                          |                   | CSH               | SL1[3:0]          |                   |                   | CSHS              | SL0[3:0]         |                  |

| GPT                    | GTHPSR                   | CSHPL3[3:0]       |                   |                   | CSHPL2[3:0]       |                   |                   |                  |                  |

|                        |                          |                   | CSHPL1[3:0]       |                   |                   | CSHF              | PL0[3:0]          |                  |                  |

| GPT                    | GTWP                     | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

|                        |                          |                   | _                 | _                 | _                 | WP3               | WP2               | WP1              | WP0              |

| GPT                    | GTSYNC                   | _                 | _                 | SYN               | IC3[1:0]          | _                 | _                 | SYN              | C2[1:0]          |

|                        |                          | _                 | _                 | SYN               | IC1[1:0]          | _                 | _                 | SYN              | C0[1:0]          |

| GPT                    | GTETINT                  | _                 | _                 | _                 | _                 | _                 | _                 | ETINF            | ETIPF            |

|                        |                          |                   | _                 | _                 | _                 | _                 | _                 | ETINEN           | ETIPEN           |

### Table 4.2 List of I/O Registers (Bit Order) (22 / 30)

| Module<br>Abbreviation | Register<br>Abbreviation | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/ |  |

|------------------------|--------------------------|-------------------|-----------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------|--|

| GPT1                   | GTADTBRB                 | -                 |                       |                   |                   |                   |                   |                  |                 |  |

| GPT1                   | GTADTDBRB                |                   |                       |                   |                   |                   |                   |                  |                 |  |

| GPT1                   | GTONCR                   | OBE               | OAE                   | _                 | SWN               | _                 | _                 | _                | NFV             |  |

|                        |                          |                   | NF                    | S[3:0]            |                   | NVB               | NVA               | NEB              | NEA             |  |

| GPT1                   | GTDTCR                   | _                 | _                     | _                 | _                 | _                 | _                 | _                | TDFE            |  |

|                        |                          | _                 | _                     | TDBDE             | TDBUE             | _                 | _                 | —                | TDE             |  |

| GPT1                   | GTDVU                    |                   |                       |                   |                   |                   |                   |                  |                 |  |

| GPT1                   | GTDVD                    |                   |                       |                   |                   |                   |                   |                  |                 |  |

| GPT1                   | GTDBU                    |                   |                       |                   |                   |                   |                   |                  |                 |  |

| GPT1                   | GTDBD                    |                   |                       |                   |                   |                   |                   |                  |                 |  |

| GPT1                   | GTSOS                    | _                 | _                     | _                 | _                 | _                 | _                 | _                | _               |  |

|                        |                          |                   | _                     | _                 | _                 | _                 | _                 | SC               | S[1:0]          |  |

| GPT1                   | GTSOTR                   |                   | —                     | —                 | —                 | —                 | —                 | —                | _               |  |

|                        |                          | _                 | _                     | —                 | _                 | —                 | —                 | —                | SOTE            |  |

| GPT2                   | GTIOR                    | OBHLD             | OBDFLT                |                   |                   | GTI               | OB[5:0]           |                  |                 |  |

|                        |                          | OAHLD             | HLD OADFLT GTIOA[5:0] |                   | OA[5:0]           |                   |                   |                  |                 |  |

| GPT2                   | GTINTAD                  | ADTRBDEN          | ADTRBUEN              | ADTRADEN          | ADTRAUEN          | EINT              | _                 | _                |                 |  |

|                        |                          | GTIN              | TPR[1:0]              | GTINTF            | GTINTE            | GTINTD            | GTINTC            | GTINTB           | GTINT           |  |

| GPT2                   | GTCR                     |                   | _                     | CCL               | R[1:0]            |                   |                   | TPCS[1:0]        |                 |  |

|                        |                          | _                 | _                     | _                 | _                 | _                 |                   | MD[2:0]          |                 |  |

| GPT2                   | GTBER                    |                   | ADTDB                 | ADT               | FB[1:0]           | —                 | — ADTDA           |                  | ADTTA[1:0]      |  |

|                        |                          | _                 | CCRSWT                | PR                | [1:0]             | CCI               | RB[1:0]           | CCI              | RA[1:0]         |  |

| GPT2                   | GTUDC                    | _                 | _                     | —                 | _                 | _                 | _                 | _                | _               |  |

|                        |                          | _                 | _                     | _                 | _                 | _                 | _                 | UDF              | UD              |  |

| GPT2                   | GTITC                    | _                 | ADTBL                 | _                 | ADTAL             | _                 |                   | IVTT[2:0]        |                 |  |

|                        |                          |                   | C[1:0]                | ITLF              | ITLE              | ITLD              | ITLC              | ITLB             | ITLA            |  |

| GPT2                   | GTST                     | TUCF              |                       | _                 | _                 | DTEF              |                   | ITCNT[2:0]       |                 |  |

|                        |                          | TCFPU             | TCFPO                 | TCFF              | TCFE              | TCFD              | TCFC              | TCFB             | TCFA            |  |

| GPT2                   | GTCNT                    |                   |                       |                   |                   |                   |                   |                  |                 |  |

|                        |                          |                   |                       |                   |                   |                   |                   |                  |                 |  |

| GPT2                   | GTCCRA                   |                   |                       |                   |                   |                   |                   |                  |                 |  |

| 0.0770                 | 070000                   |                   |                       |                   |                   |                   |                   |                  |                 |  |

| GPT2                   | GTCCRB                   |                   |                       |                   |                   |                   |                   |                  |                 |  |

| GPT2                   | GTCCRC                   |                   |                       |                   |                   |                   |                   |                  |                 |  |

| GPT2                   | GTCCRD                   |                   |                       |                   |                   |                   |                   |                  |                 |  |

| GPT2                   | GTCCRE                   |                   |                       |                   |                   |                   |                   |                  |                 |  |

|                        |                          |                   |                       |                   |                   |                   |                   |                  |                 |  |

| GPT2                   | GTCCRF                   |                   |                       |                   |                   |                   |                   |                  |                 |  |

|                        |                          |                   |                       |                   |                   |                   |                   |                  |                 |  |

### Table 4.2 List of I/O Registers (Bit Order) (26 / 30)

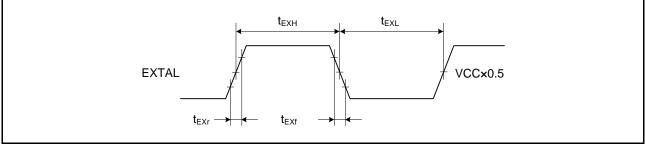

Figure 5.4 EXTAL External Input Clock Timing

# 5.4 A/D Conversion Characteristics

#### Table 5.15 10-Bit A/D Conversion Characteristics

Note: Items for which test conditions are not specifically stated in the table below have the same values under conditions 1 to 3.

Condition 1: VCC = PLLVCC = 2.7 to 3.6 V, VSS = PLLVSS = AVSS0 = AVSS = VREFL0 = 0 V

AVCC0 = AVCC = 3.0 to 3.6 V, VREFH0 = 3.0 V to AVCC0, VREF = 3.0 V to AVCC

Ta = Topr

| Item                                               | Min. | Тур. | Max. | Unit | Test Conditions    |

|----------------------------------------------------|------|------|------|------|--------------------|

| Resolution                                         | 10   | 10   | 10   | Bit  |                    |

| Conversion time*1<br>(AD clock = 25-MHz operation) | 2.0  | -    | -    | μS   | Sampling 25 states |

| Analog input capacitance                           | -    | -    | 4    | pF   |                    |

| Integral nonlinearity error                        | -    | -    | ±3.0 | LSB  |                    |

| Offset error                                       | -    | -    | ±3.0 | LSB  |                    |

| Full-scale error                                   | -    | -    | ±3.0 | LSB  |                    |

| Quantization error                                 | -    | ±0.5 | -    | LSB  |                    |

| Absolute accuracy                                  | -    | -    | ±4.0 | LSB  |                    |

| Permissible signal source impedance                | -    | -    | 1.0  | kΩ   |                    |

Condition 2: VCC = PLLVCC = 2.7 to 3.6 V, VSS = PLLVSS = AVSS0 = AVSS = VREFL0 = 0 V AVCC0 = AVCC = 4.0 to 5.5 V, VREFH0 = 4.0 V to AVCC0, VREF = 4.0 V to AVCC

Condition 3: VCC = PLLVCC = 4.0 to 5.5 V, VSS = PLLVSS = AVSS0 = AVSS = VREFL0 = 0 V AVCC0 = AVCC = 4.0 to 5.5 V, VREFH0 = 4.0 V to AVCC0, VREF = 4.0 V to AVCC Ta = Topr. Ta is the same under conditions 2 and 3.

| Item                                               | Min. | Тур. | Max. | Unit | Test Conditions    |

|----------------------------------------------------|------|------|------|------|--------------------|

| Resolution                                         | 10   | 10   | 10   | Bit  |                    |

| Conversion time*1<br>(AD clock = 50-MHz operation) | 1.0  | -    | -    | μS   | Sampling 25 states |

| Analog input capacitance                           | -    | -    | 4    | pF   |                    |

| Integral nonlinearity error                        | -    | -    | ±3.0 | LSB  |                    |

| Offset error                                       | -    | -    | ±3.0 | LSB  |                    |

| Full-scale error                                   | -    | -    | ±3.0 | LSB  |                    |

| Quantization error                                 | -    | ±0.5 | -    | LSB  |                    |

| Absolute accuracy                                  | -    | -    | ±4.0 | LSB  |                    |

| Permissible signal source impedance                | -    | -    | 1.0  | kΩ   |                    |

Note 1. The conversion time includes the sampling time and the comparison time. As the test conditions, the number of sampling states is indicated.

#### Table 5.17 Characteristics of the Programmable Gain Amplifier

Note: Items for which test conditions are not specifically stated in the table below have the same values under conditions 1 to 3.

$\begin{array}{l} \mbox{Condition 1: VCC = PLLVCC = 2.7 to 3.6 V, VSS = PLLVSS = AVSS0 = AVSS = VREFL0 = 0 V \\ \mbox{AVCC0 = AVCC = 3.0 to 3.6 V, VREFH0 = 3.0 V to AVCC0, VREF = 3.0 V to AVCC} \end{array}$

Condition 2: VCC = PLLVCC = 2.7 to 3.6 V, VSS = PLLVSS = AVSS0 = AVSS = VREFL0 = 0 V

AVCC0 = AVCC = 4.0 to 5.5 V, VREFH0 = 4.0 V to AVCC0, VREF = 4.0 V to AVCC

Condition 3: VCC = PLLVCC = 4.0 to 5.5 V, VSS = PLLVSS = AVSS0 = AVSS = VREFL0 = 0 V AVCC0 = AVCC = 4.0 to 5.5V, VREFH0 = 4.0 V to AVCC0, VREF = 4.0 V to AVCC Ta = Topr. Ta is the same under conditions 1 to 3.

| ltem                     |               | Symbol | Min.         | Тур. | Max.         | Unit | Test<br>Conditions |

|--------------------------|---------------|--------|--------------|------|--------------|------|--------------------|

| Analog input capacitance |               | Cin    | -            | -    | 6            | pF   |                    |

| Input offset volta       | age           | Voff   | -            | -    | 8            | mV   |                    |

| Input voltage            | Gain × 2.000  | Vin    | 0.050 x AVcc | -    | 0.450 x AVcc | V    |                    |

| range (Vin)              | Gain × 2.500  |        | 0.047 x AVcc | -    | 0.360 x AVcc |      |                    |

|                          | Gain × 3.077  |        | 0.045 x AVcc | -    | 0.292 x AVcc |      |                    |

|                          | Gain × 3.636  |        | 0.042 x AVcc | -    | 0.247 x AVcc |      |                    |

|                          | Gain × 4.000  |        | 0.040 x AVcc | -    | 0.212 x AVcc |      |                    |

|                          | Gain × 4.444  |        | 0.036 x AVcc | -    | 0.191 x AVcc |      |                    |

|                          | Gain × 5.000  |        | 0.033 x AVcc | -    | 0.170 x AVcc |      |                    |