#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI                                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64 x 8                                                                   |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 5x10b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 28-SPDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f872-e-sp |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, microID, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, PowerSmart, rfPIC and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AmpLab, FilterLab, Migratable Memory, MXDEV, MXLAB, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, ECAN, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, Linear Active Thermistor, Mindi, MiWi, MPASM, MPLIB, MPLINK, PICkit, PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, rfPICDEM, Select Mode, Smart Serial, SmartTel, Total Endurance, UNI/O, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2006, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona, Gresham, Oregon and Mountain View, California. The Company's quality system processes and procedures are for its PICmicro® 8-bit MCUs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

#### 2.2.2.2 OPTION\_REG Register

The OPTION\_REG Register is a readable and writable register, which contains various control bits to configure the TMR0 prescaler/WDT postscaler (single assignable register known also as the prescaler), the External INT Interrupt, TMR0 and the weak pull-ups on PORTB.

Note: To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer.

#### REGISTER 2-2: OPTION\_REG REGISTER (ADDRESS 81h, 181h)

|         | R/W-1            | R/W-1                               | R/W-1         | R/W-1        | R/W-1         | R/W-1      | R/W-1        | R/W-1 |

|---------|------------------|-------------------------------------|---------------|--------------|---------------|------------|--------------|-------|

|         | RBPU             | INTEDG                              | TOCS          | T0SE         | PSA           | PS2        | PS1          | PS0   |

|         | bit 7            |                                     |               |              |               |            |              | bit C |

| bit 7   |                  | ORTB Pull-up<br>B pull-ups ar       |               |              |               |            |              |       |

|         |                  | B pull-ups ar                       |               | y individual | port latch va | lues       |              |       |

| bit 6   | INTEDG:          | Interrupt Edg                       | e Select bit  |              |               |            |              |       |

|         |                  | upt on rising e<br>upt on falling ( | •             | •            |               |            |              |       |

| bit 5   | <b>T0CS</b> : TM | IR0 Clock So                        | urce Select   | bit          |               |            |              |       |

|         |                  | tion on RA4/<br>al instruction      | •             | (CLKOUT)     |               |            |              |       |

| bit 4   | TOSE: TM         | R0 Source E                         | dge Select I  | oit          |               |            |              |       |

|         |                  | nent on high-<br>nent on low-to     |               |              |               |            |              |       |

| bit 3   | PSA: Pres        | scaler Assign                       | ment bit      |              |               |            |              |       |

|         |                  | aler is assign<br>aler is assign    |               |              | Э             |            |              |       |

| bit 2-0 | PS2:PS0:         | Prescaler Ra                        | ate Select bi | ts           |               |            |              |       |

|         | Bit Value        | TMR0 Rate                           | WDT Rate      |              |               |            |              |       |

|         | 000<br>001       | 1:2<br>1:4                          | 1:1<br>1:2    |              |               |            |              |       |

|         | 010<br>011       | 1:8<br>1:16                         | 1:4<br>1:8    |              |               |            |              |       |

|         | 100              | 1:32                                | 1:16          |              |               |            |              |       |

|         | 101<br>110       | 1:64                                | 1:32<br>1:64  |              |               |            |              |       |

|         | 111              | 1 : 128<br>1 : 256                  | 1 : 128       |              |               |            |              |       |

|         | Legend:          |                                     |               |              |               |            |              |       |

|         | R = Reada        | able bit                            | W = W         | ritable bit  | U = Unim      | nolemented | bit, read as | 0'    |

|         | -n = Value       |                                     |               | it is set    |               | s cleared  | x = Bit is u |       |

|         | = tala           |                                     | · – D         |              |               |            |              |       |

ation of the device

## 2.3 PCL and PCLATH

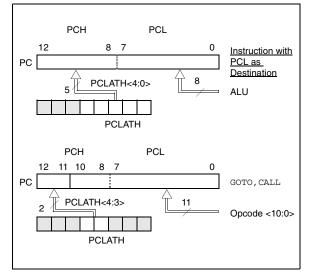

The program counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a readable and writable register. The upper bits (PC<12:8>) are not readable, but are indirectly writable through the PCLATH register. On any RESET, the upper bits of the PC will be cleared. Figure 2-3 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 2-3: LOADING OF PC IN DIFFERENT SITUATIONS

## 2.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 byte block). Refer to the Application Note, *"Implementing a Table Read"* (AN556).

## 2.3.2 STACK

The PIC16FXXX family has an 8-level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

**Note 1:** There are no status bits to indicate stack overflow or stack underflow conditions.

2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions, or the vectoring to an interrupt address.

## 2.4 Program Memory Paging

All PIC16FXXX devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction, the upper 2 bits of the address are provided by PCLATH<4:3>. Since the PIC16F872 has only 2K words of program memory or one page, additional code is not required to ensure that the correct page is selected before a CALL or GOTO instruction is executed. The PCLATH<4:3> bits should always be maintained as zeros. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is popped off the stack. Therefore. manipulation of the PCLATH<4:3> bits are not required for the return instructions (which POPs the address from the stack).

Note: The contents of the PCLATH register are unchanged after a RETURN or RETFIE instruction is executed. The user must rewrite the contents of the PCLATH register for any subsequent subroutine calls or GOTO instructions. The steps to write to program memory are:

- 1. Write the address to EEADRH:EEADR. Make sure that the address is not larger than the memory size of the device.

- 2. Write the 14-bit data value to be programmed in the EEDATH:EEDATA registers.

- 3. Set the EEPGD bit to point to FLASH Program memory.

- 4. Set the WREN bit to enable program operations.

- 5. Disable interrupts (if enabled).

- 6. Execute the special five instruction sequence:

- Write 55h to EECON2 in two steps (first to W, then to EECON2)

- Write AAh to EECON2 in two steps (first to W, then to EECON2)

- · Set the WR bit

- 7. Execute two NOP instructions to allow the microcontroller to setup for write operation.

- 8. Enable interrupts (if using interrupts).

- 9. Clear the WREN bit to disable program operations.

At the completion of the write cycle, the WR bit is cleared and the EEIF interrupt flag bit is set. (EEIF must be cleared by firmware). Since the microcontroller does not execute instructions during the write cycle, the firmware does not necessarily have to check either EEIF or WR to determine if the write had finished.

|   |                      | BSF   | STATUS, RP1   | ;                        |

|---|----------------------|-------|---------------|--------------------------|

|   |                      | BCF   | STATUS, RPO   | ;Bank 2                  |

|   |                      | MOVF  | ADDRL, W      | ;Write address           |

|   |                      | MOVWF | EEADR         | ;of desired              |

|   |                      | MOVF  | ADDRH, W      | ;program memory          |

|   |                      | MOVWF | EEADRH        | ;location                |

|   |                      | MOVF  | VALUEL, W     | ;Write value to          |

|   |                      | MOVWF | EEDATA        | ;program at              |

|   |                      | MOVF  | VALUEH, W     | ;desired memory          |

|   |                      | MOVWF | EEDATH        | ;location                |

|   |                      | BSF   | STATUS, RPO   | ;Bank 3                  |

|   |                      | BSF   | EECON1, EEPGD | ;Point to Program memory |

|   |                      | BSF   | EECON1, WREN  | ;Enable writes           |

|   |                      |       |               | ;Only disable interrupts |

|   |                      | BCF   | INTCON, GIE   | ; if already enabled,    |

|   |                      |       |               | ;otherwise discard       |

|   |                      | MOVLW | 0x55          | ;Write 55h to            |

|   |                      | MOVWF | EECON2        | ; EECON2                 |

|   | Required<br>Sequence | MOVLW | 0xAA          | ;Write AAh to            |

|   | qui                  | MOVWF | EECON2        | ; EECON2                 |

|   | Sec                  | BSF   | EECON1, WR    | ;Start write operation   |

|   |                      | NOP   |               | ;Two NOPs to allow micro |

|   |                      | NOP   |               | ;to setup for write      |

|   |                      |       |               | ;Only enable interrupts  |

|   |                      | BSF   | INTCON, GIE   | ; if using interrupts,   |

| 1 |                      |       |               | ;otherwise discard       |

| 1 |                      | BCF   | EECON1, WREN  | ;Disable writes          |

|   |                      |       |               |                          |

#### EXAMPLE 3-4: FLASH PROGRAM WRITE

## 3.6 Write Verify

The PIC16F87X devices do not automatically verify the value written during a write operation. Depending on the application, good programming practice may dictate that the value written to memory be verified against the original value. This should be used in applications where excessive writes can stress bits near the specified endurance limits.

## 3.7 Protection Against Spurious Writes

There are conditions when the device may not want to write to the EEPROM Data memory or FLASH program memory. To protect against these spurious write conditions various mechanisms have been built into the device. On power-up, the WREN bit is cleared and the Power-up Timer (if enabled) prevents writes.

The write initiate sequence and the WREN bit together help prevent any accidental writes during brown-out, power glitches or firmware malfunction.

| Name         | Bit# | Buffer | Function                                                                        |  |  |  |

|--------------|------|--------|---------------------------------------------------------------------------------|--|--|--|

| RA0/AN0      | bit0 | TTL    | Input/output or analog input.                                                   |  |  |  |

| RA1/AN1      | bit1 | TTL    | nput/output or analog input.                                                    |  |  |  |

| RA2/AN2      | bit2 | TTL    | Input/output or analog input.                                                   |  |  |  |

| RA3/AN3/VREF | bit3 | TTL    | Input/output or analog input or VREF.                                           |  |  |  |

| RA4/T0CKI    | bit4 | ST     | Input/output or external clock input for Timer0.<br>Output is open drain type.  |  |  |  |

| RA5/SS/AN4   | bit5 | TTL    | Input/output or slave select input for synchronous serial port or analog input. |  |  |  |

#### TABLE 4-1: PORTA FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

## TABLE 4-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3      | Bit 2 | Bit 1   | Bit 0   | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|---------|--------|-------|-------|-------|--------|------------|-------|---------|---------|--------------------------|---------------------------------|

| 05h     | PORTA  | —     | —     | RA5   | RA4    | RA3        | RA2   | RA1     | RA0     | 0x 0000                  | 0u 0000                         |

| 85h     | TRISA  | —     |       | PORTA | Data D | irection F |       | 11 1111 | 11 1111 |                          |                                 |

| 9Fh     | ADCON1 | ADFM  | _     | _     |        | PCFG3      | PCFG2 | PCFG1   | PCFG0   | 0- 0000                  | 0- 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

Note: When using the SSP module in SPI Slave mode and  $\overline{SS}$  enabled, the A/D converter must be set to one of the following modes, where PCFG3:PCFG0 = 0100, 0101, 011x, 1101, 1110, 1111.

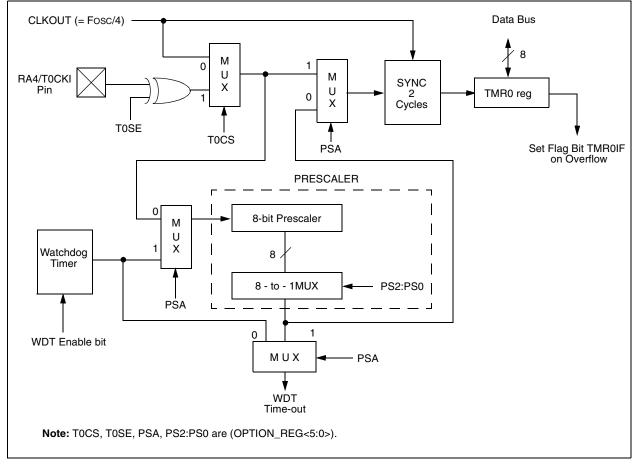

## 5.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge select for external clock

Figure 5-1 is a block diagram of the Timer0 module and the prescaler shared with the WDT.

Additional information on the Timer0 module is available in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023).

Timer mode is selected by clearing bit TOCS (OPTION\_REG<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register. Counter mode is selected by setting bit TOCS (OPTION\_REG<5>). In Counter mode, Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit T0SE (OPTION\_REG<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 5.2.

The prescaler is mutually exclusively shared between the Timer0 module and the Watchdog Timer. The prescaler is not readable or writable. Section 5.3 details the operation of the prescaler.

## 5.1 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit TMR0IF (INTCON<2>). The interrupt can be masked by clearing bit TMR0IE (INTCON<5>). Bit TMR0IF must be cleared in software by the Timer0 module Interrupt Service Routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from SLEEP, since the timer is shut-off during SLEEP.

FIGURE 5-1: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

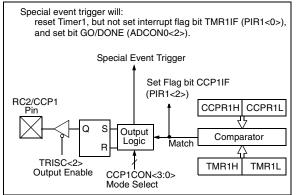

## 8.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 pin is:

- Driven high

- Driven low

- · Remains unchanged

The action on the pin is based on the value of control bits, CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

#### FIGURE 8-2: COMPARE MODE OPERATION BLOCK DIAGRAM

## 8.2.1 CCP PIN CONFIGURATION

The user must configure the RC2/CCP1 pin as an output by clearing the TRISC<2> bit.

| Note: | Clearing the CCP1CON register will force |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|

|       | the RC2/CCP1 compare output latch to the |  |  |  |  |  |  |

|       | default low level. This is not the PORTC |  |  |  |  |  |  |

|       | I/O data latch.                          |  |  |  |  |  |  |

#### 8.2.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

## 8.2.3 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt mode is chosen, the CCP1 pin is not affected. The CCPIF bit is set, causing a CCP interrupt (if enabled).

#### 8.2.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated, which may be used to initiate an action.

The special event trigger output of CCP1 resets the TMR1 register pair and starts an A/D conversion (if the A/D module is enabled). This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

**Note:** The special event trigger from the CCP module will not set interrupt flag bit TMR1IF (PIR1<0>).

## TABLE 8-2: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, AND TIMER1

| Address                | Name    | Bit 7   | Bit 6                               | Bit 5         | Bit 4         | Bit 3          | Bit 2        | Bit 1      | Bit 0  | Value<br>PO<br>BC | R,   | all o | e on<br>other<br>SETS |

|------------------------|---------|---------|-------------------------------------|---------------|---------------|----------------|--------------|------------|--------|-------------------|------|-------|-----------------------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON  | GIE     | PEIE                                | TMR0IE        | INTE          | RBIE           | TMR0IF       | INTF       | RBIF   | 0000              | 000x | 0000  | 000u                  |

| 0Ch                    | PIR1    | (1)     | ADIF                                | (1)           | (1)           | SSPIF          | CCP1IF       | TMR2IF     | TMR1IF | r0rr              | 0000 | 0000  | 0000                  |

| 8Ch                    | PIE1    | (1)     | ADIE                                | (1)           | (1)           | SSPIE          | CCP1IE       | TMR2IE     | TMR1IE | r0rr              | 0000 | 0000  | 0000                  |

| 87h                    | TRISC   | PORTC   | Data Di                             | rection Reg   | ister         |                |              |            |        | 1111              | 1111 | 1111  | 1111                  |

| 0Eh                    | TMR1L   | Holding | Registe                             | r for the Lea | ast Significa | nt Byte of th  | ie 16-bit Tl | MR1 Regis  | ster   | xxxx              | xxxx | uuuu  | uuuu                  |

| 0Fh                    | TMR1H   | Holding | Registe                             | r for the Mo  | st Significar | nt Byte of the | e 16-bit TN  | /IR1 Regis | ter    | xxxx              | xxxx | uuuu  | uuuu                  |

| 10h                    | T1CON   | —       | —                                   | T1CKPS1       | T1CKPS0       | T1OSCEN        | T1SYNC       | TMR1CS     | TMR10N | 00                | 0000 | uu    | uuuu                  |

| 15h                    | CCPR1L  | Capture | Capture/Compare/PWM Register1 (LSB) |               |               |                |              |            |        |                   | xxxx | uuuu  | uuuu                  |

| 16h                    | CCPR1H  | Capture | /Compa                              | re/PWM Re     | gister1 (MS   | B)             |              |            |        | xxxx              | xxxx | uuuu  | uuuu                  |

| 17h                    | CCP1CON | _       | _                                   | CCP1X         | CCP1Y         | CCP1M3         | CCP1M2       | CCP1M1     | CCP1M0 | 00                | 0000 | 00    | 0000                  |

Note 1: These bits are reserved; always maintain clear.

NOTES:

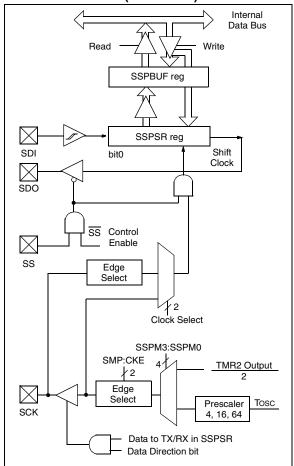

## 9.1 SPI Mode

The SPI mode allows 8 bits of data to be synchronously transmitted and received, simultaneously. All four modes of SPI are supported. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO)

- Serial Data In (SDI)

- Serial Clock (SCK)

Additionally, a fourth pin may be used when in a Slave mode of operation:

• Slave Select (SS)

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPCON<5:0> and SSPSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (IDLE state of SCK)

- Data input sample phase (middle or end of data output time)

- Clock edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- Slave Select mode (Slave mode only)

Figure 9-4 shows the block diagram of the MSSP module when in SPI mode.

To enable the serial port, MSSP Enable bit, SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear bit SSPEN, re-initialize the SSPCON registers, and then set bit SSPEN. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed. That is:

- SDI is automatically controlled by the SPI module

- SDO must have TRISC<5> cleared

- SCK (Master mode) must have TRISC<3> cleared

- SCK (Slave mode) must have TRISC<3> set

- SS must have TRISA<5> set, and

- Register ADCON1 must be set in a way that pin RA5 is configured as a digital I/O

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

#### FIGURE 9-1:

#### MSSP BLOCK DIAGRAM (SPI MODE)

## 9.1.1 MASTER MODE

The master can initiate the data transfer at any time because it controls the SCK. The master determines when the slave (Processor 2, Figure 9-5) is to broad-cast data by the software protocol.

In Master mode, the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI module is only going to receive, the SDO output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and status bits appropriately set). This could be useful in receiver applications as a "line activity monitor".

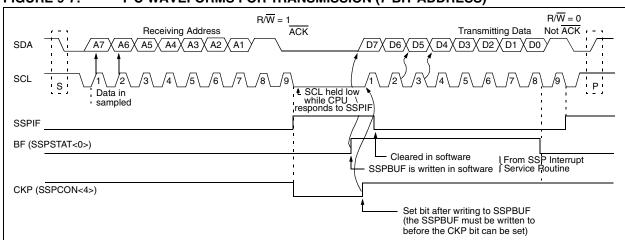

#### FIGURE 9-7: I<sup>2</sup>C WAVEFORMS FOR TRANSMISSION (7-BIT ADDRESS)

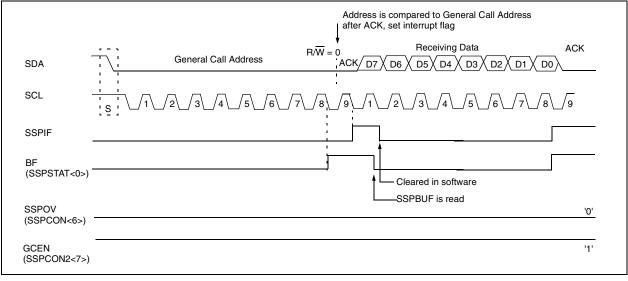

#### 9.2.2 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the  $I^2C$  bus is such that the first byte after the START condition usually determines which device will be the slave addressed by the master. The exception is the general call address, which can address all devices. When this address is used, all devices should, in theory, respond with an Acknowledge.

The general call address is one of eight addresses reserved for specific purposes by the I<sup>2</sup>C protocol. It consists of all 0's with R/W = 0.

The general call address is recognized when the General Call Enable bit (GCEN) is enabled (SSPCON2<7> is set). Following a START bit detect, 8-bits are shifted into SSPSR and the address is compared against SSPADD. It is also compared to the general call address and fixed in hardware. If the general call address matches, the SSPSR is transferred to the SSPBUF, the BF flag is set (eighth bit), and on the falling edge of the ninth bit (ACK bit), the SSPIF flag is set.

When the interrupt is serviced, the source for the interrupt can be checked by reading the contents of the SSPBUF, to determine if the address was device specific or a general call address.

In 10-bit mode, the SSPADD is required to be updated for the second half of the address to match, and the UA bit is set (SSPSTAT<1>). If the general call address is sampled when GCEN is set while the slave is configured in 10-bit Address mode, then the second half of the address is not necessary, the UA bit will not be set, and the slave will begin receiving data after the Acknowledge (Figure 9-8).

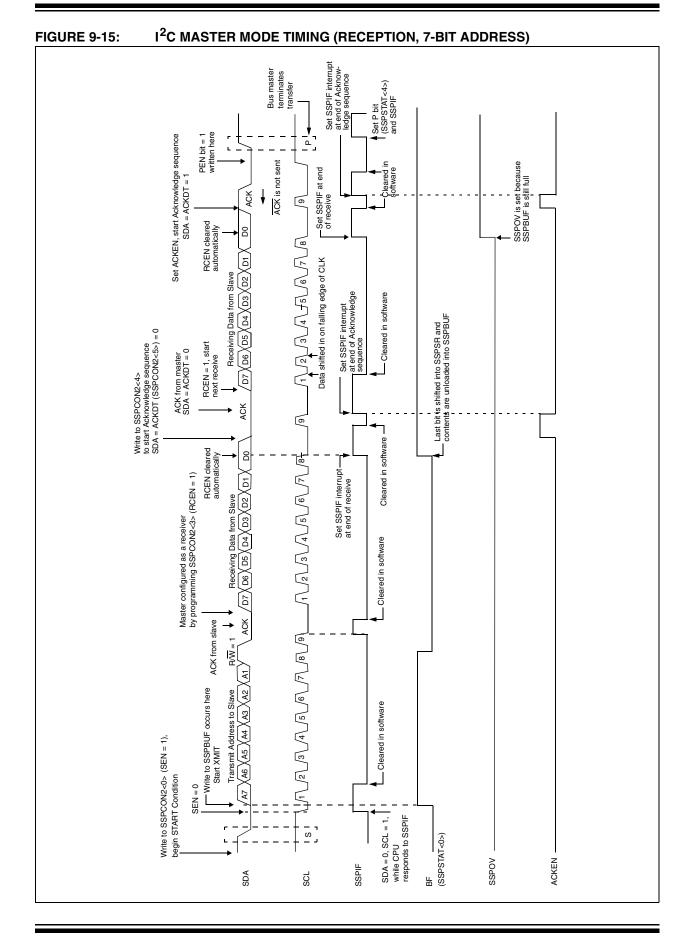

## 9.2.12 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the receive enable bit, RCEN (SSPCON2<3>).

# Note: The SSP module must be in an IDLE state before the RCEN bit is set, or the RCEN bit will be disregarded.

The baud rate generator begins counting, and on each rollover, the state of the SCL pin changes (high to low/ low to high), and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag is set, the SSPIF is set, and the baud rate generator is suspended from counting, holding SCL low. The SSP is now in IDLE state, awaiting the next command. When the buffer is read by the CPU, the BF flag is automatically cleared. The user can then send an Acknowledge bit at the end of reception, by setting the Acknowledge sequence enable bit, ACKEN (SSPCON2<4>).

#### 9.2.12.1 BF Status Flag

In receive operation, BF is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when SSPBUF is read.

#### 9.2.12.2 SSPOV Status Flag

In receive operation, SSPOV is set when 8 bits are received into the SSPSR, and the BF flag is already set from a previous reception.

### 9.2.12.3 WCOL Status Flag

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

## PIC16F872

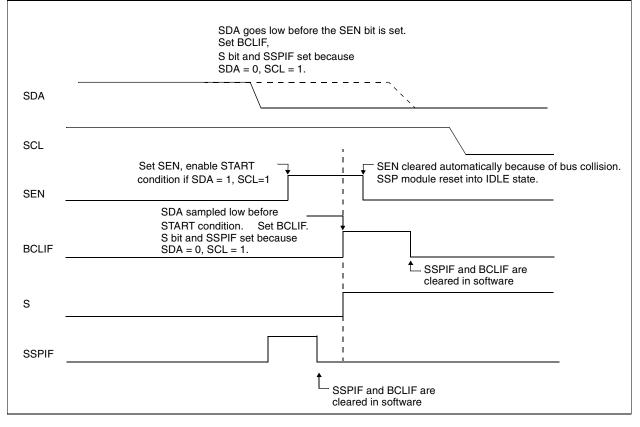

#### 9.2.18.1 Bus Collision During a START Condition

During a START condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the START condition (Figure 9-20).

- b) SCL is sampled low before SDA is asserted low. (Figure 9-21).

During a START condition, both the SDA and the SCL pins are monitored. If either the SDA pin <u>or</u> the SCL pin is already low, then these events all occur:

- the START condition is aborted,

- and the BCLIF flag is set

- <u>and</u> the SSP module is reset to its IDLE state (Figure 9-20).

The START condition begins with the SDA and SCL pins de-asserted. When the SDA pin is sampled high, the baud rate generator is loaded from SSPADD<6:0> and counts down to 0. If the SCL pin is sampled low while SDA is high, a bus collision occurs, because it is assumed that another master is attempting to drive a data '1' during the START condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 9-22). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The baud rate generator is then reloaded and counts down to 0. During this time, if the SCL pins are sampled as '0', a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a START condition, is that no two bus masters can assert a START condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision, because the two masters must be allowed to arbitrate the first address following the START condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated START or STOP conditions.

## FIGURE 9-20: BUS COLLISION DURING START CONDITION (SDA ONLY)

NOTES:

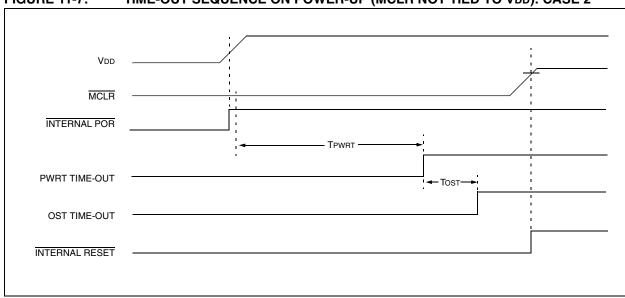

FIGURE 11-7: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

# PIC16F872

| SWAPF            | Swap Nibbles in f                                                                                                                                                              |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] SWAPF f,d                                                                                                                                                     |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                             |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>), (f<7:4>) \rightarrow (destination<3:0>)$                                                                                             |

| Status Affected: | None                                                                                                                                                                           |

| Description:     | The upper and lower nibbles of<br>register 'f' are exchanged. If 'd' is<br>0, the result is placed in the W<br>register. If 'd' is 1, the result is<br>placed in register 'f'. |

| XORWF            | Exclusive OR W with f                                                                                                                                                       |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] XORWF f,d                                                                                                                                                           |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                                                  |  |  |  |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                   |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                           |  |  |  |  |  |  |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |  |  |  |  |  |  |

| XORLW            | Exclusive OR Literal with W                                                                                                  |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                                     |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                            |  |  |  |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                                |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                            |  |  |  |  |  |  |

| Description:     | The contents of the W register<br>are XOR'ed with the eight-bit lit-<br>eral 'k'. The result is placed in<br>the W register. |  |  |  |  |  |  |

## 14.2 DC Characteristics: PIC16F872 (Commercial, Industrial) PIC16LF872 (Commercial, Industrial) (Continued)

| DC CHA       | ARACTE | RISTICS                                                | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $0^{\circ}C \le TA \le +70^{\circ}C$ for commercialOperating voltage VDD range as described in DC specification |                     |          |       |                                                             |  |  |  |

|--------------|--------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------|-------|-------------------------------------------------------------|--|--|--|

| Param<br>No. | Sym    | Characteristic                                         | (Section 1<br>Min                                                                                                                                                                                                                                  | 4.1)<br><b>Typ†</b> | Мах      | Units | Conditions                                                  |  |  |  |

|              | Vol    | Output Low Voltage                                     |                                                                                                                                                                                                                                                    |                     |          |       |                                                             |  |  |  |

| D080         | VOL    | I/O ports                                              | -                                                                                                                                                                                                                                                  | -                   | 0.6      | v     | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C                 |  |  |  |

| D083         |        | OSC2/CLKOUT (RC osc config)                            | -                                                                                                                                                                                                                                                  | -                   | 0.6      | V     | IOL = 1.6 mA, VDD = 4.5V,<br>-40°C to +85°C                 |  |  |  |

|              | Vон    | Output High Voltage                                    |                                                                                                                                                                                                                                                    |                     |          |       |                                                             |  |  |  |

| D090         |        | I/O ports <sup>(3)</sup>                               | Vdd - 0.7                                                                                                                                                                                                                                          | -                   | -        | V     | IOH = -3.0 mA, VDD = 4.5V,<br>-40°C to +85°C                |  |  |  |

| D092         |        | OSC2/CLKOUT (RC osc config)                            | Vdd - 0.7                                                                                                                                                                                                                                          | -                   | -        | V     | IOH = -1.3 mA, VDD = 4.5V,<br>-40°С to +85°С                |  |  |  |

| D150*        | Vod    | Open Drain High Voltage                                | -                                                                                                                                                                                                                                                  | -                   | 8.5      | V     | RA4 pin                                                     |  |  |  |

| D100         | Cosc2  | Capacitive Loading Specs on<br>Output Pins<br>OSC2 pin | -                                                                                                                                                                                                                                                  | -                   | 15       | pF    | In XT, HS and LP modes when external clock is used to drive |  |  |  |

|              |        |                                                        |                                                                                                                                                                                                                                                    |                     |          |       | OSC1                                                        |  |  |  |

| D101         | Cio    | All I/O pins and OSC2 (RC                              | -                                                                                                                                                                                                                                                  | -                   | 50       | pF    |                                                             |  |  |  |

| D102         | Св     | mode) SCL, SDA (I <sup>2</sup> C mode)                 | -                                                                                                                                                                                                                                                  | -                   | 400      | pF    |                                                             |  |  |  |

| D120         | ED     | Data EEPROM Memory Endurance                           | 100K                                                                                                                                                                                                                                               |                     |          | E/W   | 25°C at 5V                                                  |  |  |  |

| D120<br>D121 | VDRW   | VDD for read/write                                     | VMIN                                                                                                                                                                                                                                               | -                   | -<br>5.5 | V     | Using EECON to read/write                                   |  |  |  |

| D122         | TDEW   | Erase/write cycle time                                 | -                                                                                                                                                                                                                                                  | 4                   | 8        | ms    |                                                             |  |  |  |

|              |        | Program FLASH Memory                                   |                                                                                                                                                                                                                                                    |                     |          |       |                                                             |  |  |  |

| D130         | Ер     | Endurance                                              | 1000                                                                                                                                                                                                                                               | -                   | -        | E/W   | 25°C at 5V                                                  |  |  |  |

| D131         | VPR    | VDD for read                                           | VMIN                                                                                                                                                                                                                                               | -                   | 5.5      | V     | Vmin = min operating voltage                                |  |  |  |

| D132A        |        | VDD for erase/write                                    | VMIN                                                                                                                                                                                                                                               | -                   | 5.5      | V     | Using EECON to read/write,<br>VMIN = min. operating voltage |  |  |  |

| D133         | TPEW   | Erase/Write cycle time                                 | -                                                                                                                                                                                                                                                  | 4                   | 8        | ms    |                                                             |  |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16F872 be driven with external clock in RC mode.

The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

Negative surrent is defined as surrent expressed by the pin.

3: Negative current is defined as current sourced by the pin.

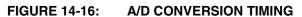

#### TABLE 14-10: A/D CONVERSION REQUIREMENTS

| Param<br>No. | Sym  | Characteristic                                    |              | Min      | Тур†     | Max | Units | Conditions                                                                                                                                                                                                                      |

|--------------|------|---------------------------------------------------|--------------|----------|----------|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130          | TAD  | A/D Clock Period                                  | Standard(F)  | 1.6      |          |     | μs    | Tosc based, VREF ≥ 3.0V                                                                                                                                                                                                         |

|              |      |                                                   | Extended(LF) | 3.0      | —        |     | μs    | Tosc based, VREF ≥ 2.0V                                                                                                                                                                                                         |

|              |      |                                                   | Standard(F)  | 2.0      | 4.0      | 6.0 | μs    | A/D RC mode                                                                                                                                                                                                                     |

|              |      |                                                   | Extended(LF) | 3.0      | 6.0      | 9.0 | μs    | A/D RC mode                                                                                                                                                                                                                     |

| 131          | TCNV | Conversion Time (not including S/H time) (Note 1) |              |          | —        | 12  | TAD   |                                                                                                                                                                                                                                 |

| 132          | TACQ | Acquisition Time                                  |              | (Note 2) | 40       |     | μs    |                                                                                                                                                                                                                                 |

|              |      |                                                   |              | 10*      |          | _   | μs    | The minimum time is the<br>amplifier settling time. This may<br>be used if the "new" input volt-<br>age has not changed by more<br>than 1 LSb (i.e., 20.0 mV @<br>5.12V) from the last sampled<br>voltage (as stated on CHOLD). |

| 134          | TGO  | Q4 to A/D Clock Star                              | t            | _        | Tosc/2 § | _   | _     | If the A/D clock source is<br>selected as RC, a time of Tcy is<br>added before the A/D clock<br>starts. This allows the SLEEP<br>instruction to be executed.                                                                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

Note 1: ADRES register may be read on the following TCY cycle.

**2:** See Section 10.1 for min. conditions.

## APPENDIX A: REVISION HISTORY

| Version | Date  | Revision Description                                                                                                                                                  |  |

|---------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| A       | 11/99 | This is a new data sheet (Pre-<br>liminary). However, these<br>devices are similar to the<br>PIC16C72A devices found in<br>the PIC16C62B/72A Data<br>Sheet (DS35008). |  |

| В       | 12/01 | Final version of data sheet.<br>Includes DC and AC charac-<br>teristics graphs and updated<br>electrical specifications.                                              |  |

| С       | 9/06  | Packaging diagrams updated.                                                                                                                                           |  |

## APPENDIX B: CONVERSION CONSIDERATIONS

Considerations for converting from previous versions of devices to the ones listed in this data sheet are listed in Table B-1.

| TABLE B-1: | CONVERSION     |  |

|------------|----------------|--|

|            | CONSIDERATIONS |  |

| Characteristic    | PIC16C72A                                     | PIC16F872                                             |

|-------------------|-----------------------------------------------|-------------------------------------------------------|

| Pins              | 28                                            | 28                                                    |

| Timers            | 3                                             | 3                                                     |

| Interrupts        | 7                                             | 10                                                    |

| Communication     | Basic SSP<br>(SPI, I <sup>2</sup> C<br>Slave) | SSP (SPI, I <sup>2</sup> C<br>Master/Slave)           |

| Frequency         | 20 MHz                                        | 20 MHz                                                |

| A/D               | 8-bit,<br>5 channels                          | 10-bit<br>5 channels                                  |

| ССР               | 1                                             | 1                                                     |

| Program<br>Memory | 2K EPROM                                      | 2K FLASH                                              |

| RAM               | 128 bytes                                     | 128 bytes                                             |

| EEPROM Data       | None                                          | 64 bytes                                              |

| Other             | _                                             | In-Circuit<br>Debugger,<br>Low Voltage<br>Programming |

## WORLDWIDE SALES AND SERVICE

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://support.microchip.com Web Address: www.microchip.com

Atlanta Alpharetta, GA Tel: 770-640-0034 Fax: 770-640-0307

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

**Chicago** Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

**Kokomo** Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Habour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Fuzhou** Tel: 86-591-8750-3506 Fax: 86-591-8750-3521

**China - Hong Kong SAR** Tel: 852-2401-1200 Fax: 852-2401-3431

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

**China - Shunde** Tel: 86-757-2839-5507 Fax: 86-757-2839-5571

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7250 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-4182-8400 Fax: 91-80-4182-8422

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Yokohama** Tel: 81-45-471- 6166 Fax: 81-45-471-6122

**Korea - Gumi** Tel: 82-54-473-4301 Fax: 82-54-473-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

**Malaysia - Penang** Tel: 60-4-646-8870 Fax: 60-4-646-5086

Philippines - Manila Tel: 63-2-634-9065

Fax: 63-2-634-9069 Singapore Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-572-9526 Fax: 886-3-572-6459

**Taiwan - Kaohsiung** Tel: 886-7-536-4818 Fax: 886-7-536-4803

**Taiwan - Taipei** Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-3910 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820