Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

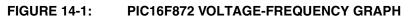

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I²C, SPI                                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64 × 8                                                                   |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 5x10b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                           |

| Supplier Device Package    | 28-SSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f872-e-ss |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Write operations have two control bits, WR and WREN. and two status bits, WRERR and EEIF. The WREN bit is used to enable or disable the write operation. When WREN is clear, the write operation will be disabled. Therefore, the WREN bit must be set before executing a write operation. The WR bit is used to initiate the write operation. It also is automatically cleared at the end of the write operation. The interrupt flag EEIF (located in register PIR2) is used to determine when the memory write completes. This flag must be cleared in software before setting the WR bit. For EEPROM Data memory, once the WREN bit and the WR bit have been set, the desired memory address in EEADR will be erased followed by a write of the data in EEDATA. This operation takes place in parallel with the microcontroller continuing to execute normally. When the write is complete, the EEIF flag bit will be set. For program memory, once the WREN bit and the WR bit have been set, the microcontroller will cease to execute instructions. The

desired memory location pointed to by EEADRH:EEADR will be erased. Then the data value in EEDATH:EEDATA will be programmed. When complete, the EEIF flag bit will be set and the microcontroller will continue to execute code.

The WRERR bit is used to indicate when the device has been RESET during a write operation. WRERR should be cleared after Power-on Reset. Thereafter, it should be checked on any other RESET. The WRERR bit is set when a write operation is interrupted by a MCLR Reset or a WDT Time-out Reset during normal operation. In these situations, following a RESET, the user should check the WRERR bit and rewrite the memory location if set. The contents of the data registers, address registers and EEPGD bit are not affected by either MCLR Reset or WDT Time-out Reset during normal operation.

## REGISTER 3-1: EECON1 REGISTER (ADDRESS 18Ch)

| -       |                |                                                            |               |               |              |               |               |           |  |  |  |  |  |

|---------|----------------|------------------------------------------------------------|---------------|---------------|--------------|---------------|---------------|-----------|--|--|--|--|--|

|         | R/W-x          | U-0                                                        | U-0           | U-0           | R/W-x        | R/W-0         | R/S-0         | R/S-0     |  |  |  |  |  |

|         | EEPGD          | _                                                          | —             | _             | WRERR        | WREN          | WR            | RD        |  |  |  |  |  |

|         | bit 7          |                                                            |               |               |              |               |               | bit 0     |  |  |  |  |  |

|         |                |                                                            |               |               |              |               |               |           |  |  |  |  |  |

| bit 7   | EEPGD: Pr      | ogram/Data                                                 | a EEPROM S    | Select bit    |              |               |               |           |  |  |  |  |  |

|         |                | es Program                                                 |               |               |              |               |               |           |  |  |  |  |  |

|         |                | es data mei                                                |               | a read or wri | to operation | ie in progra  |               |           |  |  |  |  |  |

| bit 6-4 | •              |                                                            | •             |               |              | ris in piogre |               |           |  |  |  |  |  |

| bit 3   | •              | Inimplemented: Read as '0'<br>VRERR: EEPROM Error Flag bit |               |               |              |               |               |           |  |  |  |  |  |

| DIT 5   |                | = A write operation is prematurely terminated              |               |               |              |               |               |           |  |  |  |  |  |

|         |                | (any MCLR Reset or any WDT Reset during normal operation)  |               |               |              |               |               |           |  |  |  |  |  |

|         | • •            | 0 = The write operation completed                          |               |               |              |               |               |           |  |  |  |  |  |

| bit 2   | WREN: EE       | PROM Writ                                                  | e Enable bit  |               |              |               |               |           |  |  |  |  |  |

|         |                | write cycles                                               |               |               |              |               |               |           |  |  |  |  |  |

|         |                | write to the                                               | EEPROM        |               |              |               |               |           |  |  |  |  |  |

| bit 1   | WR: Write      |                                                            |               |               |              |               |               |           |  |  |  |  |  |

|         |                | -                                                          | •             | s cleared by  | hardware o   | nce write is  | complete. T   | he WR bit |  |  |  |  |  |

|         |                | •                                                          | t cleared) in |               |              |               |               |           |  |  |  |  |  |

| bit 0   | RD: Read (     | •                                                          |               |               |              |               |               |           |  |  |  |  |  |

|         | 1 = Initiates  | an EEPRC                                                   | DM read RD    | is cleared in | hardware.    | The RD bit o  | can only be a | set (not  |  |  |  |  |  |

|         |                | ) in software                                              |               |               |              |               |               | ,         |  |  |  |  |  |

|         | 0 = Does n     | ot initiate ar                                             | EEPROM I      | read          |              |               |               |           |  |  |  |  |  |

|         |                |                                                            |               |               |              |               |               |           |  |  |  |  |  |

|         | Legend:        |                                                            |               |               |              |               |               |           |  |  |  |  |  |

|         | S = Settable   |                                                            | -             | adable bit    |              | W = Writab    | le bit        |           |  |  |  |  |  |

|         | U = Unimple    | emented bit                                                | , read as '0' |               |              | - n = Value   | at POR        |           |  |  |  |  |  |

|         | '1' = Bit is s | et                                                         | '0' = Bi      | t is cleared  |              | x = Bit is ur | Iknown        |           |  |  |  |  |  |

|         |                |                                                            |               |               |              |               |               |           |  |  |  |  |  |

| Name    | Bit# | Buffer                | Function                                                                                                                                          |

|---------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/INT | bit0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up.                                                        |

| RB1     | bit1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                                                    |

| RB2     | bit2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                                                    |

| RB3/PGM | bit3 | TTL                   | Input/output pin or programming pin in LVP mode.<br>Internal software programmable weak pull-up.                                                  |

| RB4     | bit4 | TTL                   | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up.                                                      |

| RB5     | bit5 | TTL                   | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up.                                                      |

| RB6/PGC | bit6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change) or In-Circuit Debugger pin.<br>Internal software programmable weak pull-up. Serial programming clock. |

| RB7/PGD | bit7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change) or In-Circuit Debugger pin.<br>Internal software programmable weak pull-up. Serial programming data.  |

#### TABLE 4-3: PORTB FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

#### TABLE 4-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address   | Name       | Bit 7 | Bit 6                         | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|-----------|------------|-------|-------------------------------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 06h, 106h | PORTB      | RB7   | RB6                           | RB5   | RB4   | RB3   | RB2   | RB1   | RB0   | XXXX XXXX                | uuuu uuuu                       |

| 86h, 186h | TRISB      | PORTB | PORTB Data Direction Register |       |       |       |       |       |       | 1111 1111                | 1111 1111                       |

| 81h, 181h | OPTION_REG | RBPU  | INTEDG                        | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                | 1111 1111                       |

Legend:  $\mathbf{x}$  = unknown,  $\mathbf{u}$  = unchanged. Shaded cells are not used by PORTB.

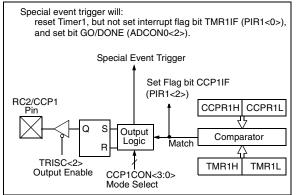

## 8.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 pin is:

- Driven high

- Driven low

- · Remains unchanged

The action on the pin is based on the value of control bits, CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

#### FIGURE 8-2: COMPARE MODE OPERATION BLOCK DIAGRAM

#### 8.2.1 CCP PIN CONFIGURATION

The user must configure the RC2/CCP1 pin as an output by clearing the TRISC<2> bit.

| Note: | Clearing the CCP1CON register will force |  |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|--|

|       | the RC2/CCP1 compare output latch to the |  |  |  |  |  |  |  |

|       | default low level. This is not the PORTC |  |  |  |  |  |  |  |

|       | I/O data latch.                          |  |  |  |  |  |  |  |

#### 8.2.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

## 8.2.3 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt mode is chosen, the CCP1 pin is not affected. The CCPIF bit is set, causing a CCP interrupt (if enabled).

#### 8.2.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated, which may be used to initiate an action.

The special event trigger output of CCP1 resets the TMR1 register pair and starts an A/D conversion (if the A/D module is enabled). This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

**Note:** The special event trigger from the CCP module will not set interrupt flag bit TMR1IF (PIR1<0>).

#### TABLE 8-2: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, AND TIMER1

| Address                | Name    | Bit 7   | Bit 6                               | Bit 5         | Bit 4         | Bit 3          | Bit 2        | Bit 1      | Bit 0  | Value<br>PO<br>BC | R,   | all o | e on<br>other<br>SETS |

|------------------------|---------|---------|-------------------------------------|---------------|---------------|----------------|--------------|------------|--------|-------------------|------|-------|-----------------------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON  | GIE     | PEIE                                | TMR0IE        | INTE          | RBIE           | TMR0IF       | INTF       | RBIF   | 0000              | 000x | 0000  | 000u                  |

| 0Ch                    | PIR1    | (1)     | ADIF                                | (1)           | (1)           | SSPIF          | CCP1IF       | TMR2IF     | TMR1IF | r0rr              | 0000 | 0000  | 0000                  |

| 8Ch                    | PIE1    | (1)     | ADIE                                | (1)           | (1)           | SSPIE          | CCP1IE       | TMR2IE     | TMR1IE | r0rr              | 0000 | 0000  | 0000                  |

| 87h                    | TRISC   | PORTC   | Data Di                             | rection Reg   | ister         |                |              |            |        | 1111              | 1111 | 1111  | 1111                  |

| 0Eh                    | TMR1L   | Holding | Registe                             | r for the Lea | ast Significa | nt Byte of th  | ie 16-bit Tl | MR1 Regis  | ster   | xxxx              | xxxx | uuuu  | uuuu                  |

| 0Fh                    | TMR1H   | Holding | Registe                             | r for the Mo  | st Significar | nt Byte of the | e 16-bit TN  | /IR1 Regis | ter    | xxxx              | xxxx | uuuu  | uuuu                  |

| 10h                    | T1CON   | —       | —                                   | T1CKPS1       | T1CKPS0       | T1OSCEN        | T1SYNC       | TMR1CS     | TMR10N | 00                | 0000 | uu    | uuuu                  |

| 15h                    | CCPR1L  | Capture | /Compa                              | re/PWM Re     | gister1 (LSE  | 3)             |              |            |        | xxxx              | xxxx | uuuu  | uuuu                  |

| 16h                    | CCPR1H  | Capture | Capture/Compare/PWM Register1 (MSB) |               |               |                |              |            |        |                   | xxxx | uuuu  | uuuu                  |

| 17h                    | CCP1CON | _       | _                                   | CCP1X         | CCP1Y         | CCP1M3         | CCP1M2       | CCP1M1     | CCP1M0 | 00                | 0000 | 00    | 0000                  |

Note 1: These bits are reserved; always maintain clear.

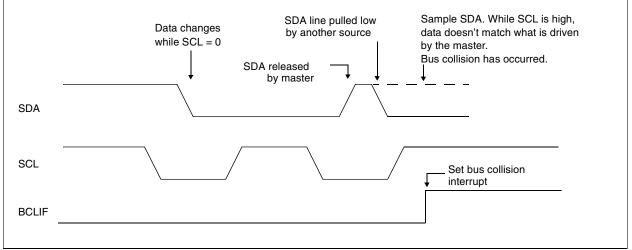

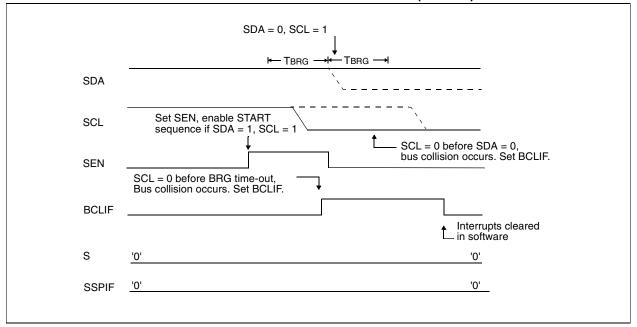

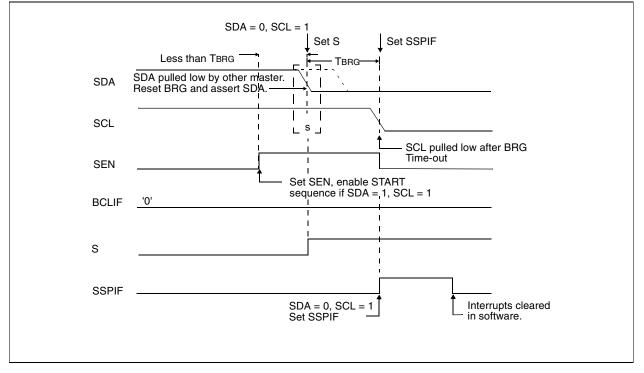

#### 9.2.18 MULTI -MASTER COMMUNICATION, BUS COLLISION, AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA, by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin = '0', a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLIF and reset the  $I^2C$ port to its IDLE state. (Figure 9-19).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are de-asserted, and the SSPBUF can be written to. When the user services the bus collision Interrupt Service Routine, and if the  $I^2C$  bus is free, the user can resume communication by asserting a START condition.

If a START, Repeated START, STOP or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are de-asserted, and the respective control bits in the SSPCON2 register are cleared. When the user services the bus collision Interrupt Service Routine, and if the  $l^2C$  bus is free, the user can resume communication by asserting a START condition.

The master will continue to monitor the SDA and SCL pins, and if a STOP condition occurs, the SSPIF bit will be set.

A write to the SSPBUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of START and STOP conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPSTAT register, or the bus is IDLE and the S and P bits are cleared.

## 9.3 Connection Considerations for I<sup>2</sup>C Bus

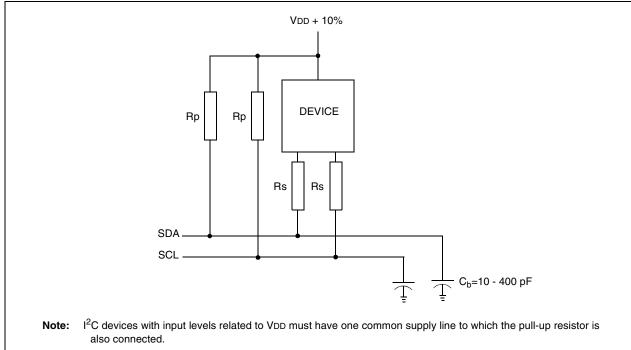

For standard mode  $I^2C$  bus devices, the values of resistors  $R_p$  and  $R_s$  in Figure 9-27 depend on the following parameters:

- Supply voltage

- Bus capacitance

- Number of connected devices (input current + leakage current).

The supply voltage limits the minimum value of resistor  $R_p$ , due to the specified minimum sink current of 3 mA at VoL max = 0.4V, for the specified output stages. For example, with a supply voltage of VDD =  $5V\pm10\%$  and

VoL max = 0.4V at 3 mA,  $R_{p \text{ min}} = (5.5-0.4)/0.003 = 1.7 \text{ k}\Omega$ . VDD, as a function of  $R_p$ , is shown in Figure 9-27. The desired noise margin of 0.1 VDD for the low level limits the maximum value of  $R_s$ . Series resistors are optional and used to improve ESD susceptibility.

The bus capacitance is the total capacitance of wire, connections, and pins. This capacitance limits the maximum value of  $R_{p}$ , due to the specified rise time (Figure 9-27).

The SMP bit is the slew rate control enabled bit. This bit is in the SSPSTAT register, and controls the slew rate of the I/O pins when in  $I^2C$  mode (master or slave).

## FIGURE 9-27: SAMPLE DEVICE CONFIGURATION FOR I<sup>2</sup>C BUS

# PIC16F872

#### REGISTER 10-2: ADCON1 REGISTER (ADDRESS: 9Fh)

|   | U-0   | U-0 | R/W-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|---|-------|-----|-------|-----|-------|-------|-------|-------|

|   | ADFM  | —   | —     | —   | PCFG3 | PCFG2 | PCFG1 | PCFG0 |

| k | oit 7 |     |       |     |       |       |       | bit 0 |

bit 7 ADFM: A/D Result Format Select bit

1 = Right justified. Six Most Significant bits of ADRESH are read as '0'.

0 = Left justified. Six Least Significant bits of ADRESL are read as '0'.

#### bit 6-4 Unimplemented: Read as '0'

| bit 3-0 | PCFG3:PCFG0: | A/D Port | Configuration | Control bits: |

|---------|--------------|----------|---------------|---------------|

|         |              |          |               |               |

| PCFG3:<br>PCFG0 | AN4<br>RA5 | AN3<br>RA3 | AN2<br>RA2 | AN1<br>RA1 | AN0<br>RA0 | VREF+ | VREF- | CHAN/<br>Refs <sup>(1)</sup> |

|-----------------|------------|------------|------------|------------|------------|-------|-------|------------------------------|

| 0000            | А          | А          | Α          | Α          | Α          | Vdd   | Vss   | 8/0                          |

| 0001            | А          | VREF+      | Α          | Α          | Α          | RA3   | Vss   | 7/1                          |

| 0010            | А          | А          | Α          | Α          | Α          | Vdd   | Vss   | 5/0                          |

| 0011            | А          | VREF+      | А          | А          | Α          | RA3   | Vss   | 4/1                          |

| 0100            | D          | А          | D          | А          | Α          | Vdd   | Vss   | 3/0                          |

| 0101            | D          | VREF+      | D          | Α          | Α          | RA3   | Vss   | 2/1                          |

| 011x            | D          | D          | D          | D          | D          | Vdd   | Vss   | 0/0                          |

| 1000            | А          | VREF+      | VREF-      | А          | Α          | RA3   | RA2   | 6/2                          |

| 1001            | А          | А          | А          | А          | Α          | Vdd   | Vss   | 6/0                          |

| 1010            | А          | VREF+      | А          | А          | Α          | RA3   | Vss   | 5/1                          |

| 1011            | А          | VREF+      | VREF-      | А          | Α          | RA3   | RA2   | 4/2                          |

| 1100            | А          | VREF+      | VREF-      | Α          | Α          | RA3   | RA2   | 3/2                          |

| 1101            | D          | VREF+      | VREF-      | А          | Α          | RA3   | RA2   | 2/2                          |

| 1110            | D          | D          | D          | D          | А          | Vdd   | Vss   | 1/0                          |

| 1111            | D          | VREF+      | VREF-      | D          | Α          | RA3   | RA2   | 1/2                          |

A = Analog input

D = Digital I/O

**Note 1:** This column indicates the number of analog channels available as A/D inputs and the number of analog channels used as voltage reference inputs.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 10.2 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires a minimum 12TAD per 10-bit conversion. The source of the A/D conversion clock is software selected. The four possible options for TAD are:

- 2Tosc

- 8Tosc

- 32Tosc

- Internal A/D module RC oscillator (2-6 μs)

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time of 1.6  $\mu s.$

Table 10-1<br/>shows the resultant TAD times derived from the device operating frequencies and the<br/> A/D clock source selected.

# 10.3 Configuring Analog Port Pins

The ADCON1, and TRIS registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS2:CHS0 bits and the TRIS bits.

- Note 1: When reading the port register, any pin configured as an analog input channel will read as cleared (a low level). Pins configured as digital inputs will convert an analog input. Analog levels on a digitally configured input will not affect the conversion accuracy.

- 2: Analog levels on any pin that is defined as a digital input (including the AN7:AN0 pins), may cause the input buffer to consume current that is out of the device specifications.

## TABLE 10-1: TAD VS. MAXIMUM DEVICE OPERATING FREQUENCIES (STANDARD DEVICES (C))

| AD Clock S              |             |                          |  |  |

|-------------------------|-------------|--------------------------|--|--|

| Operation               | ADCS1:ADCS0 | Maximum Device Frequency |  |  |

| 2Tosc                   | 0 0         | 1.25 MHz                 |  |  |

| 8Tosc                   | 01          | 5 MHz                    |  |  |

| 32Tosc                  | 10          | 20 MHz                   |  |  |

| RC <sup>(1, 2, 3)</sup> | 11          | (Note 1)                 |  |  |

Note 1: The RC source has a typical TAD time of 4 µs, but can vary between 2-6 µs.

2: When the device frequencies are greater than 1 MHz, the RC A/D conversion clock source is only recommended for SLEEP operation.

3: For extended voltage devices (LC), please refer to the Electrical Characteristics (Sections 14.1 and 14.2).

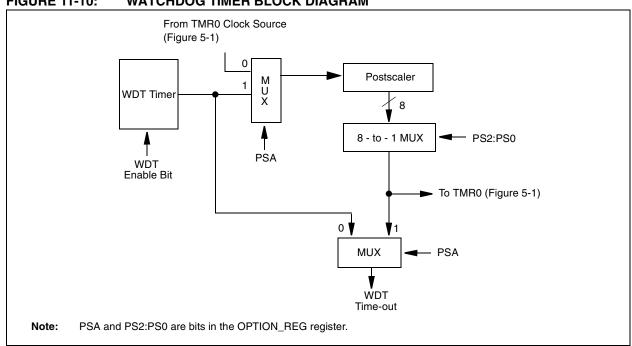

# 11.12 Watchdog Timer (WDT)

The Watchdog Timer is a free running on-chip RC oscillator, which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKI pin. That means that the WDT will run, even if the clock on the OSC1/CLKI and OSC2/CLKO pins of the device has been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT time-out generates a device RESET (Watchdog Timer Reset). If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The TO bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

The WDT can be permanently disabled by clearing configuration bit WDTE (Section 11.1).

WDT time-out period values may be found in the Electrical Specifications section under parameter #31. Values for the WDT prescaler (actually a postscaler, but shared with the Timer0 prescaler) may be assigned using the OPTION\_REG register.

- Note 1: The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET condition.

- 2: When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared, but the prescaler assignment is not changed.

## FIGURE 11-10: WATCHDOG TIMER BLOCK DIAGRAM

#### TABLE 11-7: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address  | Name         | Bit 7 | Bit 6                | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 |

|----------|--------------|-------|----------------------|-------|-------|----------------------|-------|-------|-------|

| 2007h    | Config. bits | (1)   | BODEN <sup>(1)</sup> | CP1   | CP0   | PWRTE <sup>(1)</sup> | WDTE  | FOSC1 | FOSC0 |

| 81h,181h | OPTION_REG   | RBPU  | INTEDG               | TOCS  | T0SE  | PSA                  | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

**Note 1:** See Register 11-1 for operation of these bits.

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                       |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                                                                                                                                                                                            |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                   |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                         |

| Description:     | The contents of register 'f' are<br>decremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'.<br>If the result is 1, the next instruc-<br>tion is executed. If the result is 0,<br>then a NOP is executed instead,<br>making it a 2TCY instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \\ (f) + 1 \rightarrow (destination), \\ skip \ if \ result = 0 \end{array}$                                                                                                                                                                                         |  |  |  |  |

| Operation:       |                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1,<br>the result is placed back in<br>register 'f'.<br>If the result is 1, the next instruc-<br>tion is executed. If the result is 0,<br>a NOP is executed instead, making<br>it a 2TCY instruction. |  |  |  |  |

| GOTO             | Unconditional Branch                                                                                                                                                                              |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                           |  |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                                |  |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                                   |  |

| Status Affected: | None                                                                                                                                                                                              |  |

| Description:     | GOTO is an unconditional branch.<br>The eleven-bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a two-<br>cycle instruction. |  |

| IORLW            | Inclusive OR Literal with W                                                                                               |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                                  |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                         |  |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                              |  |  |  |  |  |

| Status Affected: | Z                                                                                                                         |  |  |  |  |  |

| Description:     | The contents of the W register are<br>OR'ed with the eight-bit literal 'k'.<br>The result is placed in the W<br>register. |  |  |  |  |  |

| INCF                                                                                                                                                                                | Increment f                                                                | IORWF            | Inclusive OR W with f                                                                                                                                                   |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:                                                                                                                                                                             | [label] INCF f,d                                                           | Syntax:          | [ label ] IORWF f,d                                                                                                                                                     |  |

| Operands:                                                                                                                                                                           | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$ | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                                              |  |

| Operation:                                                                                                                                                                          | (f) + 1 $\rightarrow$ (destination)                                        | Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                                |  |

| Status Affected:                                                                                                                                                                    | Z                                                                          | Status Affected: | Z                                                                                                                                                                       |  |

| Description: The contents of register 'f' are<br>incremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'. |                                                                            | Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1,<br>the result is placed back in<br>register 'f'. |  |

## 13.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK object linker combines relocatable objects created by the MPASM assembler and the MPLAB C17 and MPLAB C18 C compilers. It can also link relocatable objects from pre-compiled libraries, using directives from a linker script.

The MPLIB object librarian is a librarian for precompiled code to be used with the MPLINK object linker. When a routine from a library is called from another source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications. The MPLIB object librarian manages the creation and modification of library files.

The MPLINK object linker features include:

- Integration with MPASM assembler and MPLAB C17 and MPLAB C18 C compilers.

- Allows all memory areas to be defined as sections to provide link-time flexibility.

The MPLIB object librarian features include:

- Easier linking because single libraries can be included instead of many smaller files.

- Helps keep code maintainable by grouping related modules together.

- Allows libraries to be created and modules to be added, listed, replaced, deleted or extracted.

#### 13.5 MPLAB SIM Software Simulator

The MPLAB SIM software simulator allows code development in a PC-hosted environment by simulating the PICmicro series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user-defined key press, to any of the pins. The execution can be performed in single step, execute until break, or trace mode.

The MPLAB SIM simulator fully supports symbolic debugging using the MPLAB C17 and the MPLAB C18 C compilers and the MPASM assembler. The software simulator offers the flexibility to develop and debug code outside of the laboratory environment, making it an excellent multiproject software development tool.

## 13.6 MPLAB ICE High Performance Universal In-Circuit Emulator with MPLAB IDE

The MPLAB ICE universal in-circuit emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PICmicro microcontrollers (MCUs). Software control of the MPLAB ICE in-circuit emulator is provided by the MPLAB Integrated Development Environment (IDE), which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICE 2000 is a full-featured emulator system with enhanced trace, trigger and data monitoring features. Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB ICE in-circuit emulator allows expansion to support new PICmicro microcontrollers.

The MPLAB ICE in-circuit emulator system has been designed as a real-time emulation system, with advanced features that are generally found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows environment were chosen to best make these features available to you, the end user.

## 13.7 ICEPIC In-Circuit Emulator

The ICEPIC low cost, in-circuit emulator is a solution for the Microchip Technology PIC16C5X, PIC16C6X, PIC16C7X and PIC16CXXX families of 8-bit One-Time-Programmable (OTP) microcontrollers. The modular system can support different subsets of PIC16C5X or PIC16CXXX products through the use of interchangeable personality modules, or daughter boards. The emulator is capable of emulating without target application circuitry being present.

## 13.8 MPLAB ICD In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD, is a powerful, low cost, run-time development tool. This tool is based on the FLASH PICmicro MCUs and can be used to develop for this and other PICmicro microcontrollers. The MPLAB ICD utilizes the in-circuit debugging capability built into the FLASH devices. This feature, along with Microchip's In-Circuit Serial Programming<sup>™</sup> protocol, offers cost-effective in-circuit FLASH debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by watching variables, single-stepping and setting break points. Running at full speed enables testing hardware in realtime.

## 13.9 PRO MATE II Universal Device Programmer

The PRO MATE II universal device programmer is a full-featured programmer, capable of operating in stand-alone mode, as well as PC-hosted mode. The PRO MATE II device programmer is CE compliant.

The PRO MATE II device programmer has programmable VDD and VPP supplies, which allow it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for instructions and error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In stand-alone mode, the PRO MATE II device programmer can read, verify, or program PICmicro devices. It can also set code protection in this mode.

## 13.10 PICSTART Plus Entry Level Development Programmer

The PICSTART Plus development programmer is an easy-to-use, low cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient.

The PICSTART Plus development programmer supports all PICmicro devices with up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus development programmer is CE compliant.

## 13.11 PICDEM 1 Low Cost PICmicro Demonstration Board

The PICDEM 1 demonstration board is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44, All necessary hardware and software is included to run basic demo programs. The user can program the sample microcontrollers provided with the PICDEM 1 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The user can also connect the PICDEM 1 demonstration board to the MPLAB ICE incircuit emulator and download the firmware to the emulator for testing. A prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push button switches and eight LEDs connected to PORTB.

## 13.12 PICDEM 2 Low Cost PIC16CXX Demonstration Board

The PICDEM 2 demonstration board is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM 2 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The MPLAB ICE in-circuit emulator may also be used with the PICDEM 2 demonstration board to test firmware. A prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push button switches, a potentiometer for simulated analog input, a serial EEPROM to demonstrate usage of the I<sup>2</sup>C<sup>™</sup> bus and separate headers for connection to an LCD module and a keypad.

# PIC16F872

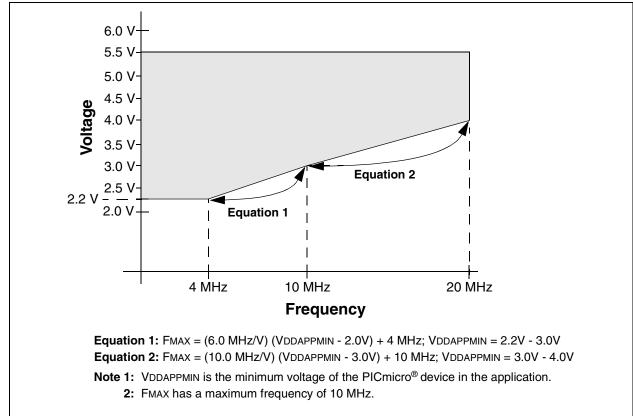

FIGURE 14-2: PIC16LF872 VOLTAGE-FREQUENCY GRAPH

## 14.4 DC Characteristics: PIC16F872 (Extended)

| DC CHARACTERISTICS |       | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$<br>Operating voltage VDD range as described in DC specification<br>(Section 14.1) |                   |      |         |       |                                                             |

|--------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------|---------|-------|-------------------------------------------------------------|

| Param<br>No.       | Sym   | Characteristic                                                                                                                                                                                             | Min Typ           | Тур† | /p† Max | Units | Conditions                                                  |

|                    | VIL   | Input Low Voltage                                                                                                                                                                                          |                   |      |         |       |                                                             |

|                    |       | I/O ports:                                                                                                                                                                                                 |                   |      |         |       |                                                             |

| D030               |       | with TTL buffer                                                                                                                                                                                            | Vss               | -    | 0.15VDD | V     | For entire VDD range                                        |

| D030A              |       |                                                                                                                                                                                                            | Vss               | -    | 0.8V    | V     | $4.5V \le VDD \le 5.5V$                                     |

| D031               |       | with Schmitt Trigger buffer                                                                                                                                                                                | Vss               | -    | 0.2Vdd  | V     |                                                             |

| D032               |       | MCLR, OSC1 (in RC mode)                                                                                                                                                                                    | Vss               | -    | 0.2VDD  | V     |                                                             |

| D033               |       | OSC1 (in XT, HS and LP modes)                                                                                                                                                                              | Vss               | -    | 0.3VDD  | V     | (Note1)                                                     |

|                    |       | Ports RC3 and RC4:                                                                                                                                                                                         |                   |      |         |       |                                                             |

| D034               |       | with Schmitt Trigger buffer                                                                                                                                                                                | Vss               | -    | 0.3VDD  | V     | For entire VDD range                                        |

| D034A              |       | with SMBus                                                                                                                                                                                                 | -0.5              | -    | 0.6     | V     | for VDD = 4.5 to 5.5V                                       |

|                    | VIH   | Input High Voltage                                                                                                                                                                                         |                   |      |         |       |                                                             |

|                    |       | I/O ports:                                                                                                                                                                                                 |                   | -    |         |       |                                                             |

| D040               |       | with TTL buffer                                                                                                                                                                                            | 2.0               | -    | Vdd     | V     | $4.5V \le VDD \le 5.5V$                                     |

| D040A              |       |                                                                                                                                                                                                            | 0.25Vdd<br>+ 0.8V | -    | Vdd     | V     | For entire VDD range                                        |

| D041               |       | with Schmitt Trigger buffer                                                                                                                                                                                | 0.8VDD            | -    | Vdd     | V     | For entire VDD range                                        |

| D042               |       | MCLR                                                                                                                                                                                                       | 0.8VDD            | -    | Vdd     | V     |                                                             |

| D042A              |       | OSC1 (XT, HS and LP modes)                                                                                                                                                                                 | 0.7Vdd            | -    | Vdd     | V     | (Note1)                                                     |

| D043               |       | OSC1 (in RC mode)                                                                                                                                                                                          | 0.9Vdd            | -    | Vdd     | V     |                                                             |

|                    |       | Ports RC3 and RC4:                                                                                                                                                                                         |                   |      |         |       |                                                             |

| D044               |       | with Schmitt Trigger buffer                                                                                                                                                                                | 0.7Vdd            | -    | Vdd     | V     | For entire VDD range                                        |

| D044A              |       | with SMBus                                                                                                                                                                                                 | 1.4               | -    | 5.5     | V     | for VDD = 4.5 to 5.5V                                       |

| D070A              | IPURB | PORTB Weak Pull-up Current                                                                                                                                                                                 | 50                | 300  | 500     | μΑ    | VDD = 5V, $VPIN = VSS$ ,                                    |

|                    | lı∟   | Input Leakage Current <sup>(2, 3)</sup>                                                                                                                                                                    |                   |      |         |       |                                                             |

| D060               |       | I/O ports                                                                                                                                                                                                  | -                 | -    | ±1      | μA    | $Vss \leq VPIN \leq VDD$ ,                                  |

|                    |       |                                                                                                                                                                                                            |                   |      |         |       | Pin at hi-impedance                                         |

| D061               |       | MCLR, RA4/T0CKI                                                                                                                                                                                            | -                 | -    | ±5      | μA    | $Vss \le VPIN \le VDD$                                      |

| D063               |       | OSC1                                                                                                                                                                                                       | -                 | -    | ±5      | μA    | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP osc configuration |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16F872 be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

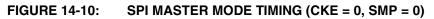

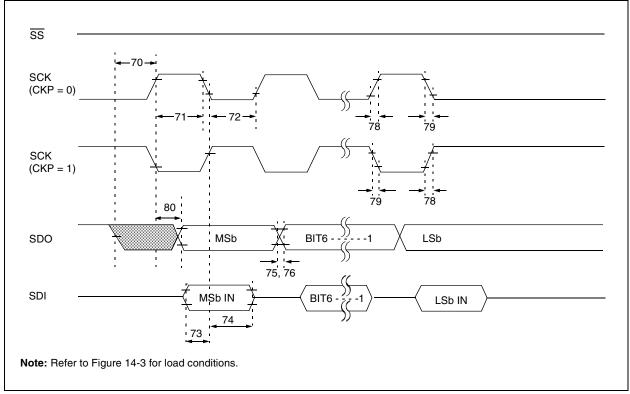

## FIGURE 14-11: SPI MASTER MODE TIMING (CKE = 1, SMP = 1)

NOTES:

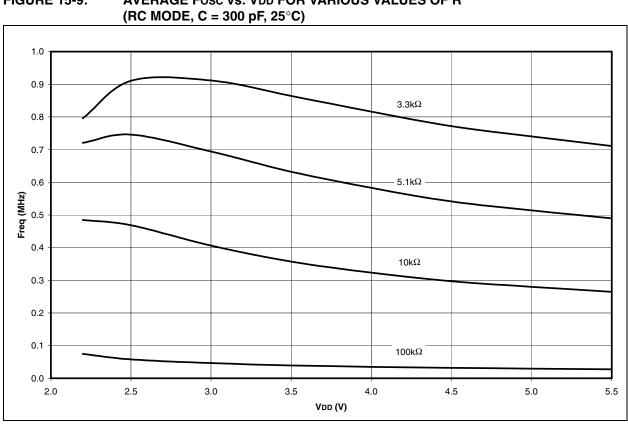

AVERAGE FOSC vs. VDD FOR VARIOUS VALUES OF R **FIGURE 15-9:**

© 2006 Microchip Technology Inc.

NOTES:

# INDEX

| A/D       79         Acquisition Requirements       82         ADCON0 Register       79         ADCON1 Register       79         ADIF Bit       81         ADRESH Register       79         ADRESH Register       83         Configuring the Module       81         Conversion Clock       83         Conversion Succk       84         Effects of a RESET       85         GO/DONE Bit       81         Internal Sampling Switch (Rss) Impedance       82         Operation During SLEEP       85         Result Registers       84         Source Impedance       82         TaD       83         Acknowledge Data Bit (ACKDT)       54         Acknowledge Sequence Enable Bit (ACKEN)       54         Acknowledge Status Bit (ACKSTAT)       54         ACKSTAT Status Flag       79                                                                                                                                                                                   | Α                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| ADCON0 Register         79           ADCN1 Register         79           ADIF Bit         81           ADRESH Register         79           ADRESL Register         79           ADRESL Register         79           ADRESL Register         79           Associated Registers and Bits         85           Configuring the Interrupt         81           Configuring the Module         81           Conversion Clock         83           Conversion S         84           Effects of a RESET         85           GO/DONE Bit         81           Internal Sampling Switch (Rss) Impedance         82           Operation During SLEEP         85           Result Registers         84           Source Impedance         82           ACKD Bit         Acknowledge Sequence Enable Bit (ACKEN)           ACKNowledge Sequence Enable Bit (ACKSTAT)         5                                                                                                     | A/D79                          |

| ADCON1 Register         79           ADIF Bit         81           ADRESH Register         79           ADRESL Register         79           Associated Registers and Bits         85           Configuring Analog Port Pins         83           Configuring the Interrupt         81           Configuring the Module         81           Conversion Clock         83           Conversion S         84           Effects of a RESET         85           GO/DONE Bit         81           Internal Sampling Switch (Rss) Impedance         82           Operation During SLEEP         85           Result Registers         84           Source Impedance         82           TaD         83           Acknowledge Data Bit (ACKDT)         54           Acknowledge Data Bit (ACKDT)         54           Acknowledge Sequence Enable Bit (ACKEN)         54           Acknowledge Status Bit (ACKSTAT)         54           AcKNowledge Pulse (ACK)         59           ADCON1 Register         9           ADESH Register         9           ADESH Register         9           ADESH Register         10           Analog-to-Digital Converte                                                                                            | Acquisition Requirements82     |

| ADIF Bit       81         ADRESH Register       79         ADRESL Registers and Bits       85         Configuring the Interrupt       81         Configuring the Module       81         Conversion       83         Conversions       84         Effects of a RESET       85         GO/DONE Bit       81         Internal Sampling Switch (Rss) Impedance       82         Operation During SLEEP       85         Result Registers       84         Source Impedance       82         TAD       83         Acknowledge Data Bit (ACKDT)       54         Acknowledge Data Bit (ACKDT)       54         Acknowledge Status Bit (ACKSTAT)       54         Acknowledge Status Bit (ACKSTAT)       54         Acknowledge Status Bit (ACKSTAT)       54         ACKSTAT Status Flag       67         ADCON0 Register       9         ADCON1 Register       10         Anleg-to-Digital Converter. See A/D         <                                                                                                                                                             | ADCON0 Register                |

| ADRESL Register       79         ADRESL Register       79         Associated Registers and Bits       85         Configuring Analog Port Pins       83         Configuring the Interrupt       81         Conversion Clock       83         GO/DONE Bit       81         Internal Sampling Switch (Rss) Impedance       82         Operation During SLEEP       85         Result Registers       84         Source Impedance       82         TAD       83         Acknowledge Data Bit (ACKDT)       54         Acknowledge Pulse (ACK)       59         Acknowledge Sequence Enable Bit (ACKEN)       54         Acknowledge Status Bit (ACKSTAT)       54         ACKSTAT Status Flag       67         ADCON1 Register       9         ADRESL Register       10         AN552 (Implementing Wake-up on Key Stroke)                                                                                                                                                   | ADCON1 Register79              |

| ADRESL Register       79         Associated Registers and Bits       85         Configuring Analog Port Pins       83         Configuring the Interrupt       81         Conversion Clock       83         Conversion S       84         Effects of a RESET       85         GO/DONE Bit       81         Internal Sampling Switch (Rss) Impedance       82         Operation During SLEEP       85         Result Registers       84         Source Impedance       82         TAD       83         Absolute Maximum Ratings       117         ACK pulse       59         ACKDT Bit       54         Acknowledge Data Bit (ACKDT)       54         ACKNT Bit       54         Acknowledge Sequence Enable Bit (ACKEN)       54         ACKNTAT Bit       54         ACKNTAT Status Flag       67         ADCON1 Register       9         ADCON1 Register       9         ADCON1 Register       10         ADRESL Register       9         ADCON1 Register       10         ADRESL Register       9         ADCON1 Register       10         AN526 (Implementing a Table Re                                                                                                                                                                          |                                |

| Associated Registers and Bits       85         Configuring Analog Port Pins       83         Configuring the Interrupt       81         Conversion Clock       83         Conversion Clock       83         Conversion Clock       83         Conversion S       84         Effects of a RESET       85         GO/DONE Bit       81         Internal Sampling Switch (Rss) Impedance       82         Operation During SLEEP       85         Result Registers       84         Source Impedance       82         TAD       83         Absolute Maximum Ratings       117         ACK pulse       59         ACKDT Bit       54         Acknowledge Data Bit (ACKDT)       54         Acknowledge Sequence Enable Bit (ACKEN)       54         Acknowledge Status Bit (ACKSTAT)       54         ACKSTAT Bit       Acknowledge Status Flag       67         ADCON1 Register       9       ADCON1 Register       9         ADCON1 Register       10       Analog-to-Digital Converter. See A/D       20         AN552 (Implementing Wake-up on Key Stroke)       31       AN556 (Implementing a Table Read)       20         AN578 (Use of the SSP Modul                                                                                             | •                              |

| Configuring Analog Port Pins         83           Configuring the Interrupt         81           Configuring the Module         81           Conversion Clock         83           Conversions         84           Effects of a RESET         85           GO/DONE Bit         81           Internal Sampling Switch (Rss) Impedance         82           Operation During SLEEP         85           Result Registers         84           Source Impedance         82           TAD         83           Absolute Maximum Ratings         117           ACK pulse         59           ACKDT Bit         Acknowledge Data Bit (ACKDT)           AcKnowledge Sequence Enable Bit (ACKEN)         54           Acknowledge Pulse (ACK)         59           ACKSTAT Bit         Acknowledge Status Bit (ACKSTAT)           ACKSTAT Status Flag         67           ADCON0 Register         9           ADCON1 Register         10           ADRESH Register         9           ADCON1 Register         10           Analog-to-Digital Converter. See A/D           Application Notes         AN556 (Implementing Wake-up on Key Stroke)           AN578 (Use of the SSP Module in the I <sup>2</sup> C                                            |                                |

| Configuring the Interrupt         81           Configuring the Module         81           Conversion Clock         83           Conversion Clock         83           Conversions         84           Effects of a RESET         84           GO/DONE Bit         81           Internal Sampling Switch (Rss) Impedance         82           Operation During SLEEP         85           Result Registers         84           Source Impedance         82           TAD         83           Absolute Maximum Ratings         117           ACK pulse         59           ACKDT Bit         Acknowledge Data Bit (ACKDT)           ACKEN Bit         Acknowledge Sequence Enable Bit (ACKEN)           ACKSTAT Bit         Acknowledge Status Bit (ACKSTAT)           ACKSTAT Status Flag         67           ADCON0 Register         9           ADCON1 Register         10           ADRESL Register         9           ADCON1 Register         10           Analog-to-Digital Converter. See A/D           Application Notes         AN552 (Implementing Wake-up on Key Stroke)           AN578 (Use of the SSP Module in the I <sup>2</sup> C           Multi-Master Environment)         58                                               | •                              |

| Configuring the Module         81           Conversion Clock         83           GO/DONE Bit         85           Internal Sampling Switch (Rss) Impedance         82           Operation During SLEEP         85           Result Registers         84           Source Impedance         82           TAD         83           Absolute Maximum Ratings         117           ACK pulse         59           ACKDT Bit         54           Acknowledge Data Bit (ACKDT)         54           Acknowledge Sequence Enable Bit (ACKEN)         54           Acknowledge Status Bit (ACKSTAT)         54           ACKSTAT Bit         Acknowledge Status Flag         67           ADCON Register         9         ADCON Register         9           ADRESL Register         10         Anlaog-to-Digital Converter. See A/D         Application Notes           AN556 (Implementing a Table Read)         20         AN578 (Use of the SSP Module in the I                                                  |                                |

| Conversion Clock         83           Conversions         84           Effects of a RESET         85           GO/DONE Bit         81           Internal Sampling Switch (Rss) Impedance         82           Operation During SLEEP         85           Result Registers         84           Source Impedance         82           TAD         83           Absolute Maximum Ratings         117           ACK pulse         59           ACKDT Bit         Acknowledge Data Bit (ACKDT)           ACKEN Bit         Acknowledge Sequence Enable Bit (ACKEN)           ACKSTAT Bit         Acknowledge Status Bit (ACKSTAT)           ACKSTAT Status Flag         67           ADCON Register         9           ADCON Register         9           ADCON Register         9           ADCON Register         10           Analog-to-Digital Converter. See A/D         Application Notes           AN552 (Implementing Wake-up on Key Stroke)         31           AN5532 (Implementing a Table Read)         20           AN578 (Use of the SSP Module in the I <sup>2</sup> C         Multi-Master Environment)           Assembler         111           B         Batifer Full Status Bit (BF)         52                                   |                                |

| Conversions         84           Effects of a RESET         85           GO/DONE Bit         81           Internal Sampling Switch (Rss) Impedance         82           Operation During SLEEP         85           Result Registers         84           Source Impedance         82           TAD         83           Absolute Maximum Ratings         117           ACK pulse         59           ACKDT Bit         Acknowledge Data Bit (ACKDT)           Acknowledge Sequence Enable Bit (ACKEN)         54           Acknowledge Status Bit (ACKSTAT)         54           ACKSTAT Bit         Acknowledge Status Bit (ACKSTAT)           ACKSTAT Status Flag         67           ADCON1 Register         9           ADCON1 Register         10           ADRESL Register         9           ADRESL Register         10           Analog-to-Digital Converter. See A/D         20           AN552 (Implementing Wake-up on Key Stroke)         31           AN552 (Implementing a Table Read)         20           AN578 (Use of the SSP Module in the I <sup>2</sup> C         Multi-Master Environment)           MPASM Assembler         111           B         Buffer Full Status Bit (BF)         52 <td></td>                      |                                |

| Effects of a RESET       85         GO/DONE Bit       81         Internal Sampling Switch (Rss) Impedance       82         Operation During SLEEP       85         Result Registers       84         Source Impedance       82         TAD       83         Absolute Maximum Ratings       117         ACK pulse       59         ACKDT Bit       54         Acknowledge Data Bit (ACKDT)       54         Acknowledge Sequence Enable Bit (ACKEN)       54         Acknowledge Pulse (ACK)       59         ACKSTAT Bit       67         Acknowledge Status Bit (ACKSTAT)       54         ACKSTAT Status Flag       67         ADCON1 Register       9         ADESH Register       10         Analog-to-Digital Converter. See A/D       Application Notes         AN552 (Implementing Wake-up on Key Stroke)       31         AN552 (Implementing a Table Read)       20         AN578 (Use of the SSP Module in the I <sup>2</sup> C       Multi-Master Environment)         MPASM Assembler       111         B       8         Banking, Data Memory       7         BCLIF Bit       18         BF Bit       Buffer Full Status Bit (BF)                                                                                                       |                                |

| GO/DONE Bit         81           Internal Sampling Switch (Rss) Impedance         82           Operation During SLEEP         85           Result Registers         84           Source Impedance         82           TAD         83           Absolute Maximum Ratings         117           ACK pulse         59           ACKDT Bit         54           Acknowledge Data Bit (ACKDT)         54           ACKEN Bit         Acknowledge Sequence Enable Bit (ACKEN)           ACKSTAT Bit         67           Acknowledge Status Bit (ACKSTAT)         54           Acknowledge Status Bit (ACKSTAT)         54           ACKSTAT Status Flag         67           ADCON0 Register         9           ADCON1 Register         10           ADRESL Register         10           ADRESL Register         10           Analog-to-Digital Converter. See A/D         31           AN552 (Implementing Wake-up on Key Stroke)         31           AN553 (Use of the SSP Module in the I <sup>2</sup> C         Multi-Master Environment)           ANS78 (Use of the SSP Module in the I <sup>2</sup> C         Multi-Master Environment)           ASB         Sasembler         111           B         Banking, Data Memory<                  |                                |

| Internal Sampling Switch (Rss) Impedance         82           Operation During SLEEP         85           Result Registers         84           Source Impedance         82           TAD         83           Absolute Maximum Ratings         117           ACK pulse         59           ACKDT Bit         54           Acknowledge Data Bit (ACKDT)         54           ACKEN Bit         54           Acknowledge Valse (ACK)         59           ACKSTAT Bit         54           Acknowledge Status Bit (ACKSTAT)         54           ACKSTAT Status Flag         67           ADCON1 Register         9           ADCON1 Register         9           ADCON1 Register         10           Analog-to-Digital Converter. See A/D         31           AN552 (Implementing Wake-up on Key Stroke)         31           AN556 (Implementing a Table Read)         20           AN578 (Use of the SSP Module in the I <sup>2</sup> C         Multi-Master Environment)           MPASM Assembler         111           B         Banking, Data Memory         7           BCLIF Bit         18           BF Bit         81           Budfer Full Status Bit (BF)         52 </td <td></td>                                                   |                                |