Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI                                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64 x 8                                                                   |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 5x10b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 28-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f872-i-so |

#### **Table of Contents**

| 1.0   | Device Overview                              | 3    |

|-------|----------------------------------------------|------|

| 2.0   | Memory Organization                          |      |

| 3.0   | Data EEPROM and FLASH Program Memory         | 23   |

| 4.0   | I/O Ports                                    | . 29 |

| 5.0   | Timer0 Module                                | . 35 |

| 6.0   | Timer1 Module                                | . 39 |

| 7.0   | Timer2 Module                                |      |

| 8.0   | Capture/Compare/PWM Module                   | 45   |

| 9.0   | Master Synchronous Serial Port (MSSP) Module |      |

| 10.0  | Analog-to-Digital Converter (A/D) Module     | . 79 |

| 11.0  | Special Features of the CPU                  | . 87 |

| 12.0  | Instruction Set Summary                      | 103  |

| 13.0  | Development Support                          | 111  |

| 14.0  | Electrical Characteristics                   | 117  |

| 15.0  | DC and AC Characteristics Graphs and Tables  |      |

| 16.0  | Packaging Information                        | 151  |

| Appe  | ndix A: Revision History                     | 155  |

| Appe  | ndix B: Conversion Considerations            | 155  |

| Index |                                              | 157  |

| On-Li | ine Support                                  | 163  |

| Read  | er Response                                  | 164  |

| PIC1  | 6F872 Product Identification System          | 165  |

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

#### 1.0 DEVICE OVERVIEW

This document contains device specific information about the PIC16F872 microcontroller. Additional information may be found in the PICmicro™ Mid-Range Reference Manual (DS33023), which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip website. The Reference Manual should be considered a complementary

document to this data sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

The block diagram of the PIC16F872 architecture is shown in Figure 1-1. A pinout description is provided in Table 1-2.

TABLE 1-1: KEY FEATURES OF THE PIC16F872

| Operating Frequency                 | DC - 20 MHz          |

|-------------------------------------|----------------------|

| RESETS (and Delays)                 | POR, BOR (PWRT, OST) |

| FLASH Program Memory (14-bit words) | 2K                   |

| Data Memory (bytes)                 | 128                  |

| EEPROM Data Memory (bytes)          | 64                   |

| Interrupts                          | 10                   |

| I/O Ports                           | Ports A, B, C        |

| Timers                              | 3                    |

| Capture/Compare/PWM module          | 1                    |

| Serial Communications               | MSSP                 |

| 10-bit Analog-to-Digital Module     | 5 input channels     |

| Instruction Set                     | 35 Instructions      |

| Packaging                           | 28-lead PDIP         |

|                                     | 28-lead SOIC         |

|                                     | 28-lead SSOP         |

#### 2.2.2.2 OPTION\_REG Register

The OPTION\_REG Register is a readable and writable register, which contains various control bits to configure the TMR0 prescaler/WDT postscaler (single assignable register known also as the prescaler), the External INT Interrupt, TMR0 and the weak pull-ups on PORTB.

**Note:** To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer.

#### REGISTER 2-2: OPTION\_REG REGISTER (ADDRESS 81h, 181h)

| R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|--------|-------|-------|-------|-------|-------|-------|

| RBPU  | INTEDG | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   |

| bit 7 |        |       |       |       |       |       | bit 0 |

bit 7 RBPU: PORTB Pull-up Enable bit

1 = PORTB pull-ups are disabled

0 = PORTB pull-ups are enabled by individual port latch values

bit 6 INTEDG: Interrupt Edge Select bit

1 = Interrupt on rising edge of RB0/INT pin

0 = Interrupt on falling edge of RB0/INT pin

bit 5 **T0CS**: TMR0 Clock Source Select bit

1 = Transition on RA4/T0CKI pin 0 = Internal instruction cycle clock (CLKOUT)

bit 4 T0SE: TMR0 Source Edge Select bit

1 = Increment on high-to-low transition on RA4/T0CKI pin

0 = Increment on low-to-high transition on RA4/T0CKI pin

bit 3 **PSA**: Prescaler Assignment bit

1 = Prescaler is assigned to the WDT

0 = Prescaler is assigned to the Timer0 module

bit 2-0 **PS2:PS0**: Prescaler Rate Select bits

| Bit Value                                     | TMR0 Rate                                                   | WDT Rate                                                  |

|-----------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------|

| 000<br>001<br>010<br>011<br>100<br>101<br>110 | 1:2<br>1:4<br>1:8<br>1:16<br>1:32<br>1:64<br>1:128<br>1:256 | 1:1<br>1:2<br>1:4<br>1:8<br>1:16<br>1:32<br>1:64<br>1:128 |

|                                               |                                                             |                                                           |

Legend:

$R = Readable \ bit$   $W = Writable \ bit$   $U = Unimplemented \ bit$ , read as '0'  $- n = Value \ at \ POR$  '1' = Bit is set '0' = Bit is cleared  $x = Bit \ is \ unknown$

**Note:** When using low voltage ICSP programming (LVP) and the pull-ups on PORTB are enabled, bit 3 in the TRISB register must be cleared to disable the pull-up on RB3 and ensure the proper operation of the device

Write operations have two control bits. WR and WREN. and two status bits, WRERR and EEIF. The WREN bit is used to enable or disable the write operation. When WREN is clear, the write operation will be disabled. Therefore, the WREN bit must be set before executing a write operation. The WR bit is used to initiate the write operation. It also is automatically cleared at the end of the write operation. The interrupt flag EEIF (located in register PIR2) is used to determine when the memory write completes. This flag must be cleared in software before setting the WR bit. For EEPROM Data memory, once the WREN bit and the WR bit have been set, the desired memory address in EEADR will be erased followed by a write of the data in EEDATA. This operation takes place in parallel with the microcontroller continuing to execute normally. When the write is complete, the EEIF flag bit will be set. For program memory, once the WREN bit and the WR bit have been set, the microcontroller will cease to execute instructions. The

desired memory location pointed to by EEADRH:EEADR will be erased. Then the data value in EEDATH:EEDATA will be programmed. When complete, the EEIF flag bit will be set and the microcontroller will continue to execute code.

The WRERR bit is used to indicate when the device has been RESET during a write operation. WRERR should be cleared after Power-on Reset. Thereafter, it should be checked on any other RESET. The WRERR bit is set when a write operation is interrupted by a MCLR Reset or a WDT Time-out Reset during normal operation. In these situations, following a RESET, the user should check the WRERR bit and rewrite the memory location if set. The contents of the data registers, address registers and EEPGD bit are not affected by either MCLR Reset or WDT Time-out Reset during normal operation.

#### REGISTER 3-1: EECON1 REGISTER (ADDRESS 18Ch)

| R/W-x | U-0 | U-0 | U-0 | R/W-x | R/W-0 | R/S-0 | R/S-0 |

|-------|-----|-----|-----|-------|-------|-------|-------|

| EEPGD | _   | _   | _   | WRERR | WREN  | WR    | RD    |

| bit 7 |     |     |     |       |       |       | bit 0 |

bit 7 **EEPGD**: Program/Data EEPROM Select bit

1 = Accesses Program memory

0 = Accesses data memory

(This bit cannot be changed while a read or write operation is in progress.)

bit 6-4 Unimplemented: Read as '0'

bit 3 WRERR: EEPROM Error Flag bit

1 = A write operation is prematurely terminated

(any MCLR Reset or any WDT Reset during normal operation)

0 = The write operation completed

bit 2 WREN: EEPROM Write Enable bit

1 = Allows write cycles

0 = Inhibits write to the EEPROM

bit 1 WR: Write Control bit

1 = Initiates a write cycle (The bit is cleared by hardware once write is complete. The WR bit can only be set (not cleared) in software.)

0 = Write cycle to the EEPROM is complete

bit 0 RD: Read Control bit

1 = Initiates an EEPROM read RD is cleared in hardware. The RD bit can only be set (not cleared) in software.

0 = Does not initiate an EEPROM read

Legend:

S = Settable bit R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR '1' = Bit is set '0' = Bit is cleared - n = Value at POR - n = Val

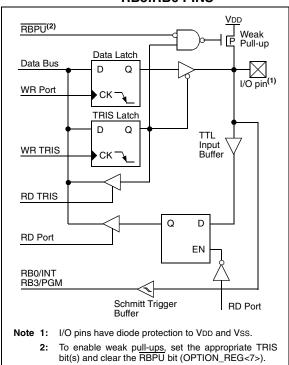

#### 4.2 PORTB and the TRISB Register

PORTB is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= '1') will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISB bit (= '0') will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

Three pins of PORTB are multiplexed with the Low Voltage Programming function; RB3/PGM, RB6/PGC and RB7/PGD. The alternate functions of these pins are described in the Special Features Section.

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

FIGURE 4-3: BLOCK DIAGRAM OF RB3:RB0 PINS

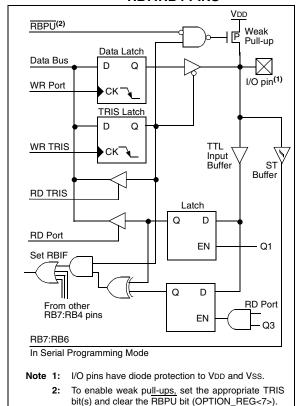

Four of the PORTB pins, RB7:RB4, have an interrupt-on-change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupt-on-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

This interrupt on mismatch feature, together with soft-ware configurable pull-ups on these four pins, allow easy interface to a keypad and make it possible for wake-up on key depression. Refer to the Embedded Control Handbook, "Implementing Wake-Up on Key Stroke" (AN552).

RB0/INT is an external interrupt input pin and is configured using the INTEDG bit (OPTION\_REG<6>).

RB0/INT is discussed in detail in Section 11.10.1.

FIGURE 4-4: BLOCK DIAGRAM OF RB7:RB4 PINS

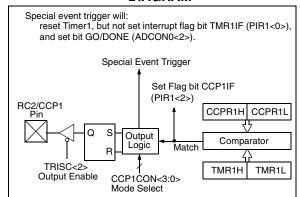

#### 8.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 pin is:

- · Driven high

- · Driven low

- · Remains unchanged

The action on the pin is based on the value of control bits, CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

# FIGURE 8-2: COMPARE MODE OPERATION BLOCK DIAGRAM

#### 8.2.1 CCP PIN CONFIGURATION

The user must configure the RC2/CCP1 pin as an output by clearing the TRISC<2> bit.

Note: Clearing the CCP1CON register will force the RC2/CCP1 compare output latch to the default low level. This is not the PORTC I/O data latch.

#### 8.2.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 8.2.3 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt mode is chosen, the CCP1 pin is not affected. The CCPIF bit is set, causing a CCP interrupt (if enabled).

#### 8.2.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated, which may be used to initiate an action.

The special event trigger output of CCP1 resets the TMR1 register pair and starts an A/D conversion (if the A/D module is enabled). This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

**Note:** The special event trigger from the CCP module will not set interrupt flag bit TMR1IF (PIR1<0>).

TABLE 8-2: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, AND TIMER1

| Address                | Name    | Bit 7   | Bit 6                         | Bit 5         | Bit 4         | Bit 3          | Bit 2        | Bit 1      | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|---------|---------|-------------------------------|---------------|---------------|----------------|--------------|------------|--------|--------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON  | GIE     | PEIE                          | TMR0IE        | INTE          | RBIE           | TMR0IF       | INTF       | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1    | (1)     | ADIF                          | (1)           | (1)           | SSPIF          | CCP1IF       | TMR2IF     | TMR1IF | r0rr 0000                | 0000 0000                       |

| 8Ch                    | PIE1    | (1)     | ADIE                          | (1)           | (1)           | SSPIE          | CCP1IE       | TMR2IE     | TMR1IE | r0rr 0000                | 0000 0000                       |

| 87h                    | TRISC   | PORTO   | PORTC Data Direction Register |               |               |                |              |            |        |                          | 1111 1111                       |

| 0Eh                    | TMR1L   | Holding | Registe                       | r for the Lea | ast Significa | nt Byte of th  | ne 16-bit Tl | MR1 Regis  | ster   | xxxx xxxx                | uuuu uuuu                       |

| 0Fh                    | TMR1H   | Holding | Registe                       | r for the Mo  | st Significar | nt Byte of the | e 16-bit TN  | /IR1 Regis | ter    | xxxx xxxx                | uuuu uuuu                       |

| 10h                    | T1CON   |         | I                             | T1CKPS1       | T1CKPS0       | T1OSCEN        | T1SYNC       | TMR1CS     | TMR10N | 00 0000                  | uu uuuu                         |

| 15h                    | CCPR1L  | Capture | :/Compa                       | re/PWM Re     | gister1 (LSI  | 3)             |              |            |        | xxxx xxxx                | uuuu uuuu                       |

| 16h                    | CCPR1H  | Capture | /Compa                        | re/PWM Re     | gister1 (MS   | В)             |              |            |        | xxxx xxxx                | uuuu uuuu                       |

| 17h                    | CCP1CON |         | ı                             | CCP1X         | CCP1Y         | CCP1M3         | CCP1M2       | CCP1M1     | CCP1M0 | 00 0000                  | 00 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by Capture and Timer1.

Note 1: These bits are reserved; always maintain clear.

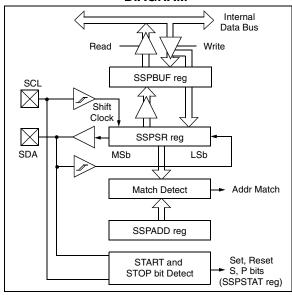

### 9.2 MSSP I<sup>2</sup>C Operation

The MSSP module in I<sup>2</sup>C mode, fully implements all master and slave functions (including general call support) and provides interrupts on START and STOP bits in hardware to determine a free bus (multi-master function). The MSSP module implements the standard mode specifications, as well as 7-bit and 10-bit addressing.

Refer to Application Note (AN578), "Use of the SSP Module in the I<sup>2</sup>C Multi-Master Environment."

A "glitch" filter is on the SCL and SDA pins when the pin is an input. This filter operates in both the 100 kHz and 400 kHz modes. In the 100 kHz mode, when these pins are an output, there is a slew rate control of the pin that is independent of device frequency.

FIGURE 9-5: I<sup>2</sup>C SLAVE MODE BLOCK DIAGRAM

Two pins are used for data transfer. These are the SCL pin, which is the clock, and the SDA pin, which is the data. The SDA and SCL pins are automatically configured when the I<sup>2</sup>C mode is enabled. The SSP module functions are enabled by setting SSP Enable bit SSPEN (SSPCON<5>).

The MSSP module has six registers for  $I^2C$  operation. They are the:

- SSP Control Register (SSPCON)

- SSP Control Register2 (SSPCON2)

- SSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift Register (SSPSR) Not directly accessible

- SSP Address Register (SSPADD)

The SSPCON register allows control of the I<sup>2</sup>C operation. Four mode selection bits (SSPCON<3:0>) allow one of the following I<sup>2</sup>C modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Master mode, clock = OSC/4 (SSPADD +1)

Before selecting any  $I^2C$  mode, the SCL and SDA pins must be programmed to inputs by setting the appropriate TRIS bits. Selecting an  $I^2C$  mode by setting the SSPEN bit, enables the SCL and SDA pins to be used as the clock and data lines in  $I^2C$  mode. Pull-up resistors must be provided externally to the SCL and SDA pins for the proper operation of the  $I^2C$  module.

The CKE bit (SSPSTAT<6:7>) sets the levels of the SDA and SCL pins in either Master or Slave mode. When CKE = 1, the levels will conform to the SMBus specification. When CKE = 0, the levels will conform to the  $I^2$ C specification.

The SSPSTAT register gives the status of the data transfer. This information includes detection of a START (S) or STOP (P) bit, specifies if the received byte was data or address, if the next byte is the completion of 10-bit address, and if this will be a read or write data transfer.

SSPBUF is the register to which the transfer data is written to or read from. The SSPSR register shifts the data in or out of the device. In receive operations, the SSPBUF and SSPSR create a doubled buffered receiver. This allows reception of the next byte to begin before reading the last byte of received data. When the complete byte is received, it is transferred to the SSPBUF register and flag bit SSPIF is set. If another complete byte is received before the SSPBUF register is read, a receiver overflow has occurred and bit SSPOV (SSPCON<6>) is set and the byte in the SSPSR is lost.

The SSPADD register holds the slave address. In 10-bit mode, the user needs to write the high byte of the address (1111  $\,^{0}$  A9 A8  $\,^{0}$ ). Following the high byte address match, the low byte of the address needs to be loaded (A7:A0).

#### 9.2.1 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs. The MSSP module will override the input state with the output data when required (slave-transmitter).

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge (ACK) pulse, and then load the SSPBUF register with the received value currently in the SSPSR register.

There are certain conditions that will cause the MSSP module not to give this  $\overline{ACK}$  pulse. These are if either (or both):

- The buffer full bit BF (SSPSTAT<0>) was set before the transfer was received.

- The overflow bit SSPOV (SSPCON<6>) was set before the transfer was received.

If the BF bit is set, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF and SSPOV are set. Table 9-2 shows what happens when a data transfer byte is received, given the status of bits BF and SSPOV. The shaded cells show the condition where user software did not properly clear the overflow condition. Flag bit BF is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and low time for proper operation. The high and low times of the I<sup>2</sup>C specification, as well as the requirement of the MSSP module, is shown in timing parameter #100 and parameter #101 of the electrical specifications.

#### 9.2.1.1 Addressing

Once the MSSP module has been enabled, it waits for a START condition to occur. Following the START condition, the 8-bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match, and the BF and SSPOV bits are clear, the following events occur:

- The SSPSR register value is loaded into the SSPBUF register on the falling edge of the 8th SCL pulse.

- b) The buffer full bit, BF, is set on the falling edge of the 8th SCL pulse.

- c) An  $\overline{ACK}$  pulse is generated.

- d) SSP interrupt flag bit, SSPIF (PIR1<3>), is set (interrupt is generated if enabled) on the falling edge of the 9th SCL pulse.

In 10-bit Address mode, two address bytes need to be received by the slave. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit  $R/\overline{W}$  (SSPSTAT<2>) must specify a write, so the slave device will receive the second address byte. For a 10-bit address the first byte would equal '1111 0 A9 A8 0', where A9 and A8 are the two MSbs of the address. The sequence of events for a 10-bit address is as follows, with steps 7-9 for slave transmitter:

- Receive first (high) byte of Address (bits SSPIF, BF and UA (SSPSTAT<1>) are set).

- Update the SSPADD register with the second (low) byte of Address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- Receive second (low) byte of Address (bits SSPIF, BF and UA are set).

- Update the SSPADD register with the first (high) byte of Address. This will clear bit UA and release the SCL line.

- Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive Repeated START condition.

- Receive first (high) byte of Address (bits SSPIF and BF are set).

- Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

Note: Following the Repeated START condition (step 7) in 10-bit mode, the user only needs to match the first 7-bit address. The user does not update the SSPADD for the second half of the address.

#### 9.2.1.2 Slave Reception

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address byte overflow condition exists, then no Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set, or bit SSPOV (SSPCON<6>) is set. This is an error condition due to user firmware.

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the received byte.

Note: The SSPBUF will be loaded if the SSPOV bit is set and the BF flag is cleared. If a read of the SSPBUF was performed, but the user did not clear the state of the SSPOV bit before the next receive occurred, the ACK is not sent and the SSPBUF is updated.

#### 11.3 Reset

The PIC16F872 differentiates between various kinds of RESET:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during SLEEP

- WDT Reset (during normal operation)

- WDT Wake-up (during SLEEP)

- Brown-out Reset (BOR)

Some registers are not affected in any RESET condition. Their status is unknown on POR and unchanged in any other RESET. Most other registers are reset to a "RESET state" on Power-on Reset (POR), on the MCLR and WDT Reset, on MCLR Reset during

SLEEP, and Brown-out Reset (BOR). They are not affected by a WDT Wake-up, which is viewed as the resumption of normal operation. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are set or cleared differently in different RESET situations, as indicated in Table 11-4. These bits are used in software to determine the nature of the RESET. See Table 11-6 for a full description of RESET states of all registers.

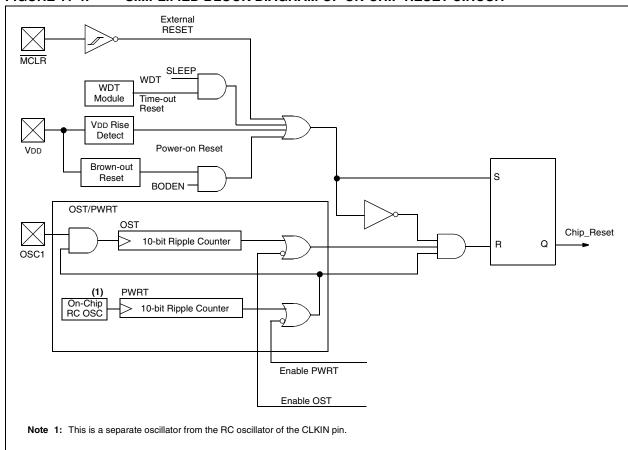

A simplified block diagram of the On-Chip Reset circuit is shown in Figure 11-4.

These devices have a  $\overline{\text{MCLR}}$  noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive  $\overline{\text{MCLR}}$  pin low.

FIGURE 11-4: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

TABLE 11-6: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

| Register   | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset | Wake-up via WDT or<br>Interrupt |

|------------|------------------------------------|--------------------------|---------------------------------|

| TMR1L      | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| TMR1H      | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| T1CON      | 00 0000                            | uu uuuu                  | uu uuuu                         |

| TMR2       | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| T2CON      | -000 0000                          | -000 0000                | -uuu uuuu                       |

| SSPBUF     | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| SSPCON     | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| CCPR1L     | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| CCPR1H     | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| CCP1CON    | 00 0000                            | 00 0000                  | uu uuuu                         |

| ADRESH     | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| ADCON0     | 0000 00-0                          | 0000 00-0                | uuuu uu-u                       |

| OPTION_REG | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| TRISA      | 11 1111                            | 11 1111                  | uu uuuu                         |

| TRISB      | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| TRISC      | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| PIE1       | r0rr 0000                          | r0rr 0000                | rurr uuuu                       |

| PIE2       | -r-0 0r                            | -r-0 0r                  | -r-u ur                         |

| PCON       | qq                                 | uu                       | uu                              |

| SSPCON2    | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| PR2        | 1111 1111                          | 1111 1111                | 1111 1111                       |

| SSPADD     | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| SSPSTAT    | 00 0000                            | 00 0000                  | uu uuuu                         |

| ADRESL     | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| ADCON1     | 0 0000                             | 0 0000                   | u uuuu                          |

| EEDATA     | 0 0000                             | 0 0000                   | u uuuu                          |

| EEADR      | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| EEDATH     | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| EEADRH     | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| EECON1     | x x000                             | u u000                   | u uuuu                          |

| EECON2     |                                    |                          |                                 |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition, r = reserved, maintain clear

Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

<sup>2:</sup> When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

<sup>3:</sup> See Table 11-5 for RESET value for specific condition.

#### 11.14 In-Circuit Debugger

When the DEBUG bit in the configuration word is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB® IDE. When the microcontroller has this feature enabled, some of the resources are not available for general use. Table 11-8 shows which features are consumed by the background debugger.

TABLE 11-8: DEBUGGER RESOURCES

| I/O pins       | RB6, RB7                                     |

|----------------|----------------------------------------------|

| Stack          | 1 level                                      |

| Program Memory | Address 0000h must be NOP                    |

|                | Last 100h words                              |

| Data Memory    | 0x070 (0x0F0, 0x170, 0x1F0)<br>0x1EB - 0x1EF |

To use the In-Circuit Debugger function of the microcontroller, the design must implement In-Circuit Serial Programming connections to  $\overline{\text{MCLR}}/\text{VPP}$ , VDD, GND, RB7 and RB6. This will interface to the In-Circuit Debugger module available from Microchip or one of the third party development tool companies.

### 11.15 Program Verification/Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

#### 11.16 ID Locations

Four memory locations (2000h - 2003h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution, but are readable and writable during program/verify. It is recommended that only the 4 Least Significant bits of the ID location are used.

#### 11.17 In-Circuit Serial Programming

PIC16F872 microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

When using ICSP, the part must be supplied 4.5V to 5.5V if a bulk erase will be executed. This includes reprogramming of the code protect, both from an onstate to off-state. For all other cases of ICSP, the part may be programmed at the normal operating voltages. This means calibration values, unique user IDs or user code can be reprogrammed or added.

For complete details of serial programming, please refer to the EEPROM Memory Programming Specification for the PIC16F87X (DS39025).

#### 11.18 Low Voltage ICSP Programming

The LVP bit of the configuration word enables low voltage ICSP programming. This mode allows the microcontroller to be programmed via ICSP, using a VDD source in the operating voltage range. This only means that VPP does not have to be brought to VIHH, but can instead be left at the normal operating voltage. In this mode, the RB3/PGM pin is dedicated to the programming function and ceases to be a general purpose I/O pin. During programming, VDD is applied to the MCLR pin. To enter Programming mode, VDD must be applied to the RB3/PGM pin, provided the LVP bit is set. The LVP bit defaults to on ('1') from the factory.

- Note 1: The High Voltage Programming mode is always available, regardless of the state of the LVP bit, by applying VIHH to the MCLR pin.

- 2: While in low voltage ICSP mode, the RB3 pin can no longer be used as a general purpose I/O pin.

- **3:** When using low voltage ICSP programming (LVP) and the pull-ups on PORTB are enabled, bit 3 in the TRISB register must be cleared to disable the pull-up on RB3 and ensure the proper operation of the device.

If Low Voltage Programming mode is not used, the LVP bit can be programmed to a '0' and RB3/PGM becomes a digital I/O pin. However, the LVP bit may only be programmed when programming is entered with VIHH on MCLR. The LVP bit can only be charged when using high voltage on  $\overline{\text{MCLR}}.$

It should be noted that once the LVP bit is programmed to 0, only the High Voltage Programming mode is available and only High Voltage Programming mode can be used to program the device.

When using low voltage ICSP, the part must be supplied 4.5V to 5.5V if a bulk erase will be executed. This includes reprogramming of the code protect bits from an on-state to off-state. For all other cases of low voltage ICSP, the part may be programmed at the normal operating voltage. This means calibration values, unique user IDs, or user code can be reprogrammed or added.

| DECFSZ                           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                              | INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                         |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                          | [ label ] DECFSZ f,d                                                                                                                                                                                                                                                                                | Syntax:          | [ label ] INCFSZ f,d                                                                                                                                                                                                                                                                           |

| Operands:                        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                  | Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                             |

| Operation:                       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                          | Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                     |

| Status Affected:                 | None                                                                                                                                                                                                                                                                                                | Status Affected: | None                                                                                                                                                                                                                                                                                           |

| Description:                     | The contents of register 'f' are decremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'.  If the result is 1, the next instruction is executed. If the result is 0, then a NOP is executed instead, making it a 2Tcy instruction. | Description:     | The contents of register 'f' are incremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'.  If the result is 1, the next instruction is executed. If the result is 0, a NOP is executed instead, making it a 2Tcy instruction. |

| GОТО                             | Unconditional Branch                                                                                                                                                                                                                                                                                | IORLW            | Inclusive OR Literal with W                                                                                                                                                                                                                                                                    |

| Syntax:                          | [ label ] GOTO k                                                                                                                                                                                                                                                                                    | Syntax:          | [ label ] IORLW k                                                                                                                                                                                                                                                                              |

| Operands:                        | $0 \le k \le 2047$                                                                                                                                                                                                                                                                                  | Operands:        | $0 \leq k \leq 255$                                                                                                                                                                                                                                                                            |

| Operation:                       | $k \rightarrow PC < 10:0 >$                                                                                                                                                                                                                                                                         | Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                                                                                                                                                                                                   |

|                                  | PCLATH<4:3> → PC<12:11>                                                                                                                                                                                                                                                                             | Status Affected: | Z                                                                                                                                                                                                                                                                                              |

| Status Affected:<br>Description: | None GOTO is an unconditional branch. The eleven-bit immediate value is loaded into PC bits <10:0>. The upper bits of PC are loaded from PCLATH<4:3>. GOTO is a two-cycle instruction.                                                                                                              | Description:     | The contents of the W register are OR'ed with the eight-bit literal 'k'. The result is placed in the W register.                                                                                                                                                                               |

| INCF                             | Increment f                                                                                                                                                                                                                                                                                         | IORWF            | Inclusive OR W with f                                                                                                                                                                                                                                                                          |

| Syntax:                          | [ label ] INCF f,d                                                                                                                                                                                                                                                                                  | Syntax:          | [ label ] IORWF f,d                                                                                                                                                                                                                                                                            |

| Operands:                        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                  | Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                             |

| Operation:                       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                                                                                                                                                 | Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                                                                                                                                                       |

| Status Affected:                 | Z                                                                                                                                                                                                                                                                                                   | Status Affected: | Z                                                                                                                                                                                                                                                                                              |

| Description:                     | The contents of register 'f' are incremented. If 'd' is 0, the result                                                                                                                                                                                                                               | Description:     | Inclusive OR the W register with register 'f'. If 'd' is 0, the result is                                                                                                                                                                                                                      |

is placed in the W register. If 'd' is

1, the result is placed back in

register 'f'.

placed in the W register. If 'd' is 1,

the result is placed back in

register 'f'.

TABLE 13-1: DEVELOPMENT TOOLS FROM MICROCHIP

| MPLAB® Integrated                                                    | -DIC | PIC1 | PIC16 | PIC16    | PIC16 | PIC16 | PIC16 | PIC16 | PIC16    | PIC16F | PIC160      | FIC17 | PIC17C | PIC18C | PIC18F | 93C)<br>54CX | нсех        | MCRF | WCP2 |

|----------------------------------------------------------------------|------|------|-------|----------|-------|-------|-------|-------|----------|--------|-------------|-------|--------|--------|--------|--------------|-------------|------|------|

|                                                                      | >    | >    | >     | >        | >     | >     | >     | >     | >        | >      | >           | >     | >      | >      | >      |              |             |      |      |

| MPLAB® C17 C Compiler                                                |      | !    |       |          |       |       |       |       |          |        |             | >     | `      | ļ      |        |              |             |      |      |

| MPLAB® C18 C Compiler                                                |      |      |       |          |       |       |       |       |          |        |             |       |        | ^      | ^      |              |             |      |      |

| MPASM <sup>TM</sup> Assembler/<br>MPLINK <sup>TM</sup> Object Linker | >    | >    | >     | >        | >     | >     | >     | >     | >        | >      | ^           | >     | >      | >      | ^      | ^            | <b>&gt;</b> |      |      |

| MPLAB® ICE In-Circuit Emulator                                       | >    | >    | >     | >        | >     | **^   | >     | >     | >        | `      | >           | >     | `      | >      | >      |              |             |      |      |

| ICEPIC™ In-Circuit Emulator                                          | >    |      | >     | >        | >     |       | >     | >     | >        |        | <i>&gt;</i> |       | 1      |        |        |              |             |      |      |

| MPLAB® ICD In-Circuit                                                |      |      |       | *        |       |       | *>    |       |          | >      |             |       |        |        | >      |              |             |      |      |

| PICSTART® Plus Entry Level Development Programmer                    | >    | >    | >     | >        | >     | **^   | >     | >     | >        | `      | >           | >     | >      | >      | `      |              |             |      |      |

| E<br>D<br>D Iniversal Device Programmer<br>D                         | >    | >    | >     | `        | >     | **    | >     | >     | <b>,</b> | >      | <i>&gt;</i> | >     | >      | >      | >      | <i>&gt;</i>  | >           |      |      |

| PICDEM™ 1 Demonstration<br>Board                                     |      |      | >     |          | >     |       | +     |       | >        |        |             | >     |        |        |        |              |             |      |      |

| PICDEM™ 2 Demonstration<br>Board                                     |      |      |       | <b>₹</b> |       |       | +     |       |          |        |             |       |        | >      | ^      |              |             |      |      |

| PICDEM™ 3 Demonstration<br>Board                                     |      |      |       |          |       |       |       |       |          |        | >           |       |        |        |        |              |             |      |      |

| PICDEM™ 14A Demonstration<br>Board                                   |      | >    |       |          |       |       |       |       |          |        |             |       |        |        |        |              |             |      |      |

| PICDEM™ 17 Demonstration<br>Board                                    |      |      |       |          |       |       |       |       |          |        |             |       | >      |        |        |              |             |      |      |

| KEELoo® Evaluation Kit                                               |      |      |       |          |       |       |       |       |          |        |             |       |        |        |        |              | ^           |      |      |

| KEELoo® Transponder Kit                                              |      |      |       |          |       |       |       |       |          |        |             |       |        |        |        |              | ^           |      |      |

| microlD™ Programmer's Kit                                            |      |      |       |          |       |       |       |       |          |        |             |       |        |        |        |              |             | >    |      |

| 125 kHz microlD™<br>Developer's Kit                                  |      |      |       |          |       |       |       |       |          |        |             |       |        |        |        |              |             | >    |      |

| 125 kHz Anticollision microlD™<br>Developer's Kit                    |      |      |       |          |       |       |       |       |          |        |             |       |        |        |        |              |             | >    |      |

| 13.56 MHz Anticollision<br>microlD™ Developer's Kit                  |      |      |       |          |       |       |       |       |          |        |             |       |        |        |        |              |             | >    |      |

| MCP2510 CAN Developer's Kit                                          |      |      |       |          |       |       |       |       |          |        |             |       |        |        |        |              |             |      | ^    |

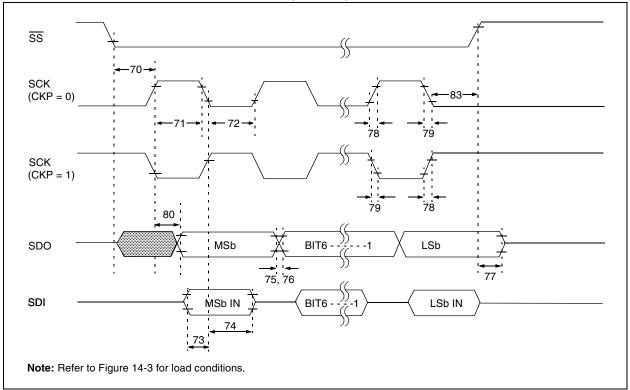

FIGURE 14-12: SPI SLAVE MODE TIMING (CKE = 0)

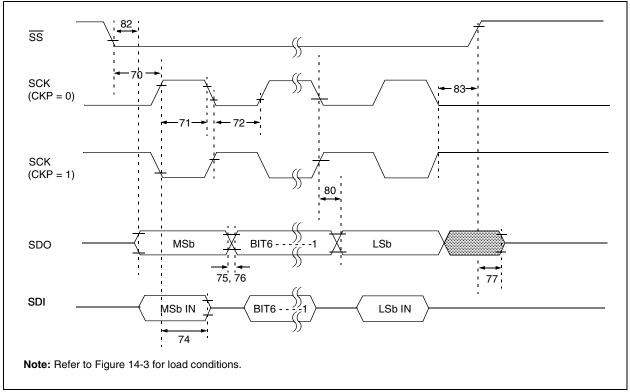

FIGURE 14-13: SPI SLAVE MODE TIMING (CKE = 1)

NOTES:

| P                                       |            | Program Memory                                                   |       |

|-----------------------------------------|------------|------------------------------------------------------------------|-------|

| P Bit                                   |            | Interrupt Vector                                                 |       |

| STOP Bit (P)                            | 52         | Paging                                                           | 20    |

| Packaging                               |            | Program Memory Map and Stack                                     | 7     |

| PCL Register                            |            | RESET Vector                                                     | 7     |

| PCLATH Register                         | , ,        | Program Verification                                             | 101   |

| <del>-</del>                            | ,          | Programming, Device Instructions                                 | 103   |

| PCON Register                           |            | Pulse Width Modulation. See Capture/Compare/PWM,                 |       |

| BOR Bit<br>POR Bit                      |            | PWM Mode.                                                        |       |

|                                         | 19         | PUSH                                                             | 20    |

| PEN Bit                                 | <b>5</b> 4 | PWM Mode                                                         |       |

| STOP Condition Enable Bit (PEN)         | 54         | Setup                                                            | 49    |

| PICDEM 1 Low Cost PICmicro              | 440        | _                                                                |       |

| Demonstration Board                     |            | R                                                                |       |

| PICDEM 17 Demonstration Board           | 114        | R/W Bit                                                          | 59    |

| PICDEM 2 Low Cost PIC16CXX              |            | Read/Write Bit Information (R/W)                                 |       |

| Demonstration Board                     | 113        | R/W Bit                                                          |       |

| PICDEM 3 Low Cost PIC16CXXX             |            | RA0/AN0 Pin                                                      |       |

| Demonstration Board                     | 114        | RA1/AN1 Pin                                                      | _     |

| PICSTART Plus Entry Level Development   |            | RA2/AN2/VREF- Pin                                                | _     |

| Programmer                              | 113        | RA3/AN3/VREF+ Pin                                                |       |

| PIE1 Register                           | 10, 15     | RA4/T0CKI Pin                                                    | _     |

| PIE2 Register                           | 10, 17     | RA5/SS/AN4 Pin                                                   | _     |

| Pinout Descriptions                     | 5—6        |                                                                  | 5     |

| PIR1 Register                           | 9, 16      | RAM. See Data Memory                                             |       |

| PIR2 Register                           | 9, 18      | RB0/INT Pin                                                      |       |

| POP                                     | 20         | RB1 Pin                                                          | _     |

| POR. See Power-on Reset                 |            | RB2 Pin                                                          | -     |

| PORTA                                   | 5          | RB3/PGM Pin                                                      |       |

| Associated Registers                    | 30         | RB4 Pin                                                          | _     |

| Functions                               | 30         | RB5 Pin                                                          | -     |

| PORTA Register                          |            | RB6/PGC Pin                                                      |       |

| RA3                                     | -, -       | RB7/PGD Pin                                                      |       |

| RA0 and RA5 Port Pins                   | 29         | RC0/T1OSO/T1CKI Pin                                              |       |

| TRISA Register                          |            | RC1/T1OSI Pin                                                    |       |

| PORTB                                   |            | RC2/CCP1 Pin                                                     | -     |

| Associated Registers                    |            | RC3/SCK/SCL Pin                                                  | -     |

| Functions                               |            | RC4/SDI/SDA Pin                                                  |       |

| PORTB Register                          |            | RC5/SDO Pin                                                      | 6     |

| RB0/INT Pin, External                   |            | RC6 Pin                                                          | 6     |

| RB7:RB4 Interrupt-on-Change             |            | RC7 Pin                                                          | 6     |

| RB7:RB4 Interrupt-on-Change Enable      |            | RCEN Bit                                                         |       |

| (RBIE Bit)                              | QΩ         | Receive Enable Bit (RCEN)                                        | 54    |

|                                         | 90         | Receive Overflow Indicator Bit (SSPOV)                           | 53    |

| RB7:RB4 Interrupt-on-Change Flag        | 21 00      | Registers                                                        |       |

| (RBIF Bit)                              |            | ADCON0 (A/D Control 0) Register                                  | 79    |

| TRISB Register                          |            | ADCON1 (A/D Control 1) Register                                  | 80    |

| PORTC                                   |            | CCP1CON (CCP Control 1) Register                                 | 45    |

| Associated Registers                    |            | EECON1 (EEPROM Control) Register                                 |       |

| Functions                               |            | INTCON Register                                                  |       |

| PORTC Register                          | ,          | OPTION_REG Register1                                             | 3, 36 |

| TRISC Register                          | 33         | PCON (Power Control) Register                                    |       |

| Power-down Mode. See SLEEP              |            | PIE1 (Peripheral Interrupt Enable 1) Register                    |       |

| Power-on Reset (POR)                    |            | PIE2 (Peripheral Interrupt Enable 2) Register                    |       |

| Oscillator Start-up Timer (OST)         |            | PIR1 (Peripheral Interrupt Request 1) Register                   |       |

| Power Control (PCON) Register           |            | PIR2 (Peripheral Interrupt Request 2) Register                   |       |

| Power-down (PD Bit)                     |            | Special Function, Summary                                        |       |

| Power-up <u>Tim</u> er (PWRT)           |            | SSPCON (Sync Serial Port Control) Register                       |       |

| Time-out (TO Bit)                       |            | SSPCON2 (Sync Serial Port Control 2) Register                    |       |

| Time-out Sequence on Power-up           |            | , ,                                                              |       |

| PR2 Register                            | 10, 43     | SSPSTAT (Sync Serial Port Status) Register                       |       |

| PRO MATE II Universal Device Programmer | 113        | STATUS Register                                                  |       |

| Program Counter                         |            | T1CON (Timer1 Control) Register T2CON (Timer 2 Control) Register |       |

| RESET Conditions                        | 93         | 1200N (Timel 2 Control) negister                                 | 43    |

| RESET87, 9                                       | 91         | STATUS Register9                            | , 12 |

|--------------------------------------------------|------------|---------------------------------------------|------|

| RESET Conditions for All Registers               | 93         | C Bit                                       | 12   |

| RESET Conditions for PCON Register               | 93         | DC Bit                                      | 12   |

| RESET Conditions for Program Counter             | 93         | IRP Bit                                     | 12   |

| RESET Conditions for Special Registers           | 93         | PD Bit12                                    | , 91 |

| RESET Conditions for STATUS Register             | 93         | RP1:RP0 Bits                                | 12   |

| RESET                                            |            | TO Bit12                                    | , 91 |

| Brown-out Reset (BOR). See Brown-out Reset (BOR) |            | Z Bit                                       | 12   |

| MCLR Reset. See MCLR                             |            | Synchronous Serial Port Enable Bit (SSPEN)  | 53   |

| Power-on Reset (POR). See Power-on Reset (POR)   |            | Synchronous Serial Port Interrupt           | 16   |

| WDT Reset. See Watchdog Timer (WDT)              |            | Synchronous Serial Port Mode Select Bits    |      |

| Revision History1                                | 55         | (SSPM3:SSPM0)                               | 53   |

| RSEN Bit                                         |            |                                             |      |

| Repeated START Condition Enabled Bit (RSEN)      | 54         | Т                                           |      |

|                                                  |            | T1CKPS0 bit                                 | 39   |

| S                                                |            | T1CKPS1 bit                                 | 39   |

| S Bit                                            |            | T1CON Register                              | 9    |

| START Bit (S)                                    | 52         | T1OSCEN bit                                 |      |

| Sample Bit (SMP)                                 | 52         | T1SYNC bit                                  | 39   |

| SCK Pin                                          | 55         | T2CON Register                              | 9    |

| SCL Pin                                          | 58         | Time-out Sequence                           | 92   |

| SDA Pin                                          | 58         | Timer0                                      |      |

| SDI Pin                                          | 55         | Associated Registers                        |      |

| SDO Pin                                          |            | External Clock                              |      |

| SEN Bit                                          |            | Interrupt                                   |      |

| START Condition Enabled Bit (SEN)                | 54         | Overflow Flag (TMR0IF Bit)                  |      |

| Serial Clock (SCK)                               |            | Overflow Interrupt                          |      |

| Serial Clock (SCL)                               |            | Prescaler                                   |      |

| Serial Data Address (SDA)                        |            | T0CKI                                       | 36   |

| Serial Data In (SDI)                             |            | Timer1                                      |      |

| Serial Data Out (SDO)                            |            | Associated Registers                        |      |

| Slave Select (SS)                                |            | Asynchronous Counter Mode                   |      |

| SLEEP87, 91, 10                                  |            | Counter Operation                           |      |

| SMP Bit                                          |            | Operation in Timer Mode                     |      |

| Software Simulator (MPLAB SIM)                   |            | Oscillator                                  |      |

| Special Features of the CPU                      |            | Capacitor Selection                         |      |

| Special Function Registers (SFRs)                |            | Prescaler                                   |      |

| Data EEPROM and FLASH Program Memory             |            | Reading and Writing in Asynchronous         |      |

| Speed, Operating                                 |            | Counter Mode                                | 41   |

| SPI Clock Edge Select Bit (CKE)                  |            | Resetting of Timer1 Registers               |      |

| SPI Mode                                         | _          | Resetting Timer1 using a CCP Trigger Output |      |

| Associated Registers                             | 57         | Synchronized Counter Mode                   |      |

| Master Mode                                      |            | Timer2                                      |      |

| Serial Clock                                     |            | Associated Registers                        | _    |

| Serial Data In                                   |            | Output                                      |      |

| Serial Data Out                                  |            | Postscaler                                  |      |

| Slave Select                                     |            | Prescaler                                   |      |

| SPI Clock                                        |            | Prescaler and Postscaler                    |      |

| SS Pin                                           | -          | Timing Diagrams                             |      |

| SSBUF Register                                   |            | A/D Conversion                              | 137  |

| MSSP                                             | . 0        | Acknowledge Sequence                        |      |

| See also I <sup>2</sup> C Mode and SPI Mode.     |            | Baud Rate Generator with Clock Arbitration  |      |

| SSPADD Register                                  | 10         | BRG Reset Due to SDA Collision During       | 00   |

| SSPBUF register                                  |            | START Condition                             | 75   |

| SSPCON Register                                  |            | Brown-out Reset                             |      |

| SSPCON2 Register                                 |            | Bus Collision                               | 123  |

| SSPEN Bit                                        |            |                                             | 72   |

|                                                  |            | Transmit and Acknowledge                    | 73   |

| SSPIF                                            |            | Bus Collision During a Repeated START       | 70   |

| SSPM3:SSPM0 Bits                                 |            | Condition (Case 1)                          | /0   |

| SSPOV Bit                                        |            | Bus Collision During a Repeated START       | 70   |

| SSPOV Status Flag                                |            | Condition (Case2)                           | /6   |

| SSPSTAT Register                                 |            | Bus Collision During a STOP Condition       |      |

| Stack                                            |            | (Case 1)                                    | //   |

| Overflows                                        |            | Bus Collision During a STOP Condition       |      |

| Underflow                                        | <u>-</u> U | (Case 2)                                    | //   |

| Bus Collision During START Condition       |        |

|--------------------------------------------|--------|

| (SCL = 0)                                  | 75     |

| Bus Collision During START Condition       |        |

| (SDA Only)                                 | 74     |

| Capture/Compare/PWM                        | 131    |

| CLKOUT and I/O                             |        |

| External Clock                             |        |

| First START Bit Timing                     |        |

| I <sup>2</sup> C Bus Data                  |        |

| I <sup>2</sup> C Bus START/STOP Bits       | 12/    |

| I <sup>2</sup> C Master Mode Transmission  |        |

| I <sup>2</sup> C Mode (7-bit Reception)    |        |

|                                            |        |

| I <sup>2</sup> C Mode (7-bit Transmission) |        |

| Master Mode Transmit Clock Arbitration     |        |

| Power-up Timer                             |        |

| Repeat START Condition                     |        |

| RESET                                      | 129    |

| Slave Mode General Call Address Sequence   |        |

| (7 or 10-bit Mode)                         | 61     |

| Slow Rise Time (MCLR Tied to VDD           |        |

| Via RC Network)                            | 96     |

| SPI Master Mode                            |        |

| SPI Master Mode (CKE = 0, SMP = 0)         | 132    |

| SPI Master Mode (CKE = 1, SMP = 1)         |        |

| SPI Slave Mode (CKE = 0)                   |        |

| SPI Slave Mode (CKE = 1)                   | 57 133 |

| Start-up Timer                             |        |

| STOP Condition Receive or Transmit Mode    |        |

| Time-out Sequence on Power-up              |        |

|                                            | 96     |

| Time-out Sequence on Power-up              |        |

| (MCLR Not Tied to VDD)                     |        |

| Case 1                                     |        |

| Case 2                                     | 96     |

| Time-out Sequence on Power-up              |        |

| (MCLR Tied to VDD Via RC Network)          |        |

| Timer0                                     |        |

| Timer1                                     |        |

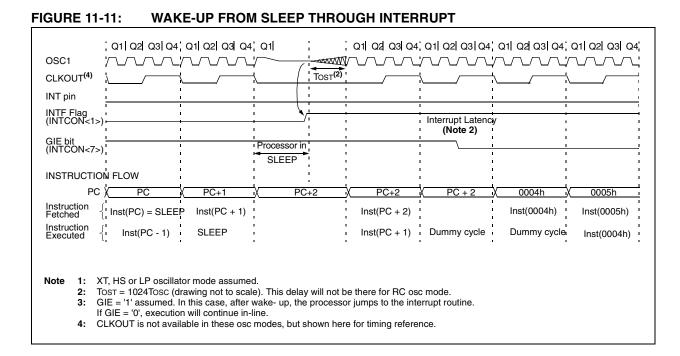

| Wake-up from SLEEP via Interrupt           | 101    |

| Watchdog Timer                             | 129    |

| Timing Parameter Symbology                 |        |

| TMR0 Register                              |        |

| TMR1CS bit                                 |        |

| TMR1H Register                             |        |

| TMR1L Register                             |        |

| TMR1ON bit                                 |        |

| TMR2 Register                              |        |

| TOUTPS3:TOUTPS0 bits                       |        |

|                                            |        |

| TRISA Register                             |        |

| TRISB Register                             |        |