### Microchip Technology - PIC16F872T-I/SO Datasheet

Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 64 x 8                                                                    |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | A/D 5x10b                                                                 |

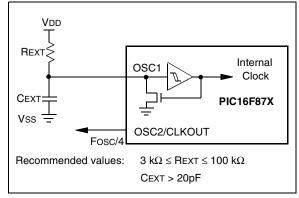

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

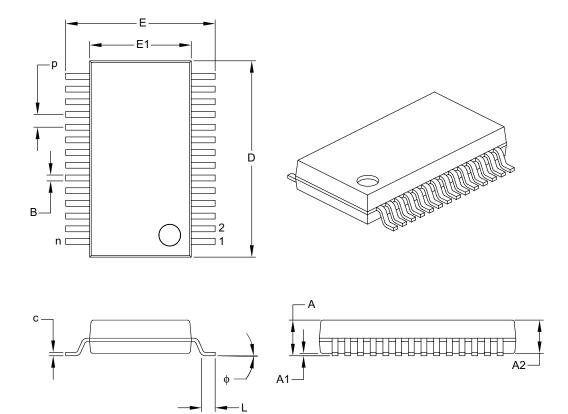

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f872t-i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| <b>TABLE 2-1:</b> | SPECIAL FUNCTION REGISTER SUMMARY | (CONTINUED) | ) |

|-------------------|-----------------------------------|-------------|---|

|-------------------|-----------------------------------|-------------|---|

| Address               | Name       | Bit 7                                                          | Bit 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Bit 5          | Bit 4                                                      | Bit 3        | Bit 2         | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Details<br>on<br>page: |

|-----------------------|------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------------------------------------------------|--------------|---------------|-------|-------|--------------------------|------------------------|

| Bank 2                |            |                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |                                                            |              |               |       |       |                          |                        |

| 100h <sup>(2)</sup>   | INDF       |                                                                | g this locations is the second s |                | tents of FSR                                               | to address   | data memo     | ry    |       | 0000 0000                | 21, 93                 |

| 101h                  | TMR0       | Timer0 Mo                                                      | odule Regis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ter            |                                                            |              |               |       |       | xxxx xxxx                | 35, 93                 |

| 102h <sup>(2)</sup>   | PCL        | Program (                                                      | Counter (PC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ) Least Sign   | nificant Byte                                              |              |               |       |       | 0000 0000                | 20, 93                 |

| 103h <sup>(2)</sup>   | STATUS     | IRP                                                            | RP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | RP0            | TO                                                         | PD           | Z             | DC    | С     | 0001 1xxx                | 12, 93                 |

| 104h <sup>(2)</sup>   | FSR        | Indirect Da                                                    | ata Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Address Po     | binter                                                     |              |               |       |       | xxxx xxxx                | 21, 93                 |

| 105h                  | _          | Unimplem                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |                                                            |              |               |       |       | _                        | _                      |

| 106h                  | PORTB      | PORTB D                                                        | ata Latch w                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | hen written:   | PORTB pin                                                  | s when read  |               |       |       | xxxx xxxx                | 31, 93                 |

| 107h                  | —          | Unimplem                                                       | nented                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                |                                                            |              |               |       |       | _                        | _                      |

| 108h                  | —          | Unimplem                                                       | nented                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                | _                                                          | _            |               |       |       |                          |                        |

| 109h                  |            | Unimplem                                                       | implemented                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                |                                                            |              |               |       |       |                          | _                      |

| 10Ah <sup>(1,2)</sup> | PCLATH     | _                                                              | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _              | - Write Buffer for the upper 5 bits of the Program Counter |              |               |       |       |                          | 20, 93                 |

| 10Bh <sup>(2)</sup>   | INTCON     | GIE                                                            | PEIE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TMR0IE         | INTE                                                       | RBIE         | TMR0IF        | INTF  | RBIF  | 0000 000x                | 14, 93                 |

| 10Ch                  | EEDATA     | EEPROM                                                         | EEPROM Data Register Low Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |                                                            |              |               |       |       |                          | 23, 94                 |

| 10Dh                  | EEADR      | EEPROM                                                         | Address Re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | egister Low I  | Byte                                                       |              |               |       |       | xxxx xxxx                | 23, 94                 |

| 10Eh                  | EEDATH     | _                                                              | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | EEPROM I       | Data Registe                                               | er High Byte |               |       |       | xxxx xxxx                | 23, 94                 |

| 10Fh                  | EEADRH     | _                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _              | EEPROM /                                                   | Address Reg  | gister High E | Byte  |       | xxxx xxxx                | 23, 94                 |

| Bank 3                | •          |                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |                                                            |              |               |       |       |                          |                        |

| 180h <sup>(2)</sup>   | INDF       |                                                                | g this locations is the second s |                | tents of FSR                                               | to address   | data memo     | ry    |       | 0000 0000                | 21, 93                 |

| 181h                  | OPTION_REG | RBPU                                                           | INTEDG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | TOCS           | TOSE                                                       | PSA          | PS2           | PS1   | PS0   | 1111 1111                | 13, 94                 |

| 182h <sup>(2)</sup>   | PCL        | Program (                                                      | Counter (PC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ) Least Sig    | nificant Byte                                              | 9            | •             |       | •     | 0000 0000                | 20, 93                 |

| 183h <sup>(2)</sup>   | STATUS     | IRP                                                            | RP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | RP0            | TO                                                         | PD           | Z             | DC    | С     | 0001 1xxx                | 12, 93                 |

| 184h <sup>(2)</sup>   | FSR        | Indirect Da                                                    | ata Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Address Po     | ointer                                                     |              |               |       |       | xxxx xxxx                | 21, 93                 |

| 185h                  | _          | Unimplem                                                       | nented                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                |                                                            |              |               |       |       | _                        |                        |

| 186h                  | TRISB      | PORTB D                                                        | ata Directio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | n Register     |                                                            |              |               |       |       | 1111 1111                | 31, 94                 |

| 187h                  | —          | Unimplem                                                       | nented                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -              |                                                            |              |               |       |       | _                        | —                      |

| 188h                  |            | Unimplem                                                       | nented                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                |                                                            |              |               |       |       | _                        | _                      |

| 189h                  | —          | Unimplem                                                       | Unimplemented                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |                                                            |              |               |       |       |                          | —                      |

| 18Ah <sup>(1,2)</sup> | PCLATH     | — — — Write Buffer for the upper 5 bits of the Program Counter |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |                                                            |              |               |       |       | 0 0000                   | 20, 93                 |

| 18Bh <sup>(2)</sup>   | INTCON     | GIE PEIE TMROIE INTE RBIE TMROIF INTE RBIF                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |                                                            |              |               |       |       | 0000 000x                | 14, 93                 |

| 18Ch                  | EECON1     | EEPGD                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |                                                            |              |               |       |       | x x000                   | 24, 94                 |

| 18Dh                  | EECON2     | EEPROM                                                         | Control Re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | gister2 (not a | a physical re                                              | gister)      |               |       |       |                          | 23, 94                 |

| 18Eh                  | —          | Reserved                                                       | ; maintain cl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ear            |                                                            |              |               |       |       | 0000 0000                | —                      |

| 18Fh                  |            | Reserved                                                       | ; maintain cl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ear            |                                                            |              |               |       |       | 0000 0000                | _                      |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

2: These registers can be addressed from any bank.

3: These bits are reserved; always maintain these bits clear.

### 2.2.2.8 PCON Register

bit 1

The Power Control (PCON) Register contains flag bits to allow differentiation between a Power-on Reset (POR), a Brown-out Reset (BOR), a Watchdog Reset (WDT) and an external MCLR Reset.

| Note: | BOR is unknown on POR. It must be set by      |  |  |  |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|--|--|--|

|       | the user and checked on subsequent            |  |  |  |  |  |  |  |  |

|       | RESETS to see if BOR is clear, indicating     |  |  |  |  |  |  |  |  |

|       | a brown-out has occurred. The BOR status      |  |  |  |  |  |  |  |  |

|       | bit is a don't care and is not predictable if |  |  |  |  |  |  |  |  |

|       | the brown-out circuit is disabled (by clear-  |  |  |  |  |  |  |  |  |

|       | ing the BODEN bit in the Configuration        |  |  |  |  |  |  |  |  |

|       | Word).                                        |  |  |  |  |  |  |  |  |

### REGISTER 2-8: PCON REGISTER (ADDRESS: 8Eh)

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-1 |

|-------|-----|-----|-----|-----|-----|-------|-------|

| —     | _   | _   | —   | —   | _   | POR   | BOR   |

| bit 7 |     |     |     |     |     |       | bit 0 |

bit 7-2 Unimplemented: Read as '0'

**POR**: Power-on Reset Status bit

1 = No Power-on Reset occurred

0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

### bit 0 BOR: Brown-out Reset Status bit

1 = No Brown-out Reset occurred

0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### 3.0 DATA EEPROM AND FLASH PROGRAM MEMORY

The Data EEPROM and FLASH Program Memory are readable and writable during normal operation over the entire VDD range. These operations take place on a single byte for Data EEPROM memory and a single word for Program memory. A write operation causes an erase-then-write operation to take place on the specified byte or word. A bulk erase operation may not be issued from user code (which includes removing code protection).

Access to program memory allows for checksum calculation. The values written to Program memory do not need to be valid instructions. Therefore, numbers of up to 14 bits can be stored in memory for use as calibration parameters, serial numbers, packed 7-bit ASCII, etc. Executing a program memory location, containing data that forms an invalid instruction, results in the execution of a NOP instruction.

The EEPROM Data memory is rated for high erase/ write cycles (specification #D120). The FLASH Program memory is rated much lower (specification #D130) because EEPROM Data memory can be used to store frequently updated values. An on-chip timer controls the write time and it will vary with voltage and temperature, as well as from chip to chip. Please refer to the specifications for exact limits (specifications #D122 and #D133).

A byte or word write automatically erases the location and writes the new value (erase before write). Writing to EEPROM Data memory does not impact the operation of the device. Writing to Program memory will cease the execution of instructions until the write is complete. The program memory cannot be accessed during the write. During the write operation, the oscillator continues to run, the peripherals continue to function and interrupt events will be detected and essentially "queued" until the write is complete. When the write completes, the next instruction in the pipeline is executed and the branch to the interrupt vector will take place if the interrupt is enabled and occurred during the write.

Read and write access to both memories take place indirectly through a set of Special Function Registers (SFR). The six SFRs used are:

- EEDATA

- EEDATH

- EEADR

- EEADRH

- EECON1

- EECON2

The EEPROM Data memory allows byte read and write operations without interfering with the normal operation of the microcontroller. When interfacing to EEPROM Data memory, the EEADR register holds the address to be accessed. Depending on the operation, the EEDATA register holds the data to be written or the data read at the address in EEADR. The PIC16F872 has 64 bytes of EEPROM Data memory and therefore, requires that the two Most Significant bits of EEADR remain clear. EEPROM Data memory on these devices wraps around to 0 (i.e., 40h in the EEADR maps to 00h).

The FLASH Program memory allows non-intrusive read access, but write operations cause the device to stop executing instructions until the write completes. When interfacing to the Program memory, the EEADRH:EEADR registers pair forms a two-byte word which holds the 13-bit address of the memory location being accessed. The EEDATH:EEDATA register pair holds the 14-bit data for writes or reflects the value of program memory after a read operation. Just as in EEPROM Data memory accesses, the value of the EEADRH:EEADR registers must be within the valid range of program memory, depending on the device (0000h to 07FFh). Addresses outside of this range wrap around to 0000h (i.e., 0800h maps to 0000h).

### 3.1 EECON1 and EECON2 Registers

The EECON1 register is the control register for configuring and initiating the access. The EECON2 register is not a physically implemented register, but is used exclusively in the memory write sequence to prevent inadvertent writes.

There are many bits used to control the read and write operations to EEPROM Data and FLASH Program memory. The EEPGD bit determines if the access will be a program or data memory access. When clear, any subsequent operations will work on the EEPROM Data memory. When set, all subsequent operations will operate in the Program memory.

Read operations only use one additional bit, RD, which initiates the read operation from the desired memory location. Once this bit is set, the value of the desired memory location will be available in the data registers. This bit cannot be cleared by firmware. It is automatically cleared at the end of the read operation. For EEPROM Data memory reads, the data will be available in the EEDATA register in the very next instruction cycle after the RD bit is set. For program memory reads, the data will be loaded into the EEDATH:EEDATA registers, following the second instruction after the RD bit is set.

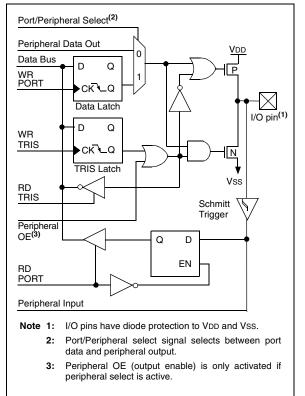

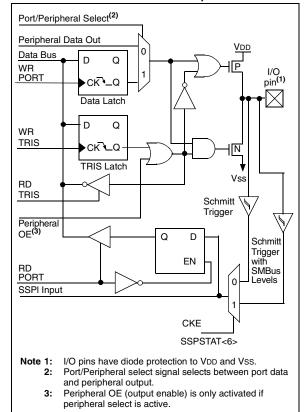

### 4.3 PORTC and the TRISC Register

PORTC is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISC. Setting a TRISC bit (= '1') will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISC bit (= '0') will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

PORTC is multiplexed with several peripheral functions (Table 4-5). PORTC pins have Schmitt Trigger input buffers.

When the  $l^2C$  module is enabled, the PORTC (4:3) pins can be configured with normal  $l^2C$  levels or with SMBus levels by using the CKE bit (SSPSTAT<6>).

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modify-write instructions (BSF, BCF, XORWF) with TRISC as the destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

### FIGURE 4-5: PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE) RC<2:0> RC<7:5>

### FIGURE 4-6:

### PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE) RC<4:3>

### TABLE 4-5:PORTC FUNCTIONS

| Name            | Bit# | Buffer Type | Function                                                                                            |

|-----------------|------|-------------|-----------------------------------------------------------------------------------------------------|

| RC0/T1OSO/T1CKI | bit0 | ST          | Input/output port pin or Timer1 oscillator output/Timer1 clock input.                               |

| RC1/T1OSI/CCP2  | bit1 | ST          | Input/output port pin or Timer1 oscillator input or Capture2 input/<br>Compare2 output/PWM2 output. |

| RC2/CCP1        | bit2 | ST          | Input/output port pin or Capture1 input/Compare1 output/<br>PWM output.                             |

| RC3/SCK/SCL     | bit3 | ST          | RC3 can also be the synchronous serial clock for both SPI and $I^2C$ modes.                         |

| RC4/SDI/SDA     | bit4 | ST          | RC4 can also be the SPI Data In (SPI mode) or Data I/O (I <sup>2</sup> C mode).                     |

| RC5/SDO         | bit5 | ST          | Input/output port pin or Synchronous Serial Port data output (SPI mode).                            |

| RC6             | bit6 | ST          | Input/output port pin.                                                                              |

| RC7             | bit7 | ST          | Input/output port pin.                                                                              |

Legend: ST = Schmitt Trigger input

### TABLE 4-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Address | Name                                | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|---------|-------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 07h     | PORTC                               | RC7   | RC6   | RC5   | RC4   | RC3   | RC2   | RC1   | RC0   | XXXX XXXX                | uuuu uuuu                       |

| 87h     | TRISC PORTC Data Direction Register |       |       |       |       |       |       |       |       | 1111 1111                | 1111 1111                       |

Legend: x = unknown, u = unchanged

### 5.2 Using Timer0 with an External Clock

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for TOCKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

### 5.3 Prescaler

There is only one prescaler available, which is mutually exclusively shared between the Timer0 module and the Watchdog Timer. A prescaler assignment for the

### **REGISTER 5-1: OPTION\_REG REGISTER**

Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa. This prescaler is not readable or writable (see Figure 5-1).

The PSA and PS2:PS0 bits (OPTION REG<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g. CLRF1, MOVWF1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

Note: Writing to TMR0, when the prescaler is assigned to Timer0, will clear the prescaler count, but will not change the prescaler assignment.

|         | R/W-1                                                | R/W-1                                                                                                                                                                                              | R/W-1                                                     | R/W-1       | R/W-1    | R/W-1     | R/W-1                | R/W-1 |  |  |  |  |  |

|---------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-------------|----------|-----------|----------------------|-------|--|--|--|--|--|

|         | RBPU                                                 | INTEDG                                                                                                                                                                                             | TOCS                                                      | T0SE        | PSA      | PS2       | PS1                  | PS0   |  |  |  |  |  |

|         | bit 7                                                |                                                                                                                                                                                                    |                                                           |             |          |           |                      | bit 0 |  |  |  |  |  |

|         |                                                      |                                                                                                                                                                                                    |                                                           |             |          |           |                      |       |  |  |  |  |  |

| bit 7   | RBPU                                                 |                                                                                                                                                                                                    |                                                           |             |          |           |                      |       |  |  |  |  |  |

| bit 6   | INTEDG                                               |                                                                                                                                                                                                    |                                                           |             |          |           |                      |       |  |  |  |  |  |

| bit 5   | 1 = Transi                                           | R0 Clock Sou<br>tion on T0CK<br>al instruction o                                                                                                                                                   | l pin                                                     |             |          |           |                      |       |  |  |  |  |  |

| bit 4   | 1 = Increm                                           | <b>TOSE</b> : TMR0 Source Edge Select bit<br>1 = Increment on high-to-low transition on T0CKI pin<br>0 = Increment on low-to-high transition on T0CKI pin<br><b>PSA</b> : Presseler Assignment bit |                                                           |             |          |           |                      |       |  |  |  |  |  |

| bit 3   | 1 = Presca                                           | <ul> <li>PSA: Prescaler Assignment bit</li> <li>1 = Prescaler is assigned to the WDT</li> <li>0 = Prescaler is assigned to the Timer0 module</li> </ul>                                            |                                                           |             |          |           |                      |       |  |  |  |  |  |

| bit 2-0 | PS2:PS0:                                             | Prescaler Ra                                                                                                                                                                                       | te Select bi                                              | ts          |          |           |                      |       |  |  |  |  |  |

|         | Bit Value                                            | TMR0 Rate                                                                                                                                                                                          | WDT Rate                                                  |             |          |           |                      |       |  |  |  |  |  |

|         | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | 1:2<br>1:4<br>1:8<br>1:16<br>1:32<br>1:64<br>1:128<br>1:256                                                                                                                                        | 1:1<br>1:2<br>1:4<br>1:8<br>1:16<br>1:32<br>1:64<br>1:128 |             |          |           |                      |       |  |  |  |  |  |

|         | Legend:                                              |                                                                                                                                                                                                    |                                                           |             |          |           |                      |       |  |  |  |  |  |

|         | R = Reada                                            | able bit                                                                                                                                                                                           | W = W                                                     | ritable bit | U = Unin | plemented | bit, read as         | '0'   |  |  |  |  |  |

|         | - n = Value                                          |                                                                                                                                                                                                    | '1' = Bit is set '0' = Bit is cleare                      |             |          |           | d x = Bit is unknown |       |  |  |  |  |  |

Note: To avoid an unintended device RESET, the instruction sequence shown in the PICmicro™ Mid-Range MCU Family Reference Manual (DS33023) must be executed when changing the prescaler assignment from Timer0 to the WDT. This sequence must be followed even if the WDT is disabled.

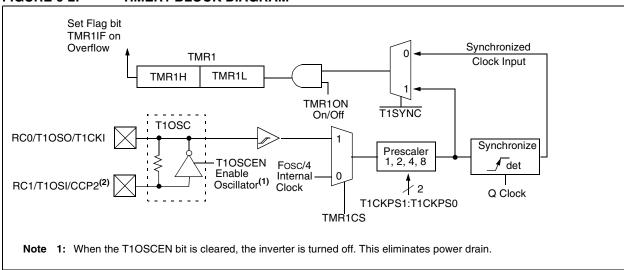

### 6.0 TIMER1 MODULE

The Timer1 module is a 16-bit timer/counter consisting of two 8-bit registers (TMR1H and TMR1L), which are readable and writable. The TMR1 Register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 Interrupt, if enabled, is generated on overflow, which is latched in interrupt flag bit TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing TMR1 interrupt enable bit TMR1IE (PIE1<0>).

Timer1 can operate in one of two modes:

- As a Timer

- As a Counter

The operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

In Timer mode, Timer1 increments every instruction cycle. In Counter mode, it increments on every rising edge of the external clock input.

Timer1 can be enabled/disabled by setting/clearing control bit TMR1ON (T1CON<0>).

Timer1 also has an internal "RESET input". This RESET can be generated by either of the two CCP modules (Section 8.0). Register 6-1 shows the Timer1 control register.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RC1/T1OSI/CCP2 and RC0/T1OSO/T1CKI pins become inputs. That is, the TRISC<1:0> value is ignored, and these pins read as '0'.

Additional information on timer modules is available in the PICmicro<sup>™</sup> Mid-range MCU Family Reference Manual (DS33023).

| -       |                                                                      |                                                                                                                                                      | -             | (             |                 | - /          |              |        |  |  |  |

|---------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|-----------------|--------------|--------------|--------|--|--|--|

|         | U-0                                                                  | U-0                                                                                                                                                  | R/W-0         | R/W-0         | R/W-0           | R/W-0        | R/W-0        | R/W-0  |  |  |  |

|         | —                                                                    | _                                                                                                                                                    | T1CKPS1       | T1CKPS0       | T1OSCEN         | T1SYNC       | TMR1CS       | TMR10N |  |  |  |

|         | bit 7                                                                |                                                                                                                                                      |               |               |                 |              |              | bit 0  |  |  |  |

| bit 7-6 | Unimpleme                                                            | nted: Bea                                                                                                                                            | d as '0'      |               |                 |              |              |        |  |  |  |

| bit 5-4 | -                                                                    |                                                                                                                                                      |               | + Clask Dress | aala Calaat k   | ita          |              |        |  |  |  |

| DIT 5-4 | 11 = 1:8 Pre<br>10 = 1:4 Pre<br>01 = 1:2 Pre<br>00 = 1:1 Pre         | escale value<br>escale value<br>escale value                                                                                                         | e<br>e<br>e   | I CIUCK FIES  | cale Select b   | 115          |              |        |  |  |  |

| bit 3   | T1OSCEN:                                                             | Timer1 Os                                                                                                                                            | cillator Enab | ble Control b | it              |              |              |        |  |  |  |

|         | 1 = Oscillato<br>0 = Oscillato                                       |                                                                                                                                                      | -             | ator inverter | is turned off   | to eliminate | e power drai | n)     |  |  |  |

| bit 2   | When TMR                                                             | <b>T1SYNC</b> : Timer1 External Clock Input Synchronization Control bit         When TMR1CS = 1:         1 = Do not synchronize external clock input |               |               |                 |              |              |        |  |  |  |

|         |                                                                      | 0 = Synchronize external clock input                                                                                                                 |               |               |                 |              |              |        |  |  |  |

|         | When TMR <sup>-</sup>                                                | When TMR1CS = 0:                                                                                                                                     |               |               |                 |              |              |        |  |  |  |

|         | This bit is ignored. Timer1 uses the internal clock when TMR1CS = 0. |                                                                                                                                                      |               |               |                 |              |              |        |  |  |  |

| bit 1   | <b>TMR1CS</b> : T                                                    |                                                                                                                                                      |               |               | I (on the risir | ng edge)     |              |        |  |  |  |

|         | 0 = Internal                                                         |                                                                                                                                                      |               |               | Υ.              | 0 0 /        |              |        |  |  |  |

| bit 0   | TMR1ON: T                                                            | ïmer1 On b                                                                                                                                           | oit           |               |                 |              |              |        |  |  |  |

|         | 1 = Enables<br>0 = Stops Ti                                          |                                                                                                                                                      |               |               |                 |              |              |        |  |  |  |

|         |                                                                      |                                                                                                                                                      |               |               |                 |              |              |        |  |  |  |

|         | Legend:                                                              |                                                                                                                                                      |               |               |                 |              |              |        |  |  |  |

|         | R = Readab                                                           | le bit                                                                                                                                               | W = W         | /ritable bit  | U = Unim        | plemented    | bit, read as | '0'    |  |  |  |

|         | - n = Value a                                                        | at POR                                                                                                                                               | '1' = B       | it is set     | '0' = Bit is    | cleared      | x = Bit is u | nknown |  |  |  |

### REGISTER 6-1: T1CON: TIMER1 CONTROL REGISTER (ADDRESS 10h)

### 6.1 Timer1 Operation in Timer Mode

Timer mode is selected by clearing the TMR1CS (T1CON<1>) bit. In this mode, the input clock to the timer is FOSC/4. The synchronize control bit  $\overline{T1SYNC}$  (T1CON<2>) has no effect since the internal clock is always in sync.

### 6.2 Timer1 Counter Operation

Timer1 may operate in either a Synchronous or an Asynchronous mode, depending on the setting of the TMR1CS bit.

When Timer1 is being incremented via an external source, increments occur on a rising edge. After Timer1 is enabled in Counter mode, the module must first have a falling edge before the counter begins to increment.

# FIGURE 6-1: TIMER1 INCREMENTING EDGE

### 6.3 Timer1 Operation in Synchronized Counter Mode

Counter mode is selected by setting bit TMR1CS. In this mode, the timer increments on every rising edge of clock input on pin RC1/T1OSI/CCP2, when bit T1OSCEN is set, or on pin RC0/T1OSO/T1CKI, when bit T1OSCEN is cleared.

If  $\overline{T1SYNC}$  is cleared, then the external clock input is synchronized with internal phase clocks. The synchronization is done after the prescaler stage. The prescaler stage is an asynchronous ripple counter.

In this configuration, during SLEEP mode, Timer1 will not increment even if the external clock is present, since the synchronization circuit is shut-off. The prescaler, however, will continue to increment.

### FIGURE 6-2: TIMER1 BLOCK DIAGRAM

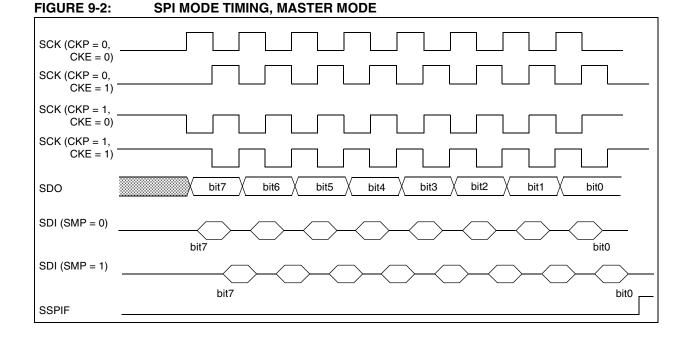

The clock polarity is selected by appropriately programming bit CKP (SSPCON<4>). This, then, would give waveforms for SPI communication as shown in Figure 9-6, Figure 9-8 and Figure 9-9, where the MSb is transmitted first. In Master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 Tcy)

- Fosc/64 (or 16 Tcy)

- Timer2 Output/2

This allows a maximum bit clock frequency (at 20 MHz) of 5.0 MHz.

Figure 9-6 shows the waveforms for Master mode. When CKE = 1, the SDO data is valid before there is a clock edge on SCK. The change of the input sample is shown based on the state of the SMP bit. The time when the SSPBUF is loaded with the received data is shown.

### 9.1.2 SLAVE MODE

In Slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched, the interrupt flag bit SSPIF (PIR1<3>) is set.

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times, as specified in the electrical specifications. While in SLEEP mode, the slave can transmit/receive data. When a byte is received, the device will wake-up from SLEEP.

- Note 1: When the SPI module is in Slave mode with SS pin control enabled (SSPCON<3:0> = 0100), the SPI module will reset if the SS pin is set to VDD.

- **2:** If the SPI is used in Slave mode with CKE = '1', then  $\overline{SS}$  pin control must be enabled.

### 9.2.3 SLEEP OPERATION

While in SLEEP mode, the  $I^2C$  module can receive addresses or data. When an address match or complete byte transfer occurs, wake the processor from SLEEP (if the SSP interrupt is enabled).

### 9.2.4 EFFECTS OF A RESET

A RESET disables the SSP module and terminates the current transfer.

| Address                | Name    | Bit 7     | Bit 6        | Bit 5       | Bit 4    | Bit 3     | Bit 2   | Bit 1  | Bit 0  | Value<br>PC<br>BC | R,   | all o | e on<br>ther<br>ETS |

|------------------------|---------|-----------|--------------|-------------|----------|-----------|---------|--------|--------|-------------------|------|-------|---------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON  | GIE       | PEIE         | TMR0IE      | INTE     | RBIE      | TMR0IF  | INTF   | RBIF   | 0000              | 000x | 0000  | 000u                |

| 0Ch                    | PIR1    | (1)       | ADIF         | (1)         | (1)      | SSPIF     | CCP1IF  | TMR2IF | TMR1IF | 0000              | 0000 | 0000  | 0000                |

| 8Ch                    | PIE1    | (1)       | ADIE         | (1)         | (1)      | SSPIE     | CCP1IE  | TMR2IE | TMR1IE | r0rr              | 0000 | 0000  | 0000                |

| 0Dh                    | PIR2    | —         | (1)          | _           | EEIF     | BCLIF     | —       | (1)    | CCP2IF | -r-0              | 0 0  | -r-0  | 0 0                 |

| 8Dh                    | PIE2    | —         | (1)          | _           | EEIE     | BCLIE     | —       | (1)    | CCP2IE | -r-0              | 0r   | -r-0  | 0r                  |

| 13h                    | SSPBUF  | Synchrono | us Serial Po | ort Receive | Buffer/T | ransmit R | egister |        |        | xxxx              | xxxx | uuuu  | uuuu                |

| 14h                    | SSPCON  | WCOL      | SSPOV        | SSPEN       | CKP      | SSPM3     | SSPM2   | SSPM1  | SSPM0  | 0000              | 0000 | 0000  | 0000                |

| 91h                    | SSPCON2 | GCEN      | ACKSTAT      | ACKDT       | ACKEN    | RCEN      | PEN     | RSEN   | SEN    | 0000              | 0000 | 0000  | 0000                |

| 94h                    | SSPSTAT | SMP       | CKE          | D/A         | Р        | S         | R/W     | UA     | BF     | 0000              | 0000 | 0000  | 0000                |

# TABLE 9-3: REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the SSP in I<sup>2</sup>C mode. Note 1: These bits are reserved; always maintain these bits clear.

### 9.2.5 MASTER MODE

Master mode of operation is supported by interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared from a RESET or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is IDLE, with both the S and P bits clear.

In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware.

The following events will cause the SSP Interrupt Flag bit, SSPIF, to be set (an SSP Interrupt will occur if enabled):

- START condition

- STOP condition

- · Data transfer byte transmitted/received

- Acknowledge transmit

- Repeated START

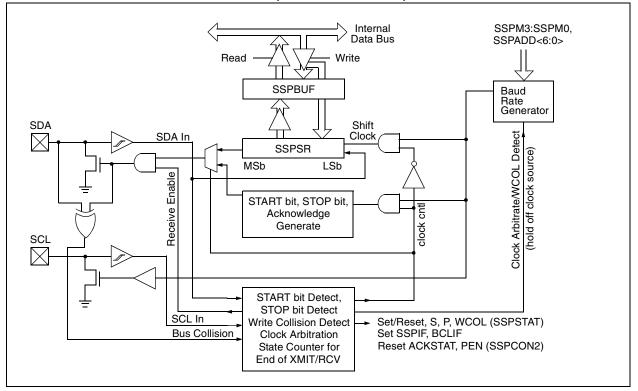

# FIGURE 9-9: SSP BLOCK DIAGRAM (I<sup>2</sup>C MASTER MODE)

### 9.2.6 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the START and STOP conditions allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a RESET or when the MSSP module is disabled. Control of the I<sup>2</sup>C bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is IDLE with both the S and P bits clear. When the bus is busy, enabling the SSP interrupt will generate the interrupt when the STOP condition occurs.

In Multi-Master operation, the SDA line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed in hardware, with the result placed in the BCLIF bit. The states where arbitration can be lost are:

- Address Transfer

- Data Transfer

- A START Condition

- A Repeated START Condition

- An Acknowledge Condition

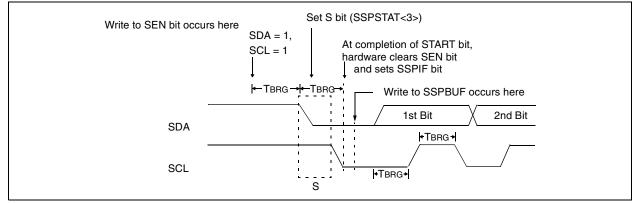

### 9.2.9 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

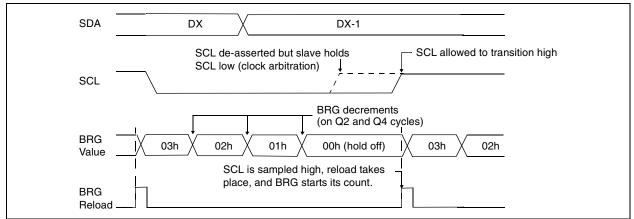

To initiate a START condition, the user sets the START condition enable bit, SEN (SSPCON2<0>). If the SDA and SCL pins are sampled high, the baud rate generator is reloaded with the contents of SSPADD<6:0> and starts its count. If SCL and SDA are both sampled high when the baud rate generator times out (TBRG), the SDA pin is driven low. The action of the SDA being driven low while SCL is high is the START condition, and causes the S bit (SSPSTAT<3>) to be set. Following this, the baud rate generator is reloaded with the contents of SSPADD<6:0> and resumes its count. When the baud rate generator times out (TBRG), the SEN bit (SSPCON2<0>) will be automatically cleared by hardware. The baud rate generator is suspended, leaving the SDA line held low, and the START condition is complete.

Note: If, at the beginning of START condition, the SDA and SCL pins are already sampled low, or if during the START condition, the SCL line is sampled low before the SDA line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag (BCLIF) is set, the START condition is aborted, and the I<sup>2</sup>C module is reset into its IDLE state.

### 9.2.9.1 WCOL Status Flag

If the user writes the SSPBUF when a START sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

**Note:** Because queueing of events is not allowed, writing to the lower 5 bits of SSPCON2 is disabled until the START condition is complete.

### FIGURE 9-12: FIRST START BIT TIMING

## 10.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The Analog-to-Digital (A/D) Converter module has five input channels. The analog input charges a sample and hold capacitor. The output of the sample and hold capacitor is the input into the converter. The converter then generates a digital result of this analog level via successive approximation. The A/D conversion of the analog input signal results in a corresponding 10-bit digital number. The A/D module has high and low voltage reference input that is software selectable to some combination of VDD, Vss, RA2 or RA3.

The A/D converter has a unique feature of being able to operate while the device is in SLEEP mode. To operate in SLEEP, the A/D clock must be derived from the A/D's internal RC oscillator. The A/D module has four registers. These registers are:

- A/D Result High Register (ADRESH)

- A/D Result Low Register (ADRESL)

- A/D Control Register0 (ADCON0)

- A/D Control Register1 (ADCON1)

The ADCON0 register, shown in Register 10-1, controls the operation of the A/D module. The ADCON1 register, shown in Register 10-2, configures the functions of the port pins. The port pins can be configured as analog inputs (RA3 can also be the voltage reference), or as digital I/O.

Additional information on using the A/D module can be found in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023).

|         | R/W-0                                 | R/W-0                        | R/W-0          | R/W-0             | R/W-0       | R/W-0                         | U-0           | R/W-0      |  |  |  |  |

|---------|---------------------------------------|------------------------------|----------------|-------------------|-------------|-------------------------------|---------------|------------|--|--|--|--|

|         | ADCS1                                 | ADCS0                        | CHS2           | CHS1              | CHS0        | GO/DONE                       |               | ADON       |  |  |  |  |

|         | bit 7                                 |                              |                |                   |             |                               |               | bit 0      |  |  |  |  |

|         |                                       |                              |                |                   |             |                               |               |            |  |  |  |  |

| bit 7-6 | ADCS1:AD                              | DCS0: A/D C                  | onversion C    | lock Select       | bits        |                               |               |            |  |  |  |  |

|         | 00 = Fosc/                            | _                            |                |                   |             |                               |               |            |  |  |  |  |

|         | 01 = Fosc/<br>10 = Fosc/              |                              |                |                   |             |                               |               |            |  |  |  |  |

|         |                                       |                              | d from the in  | ternal A/D m      | nodule RC c | oscillator)                   |               |            |  |  |  |  |

| bit 5-3 | CHS2:CHS0: Analog Channel Select bits |                              |                |                   |             |                               |               |            |  |  |  |  |

|         |                                       | nnel 0 (RA0/                 | ,              |                   |             |                               |               |            |  |  |  |  |

|         |                                       | nnel 1 (RA1)<br>nnel 2 (RA2) | ,              |                   |             |                               |               |            |  |  |  |  |

|         |                                       | nnel 3 (RA3/                 | ,              |                   |             |                               |               |            |  |  |  |  |

|         |                                       | nnel 4 (RA5/                 | ,              |                   |             |                               |               |            |  |  |  |  |

| bit 2   | GO/DONE:                              | A/D Conve                    | rsion Status   | bit               |             |                               |               |            |  |  |  |  |

|         | If ADON =                             |                              |                |                   |             | <u> </u>                      |               |            |  |  |  |  |

|         |                                       |                              |                |                   |             | D conversion<br>cleared by ha |               | on the A/D |  |  |  |  |

|         |                                       | sion is comp                 |                | (נו ווס טונ וס מנ | lomatically | cleared by h                  |               | en the A/D |  |  |  |  |