Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 64 x 8                                                                    |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | A/D 5x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 28-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f872t-i-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, microID, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, PowerSmart, rfPIC and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AmpLab, FilterLab, Migratable Memory, MXDEV, MXLAB, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, ECAN, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, Linear Active Thermistor, Mindi, MiWi, MPASM, MPLIB, MPLINK, PICkit, PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, rfPICDEM, Select Mode, Smart Serial, SmartTel, Total Endurance, UNI/O, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2006, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona, Gresham, Oregon and Mountain View, California. The Company's quality system processes and procedures are for its PICmicro® 8-bit MCUs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

#### 2.2.2.1 STATUS Register

The STATUS register contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable, therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as  $000u \ u1uu$  (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions not affecting any status bits, see the "Instruction Set Summary."

| Note: | The C and DC bits operate as a borrow       |

|-------|---------------------------------------------|

|       | and digit borrow bit, respectively, in sub- |

|       | traction. See the SUBLW and SUBWF           |

|       | instructions for examples.                  |

#### REGISTER 2-1: STATUS REGISTER (ADDRESS: 03h, 83h, 103h, 183h)

|         | R/W-0              | R/W-0                            | R/W-0          | R-1           | R-1                                              | R/W-x         | R/W-x          | R/W-x |

|---------|--------------------|----------------------------------|----------------|---------------|--------------------------------------------------|---------------|----------------|-------|

|         | IRP                | RP1                              | RP0            | TO            | PD                                               | Z             | DC             | С     |

|         | bit 7              |                                  |                |               |                                                  |               |                | bit 0 |

|         |                    |                                  |                |               |                                                  |               |                |       |

| bit 7   | -                  |                                  | -              | d for indirec | t addressing                                     | )             |                |       |

|         |                    | 2, 3 (100h - 1<br>), 1 (00h - Ff | ,              |               |                                                  |               |                |       |

| bit 6:5 | RP1:RP0:           | Register Ba                      | nk Select bit  | s (used for   | direct addres                                    | ssing)        |                |       |

|         |                    | 3 (180h - 1F                     | ,              |               |                                                  |               |                |       |

|         |                    | 2 (100h - 17<br>1 (80h - FFI     | ,              |               |                                                  |               |                |       |

|         |                    | 0 (00h - 7Fi                     | ,              |               |                                                  |               |                |       |

|         | Each bank          | is 128 bytes                     | S              |               |                                                  |               |                |       |

| bit 4   | TO: Time-o         |                                  |                |               |                                                  |               |                |       |

|         |                    | ower-up, CL<br>I time-out oc     |                | ction, or SLI | EEP instruction                                  | on            |                |       |

| bit 3   | PD: Power          | r-down bit                       |                |               |                                                  |               |                |       |

|         |                    | ower-up or t<br>ecution of the   |                |               | on                                               |               |                |       |

| bit 2   | Z: Zero bit        |                                  |                |               |                                                  |               |                |       |

|         |                    | sult of an ari<br>sult of an ari |                | •             | on is zero<br>on is not zero                     | D             |                |       |

| bit 1   | DC: Digit o        | arry/borrow                      | bit (ADDWF, 2  | ADDLW,SUE     | BLW, SUBWF I                                     | instructions) |                |       |

|         | (for borrow        | the polarity                     | is reversed)   |               |                                                  |               |                |       |

|         |                    | /-out from th<br>ry-out from t   |                |               | e result occu<br>ne result                       | rred          |                |       |

| bit 0   | <b>C</b> : Carry/b | orrow bit (AI                    | DWF, ADDLW     | , SUBLW, SI   | JBWF instru                                      | ctions)       |                |       |

|         |                    |                                  |                |               | the result or<br>of the result of                |               |                |       |

|         | Note:              | complemen                        | nt of the seco | ond operand   | . A subtracti<br>d. For rotate<br>rder bit of th | (RRF, RLF     | ) instruction  |       |

|         | Legend:            |                                  |                |               |                                                  |               |                |       |

|         | R = Reada          | able bit                         | W = W          | ritable bit   | U = Unin                                         | nplemented    | bit, read as ' | 0'    |

'1' = Bit is set

- n = Value at POR

x = Bit is unknown

'0' = Bit is cleared

## PIC16F872

#### 2.2.2.5 PIR1 Register

The PIR1 register contains the individual flag bits for the peripheral interrupts.

# Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt bits are clear prior to enabling an interrupt.

#### REGISTER 2-5: PIR1 REGISTER (ADDRESS: 0Ch)

| R/W-0    | R/W-0 | R/W-0    | R/W-0    | R/W-0 | R/W-0  | R/W-0  | R/W-0  |

|----------|-------|----------|----------|-------|--------|--------|--------|

| reserved | ADIF  | reserved | reserved | SSPIF | CCP1IF | TMR2IF | TMR1IF |

| bit 7    |       |          |          |       |        |        | bit 0  |

- bit 7 Reserved: Always maintain these bits clear

- bit 6 ADIF: A/D Converter Interrupt Flag bit

- 1 = An A/D conversion completed

- 0 = The A/D conversion is not complete

- bit 5-4 Reserved: Always maintain these bits clear

- bit 3 SSPIF: Synchronous Serial Port (SSP) Interrupt Flag

- 1 = The SSP interrupt condition has occurred, and must be cleared in software before returning from the Interrupt Service Routine. The conditions that will set this bit are:

- SPI

- A transmission/reception has taken place

- I<sup>2</sup>C Slave

- A transmission/reception has taken place

- I<sup>2</sup>C Master

- A transmission/reception has taken place

- The initiated START condition was completed by the SSP module

- The initiated STOP condition was completed by the SSP module

- The initiated Restart condition was completed by the SSP module

- The initiated Acknowledge condition was completed by the SSP module

- A START condition occurred while the SSP module was idle (multi-master system)

- A STOP condition occurred while the SSP module was idle (multi-master system)

- 0 = No SSP interrupt condition has occurred

- bit 2 CCP1IF: CCP1 Interrupt Flag bit

Capture mode:

- 1 = A TMR1 register capture occurred (must be cleared in software)

- 0 = No TMR1 register capture occurred

Compare mode:

- 1 = A TMR1 register compare match occurred (must be cleared in software)

- 0 = No TMR1 register compare match occurred

- PWM mode: Unused in this mode

- bit 1 **TMR2IF**: TMR2 to PR2 Match Interrupt Flag bit

- 1 = TMR2 to PR2 match occurred (must be cleared in software)

- 0 = No TMR2 to PR2 match occurred

#### bit 0 TMR1IF: TMR1 Overflow Interrupt Flag bit

- 1 = TMR1 register overflowed (must be cleared in software)

- 0 = TMR1 register did not overflow

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

Write operations have two control bits, WR and WREN. and two status bits, WRERR and EEIF. The WREN bit is used to enable or disable the write operation. When WREN is clear, the write operation will be disabled. Therefore, the WREN bit must be set before executing a write operation. The WR bit is used to initiate the write operation. It also is automatically cleared at the end of the write operation. The interrupt flag EEIF (located in register PIR2) is used to determine when the memory write completes. This flag must be cleared in software before setting the WR bit. For EEPROM Data memory, once the WREN bit and the WR bit have been set, the desired memory address in EEADR will be erased followed by a write of the data in EEDATA. This operation takes place in parallel with the microcontroller continuing to execute normally. When the write is complete, the EEIF flag bit will be set. For program memory, once the WREN bit and the WR bit have been set, the microcontroller will cease to execute instructions. The

desired memory location pointed to by EEADRH:EEADR will be erased. Then the data value in EEDATH:EEDATA will be programmed. When complete, the EEIF flag bit will be set and the microcontroller will continue to execute code.

The WRERR bit is used to indicate when the device has been RESET during a write operation. WRERR should be cleared after Power-on Reset. Thereafter, it should be checked on any other RESET. The WRERR bit is set when a write operation is interrupted by a MCLR Reset or a WDT Time-out Reset during normal operation. In these situations, following a RESET, the user should check the WRERR bit and rewrite the memory location if set. The contents of the data registers, address registers and EEPGD bit are not affected by either MCLR Reset or WDT Time-out Reset during normal operation.

#### REGISTER 3-1: EECON1 REGISTER (ADDRESS 18Ch)

| -       |                |                | · -           | ,             |              |               |               |           |

|---------|----------------|----------------|---------------|---------------|--------------|---------------|---------------|-----------|

|         | R/W-x          | U-0            | U-0           | U-0           | R/W-x        | R/W-0         | R/S-0         | R/S-0     |

|         | EEPGD          | _              | —             | _             | WRERR        | WREN          | WR            | RD        |

|         | bit 7          |                |               |               |              |               |               | bit 0     |

|         |                |                |               |               |              |               |               |           |

| bit 7   | EEPGD: Pr      | ogram/Data     | a EEPROM S    | Select bit    |              |               |               |           |

|         |                | es Program     |               |               |              |               |               |           |

|         |                | es data mei    |               | a read or wri | to operation | ie in progra  |               |           |

| bit 6-4 |                |                | •             |               |              | ris in piogre |               |           |

| bit 3   | WRERR: E       |                |               |               |              |               |               |           |

| DIT 5   |                |                | •             | y terminated  |              |               |               |           |

|         |                |                | •             | Reset during  |              | eration)      |               |           |

|         | • •            |                | n completed   | ·             | 5            | ,             |               |           |

| bit 2   | WREN: EE       | PROM Writ      | e Enable bit  |               |              |               |               |           |

|         |                | write cycles   |               |               |              |               |               |           |

|         |                | write to the   | EEPROM        |               |              |               |               |           |

| bit 1   | WR: Write      |                |               |               |              |               |               |           |

|         |                | -              | •             | s cleared by  | hardware o   | nce write is  | complete. T   | he WR bit |

|         |                | •              | t cleared) in |               |              |               |               |           |

| bit 0   | RD: Read (     | •              |               |               |              |               |               |           |

|         | 1 = Initiates  | an EEPRC       | DM read RD    | is cleared in | hardware.    | The RD bit o  | can only be a | set (not  |

|         |                | ) in software  |               |               |              |               |               | ,         |

|         | 0 = Does n     | ot initiate ar | EEPROM I      | read          |              |               |               |           |

|         |                |                |               |               |              |               |               |           |

|         | Legend:        |                |               |               |              |               |               |           |

|         | S = Settable   |                | -             | adable bit    |              | W = Writab    | le bit        |           |

|         | U = Unimple    | emented bit    | , read as '0' |               |              | - n = Value   | at POR        |           |

|         | '1' = Bit is s | et             | '0' = Bi      | t is cleared  |              | x = Bit is ur | Iknown        |           |

|         |                |                |               |               |              |               |               |           |

#### 3.8 Operation While Code Protected

The PIC16F872 has two code protect mechanisms, one bit for EEPROM Data memory and two bits for FLASH Program memory. Data can be read and written to the EEPROM Data memory regardless of the state of the code protection bit, CPD. When code protection is enabled, CPD cleared, external access via ICSP is disabled regardless of the state of the program memory code protect bits. This prevents the contents of EEPROM Data memory from being read out of the device.

The state of the program memory code protect bits, CP0 and CP1, do not affect the execution of instructions out of program memory. The PIC16F872 can always read the values in program memory, regardless of the state of the code protect bits. However, the state of the code protect bits and the WRT bit will have different effects on writing to program memory. Table 4-1 shows the effect of the code protect bits and the WRT bit on program memory.

Once code protection has been enabled for either EEPROM Data memory or FLASH Program memory, only a full erase of the entire device will disable code protection.

#### 3.9 FLASH Program Memory Write Protection

The configuration word contains a bit that write protects the FLASH Program memory called WRT. This bit can only be accessed when programming the device via ICSP. Once write protection is enabled, only an erase of the entire device will disable it. When enabled, write protection prevents any writes to FLASH Program memory. Write protection does not affect program memory reads.

#### TABLE 3-1: READ/WRITE STATE OF INTERNAL FLASH PROGRAM MEMORY

| Cor | nfiguration | Bits | MomenyLeasticn     | Internal | Internal | ICSP Read |            |  |

|-----|-------------|------|--------------------|----------|----------|-----------|------------|--|

| CP1 | CP0         | WRT  | Memory Location    | Read     | Write    | ICSP Read | ICSP Write |  |

| 0   | 0           | 0    | All program memory | Yes      | No       | No        | No         |  |

| 0   | 0           | 1    | All program memory | Yes      | Yes      | No        | No         |  |

| 1   | 1           | 0    | All program memory | Yes      | No       | Yes       | Yes        |  |

| 1   | 1           | 1    | All program memory | Yes      | Yes      | Yes       | Yes        |  |

| TABLE 3-2:         REGISTERS ASSOCIATED WITH DATA EEPROM/PROGRAM FLASH |

|------------------------------------------------------------------------|

|------------------------------------------------------------------------|

| Address                 | Name   | Bit 7  | Bit 6                                              | Bit 5       | Bit 4    | Bit 3        | Bit 2     | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|-------------------------|--------|--------|----------------------------------------------------|-------------|----------|--------------|-----------|-------|-------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON | GIE    | PEIE                                               | TMR0IE      | INTE     | RBIE         | TMR0IF    | INTF  | RBIF  | 0000 000x                | 0000 000u                       |

| 10Dh                    | EEADR  | EEPROM | Address I                                          | Register, L | ow Byte  |              |           |       |       | xxxx xxxx                | uuuu uuuu                       |

| 10Fh                    | EEADRH | —      | —                                                  | _           | EEPROM   | Address,     | High Byte |       |       | xxxx xxxx                | uuuu uuuu                       |

| 10Ch                    | EEDATA | EEPROM | Data Reg                                           | ister, Low  | Byte     |              |           |       |       | xxxx xxxx                | uuuu uuuu                       |

| 10Eh                    | EEDATH | —      | —                                                  | EEPROM      | Data Reg | jister, High | Byte      |       |       | xxxx xxxx                | uuuu uuuu                       |

| 18Ch                    | EECON1 | EEPGD  |                                                    | _           |          | WRERR        | WREN      | WR    | RD    | x x000                   | x u000                          |

| 18Dh                    | EECON2 | EEPROM | EEPROM Control Register2 (not a physical register) |             |          |              |           |       |       | —                        |                                 |

| 8Dh                     | PIE2   | _      | (1)                                                | —           | EEIE     | BCLIE        | _         | —     | (1)   | -r-0 0r                  | -r-0 0r                         |

| 0Dh                     | PIR2   | —      | (1)                                                | —           | EEIF     | BCLIF        | —         |       | (1)   | -r-0 0r                  | -r-0 0r                         |

Legend: x = unknown, u = unchanged, r = reserved, - = unimplemented, read as '0'. Shaded cells are not used during FLASH/EEPROM access.

Note 1: These bits are reserved; always maintain these bits clear.

#### TABLE 4-5:PORTC FUNCTIONS

| Name            | Bit# | Buffer Type | Function                                                                                            |

|-----------------|------|-------------|-----------------------------------------------------------------------------------------------------|

| RC0/T1OSO/T1CKI | bit0 | ST          | Input/output port pin or Timer1 oscillator output/Timer1 clock input.                               |

| RC1/T1OSI/CCP2  | bit1 | ST          | Input/output port pin or Timer1 oscillator input or Capture2 input/<br>Compare2 output/PWM2 output. |

| RC2/CCP1        | bit2 | ST          | Input/output port pin or Capture1 input/Compare1 output/<br>PWM output.                             |

| RC3/SCK/SCL     | bit3 | ST          | RC3 can also be the synchronous serial clock for both SPI and $I^2C$ modes.                         |

| RC4/SDI/SDA     | bit4 | ST          | RC4 can also be the SPI Data In (SPI mode) or Data I/O (I <sup>2</sup> C mode).                     |

| RC5/SDO         | bit5 | ST          | Input/output port pin or Synchronous Serial Port data output (SPI mode).                            |

| RC6             | bit6 | ST          | Input/output port pin.                                                                              |

| RC7             | bit7 | ST          | Input/output port pin.                                                                              |

Legend: ST = Schmitt Trigger input

#### TABLE 4-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Address | Name                                | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1     | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|---------|-------------------------------------|-------|-------|-------|-------|-------|-------|-----------|-----------|--------------------------|---------------------------------|

| 07h     | PORTC                               | RC7   | RC6   | RC5   | RC4   | RC3   | RC2   | RC1       | RC0       | XXXX XXXX                | uuuu uuuu                       |

| 87h     | TRISC PORTC Data Direction Register |       |       |       |       |       |       | 1111 1111 | 1111 1111 |                          |                                 |

Legend: x = unknown, u = unchanged

#### 6.4 Timer1 Operation in Asynchronous Counter Mode

If control bit  $\overline{T1SYNC}$  (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during SLEEP and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (Section 6.4.1).

In Asynchronous Counter mode, Timer1 cannot be used as a time-base for capture or compare operations.

#### 6.4.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will guarantee a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. Examples 12-2 and 12-3 in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023) show how to read and write Timer1 when it is running in Asynchronous mode.

#### 6.5 Timer1 Oscillator

A crystal oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low power oscillator, rated up to 200 kHz. It will continue to run during SLEEP. It is primarily intended for use with a 32 kHz crystal. Table 6-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

## TABLE 6-1:CAPACITOR SELECTION FOR<br/>THE TIMER1 OSCILLATOR

| Osc Type                            | Freq                                                                       | C2                                                                                                      |                                                         |

|-------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| LP                                  | 32 kHz                                                                     | 33 pF                                                                                                   | 33 pF                                                   |

|                                     | 100 kHz                                                                    | 15 pF                                                                                                   | 15 pF                                                   |

|                                     | 200 kHz                                                                    | 15 pF                                                                                                   | 15 pF                                                   |

| These va                            | lues are for o                                                             | design guidaı                                                                                           | nce only.                                               |

|                                     | Crystals                                                                   | Tested:                                                                                                 |                                                         |

| 32.768 kHz                          | Epson C-00                                                                 | 1R32.768K-A                                                                                             | ± 20 PPM                                                |

| 100 kHz                             | Epson C-2                                                                  | 100.00 KC-P                                                                                             | ± 20 PPM                                                |

| 200 kHz                             | STD XTL                                                                    | 200.000 kHz                                                                                             | ± 20 PPM                                                |

| of c<br>tim<br>2: Sin<br>cha<br>res | oscillator, but<br>e.<br>ce each reso<br>aracteristics, t<br>onator/crysta | nce increases<br>also increases<br>nator/crystal h<br>he user should<br>I manufacturei<br>external comp | the start-up<br>as its own<br>consult the<br>for appro- |

#### 6.6 Resetting Timer1 using a CCP Trigger Output

If the CCP1 or CCP2 module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1.

| Note: | The special event triggers from the CCP1 |

|-------|------------------------------------------|

|       | and CCP2 modules will not set interrupt  |

|       | flag bit TMR1IF (PIR1<0>).               |

Timer1 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this RESET operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1 or CCP2, the write will take precedence.

In this mode of operation, the CCPRxH:CCPRxL register pair effectively becomes the period register for Timer1.

#### 6.7 Resetting of Timer1 Register Pair (TMR1H, TMR1L)

TMR1H and TMR1L registers are not reset to 00h on a POR or any other RESET, except by the CCP1 and CCP2 special event triggers.

T1CON register is reset to 00h on a Power-on Reset or a Brown-out Reset, which shuts off the timer and leaves a 1:1 prescale. In all other RESETS, the register is unaffected.

#### 6.8 Timer1 Prescaler

The prescaler counter is cleared on writes to the TMR1H or TMR1L registers.

## PIC16F872

| TER 9-3: | ER 9-3: SSPCON2: SYNC SERIAL PORT CONTROL REGISTER2 (ADDRESS: 91h)                                                                       |                                                                                                                             |             |                |                          |              |                |              |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------|----------------|--------------------------|--------------|----------------|--------------|--|

|          | R/W-0                                                                                                                                    | R/W-0                                                                                                                       | R/W-0       | R/W-0          | R/W-0                    | R/W-0        | R/W-0          | R/W-0        |  |

|          | GCEN                                                                                                                                     | ACKSTAT                                                                                                                     | ACKDT       | ACKEN          | RCEN                     | PEN          | RSEN           | SEN          |  |

|          | bit 7                                                                                                                                    |                                                                                                                             |             |                |                          |              |                | bit 0        |  |

| bit 7    |                                                                                                                                          | neral Call Ena                                                                                                              |             |                |                          |              |                |              |  |

|          |                                                                                                                                          | interrupt whe                                                                                                               | -           | I call address | s (0000h) is             | received in  | the SSPSF      | 2            |  |

|          |                                                                                                                                          | al call address                                                                                                             |             | « 2°° · · ·    |                          |              |                |              |  |

| bit 6    |                                                                                                                                          | Acknowledge                                                                                                                 |             | (In I-C Maste  | er mode on               | y)           |                |              |  |

|          |                                                                                                                                          | <u>Fransmit mode</u><br>wledge was no                                                                                       |             | from aloue     |                          |              |                |              |  |

|          |                                                                                                                                          | wledge was no<br>wledge was re                                                                                              |             |                |                          |              |                |              |  |

| bit 5    |                                                                                                                                          | cknowledge D                                                                                                                |             | -              | ode only)                |              |                |              |  |

| DII J    |                                                                                                                                          | Receive mode                                                                                                                |             |                | oue only)                |              |                |              |  |

|          |                                                                                                                                          | will be transm                                                                                                              |             | the user initi | ates an Δcl              | (nowledge (  | sequence at    | t the end of |  |

|          | a receive.                                                                                                                               | will be transm                                                                                                              |             |                |                          | (ilowieuge ( | sequence a     |              |  |

|          | 1 = Not Ac                                                                                                                               | knowledge                                                                                                                   |             |                |                          |              |                |              |  |

|          | 0 = Acknow                                                                                                                               | •                                                                                                                           |             |                |                          |              |                |              |  |

| bit 4    | ACKEN: A                                                                                                                                 | cknowledge S                                                                                                                | equence E   | nable bit (In  | I <sup>2</sup> C Master  | mode only)   |                |              |  |

|          | In Master F                                                                                                                              | Receive mode                                                                                                                | <u>:</u>    |                |                          |              |                |              |  |

|          | matical                                                                                                                                  | 1 = Initiate Acknowledge sequence on SDA and SCL pins, and transmit ACKDT data bit. Auto-<br>matically cleared by hardware. |             |                |                          |              |                |              |  |

|          |                                                                                                                                          | wledge seque                                                                                                                |             |                |                          |              |                |              |  |

| bit 3    | RCEN: Receive Enable bit (In I <sup>2</sup> C Master mode only).                                                                         |                                                                                                                             |             |                |                          |              |                |              |  |

|          |                                                                                                                                          | <ul> <li>1 = Enables Receive mode for I<sup>2</sup>C</li> <li>0 = Receive IDLE</li> </ul>                                   |             |                |                          |              |                |              |  |

| bit 2    | <b>PEN:</b> STOP Condition Enable bit (In I <sup>2</sup> C Master mode only)                                                             |                                                                                                                             |             |                |                          |              |                |              |  |

|          | SCK Release Control:                                                                                                                     |                                                                                                                             |             |                |                          |              |                |              |  |

|          | <ul> <li>1 = Initiate STOP condition on SDA and SCL pins. Automatically cleared by hardware.</li> <li>0 = STOP condition IDLE</li> </ul> |                                                                                                                             |             |                |                          |              |                |              |  |

| bit 1    | RSEN: Re                                                                                                                                 | peated STAR                                                                                                                 | T Conditior | n Enabled bit  | (In I <sup>2</sup> C Mas | ster mode o  | nly)           |              |  |

|          |                                                                                                                                          |                                                                                                                             |             |                |                          |              |                | d by         |  |

|          | 1 = Initiate Repeated START condition on SDA and SCL pins. Automatically cleared by<br>hardware.                                         |                                                                                                                             |             |                |                          |              |                |              |  |

|          | -                                                                                                                                        | ted START co                                                                                                                |             |                |                          |              |                |              |  |

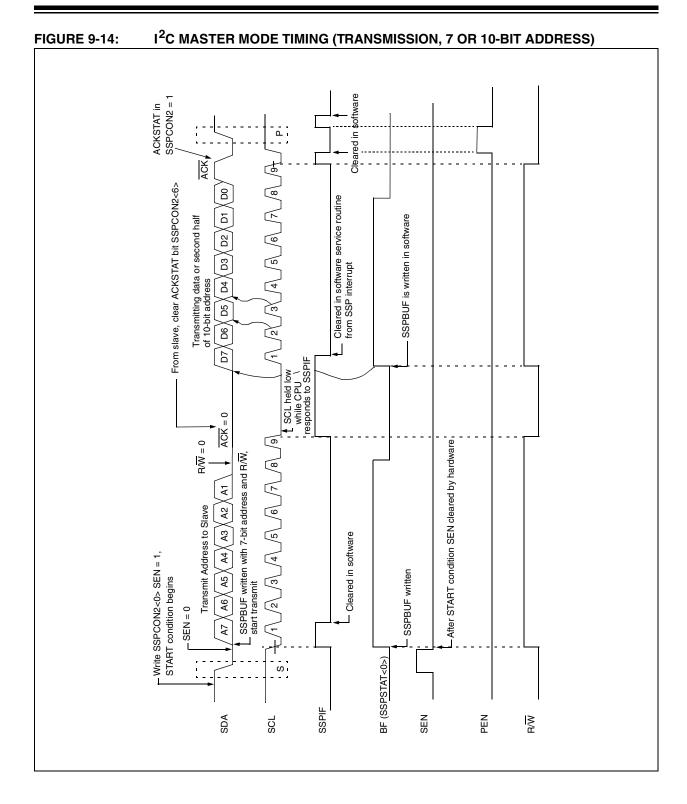

| bit 0    |                                                                                                                                          | RT Condition                                                                                                                |             |                |                          | • ·          |                |              |  |

|          | 0 = START                                                                                                                                | START condi                                                                                                                 | E           |                |                          | -            |                |              |  |

|          | 1                                                                                                                                        | For bits ACKE<br>mode, this bit<br>writes to the S                                                                          | may not be  | set (no spoo   |                          |              |                |              |  |

|          | Legend:                                                                                                                                  |                                                                                                                             |             |                |                          |              |                |              |  |

|          | R = Reada                                                                                                                                | ble bit                                                                                                                     | W = Wr      | ritable bit    | U = Unim                 | plemented I  | oit, read as ' | 0'           |  |

|          | - n = Value                                                                                                                              |                                                                                                                             | '1' = Bit   | is set         | '0' = Bit is             | cleared      | x = Bit is u   | nknown       |  |

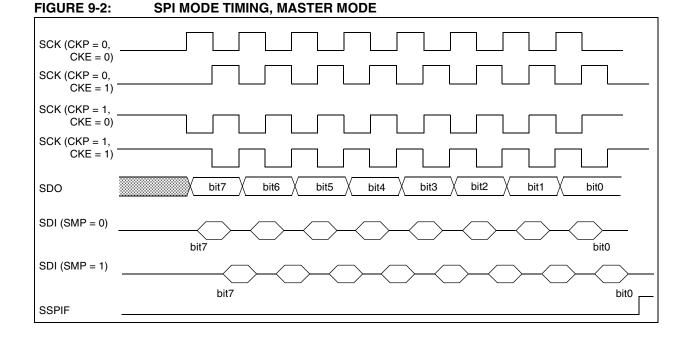

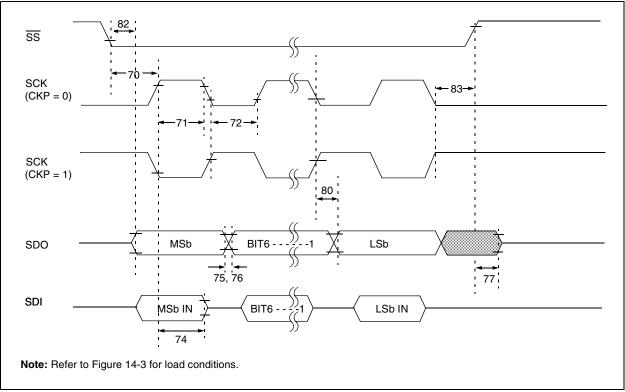

The clock polarity is selected by appropriately programming bit CKP (SSPCON<4>). This, then, would give waveforms for SPI communication as shown in Figure 9-6, Figure 9-8 and Figure 9-9, where the MSb is transmitted first. In Master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 Tcy)

- Fosc/64 (or 16 Tcy)

- Timer2 Output/2

This allows a maximum bit clock frequency (at 20 MHz) of 5.0 MHz.

Figure 9-6 shows the waveforms for Master mode. When CKE = 1, the SDO data is valid before there is a clock edge on SCK. The change of the input sample is shown based on the state of the SMP bit. The time when the SSPBUF is loaded with the received data is shown.

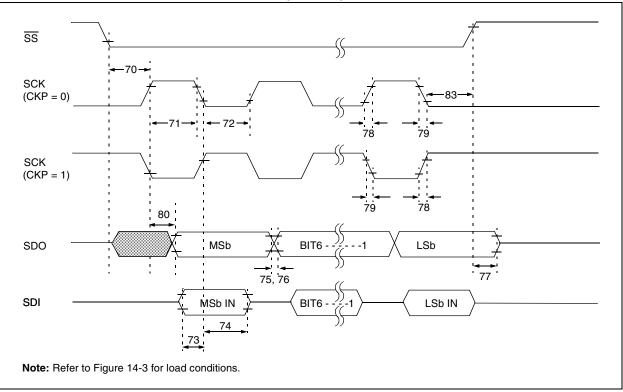

#### 9.1.2 SLAVE MODE

In Slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched, the interrupt flag bit SSPIF (PIR1<3>) is set.

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times, as specified in the electrical specifications. While in SLEEP mode, the slave can transmit/receive data. When a byte is received, the device will wake-up from SLEEP.

- Note 1: When the SPI module is in Slave mode with SS pin control enabled (SSPCON<3:0> = 0100), the SPI module will reset if the SS pin is set to VDD.

- **2:** If the SPI is used in Slave mode with CKE = '1', then  $\overline{SS}$  pin control must be enabled.

There are certain conditions that will cause the MSSP module not to give this  $\overline{\text{ACK}}$  pulse. These are if either (or both):

- a) The buffer full bit BF (SSPSTAT<0>) was set before the transfer was received.

- b) The overflow bit SSPOV (SSPCON<6>) was set before the transfer was received.

If the BF bit is set, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF and SSPOV are set. Table 9-2 shows what happens when a data transfer byte is received, given the status of bits BF and SSPOV. The shaded cells show the condition where user software did not properly clear the overflow condition. Flag bit BF is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and low time for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirement of the MSSP module, is shown in timing parameter #100 and parameter #101 of the electrical specifications.

#### 9.2.1.1 Addressing

Once the MSSP module has been enabled, it waits for a START condition to occur. Following the START condition, the 8-bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match, and the BF and SSPOV bits are clear, the following events occur:

- The SSPSR register value is loaded into the SSPBUF register on the falling edge of the 8th SCL pulse.

- b) The buffer full bit, BF, is set on the falling edge of the 8th SCL pulse.

- c) An  $\overline{ACK}$  pulse is generated.

- d) SSP interrupt flag bit, SSPIF (PIR1<3>), is set (interrupt is generated if enabled) on the falling edge of the 9th SCL pulse.

In 10-bit Address mode, two address bytes need to be received by the slave. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit  $R/\overline{W}$  (SSPSTAT<2>) must specify a write, so the slave device will receive the second address byte. For a 10-bit address the first byte would equal '1111 0 A9 A8 0', where A9 and A8 are the two MSbs of the address. The sequence of events for a 10-bit address is as follows, with steps 7-9 for slave transmitter:

- 1. Receive first (high) byte of Address (bits SSPIF, BF and UA (SSPSTAT<1>) are set).

- 2. Update the SSPADD register with the second (low) byte of Address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 4. Receive second (low) byte of Address (bits SSPIF, BF and UA are set).

- 5. Update the SSPADD register with the first (high) byte of Address. This will clear bit UA and release the SCL line.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive Repeated START condition.

- 8. Receive first (high) byte of Address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

| Note: | Following the Repeated START condition<br>(step 7) in 10-bit mode, the user only<br>needs to match the first 7-bit address. The<br>user does not update the SSPADD for the |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | second half of the address.                                                                                                                                                |

#### 9.2.1.2 Slave Reception

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address <u>byte</u> overflow condition exists, then no Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set, or bit SSPOV (SSPCON<6>) is set. This is an error condition due to user firmware.

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the received byte.

Note: The SSPBUF will be loaded if the SSPOV bit is set and the BF flag is cleared. If a read of the SSPBUF was performed, but the user did not clear the state of the SSPOV bit before the next receive occurred, the ACK is not sent and the SSPBUF is updated.

## PIC16F872

#### **R/P-1** R/P-1 R/P-1 U-0 R/P-1 R/P-1 **R/P-1 R/P-1 R/P-1 R/P-1** R/P-1 R/P-1 R/P-1 **R/P-1** F0SC0 CP1 CP0 DEBUG WRT CPD LVP BODEN CP1 CP0 PWRTE WDTE F0SC1 bit13 bit0 bit 13-12 CP1:CP0: FLASH Program Memory Code Protection bits<sup>(2)</sup> 11 = Code protection off bit 5-4 10 = Not supported 01 = Not supported 00 = All memory code protected bit 11 DEBUG: In-Circuit Debugger Mode bit 1 = In-Circuit Debugger disabled, RB6 and RB7 are general purpose I/O pins 0 = In-Circuit Debugger enabled, RB6 and RB7 are dedicated to the debugger bit 10 Unimplemented: Read as '1' bit 9 WRT: FLASH Program Memory Write Enable bit 1 = Unprotected program memory may be written to by EECON control 0 = Unprotected program memory may not be written to by EECON control CPD: Data EEPROM Memory Code Protection bit bit 8 1 = Code protection off0 = Data EEPROM memory code protected bit 7 LVP: Low Voltage In-Circuit Serial Programming Enable bit 1 = RB3/PGM pin has PGM function, low voltage programming enabled 0 = RB3 is digital I/O, HV on MCLR must be used for programming BODEN: Brown-out Reset Enable bit<sup>(3)</sup> bit 6 1 = BOR enabled 0 = BOR disabled bit 3 **PWRTE**: Power-up Timer Enable bit<sup>(3)</sup> 1 = PWRT disabled 0 = PWRT enabled bit 2 WDTE: Watchdog Timer Enable bit 1 = WDT enabled 0 = WDT disabled bit 1-0 FOSC1:FOSC0: Oscillator Selection bits 11 = RC oscillator 10 = HS oscillator 01 = XT oscillator 00 = LP oscillator Note 1: The erased (unprogrammed) value of the configuration word is 3FFFh. 2: All of the CP1:CP0 pairs have to be given the same value to enable the code protection scheme listed. 3: Enabling Brown-out Reset automatically enables Power-up Timer (PWRT), regardless of the value of bit PWRTE. Ensure the Power-up Timer is enabled any time Brown-out Reset is enabled.

#### REGISTER 11-1: CONFIGURATION WORD (ADDRESS: 2007h)<sup>(1)</sup>

#### Legend:

| R = Readable bit           | P = Programmable bit | U = Unimplemented bit, read as '0'  |

|----------------------------|----------------------|-------------------------------------|

| - n = Value when device is | s unprogrammed       | u = Unchanged from programmed state |

#### 11.13 Power-down Mode (SLEEP)

Power-down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the PD bit (STATUS<3>) is cleared, the TO (STATUS<4>) bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD or Vss, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D and disable external clocks. Pull all I/O pins that are hi-impedance inputs, high or low externally, to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or Vss for lowest current consumption. The contribution from on-chip pull-ups on PORTB should also be considered.

The  $\overline{\text{MCLR}}$  pin must be at a logic high level (VIHMC).

#### 11.13.1 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- 1. External RESET input on MCLR pin.

- 2. Watchdog Timer wake-up (if WDT was enabled).

- 3. Interrupt from INT pin, RB port change or Peripheral Interrupt.

External MCLR Reset will cause a device RESET. All other events are considered a continuation of program execution and cause a "wake-up". The TO and PD bits in the STATUS register can be used to determine the cause of device RESET. The PD bit, which is set on power-up, is cleared when SLEEP is invoked. The TO bit is cleared if a WDT time-out occurred and caused wake-up.

The following peripheral interrupts can wake the device from SLEEP:

- 1. PSP read or write.

- 2. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 3. CCP Capture mode interrupt.

- 4. Special event trigger (Timer1 in Asynchronous mode using an external clock).

- 5. SSP (START/STOP) bit detect interrupt.

- 6. SSP transmit or receive in Slave mode (SPI/I<sup>2</sup>C).

- 7. USART RX or TX (Synchronous Slave mode).

- 8. A/D conversion (when A/D clock source is RC).

- 9. EEPROM write operation completion.

Other peripherals cannot generate interrupts, since during SLEEP, no on-chip clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

#### 11.13.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs before the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake-up from SLEEP. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

#### TABLE 13-1: DEVELOPMENT TOOLS FROM MICROCHIP

| Definition         Image: processing state         Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PIC12CXXX                             | PIC16C5X | PIC16C6X | PIC16CXXX | PIC16F62X | X7OðfOld | PIC16C7XX | X8O91OId | PIC16F8XX | XX6O9FOI9 | X4271219 | XX7371319 | PIC18FXXX | 54CXX | 63CXX<br>SeCXX/ | XXXSOH | МСВЕХХХ |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------|----------|-----------|-----------|----------|-----------|----------|-----------|-----------|----------|-----------|-----------|-------|-----------------|--------|---------|

| IntrAd <sup>®</sup> C 1 C Complier         IntrAd <sup>®</sup> C 1 C C Complier         IntrAd <sup>®</sup> C 1 C C C C C C C C C C C C C C C C C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | >                                     |          |          | >         | >         | >        | >         | >        | >         | >         |          |           |           |       |                 |        |         |

| WPLAB* Complet         >                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | C Compiler                            |          |          |           |           |          |           |          |           |           |          |           |           |       |                 |        |         |

| MPCARIW         Messame         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | C Compiler                            |          |          |           |           |          |           |          |           |           |          | `         |           |       |                 |        |         |

| MPLAB*/GE Inclorent Emulator         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /         /                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | >                                     |          |          | >         | >         | >        | >         | >        | >         | >         |          |           |           |       | ~               | ~      |         |

| International conditional conditina condinative conditional conditional conditional conditi | imulator 🗸                            |          |          | >         | **/       | >        | >         | >        | >         | >         |          | _         |           |       |                 |        |         |

| MPLAB® (CD In-Circuit<br>Debugger         MPLAB® (CD In-Circuit         MPLAB® (CD In-Circuit <th></th> <th>&gt;</th> <th></th> <th>&gt;</th> <th></th> <th>&gt;</th> <th>&gt;</th> <th>&gt;</th> <th></th> <th>&gt;</th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th>                                                                                                                                                                                                                                                                           |                                       | >        |          | >         |           | >        | >         | >        |           | >         |          |           |           |       |                 |        |         |