Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 3.5КВ (2К х 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 64 x 8                                                                    |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 5.5V                                                               |

| Data Converters            | A/D 5x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf872-i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name           | Pin#  | I/O/P<br>Type | Buffer<br>Type        | Description                                                                                                             |  |  |  |

|--------------------|-------|---------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                    |       |               |                       | PORTB is a bi-directional I/O port. PORTB can be software                                                               |  |  |  |

|                    |       |               |                       | programmed for internal weak pull-up on all inputs.                                                                     |  |  |  |

| RB0/INT            | 21    | I/O           | TTL/ST <sup>(1)</sup> |                                                                                                                         |  |  |  |

| RB0                |       |               |                       | Digital I/O.                                                                                                            |  |  |  |

| INT                |       |               |                       | External interrupt pin.                                                                                                 |  |  |  |

| RB1                | 22    | I/O           | TTL                   | Digital I/O.                                                                                                            |  |  |  |

| RB2                | 23    | I/O           | TTL                   | Digital I/O.                                                                                                            |  |  |  |

| RB3/PGM            | 24    | I/O           | TTL                   |                                                                                                                         |  |  |  |

| RB3                |       |               |                       | Digital I/O.                                                                                                            |  |  |  |

| PGM                |       |               |                       | Low voltage ICSP programming enable pin.                                                                                |  |  |  |

| RB4                | 25    | I/O           | TTL                   | Digital I/O.                                                                                                            |  |  |  |

| RB5                | 26    | I/O           | TTL                   | Digital I/O.                                                                                                            |  |  |  |

| RB6/PGC            | 27    | I/O           | TTL/ST <sup>(2)</sup> |                                                                                                                         |  |  |  |

| RB6                |       |               |                       | Digital I/O.                                                                                                            |  |  |  |

| PGC                |       |               |                       | In-Circuit Debugger and ICSP programming clock.                                                                         |  |  |  |

| RB7/PGD            | 28    | I/O           | TTL/ST <sup>(2)</sup> |                                                                                                                         |  |  |  |

| RB7<br>PGD         |       |               |                       | Digital I/O.<br>In-Circuit Debugger and ICSP programming data.                                                          |  |  |  |

| FGD                |       |               |                       |                                                                                                                         |  |  |  |

|                    |       |               | o <del></del>         | PORTC is a bi-directional I/O port.                                                                                     |  |  |  |

| RC0/T1OSO/T1CKI    | 11    | I/O           | ST                    | Divite 1/0                                                                                                              |  |  |  |

| RC0<br>T1OSO       |       |               |                       | Digital I/O.<br>Timer1 oscillator output.                                                                               |  |  |  |

| T1CKI              |       |               |                       | Timer1 clock input.                                                                                                     |  |  |  |

| RC1/T1OSI          | 12    | I/O           | ST                    |                                                                                                                         |  |  |  |

| RC1                |       | ., 0          | 01                    | Digital I/O.                                                                                                            |  |  |  |

| T1OSI              |       |               |                       | Timer1 oscillator input.                                                                                                |  |  |  |

| RC2/CCP1           | 13    | I/O           | ST                    |                                                                                                                         |  |  |  |

| RC2                |       |               |                       | Digital I/O.                                                                                                            |  |  |  |

| CCP1               |       |               |                       | Capture1 input/Compare1 output/PWM1 output.                                                                             |  |  |  |

| RC3/SCK/SCL        | 14    | I/O           | ST                    |                                                                                                                         |  |  |  |

| RC3                |       |               |                       | Digital I/O.                                                                                                            |  |  |  |

| SCK                |       |               |                       | Synchronous serial clock input/output for SPI mode.<br>Synchronous serial clock input/output for I <sup>2</sup> C mode. |  |  |  |

| SCL                | 4 -   | 1/2           | <b>O</b> T            | Synchronous senal clock input/output for I=C mode.                                                                      |  |  |  |

| RC4/SDI/SDA<br>RC4 | 15    | I/O           | ST                    |                                                                                                                         |  |  |  |

| SDI                |       |               |                       | Digital I/O.<br>SPI Data In pin (SPI mode).                                                                             |  |  |  |

| SDA                |       |               |                       | SPI Data I/O pin (I <sup>2</sup> C mode).                                                                               |  |  |  |

| RC5/SDO            | 16    | I/O           | ST                    |                                                                                                                         |  |  |  |

| RC5                |       |               |                       | Digital I/O.                                                                                                            |  |  |  |

| SDO                |       |               |                       | SPI Data Out pin (SPI mode).                                                                                            |  |  |  |

| RC6                | 17    | I/O           | ST                    | Digital I/O.                                                                                                            |  |  |  |

| RC7                | 18    | I/O           | ST                    | Digital I/O.                                                                                                            |  |  |  |

| Vss                | 8, 19 | P             |                       | Ground reference for logic and I/O pins.                                                                                |  |  |  |

| VDD                | 20    | P             | <u> </u>              | Positive supply for logic and I/O pins.                                                                                 |  |  |  |

|                    | -     | O = outp      | I                     | I/O = input/output $P = power$                                                                                          |  |  |  |

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

x = Bit is unknown

# 2.2.2.6 PIE2 Register

The PIE2 register contains the individual enable bits for the CCP2 peripheral interrupt, the SSP bus collision interrupt, and the EEPROM write operation interrupt.

- n = Value at POR

| <b>REGISTER 2-6:</b> | PIE2 REGISTER (ADDRESS: 8Dh)                                             |                               |                |              |         |     |     |          |

|----------------------|--------------------------------------------------------------------------|-------------------------------|----------------|--------------|---------|-----|-----|----------|

|                      | U-0                                                                      | R/W-0                         | U-0            | R/W-0        | R/W-0   | U-0 | U-0 | R/W-0    |

|                      |                                                                          | reserved                      |                | EEIE         | BCLIE   | —   | —   | reserved |

|                      | bit 7                                                                    |                               |                |              |         |     |     | bit 0    |

|                      |                                                                          |                               |                |              |         |     |     |          |

| bit 7                | Unimplem                                                                 | ented: Read                   | as '0'         |              |         |     |     |          |

| bit 6                | Reserved:                                                                | Always mai                    | ntain this bit | clear        |         |     |     |          |

| bit 5                | Unimplem                                                                 | ented: Read                   | d as '0'       |              |         |     |     |          |

| bit 4                | EEIE: EEP                                                                | ROM Write                     | Operation In   | terrupt Enal | ole bit |     |     |          |

|                      |                                                                          | EEPROM w                      |                |              |         |     |     |          |

| bit 3                | BCLIE: Bu                                                                | s Collision Ir                | nterrupt Ena   | ble bit      |         |     |     |          |

|                      |                                                                          | bus collisior<br>bus collisio | •              |              |         |     |     |          |

| bit 2-1              | Unimplem                                                                 | ented: Read                   | d as '0'       |              |         |     |     |          |

| bit 0                | Reserved: Always maintain this bit clear                                 |                               |                |              |         |     |     |          |

|                      |                                                                          |                               |                |              |         |     |     |          |

|                      | Legend:                                                                  |                               |                |              |         |     |     |          |

|                      | R = Readable bit $W = Writable bit$ $U = Unimplemented bit, read as '0'$ |                               |                |              |         |     |     |          |

'1' = Bit is set

'0' = Bit is cleared

### 2.3 PCL and PCLATH

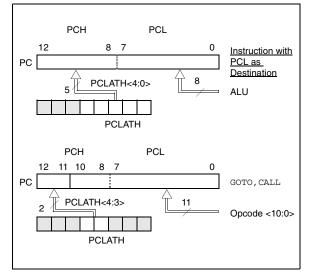

The program counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a readable and writable register. The upper bits (PC<12:8>) are not readable, but are indirectly writable through the PCLATH register. On any RESET, the upper bits of the PC will be cleared. Figure 2-3 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

### FIGURE 2-3: LOADING OF PC IN DIFFERENT SITUATIONS

### 2.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 byte block). Refer to the Application Note, *"Implementing a Table Read"* (AN556).

### 2.3.2 STACK

The PIC16FXXX family has an 8-level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

**Note 1:** There are no status bits to indicate stack overflow or stack underflow conditions.

2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions, or the vectoring to an interrupt address.

### 2.4 Program Memory Paging

All PIC16FXXX devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction, the upper 2 bits of the address are provided by PCLATH<4:3>. Since the PIC16F872 has only 2K words of program memory or one page, additional code is not required to ensure that the correct page is selected before a CALL or GOTO instruction is executed. The PCLATH<4:3> bits should always be maintained as zeros. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is popped off the stack. Therefore. manipulation of the PCLATH<4:3> bits are not required for the return instructions (which POPs the address from the stack).

Note: The contents of the PCLATH register are unchanged after a RETURN or RETFIE instruction is executed. The user must rewrite the contents of the PCLATH register for any subsequent subroutine calls or GOTO instructions.

| Name    | Bit# | Buffer                | Function                                                                                                                                          |

|---------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/INT | bit0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up.                                                        |

| RB1     | bit1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                                                    |

| RB2     | bit2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                                                    |

| RB3/PGM | bit3 | TTL                   | Input/output pin or programming pin in LVP mode.<br>Internal software programmable weak pull-up.                                                  |

| RB4     | bit4 | TTL                   | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up.                                                      |

| RB5     | bit5 | TTL                   | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up.                                                      |

| RB6/PGC | bit6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change) or In-Circuit Debugger pin.<br>Internal software programmable weak pull-up. Serial programming clock. |

| RB7/PGD | bit7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change) or In-Circuit Debugger pin.<br>Internal software programmable weak pull-up. Serial programming data.  |

### TABLE 4-3: PORTB FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

### TABLE 4-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address   | Name       | Bit 7 | Bit 6                        | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|-----------|------------|-------|------------------------------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 06h, 106h | PORTB      | RB7   | RB6                          | RB5   | RB4   | RB3   | RB2   | RB1   | RB0   | XXXX XXXX                | uuuu uuuu                       |

| 86h, 186h | TRISB      | PORTB | ORTB Data Direction Register |       |       |       |       |       |       | 1111 1111                | 1111 1111                       |

| 81h, 181h | OPTION_REG | RBPU  | INTEDG                       | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                | 1111 1111                       |

Legend:  $\mathbf{x}$  = unknown,  $\mathbf{u}$  = unchanged. Shaded cells are not used by PORTB.

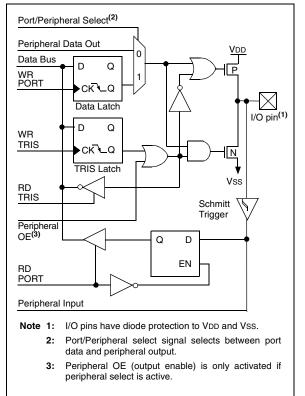

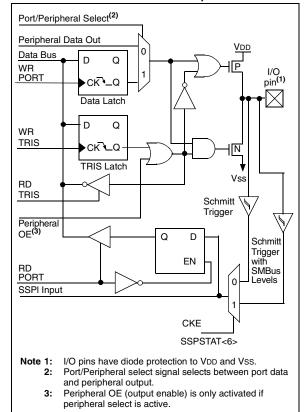

### 4.3 PORTC and the TRISC Register

PORTC is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISC. Setting a TRISC bit (= '1') will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISC bit (= '0') will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

PORTC is multiplexed with several peripheral functions (Table 4-5). PORTC pins have Schmitt Trigger input buffers.

When the  $l^2C$  module is enabled, the PORTC (4:3) pins can be configured with normal  $l^2C$  levels or with SMBus levels by using the CKE bit (SSPSTAT<6>).

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modify-write instructions (BSF, BCF, XORWF) with TRISC as the destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

### FIGURE 4-5: PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE) RC<2:0> RC<7:5>

### FIGURE 4-6:

### PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE) RC<4:3>

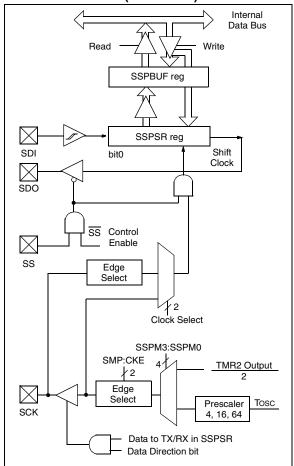

### 9.1 SPI Mode

The SPI mode allows 8 bits of data to be synchronously transmitted and received, simultaneously. All four modes of SPI are supported. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO)

- Serial Data In (SDI)

- Serial Clock (SCK)

Additionally, a fourth pin may be used when in a Slave mode of operation:

• Slave Select (SS)

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPCON<5:0> and SSPSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (IDLE state of SCK)

- Data input sample phase (middle or end of data output time)

- Clock edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- Slave Select mode (Slave mode only)

Figure 9-4 shows the block diagram of the MSSP module when in SPI mode.

To enable the serial port, MSSP Enable bit, SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear bit SSPEN, re-initialize the SSPCON registers, and then set bit SSPEN. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed. That is:

- SDI is automatically controlled by the SPI module

- SDO must have TRISC<5> cleared

- SCK (Master mode) must have TRISC<3> cleared

- SCK (Slave mode) must have TRISC<3> set

- SS must have TRISA<5> set, and

- Register ADCON1 must be set in a way that pin RA5 is configured as a digital I/O

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

### FIGURE 9-1:

#### MSSP BLOCK DIAGRAM (SPI MODE)

### 9.1.1 MASTER MODE

The master can initiate the data transfer at any time because it controls the SCK. The master determines when the slave (Processor 2, Figure 9-5) is to broad-cast data by the software protocol.

In Master mode, the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI module is only going to receive, the SDO output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and status bits appropriately set). This could be useful in receiver applications as a "line activity monitor".

# 9.2 MSSP I<sup>2</sup>C Operation

The MSSP module in I<sup>2</sup>C mode, fully implements all master and slave functions (including general call support) and provides interrupts on START and STOP bits in hardware to determine a free bus (multi-master function). The MSSP module implements the standard mode specifications, as well as 7-bit and 10-bit addressing.

Refer to Application Note (AN578), "Use of the SSP Module in the  $I^2C$  Multi-Master Environment."

A "glitch" filter is on the SCL and SDA pins when the pin is an input. This filter operates in both the 100 kHz and 400 kHz modes. In the 100 kHz mode, when these pins are an output, there is a slew rate control of the pin that is independent of device frequency.

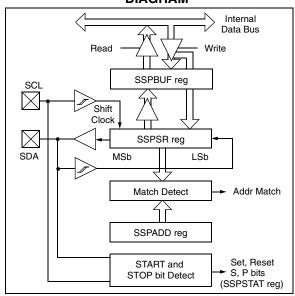

### FIGURE 9-5: I<sup>2</sup>C SLAVE MODE BLOCK DIAGRAM

Two pins are used for data transfer. These are the SCL pin, which is the clock, and the SDA pin, which is the data. The SDA and SCL pins are automatically configured when the  $l^2C$  mode is enabled. The SSP module functions are enabled by setting SSP Enable bit SSPEN (SSPCON<5>).

The MSSP module has six registers for  ${\rm I}^2{\rm C}$  operation. They are the:

- SSP Control Register (SSPCON)

- SSP Control Register2 (SSPCON2)

- SSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift Register (SSPSR) Not directly accessible

- SSP Address Register (SSPADD)

The SSPCON register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Master mode, clock = OSC/4 (SSPADD +1)

Before selecting any  $I^2C$  mode, the SCL and SDA pins must be programmed to inputs by setting the appropriate TRIS bits. Selecting an  $I^2C$  mode by setting the SSPEN bit, enables the SCL and SDA pins to be used as the clock and data lines in  $I^2C$  mode. Pull-up resistors must be provided externally to the SCL and SDA pins for the proper operation of the  $I^2C$  module.

The CKE bit (SSPSTAT<6:7>) sets the levels of the SDA and SCL pins in either Master or Slave mode. When CKE = 1, the levels will conform to the SMBus specification. When CKE = 0, the levels will conform to the  $l^2C$  specification.

The SSPSTAT register gives the status of the data transfer. This information includes detection of a START (S) or STOP (P) bit, specifies if the received byte was data or address, if the next byte is the completion of 10-bit address, and if this will be a read or write data transfer.

SSPBUF is the register to which the transfer data is written to or read from. The SSPSR register shifts the data in or out of the device. In receive operations, the SSPBUF and SSPSR create a doubled buffered receiver. This allows reception of the next byte to begin before reading the last byte of received data. When the complete byte is received, it is transferred to the SSPBUF register and flag bit SSPIF is set. If another complete byte is received before the SSPBUF register is read, a receiver overflow has occurred and bit SSPOV (SSPCON<6>) is set and the byte in the SSPSR is lost.

The SSPADD register holds the slave address. In 10-bit mode, the user needs to write the high byte of the address (1111 0 A9 A8 0). Following the high byte address match, the low byte of the address needs to be loaded (A7:A0).

### 9.2.1 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs. The MSSP module will override the input state with the output data when required (slavetransmitter).

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge ( $\overline{ACK}$ ) pulse, and then load the SSPBUF register with the received value currently in the SSPSR register.

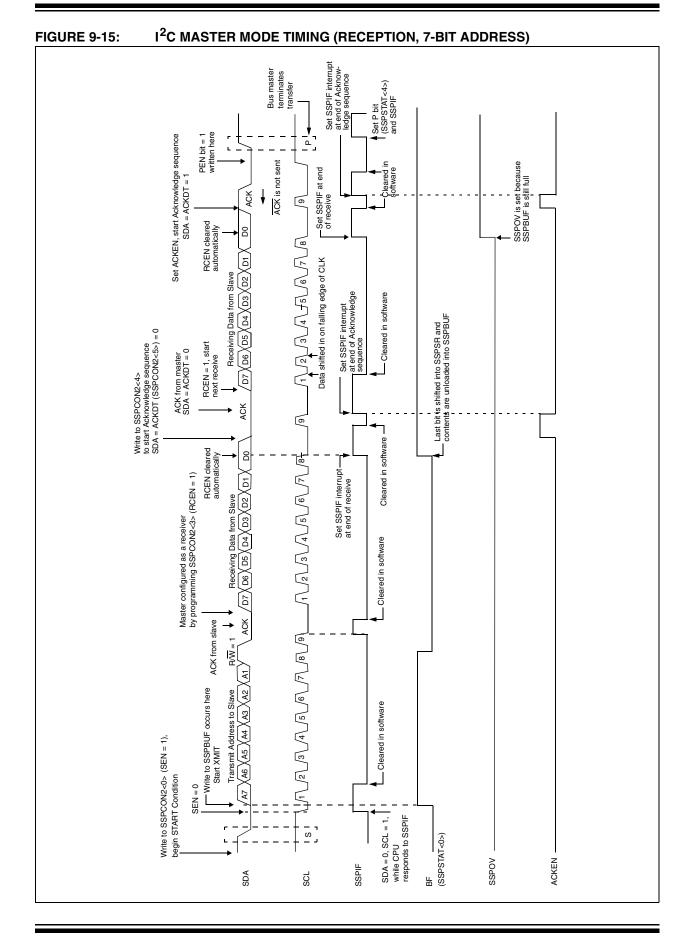

### 9.2.5 MASTER MODE

Master mode of operation is supported by interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared from a RESET or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is IDLE, with both the S and P bits clear.

In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware.

The following events will cause the SSP Interrupt Flag bit, SSPIF, to be set (an SSP Interrupt will occur if enabled):

- START condition

- STOP condition

- · Data transfer byte transmitted/received

- Acknowledge transmit

- Repeated START

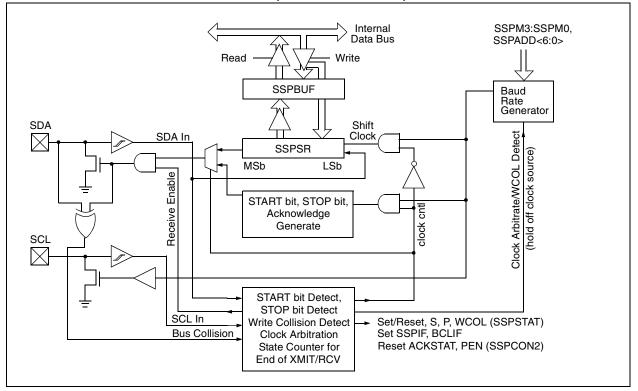

# FIGURE 9-9: SSP BLOCK DIAGRAM (I<sup>2</sup>C MASTER MODE)

### 9.2.6 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the START and STOP conditions allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a RESET or when the MSSP module is disabled. Control of the I<sup>2</sup>C bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is IDLE with both the S and P bits clear. When the bus is busy, enabling the SSP interrupt will generate the interrupt when the STOP condition occurs.

In Multi-Master operation, the SDA line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed in hardware, with the result placed in the BCLIF bit. The states where arbitration can be lost are:

- Address Transfer

- Data Transfer

- A START Condition

- A Repeated START Condition

- An Acknowledge Condition

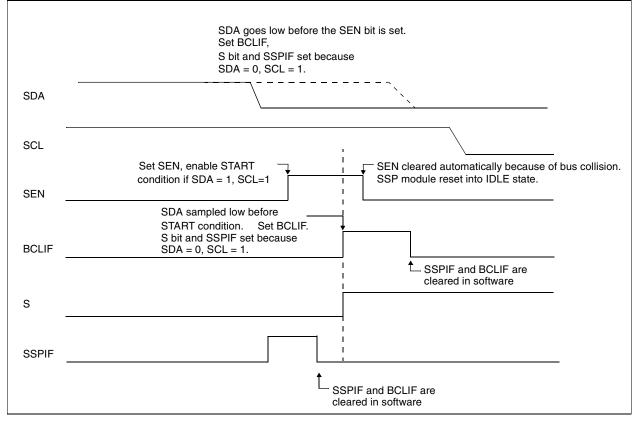

### 9.2.18.1 Bus Collision During a START Condition

During a START condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the START condition (Figure 9-20).

- b) SCL is sampled low before SDA is asserted low. (Figure 9-21).

During a START condition, both the SDA and the SCL pins are monitored. If either the SDA pin <u>or</u> the SCL pin is already low, then these events all occur:

- the START condition is aborted,

- and the BCLIF flag is set

- <u>and</u> the SSP module is reset to its IDLE state (Figure 9-20).

The START condition begins with the SDA and SCL pins de-asserted. When the SDA pin is sampled high, the baud rate generator is loaded from SSPADD<6:0> and counts down to 0. If the SCL pin is sampled low while SDA is high, a bus collision occurs, because it is assumed that another master is attempting to drive a data '1' during the START condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 9-22). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The baud rate generator is then reloaded and counts down to 0. During this time, if the SCL pins are sampled as '0', a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a START condition, is that no two bus masters can assert a START condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision, because the two masters must be allowed to arbitrate the first address following the START condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated START or STOP conditions.

### FIGURE 9-20: BUS COLLISION DURING START CONDITION (SDA ONLY)

### REGISTER 10-2: ADCON1 REGISTER (ADDRESS: 9Fh)

|   | U-0   | U-0 | R/W-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|---|-------|-----|-------|-----|-------|-------|-------|-------|

|   | ADFM  | —   | —     | —   | PCFG3 | PCFG2 | PCFG1 | PCFG0 |

| k | oit 7 |     |       |     |       |       |       | bit 0 |

bit 7 ADFM: A/D Result Format Select bit

1 = Right justified. Six Most Significant bits of ADRESH are read as '0'.

0 = Left justified. Six Least Significant bits of ADRESL are read as '0'.

### bit 6-4 Unimplemented: Read as '0'

| bit 3-0 | PCFG3:PCFG0: | A/D Port | Configuration | Control bits: |

|---------|--------------|----------|---------------|---------------|

|         |              |          |               |               |

| PCFG3:<br>PCFG0 | AN4<br>RA5 | AN3<br>RA3 | AN2<br>RA2 | AN1<br>RA1 | AN0<br>RA0 | VREF+ | VREF- | CHAN/<br>Refs <sup>(1)</sup> |

|-----------------|------------|------------|------------|------------|------------|-------|-------|------------------------------|

| 0000            | А          | А          | Α          | Α          | Α          | Vdd   | Vss   | 8/0                          |

| 0001            | А          | VREF+      | А          | Α          | Α          | RA3   | Vss   | 7/1                          |

| 0010            | А          | А          | А          | Α          | Α          | Vdd   | Vss   | 5/0                          |

| 0011            | А          | VREF+      | Α          | А          | Α          | RA3   | Vss   | 4/1                          |

| 0100            | D          | А          | D          | А          | Α          | Vdd   | Vss   | 3/0                          |

| 0101            | D          | VREF+      | D          | Α          | Α          | RA3   | Vss   | 2/1                          |

| 011x            | D          | D          | D          | D          | D          | Vdd   | Vss   | 0/0                          |

| 1000            | А          | VREF+      | VREF-      | А          | Α          | RA3   | RA2   | 6/2                          |

| 1001            | А          | А          | А          | А          | Α          | Vdd   | Vss   | 6/0                          |

| 1010            | А          | VREF+      | А          | А          | Α          | RA3   | Vss   | 5/1                          |

| 1011            | А          | VREF+      | VREF-      | А          | Α          | RA3   | RA2   | 4/2                          |

| 1100            | А          | VREF+      | VREF-      | А          | Α          | RA3   | RA2   | 3/2                          |

| 1101            | D          | VREF+      | VREF-      | А          | Α          | RA3   | RA2   | 2/2                          |

| 1110            | D          | D          | D          | D          | А          | Vdd   | Vss   | 1/0                          |

| 1111            | D          | VREF+      | VREF-      | D          | Α          | RA3   | RA2   | 1/2                          |

A = Analog input

D = Digital I/O

**Note 1:** This column indicates the number of analog channels available as A/D inputs and the number of analog channels used as voltage reference inputs.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

NOTES:

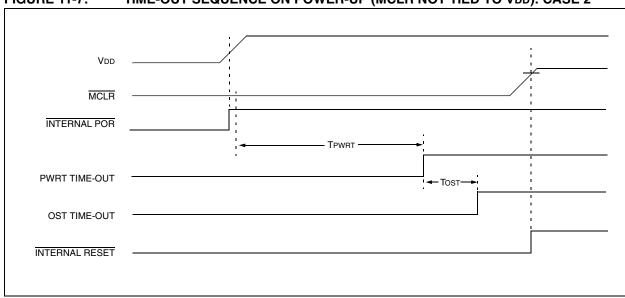

FIGURE 11-7: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

### 11.13 Power-down Mode (SLEEP)

Power-down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the PD bit (STATUS<3>) is cleared, the TO (STATUS<4>) bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD or Vss, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D and disable external clocks. Pull all I/O pins that are hi-impedance inputs, high or low externally, to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or Vss for lowest current consumption. The contribution from on-chip pull-ups on PORTB should also be considered.

The  $\overline{\text{MCLR}}$  pin must be at a logic high level (VIHMC).

### 11.13.1 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- 1. External RESET input on MCLR pin.

- 2. Watchdog Timer wake-up (if WDT was enabled).

- 3. Interrupt from INT pin, RB port change or Peripheral Interrupt.

External MCLR Reset will cause a device RESET. All other events are considered a continuation of program execution and cause a "wake-up". The TO and PD bits in the STATUS register can be used to determine the cause of device RESET. The PD bit, which is set on power-up, is cleared when SLEEP is invoked. The TO bit is cleared if a WDT time-out occurred and caused wake-up.

The following peripheral interrupts can wake the device from SLEEP:

- 1. PSP read or write.

- 2. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 3. CCP Capture mode interrupt.

- 4. Special event trigger (Timer1 in Asynchronous mode using an external clock).

- 5. SSP (START/STOP) bit detect interrupt.

- 6. SSP transmit or receive in Slave mode (SPI/I<sup>2</sup>C).

- 7. USART RX or TX (Synchronous Slave mode).

- 8. A/D conversion (when A/D clock source is RC).

- 9. EEPROM write operation completion.

Other peripherals cannot generate interrupts, since during SLEEP, no on-chip clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

### 11.13.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs before the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake-up from SLEEP. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

### 14.1 DC Characteristics: PIC16F872 (Commercial, Industrial) PIC16LF872 (Commercial, Industrial) (Continued)

| PIC16LF872 (Commercial, Industrial) |        |                                           | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                                                                                                                                                                                        |     |       |                                             |  |  |

|-------------------------------------|--------|-------------------------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|---------------------------------------------|--|--|

| PIC16F872 (Commercial, Industrial)  |        |                                           |                                                      | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial |     |       |                                             |  |  |

| Param<br>No.                        | Symbol | Characteristic/<br>Device                 | Min                                                  | Тур†                                                                                                                                                                                   | Max | Units | Conditions                                  |  |  |

| D015                                | ∆IBOR  | Brown-out<br>Reset Current <sup>(6)</sup> |                                                      | 85                                                                                                                                                                                     | 200 | μA    | BOR enabled, VDD = 5.0V                     |  |  |

|                                     | IPD    | Power-down Current <sup>(3,5)</sup>       |                                                      |                                                                                                                                                                                        |     |       |                                             |  |  |

| D020                                |        | PIC16LF872                                | _                                                    | 7.5                                                                                                                                                                                    | 30  | μA    | VDD = 3.0V, WDT enabled,<br>-40°C to +85°C  |  |  |

| D020                                |        | PIC16F872                                 | _                                                    | 10.5                                                                                                                                                                                   | 42  | μA    | VDD = 4.0V, WDT enabled,<br>-40°C to +85°C  |  |  |

| D021                                |        | PIC16LF872                                | _                                                    | 0.9                                                                                                                                                                                    | 5   | μA    | VDD = 3.0V, WDT disabled,<br>0°C to +70°C   |  |  |

| D021                                |        | PIC16F872                                 | _                                                    | 1.5                                                                                                                                                                                    | 16  | μA    | VDD = 4.0V, WDT disabled,<br>-40°C to +85°C |  |  |

| D021A                               |        | PIC16LF872                                |                                                      | 0.9                                                                                                                                                                                    | 5   | μA    | VDD = 3.0V, WDT disabled,<br>-40°C to +85°C |  |  |

| D021A                               |        | PIC16F872                                 |                                                      | 1.5                                                                                                                                                                                    | 19  | μA    | VDD = 4.0V, WDT disabled,<br>-40°C to +85°C |  |  |

| D023                                | ∆IBOR  | Brown-out<br>Reset Current <sup>(6)</sup> |                                                      | 85                                                                                                                                                                                     | 200 | μA    | BOR enabled, VDD = 5.0V                     |  |  |

Legend: Rows with standard voltage device data only are shaded for improved readability.

- † Data is "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only, and are not tested.

- **Note 1:** This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD

MCLR = VDD; WDT enabled/disabled as specified.

- **3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

- 4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kOhm.

- **5:** Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

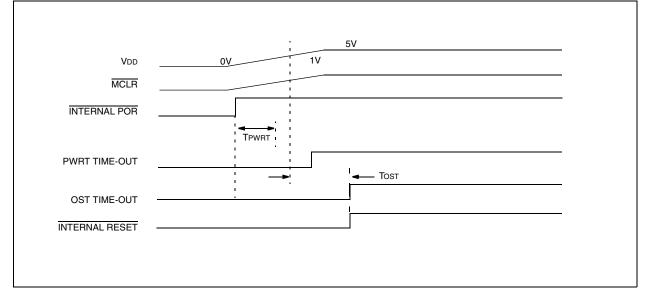

#### TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS **FIGURE 14-8:**

| Param<br>No. | Symbol    |                                                   | Characteristic                                                         |                      | Min                                       | Тур† | Max   | Units | Conditions                            |

|--------------|-----------|---------------------------------------------------|------------------------------------------------------------------------|----------------------|-------------------------------------------|------|-------|-------|---------------------------------------|

| 40*          | Tt0H      | T0CKI High Pulse                                  | Width                                                                  | No Prescaler         | 0.5TCY + 20                               | —    | —     | ns    | Must also meet                        |

|              |           | _                                                 |                                                                        | With Prescaler       | 10                                        | —    | _     | ns    | parameter 42                          |

| 41*          | Tt0L      | T0CKI Low Pulse Width                             |                                                                        | No Prescaler         | 0.5TCY + 20                               | —    | —     | ns    | Must also meet parameter 42           |

|              |           |                                                   |                                                                        | With Prescaler       | 10                                        | —    | _     | ns    |                                       |

| 42*          | Tt0P      | T0CKI Period                                      |                                                                        | No Prescaler         | Tcy + 40                                  | —    | _     | ns    |                                       |

|              |           |                                                   |                                                                        | With Prescaler       | Greater of:<br>20 or <u>Tcy + 40</u><br>N | _    | —     | ns    | N = prescale<br>value (2, 4,,<br>256) |

| 45*          | Tt1H      | Synchronou<br>Prescaler =                         | Synchronous, Pro                                                       | escaler = 1          | 0.5TCY + 20                               | —    | _     | ns    | Must also meet<br>parameter 47        |

|              |           |                                                   | Synchronous,<br>Prescaler = 2,4,8                                      | Standard(F)          | 15                                        | —    | —     | ns    |                                       |

|              |           |                                                   |                                                                        | Extended(LF)         | 25                                        | —    | —     | ns    |                                       |

|              |           |                                                   | Asynchronous                                                           | Standard(F)          | 30                                        | —    | —     | ns    |                                       |

|              |           |                                                   |                                                                        | Extended(LF)         | 50                                        | —    | —     | ns    |                                       |

| 46*          | Tt1L      | T1CKI Low Time                                    | Synchronous, Prescaler = 1                                             |                      | 0.5TCY + 20                               | —    | —     | ns    | Must also meet                        |

|              |           |                                                   | Synchronous,<br>Prescaler = 2,4,8                                      | Standard(F)          | 15                                        | —    |       | ns    | parameter 47                          |

|              |           |                                                   |                                                                        | Extended(LF)         | 25                                        | —    |       | ns    |                                       |

|              |           |                                                   | Asynchronous                                                           | Standard(F)          | 30                                        | —    |       | ns    |                                       |

|              |           |                                                   |                                                                        | Extended(LF)         | 50                                        | —    |       | ns    |                                       |

| 47*          | Tt1P      | T1CKI Input<br>Period                             | Synchronous                                                            | Standard( <b>F</b> ) | Greater of:<br>30 OR <u>Tcy + 40</u><br>N | _    | —     | ns    | N = prescale<br>value (1, 2, 4, 8)    |

|              |           |                                                   |                                                                        | Extended(LF)         | Greater of:<br>50 OR <u>TCY + 40</u><br>N |      |       |       | N = prescale<br>value (1, 2, 4, 8)    |

|              |           |                                                   | Asynchronous                                                           | Standard(F)          | 60                                        | —    |       | ns    |                                       |

|              |           |                                                   |                                                                        | Extended(LF)         | 100                                       | —    | _     | ns    |                                       |

|              | Ft1       | (oscillator enabled                               | Oscillator Input Frequency Range<br>or enabled by setting bit T1OSCEN) |                      | DC                                        | _    | 200   | kHz   |                                       |

| 48           | TCKEZtmr1 | Delay from External Clock Edge to Timer Increment |                                                                        |                      | 2Tosc                                     | _    | 7Tosc | —     |                                       |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

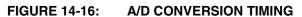

### TABLE 14-10: A/D CONVERSION REQUIREMENTS

| Param<br>No. | Sym  | Charae                          | cteristic             | Min      | Тур†     | Max | Units | Conditions                                                                                                                                                                                                                      |

|--------------|------|---------------------------------|-----------------------|----------|----------|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130          | TAD  | A/D Clock Period                | Standard(F)           | 1.6      |          |     | μs    | Tosc based, VREF ≥ 3.0V                                                                                                                                                                                                         |

|              |      |                                 | Extended(LF)          | 3.0      | —        |     | μs    | Tosc based, VREF ≥ 2.0V                                                                                                                                                                                                         |

|              |      |                                 | Standard(F)           | 2.0      | 4.0      | 6.0 | μs    | A/D RC mode                                                                                                                                                                                                                     |

|              |      |                                 | Extended(LF)          | 3.0      | 6.0      | 9.0 | μs    | A/D RC mode                                                                                                                                                                                                                     |

| 131          | TCNV | Conversion Time (no<br>(Note 1) | t including S/H time) |          | —        | 12  | TAD   |                                                                                                                                                                                                                                 |

| 132          | TACQ | Acquisition Time                |                       | (Note 2) | 40       |     | μs    |                                                                                                                                                                                                                                 |

|              |      |                                 |                       | 10*      |          | _   | μs    | The minimum time is the<br>amplifier settling time. This may<br>be used if the "new" input volt-<br>age has not changed by more<br>than 1 LSb (i.e., 20.0 mV @<br>5.12V) from the last sampled<br>voltage (as stated on CHOLD). |

| 134          | TGO  | Q4 to A/D Clock Star            | t                     | _        | Tosc/2 § | _   | _     | If the A/D clock source is<br>selected as RC, a time of Tcy is<br>added before the A/D clock<br>starts. This allows the SLEEP<br>instruction to be executed.                                                                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

Note 1: ADRES register may be read on the following TCY cycle.

**2:** See Section 10.1 for min. conditions.

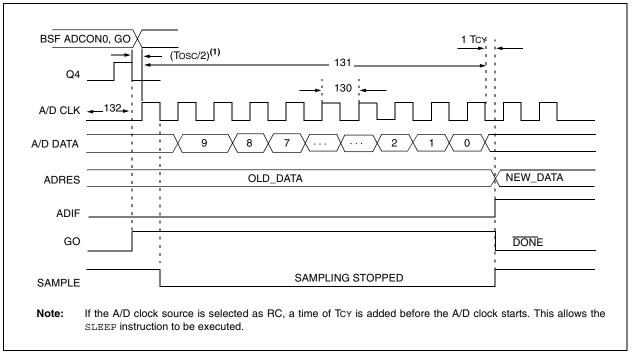

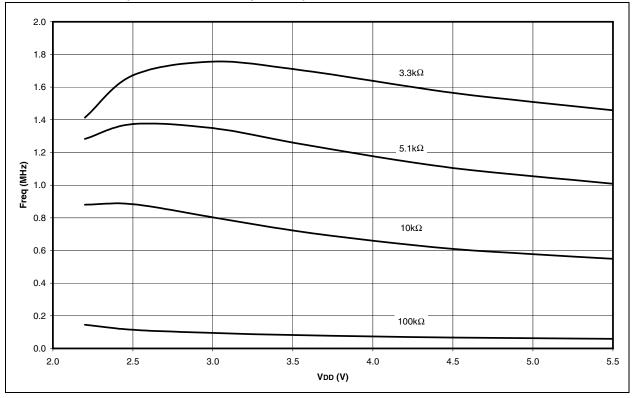

### FIGURE 15-8: AVERAGE FOSC vs. VDD FOR VARIOUS VALUES OF R (RC MODE, C = 100 pF, $25^{\circ}$ C)

DS30221C-page 142

# APPENDIX A: REVISION HISTORY

| Version | Date  | Revision Description                                                                                                                                                  |

|---------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A       | 11/99 | This is a new data sheet (Pre-<br>liminary). However, these<br>devices are similar to the<br>PIC16C72A devices found in<br>the PIC16C62B/72A Data<br>Sheet (DS35008). |

| В       | 12/01 | Final version of data sheet.<br>Includes DC and AC charac-<br>teristics graphs and updated<br>electrical specifications.                                              |

| С       | 9/06  | Packaging diagrams updated.                                                                                                                                           |

# APPENDIX B: CONVERSION CONSIDERATIONS

Considerations for converting from previous versions of devices to the ones listed in this data sheet are listed in Table B-1.

| TABLE B-1: | CONVERSION     |  |  |

|------------|----------------|--|--|

|            | CONSIDERATIONS |  |  |

| Characteristic    | PIC16C72A                                     | PIC16F872                                             |

|-------------------|-----------------------------------------------|-------------------------------------------------------|

| Pins              | 28                                            | 28                                                    |

| Timers            | 3                                             | 3                                                     |

| Interrupts        | 7                                             | 10                                                    |

| Communication     | Basic SSP<br>(SPI, I <sup>2</sup> C<br>Slave) | SSP (SPI, I <sup>2</sup> C<br>Master/Slave)           |

| Frequency         | 20 MHz                                        | 20 MHz                                                |

| A/D               | 8-bit,<br>5 channels                          | 10-bit<br>5 channels                                  |

| ССР               | 1                                             | 1                                                     |

| Program<br>Memory | 2K EPROM                                      | 2K FLASH                                              |

| RAM               | 128 bytes                                     | 128 bytes                                             |

| EEPROM Data       | None                                          | 64 bytes                                              |

| Other             |                                               | In-Circuit<br>Debugger,<br>Low Voltage<br>Programming |

| MOVF                                           | 108      |

|------------------------------------------------|----------|

| MOVLW                                          | 108      |

| MOVWF                                          | 108      |

| NOP                                            | 108      |

| RETFIE                                         | 108      |

| RETLW                                          | 108      |

| RETURN                                         | 109      |

| RLF                                            | 109      |

| RRF                                            | 109      |

| SLEEP                                          | 109      |

| SUBLW                                          | 109      |

| SUBWF                                          |          |

| SWAPF                                          | 110      |

| XORLW                                          |          |

| XORWF                                          |          |

| Summary Table                                  |          |

| INT Interrupt (RB0/INT). See Interrupt Sources |          |

| INTCON Register                                | 9, 14    |

| GIE Bit                                        |          |

| INTE Bit                                       |          |

| INTE Bit                                       |          |

| PEIE Bit                                       |          |

| RBIE Bit                                       |          |

| RBIF Bit                                       |          |

| TMR0IE Bit                                     | /        |

| TMR0IF Bit                                     |          |

| Inter-Integrated Circuit (I <sup>2</sup> C)    |          |

| Internal Sampling Switch (Rss) Impedance       |          |

| Interrupt Sources                              |          |

| Interrupt-on-Change (RB7:RB4)                  | 07, 37   |

| RB0/INT Pin, External                          |          |

| TMR0 Overflow                                  |          |

| Interrupts                                     |          |

| Bus Collision Interrupt                        | 10       |

| Synchronous Serial Port Interrupt              | 10<br>16 |

| Interrupts, Context Saving During              |          |

| Interrupts, Enable Bits                        |          |

| Global Interrupt Enable (GIE Bit)              | 07       |

| Interrupt-on-Change (RB7:RB4) Enable           | 97       |

| (RBIE Bit)                                     | 00       |

| Interrupts, Flag Bits                          |          |

|                                                |          |

| Interrupt-on-Change (RB7:RB4) Flag             | 21 00    |

| (RBIF Bit)<br>TMR0 Overflow Flag (TMR0IF Bit)  |          |

| I WIND OVERHOW Flag (TWINDIF DIC)              |          |

| К                                              |          |

| KEELOQ Evaluation and Programming Tools        | 114      |

# L

### Μ

| Master Clear (MCLR)                             |  |

|-------------------------------------------------|--|

| MCLR Reset, Normal Operation                    |  |

| MCLR Reset, SLEEP                               |  |

| Master Synchronous Serial Port. See MSSP        |  |

| MCLR/VPP Pin5                                   |  |

| Memory Organization7                            |  |

| Data Memory7                                    |  |

| Program Memory7                                 |  |

| MPLAB C17 and MPLAB C18 C Compilers 111         |  |

| MPLAB ICD In-Circuit Debugger 113               |  |

| MPLAB ICE High Performance Universal In-Circuit |  |

| Emulator with MPLAB IDE 112                     |  |

| MPLAB Integrated Development                    |  |

| Environment Software 111                        |  |

| MPLINK Object Linker/MPLIB Object Librarian 112 |  |

| MSSP                                            |  |

| I <sup>2</sup> C Operation58                    |  |

| Overflow Detect Bit (SSPOV) 59                  |  |

| Special Function Registers                      |  |

| SSPCON 51                                       |  |

| SSPCON251                                       |  |

| SSPSTAT51                                       |  |

| SPI Master Mode 55                              |  |

| SPI Mode 55                                     |  |

| SPI Slave Mode 56                               |  |

| SSPADD                                          |  |

| SSPADD Register 58                              |  |

| SSPBUF 55                                       |  |

| SSPBUF Register 58                              |  |

| SSPSR55, 59                                     |  |

| SSPSTAT Register 58                             |  |

| Multi-Master Communication73                    |  |

|                                                 |  |

# 0

| OPCODE Field Descriptions      | 103        |

|--------------------------------|------------|

| OPTION_REG Register            |            |

| INTEDG Bit                     |            |

| PS2:PS0 Bits                   | 13         |

| PSA Bit                        |            |

| RBPU Bit                       |            |

| T0CS Bit                       | 13         |

| T0SE Bit                       | 13         |

| OSC1/CLKI Pin                  | 5          |

| OSC2/CLKO Pin                  |            |

| Oscillator Configuration       |            |

| HS                             |            |

| LP                             |            |

| RC                             | 89, 90, 92 |

| XT                             |            |

| Oscillator Selection           |            |

| Oscillator, WDT                |            |

| Oscillators                    |            |

| Capacitor Selection            |            |

| Crystal and Ceramic Resonators |            |

| RC                             |            |

|                                |            |