Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

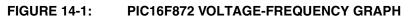

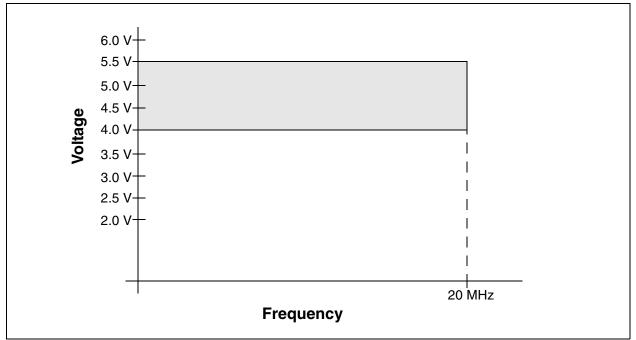

| Speed                      | 20MHz                                                                     |

| Connectivity               | I²C, SPI                                                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 64 × 8                                                                    |

| RAM Size                   | 128 × 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 5.5V                                                               |

| Data Converters            | A/D 5x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf872-i-sp |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 10    |                                              | ~   |

|-------|----------------------------------------------|-----|

| 1.0   | Device Overview                              | 3   |

| 2.0   | Memory Organization                          |     |

| 3.0   | Data EEPROM and FLASH Program Memory         | 23  |

| 4.0   | I/O Ports                                    |     |

| 5.0   | Timer0 Module                                | 35  |

| 6.0   | Timer1 Module                                | 39  |

| 7.0   | Timer2 Module                                |     |

| 8.0   | Capture/Compare/PWM Module                   | 45  |

| 9.0   | Master Synchronous Serial Port (MSSP) Module |     |

| 10.0  | Analog-to-Digital Converter (A/D) Module     | 79  |

| 11.0  | Special Features of the CPU                  | 87  |

| 12.0  | Instruction Set Summary                      |     |

| 13.0  | Development Support                          | 111 |

| 14.0  | Electrical Characteristics                   |     |

| 15.0  | DC and AC Characteristics Graphs and Tables  | 139 |

| 16.0  | Packaging Information                        | 151 |

| Apper | ndix A: Revision History                     | 155 |

| Apper | ndix B: Conversion Considerations            | 155 |

| Index |                                              | 157 |

| On-Li | ne Support                                   | 163 |

|       | er Response                                  |     |

| PIC16 | 6F872 Product Identification System          | 165 |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

| Pin Name           | Pin#  | I/O/P<br>Type | Buffer<br>Type        | Description                                                                                                             |  |  |  |  |

|--------------------|-------|---------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                    |       |               |                       | PORTB is a bi-directional I/O port. PORTB can be software                                                               |  |  |  |  |

|                    |       |               |                       | programmed for internal weak pull-up on all inputs.                                                                     |  |  |  |  |

| RB0/INT            | 21    | I/O           | TTL/ST <sup>(1)</sup> |                                                                                                                         |  |  |  |  |

| RB0                |       |               |                       | Digital I/O.                                                                                                            |  |  |  |  |

| INT                |       |               |                       | External interrupt pin.                                                                                                 |  |  |  |  |

| RB1                | 22    | I/O           | TTL                   | Digital I/O.                                                                                                            |  |  |  |  |

| RB2                | 23    | I/O           | TTL                   | Digital I/O.                                                                                                            |  |  |  |  |

| RB3/PGM            | 24    | I/O           | TTL                   |                                                                                                                         |  |  |  |  |

| RB3                |       |               |                       | Digital I/O.                                                                                                            |  |  |  |  |

| PGM                |       |               |                       | Low voltage ICSP programming enable pin.                                                                                |  |  |  |  |

| RB4                | 25    | I/O           | TTL                   | Digital I/O.                                                                                                            |  |  |  |  |

| RB5                | 26    | I/O           | TTL                   | Digital I/O.                                                                                                            |  |  |  |  |

| RB6/PGC            | 27    | I/O           | TTL/ST <sup>(2)</sup> |                                                                                                                         |  |  |  |  |

| RB6                |       |               |                       | Digital I/O.                                                                                                            |  |  |  |  |

| PGC                |       |               |                       | In-Circuit Debugger and ICSP programming clock.                                                                         |  |  |  |  |

| RB7/PGD            | 28    | I/O           | TTL/ST <sup>(2)</sup> |                                                                                                                         |  |  |  |  |

| RB7<br>PGD         |       |               |                       | Digital I/O.<br>In-Circuit Debugger and ICSP programming data.                                                          |  |  |  |  |

| FGD                |       |               |                       |                                                                                                                         |  |  |  |  |

|                    |       |               | o <del></del>         | PORTC is a bi-directional I/O port.                                                                                     |  |  |  |  |

| RC0/T1OSO/T1CKI    | 11    | I/O           | ST                    | Divite 1/0                                                                                                              |  |  |  |  |

| RC0<br>T1OSO       |       |               |                       | Digital I/O.<br>Timer1 oscillator output.                                                                               |  |  |  |  |

| T1CKI              |       |               |                       | Timer1 clock input.                                                                                                     |  |  |  |  |

| RC1/T1OSI          | 12    | I/O           | ST                    |                                                                                                                         |  |  |  |  |

| RC1                |       | ., 0          | 01                    | Digital I/O.                                                                                                            |  |  |  |  |

| T1OSI              |       |               |                       | Timer1 oscillator input.                                                                                                |  |  |  |  |

| RC2/CCP1           | 13    | I/O           | ST                    |                                                                                                                         |  |  |  |  |

| RC2                |       |               |                       | Digital I/O.                                                                                                            |  |  |  |  |

| CCP1               |       |               |                       | Capture1 input/Compare1 output/PWM1 output.                                                                             |  |  |  |  |

| RC3/SCK/SCL        | 14    | I/O           | ST                    |                                                                                                                         |  |  |  |  |

| RC3                |       |               |                       | Digital I/O.                                                                                                            |  |  |  |  |

| SCK                |       |               |                       | Synchronous serial clock input/output for SPI mode.<br>Synchronous serial clock input/output for I <sup>2</sup> C mode. |  |  |  |  |

| SCL                | 4 -   | 1/2           | <b>O</b> T            | Synchronous senal clock input/output for I=C mode.                                                                      |  |  |  |  |

| RC4/SDI/SDA<br>RC4 | 15    | I/O           | ST                    |                                                                                                                         |  |  |  |  |

| SDI                |       |               |                       | Digital I/O.<br>SPI Data In pin (SPI mode).                                                                             |  |  |  |  |

| SDA                |       |               |                       | SPI Data I/O pin (I <sup>2</sup> C mode).                                                                               |  |  |  |  |

| RC5/SDO            | 16    | I/O           | ST                    |                                                                                                                         |  |  |  |  |

| RC5                |       |               |                       | Digital I/O.                                                                                                            |  |  |  |  |

| SDO                |       |               |                       | SPI Data Out pin (SPI mode).                                                                                            |  |  |  |  |

| RC6                | 17    | I/O           | ST                    | Digital I/O.                                                                                                            |  |  |  |  |

| RC7                | 18    | I/O           | ST                    | Digital I/O.                                                                                                            |  |  |  |  |

| Vss                | 8, 19 | P             |                       | Ground reference for logic and I/O pins.                                                                                |  |  |  |  |

| VDD                | 20    | P             | <u> </u>              | Positive supply for logic and I/O pins.                                                                                 |  |  |  |  |

|                    | -     | O = outp      | I                     | I/O = input/output $P = power$                                                                                          |  |  |  |  |

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

#### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 2-1. The Special Function Registers can be classified into two sets: core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in the peripheral feature section.

| TABLE 2-1: | SPECIAL FUNCTION REGISTER SUMMARY |

|------------|-----------------------------------|

|------------|-----------------------------------|

| Address              | Name    | Bit 7      | Bit 6                                                                                             | Bit 5        | Bit 4         | Bit 3         | Bit 2         | Bit 1       | Bit 0     | Value on:<br>POR,<br>BOR | Details<br>on<br>page: |

|----------------------|---------|------------|---------------------------------------------------------------------------------------------------|--------------|---------------|---------------|---------------|-------------|-----------|--------------------------|------------------------|

| Bank 0               |         |            |                                                                                                   |              |               |               |               |             |           |                          |                        |

| 00h <sup>(2)</sup>   | INDF    |            | Addressing this location uses contents of FSR to address data memory<br>(not a physical register) |              |               |               |               |             |           |                          |                        |

| 01h                  | TMR0    | Timer0 M   | odule Regist                                                                                      | ter          |               |               |               |             |           | xxxx xxxx                | 35, 93                 |

| 02h <sup>(2)</sup>   | PCL     | Program (  | Counter (PC                                                                                       | ) Least Sign | ificant Byte  |               |               |             |           | 0000 0000                | 20, 93                 |

| 03h <sup>(2)</sup>   | STATUS  | IRP        | RP1                                                                                               | RP0          | TO            | PD            | Z             | DC          | С         | 0001 1xxx                | 12, 93                 |

| 04h <sup>(2)</sup>   | FSR     | Indirect D | ata Memory                                                                                        | Address Po   | inter         |               | •             |             | •         | xxxx xxxx                | 21, 93                 |

| 05h                  | PORTA   | _          | _                                                                                                 | PORTA Da     | ta Latch whe  | en written: P | ORTA pins     | when read   |           | 0x 0000                  | 29, 93                 |

| 06h                  | PORTB   | PORTB D    | ata Latch w                                                                                       | hen written: | PORTB pins    | when read     |               |             |           | xxxx xxxx                | 31, 93                 |

| 07h                  | PORTC   | PORTC D    | ata Latch w                                                                                       | hen written: | PORTC pin     | s when read   |               |             |           | xxxx xxxx                | 33, 93                 |

| 08h                  | —       | Unimplem   | nented                                                                                            |              |               |               |               |             |           | —                        |                        |

| 09h                  | —       | Unimplem   | nented                                                                                            |              |               |               |               |             |           | —                        | —                      |

| 0Ah <sup>(1,2)</sup> | PCLATH  | —          | —                                                                                                 | _            | Write Buffe   | er for the up | per 5 bits of | the Program | m Counter | 0 0000                   | 20, 93                 |

| 0Bh <sup>(2)</sup>   | INTCON  | GIE        | PEIE                                                                                              | TMR0IE       | INTE          | RBIE          | TMR0IF        | INTF        | RBIF      | 0000 000x                | 14, 93                 |

| 0Ch                  | PIR1    | (3)        | ADIF                                                                                              | (3)          | (3)           | SSPIF         | CCP1IF        | TMR2IF      | TMR1IF    | r0rr 0000                | 16, 93                 |

| 0Dh                  | PIR2    | _          | (3)                                                                                               |              | EEIF          | BCLIF         | _             | _           | (3)       | -r-0 0r                  | 18, 93                 |

| 0Eh                  | TMR1L   | Holding R  | egister for th                                                                                    | ne Least Sig | nificant Byte | of the 16-bi  | t TMR1 Reg    | gister      |           | xxxx xxxx                | 40, 94                 |

| 0Fh                  | TMR1H   | Holding R  | egister for th                                                                                    | ne Most Sigr | nificant Byte | of the 16-bit | TMR1 Reg      | ister       |           | xxxx xxxx                | 40, 94                 |

| 10h                  | T1CON   | —          | —                                                                                                 | T1CKPS1      | T1CKPS0       | T1OSCEN       | T1SYNC        | TMR1CS      | TMR1ON    | 00 0000                  | 39, 94                 |

| 11h                  | TMR2    | Timer2 M   | odule Regist                                                                                      | ter          |               |               |               |             |           | 0000 0000                | 43, 94                 |

| 12h                  | T2CON   | —          | TOUTPS3                                                                                           | TOUTPS2      | TOUTPS1       | TOUTPS0       | TMR2ON        | T2CKPS1     | T2CKPS0   | -000 0000                | 43, 94                 |

| 13h                  | SSPBUF  | Synchron   | ous Serial P                                                                                      | ort Receive  | Buffer/Trans  | mit Register  |               |             |           | XXXX XXXX                | 55, 94                 |

| 14h                  | SSPCON  | WCOL       | SSPOV                                                                                             | SSPEN        | CKP           | SSPM3         | SSPM2         | SSPM1       | SSPM0     | 0000 0000                | 53, 94                 |

| 15h                  | CCPR1L  |            |                                                                                                   | /M Register  | , ,           |               |               |             |           | xxxx xxxx                | 45, 94                 |

| 16h                  | CCPR1H  | Capture/C  | Compare/PW                                                                                        | /M Register  | I (MSB)       |               |               | -           | _         | XXXX XXXX                | 45, 94                 |

| 17h                  | CCP1CON | —          |                                                                                                   | CCP1X        | CCP1Y         | CCP1M3        | CCP1M2        | CCP1M1      | CCP1M0    | 00 0000                  | 45, 94                 |

| 18h                  | —       | Unimplem   | nented                                                                                            |              |               |               |               |             |           | —                        | —                      |

| 19h                  | —       | Unimplem   |                                                                                                   |              |               |               |               |             |           | —                        |                        |

| 1Ah                  | —       | Unimplem   | nented                                                                                            |              |               |               |               |             |           | —                        |                        |

| 1Bh                  | —       | Unimplem   |                                                                                                   |              |               |               |               |             |           | —                        | —                      |

| 1Ch                  | —       | Unimplem   |                                                                                                   |              |               |               |               |             |           | —                        | —                      |

| 1Dh                  | —       | Unimplem   |                                                                                                   |              |               |               |               |             |           | —                        | —                      |

| 1Eh                  | ADRESH  |            | It Register H                                                                                     |              | r             |               | T             |             |           | XXXX XXXX                | 84, 94                 |

| 1Fh                  | ADCON0  | ADCS1      | ADCS0                                                                                             | CHS2         | CHS1          | CHS0          | GO/<br>DONE   | —           | ADON      | 0000 00-0                | 79, 94                 |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

**2:** These registers can be addressed from any bank.

**3:** These bits are reserved; always maintain these bits clear.

# PIC16F872

#### 2.2.2.5 PIR1 Register

The PIR1 register contains the individual flag bits for the peripheral interrupts.

# Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt bits are clear prior to enabling an interrupt.

## REGISTER 2-5: PIR1 REGISTER (ADDRESS: 0Ch)

| R/W-0    | R/W-0 | R/W-0    | R/W-0    | R/W-0 | R/W-0  | R/W-0  | R/W-0  |

|----------|-------|----------|----------|-------|--------|--------|--------|

| reserved | ADIF  | reserved | reserved | SSPIF | CCP1IF | TMR2IF | TMR1IF |

| bit 7    |       |          |          |       |        |        | bit 0  |

- bit 7 Reserved: Always maintain these bits clear

- bit 6 ADIF: A/D Converter Interrupt Flag bit

- 1 = An A/D conversion completed

- 0 = The A/D conversion is not complete

- bit 5-4 Reserved: Always maintain these bits clear

- bit 3 SSPIF: Synchronous Serial Port (SSP) Interrupt Flag

- 1 = The SSP interrupt condition has occurred, and must be cleared in software before returning from the Interrupt Service Routine. The conditions that will set this bit are:

- SPI

- A transmission/reception has taken place

- I<sup>2</sup>C Slave

- A transmission/reception has taken place

- I<sup>2</sup>C Master

- A transmission/reception has taken place

- The initiated START condition was completed by the SSP module

- The initiated STOP condition was completed by the SSP module

- The initiated Restart condition was completed by the SSP module

- The initiated Acknowledge condition was completed by the SSP module

- A START condition occurred while the SSP module was idle (multi-master system)

- A STOP condition occurred while the SSP module was idle (multi-master system)

- 0 = No SSP interrupt condition has occurred

- bit 2 CCP1IF: CCP1 Interrupt Flag bit

Capture mode:

- 1 = A TMR1 register capture occurred (must be cleared in software)

- 0 = No TMR1 register capture occurred

Compare mode:

- 1 = A TMR1 register compare match occurred (must be cleared in software)

- 0 = No TMR1 register compare match occurred

- PWM mode: Unused in this mode

- bit 1 **TMR2IF**: TMR2 to PR2 Match Interrupt Flag bit

- 1 = TMR2 to PR2 match occurred (must be cleared in software)

- 0 = No TMR2 to PR2 match occurred

## bit 0 TMR1IF: TMR1 Overflow Interrupt Flag bit

- 1 = TMR1 register overflowed (must be cleared in software)

- 0 = TMR1 register did not overflow

| Legend:            |                                                     |                      |                    |  |

|--------------------|-----------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit   | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| - n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |

## 3.4 Reading the FLASH Program Memory

Reading FLASH Program memory is much like that of EEPROM Data memory, only two NOP instructions must be inserted after the RD bit is set. These two instruction cycles that the NOP instructions execute will be used by the microcontroller to read the data out of program memory and insert the value into the EEDATH:EEDATA registers. Data will be available following the second NOP instruction. EEDATH and EEDATA will hold their value until another read operation is initiated, or until they are written by firmware.

The steps to reading the FLASH Program Memory are:

- 1. Write the address to EEADRH:EEADR. Make sure that the address is not larger than the memory size of the device.

- 2. Set the EEPGD bit to point to FLASH Program memory.

- 3. Set the RD bit to start the read operation.

- 4. Execute two NOP instructions to allow the microcontroller to read out of program memory.

- 5. Read the data from the EEDATH:EEDATA registers.

|                      |       | I EAGITT HOUHA |                          |

|----------------------|-------|----------------|--------------------------|

|                      | BSF   | STATUS, RP1    | ;                        |

|                      | BCF   | STATUS, RPO    | ;Bank 2                  |

|                      | MOVF  | ADDRL, W       | ;Write the               |

|                      | MOVWF | EEADR          | ;address bytes           |

|                      | MOVF  | ADDRH,W        | ; for the desired        |

|                      | MOVWF | EEADRH         | ;address to read         |

|                      | BSF   | STATUS, RPO    | ;Bank 3                  |

|                      | BSF   | EECON1, EEPGD  | ;Point to Program memory |

| 8 9                  | BSF   | EECON1, RD     | ;Start read operation    |

| uen                  | NOP   |                | ;Required two NOPs       |

| Required<br>Sequence | NOP   |                | ;                        |

|                      | BCF   | STATUS, RPO    | ;Bank 2                  |

|                      | MOVF  | EEDATA, W      | ;DATAL = EEDATA          |

|                      | MOVWF | DATAL          | ;                        |

|                      | MOVF  | EEDATH,W       | ;DATAH = EEDATH          |

|                      | MOVWF | DATAH          | ;                        |

|                      |       |                |                          |

#### EXAMPLE 3-3: FLASH PROGRAM READ

# 3.5 Writing to the FLASH Program Memory

Writing to FLASH Program memory is unique in that the microcontroller does not execute instructions while programming is taking place. The oscillator continues to run and all peripherals continue to operate and queue interrupts, if enabled. Once the write operation completes (specification #D133), the processor begins executing code from where it left off. The other important difference when writing to FLASH Program memory is that the WRT configuration bit, when clear, prevents any writes to program memory (see Table 3-1).

Just like EEPROM Data memory, there are many steps in writing to the FLASH Program memory. Both address and data values must be written to the SFRs. The EEPGD bit must be set and the WREN bit must be set to enable writes. The WREN bit should be kept clear at all times, except when writing to the FLASH Program memory. The WR bit can only be set if the WREN bit was set in a previous operation, i.e., they both cannot be set in the same operation. The WREN bit should then be cleared by firmware after the write. Clearing the WREN bit before the write actually completes will not terminate the write in progress.

Writes to program memory must also be prefaced with a special sequence of instructions that prevent inadvertent write operations. This is a sequence of five instructions that must be executed without interruption for each byte written. These instructions must then be followed by two NOP instructions to allow the microcontroller to setup for the write operation. Once the write is complete, the execution of instructions starts with the instruction after the second NOP.

| Name         | Bit# | Buffer | Function                                                                        |

|--------------|------|--------|---------------------------------------------------------------------------------|

| RA0/AN0      | bit0 | TTL    | Input/output or analog input.                                                   |

| RA1/AN1      | bit1 | TTL    | Input/output or analog input.                                                   |

| RA2/AN2      | bit2 | TTL    | Input/output or analog input.                                                   |

| RA3/AN3/VREF | bit3 | TTL    | Input/output or analog input or VREF.                                           |

| RA4/T0CKI    | bit4 | ST     | Input/output or external clock input for Timer0.<br>Output is open drain type.  |

| RA5/SS/AN4   | bit5 | TTL    | Input/output or slave select input for synchronous serial port or analog input. |

#### TABLE 4-1: PORTA FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

## TABLE 4-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4                         | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|---------|--------|-------|-------|-------|-------------------------------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 05h     | PORTA  | —     | —     | RA5   | RA4                           | RA3   | RA2   | RA1   | RA0   | 0x 0000                  | 0u 0000                         |

| 85h     | TRISA  | —     |       | PORTA | PORTA Data Direction Register |       |       |       |       |                          | 11 1111                         |

| 9Fh     | ADCON1 | ADFM  | _     | _     |                               | PCFG3 | PCFG2 | PCFG1 | PCFG0 | 0- 0000                  | 0- 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

Note: When using the SSP module in SPI Slave mode and  $\overline{SS}$  enabled, the A/D converter must be set to one of the following modes, where PCFG3:PCFG0 = 0100, 0101, 011x, 1101, 1110, 1111.

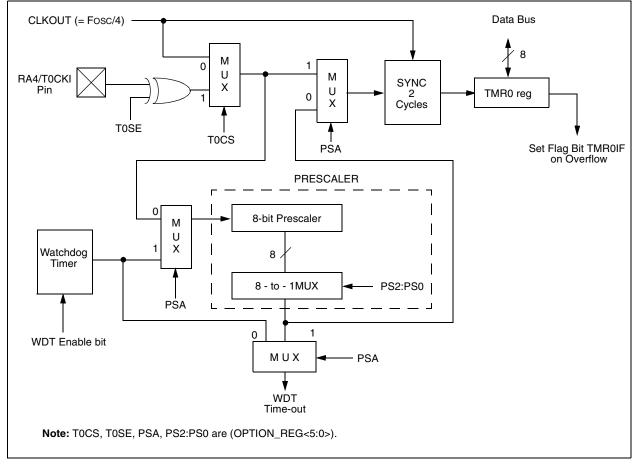

# 5.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge select for external clock

Figure 5-1 is a block diagram of the Timer0 module and the prescaler shared with the WDT.

Additional information on the Timer0 module is available in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023).

Timer mode is selected by clearing bit TOCS (OPTION\_REG<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register. Counter mode is selected by setting bit TOCS (OPTION\_REG<5>). In Counter mode, Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit T0SE (OPTION\_REG<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 5.2.

The prescaler is mutually exclusively shared between the Timer0 module and the Watchdog Timer. The prescaler is not readable or writable. Section 5.3 details the operation of the prescaler.

## 5.1 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit TMR0IF (INTCON<2>). The interrupt can be masked by clearing bit TMR0IE (INTCON<5>). Bit TMR0IF must be cleared in software by the Timer0 module Interrupt Service Routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from SLEEP, since the timer is shut-off during SLEEP.

FIGURE 5-1: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

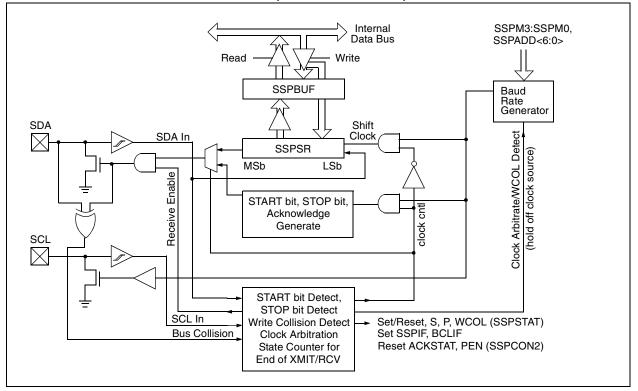

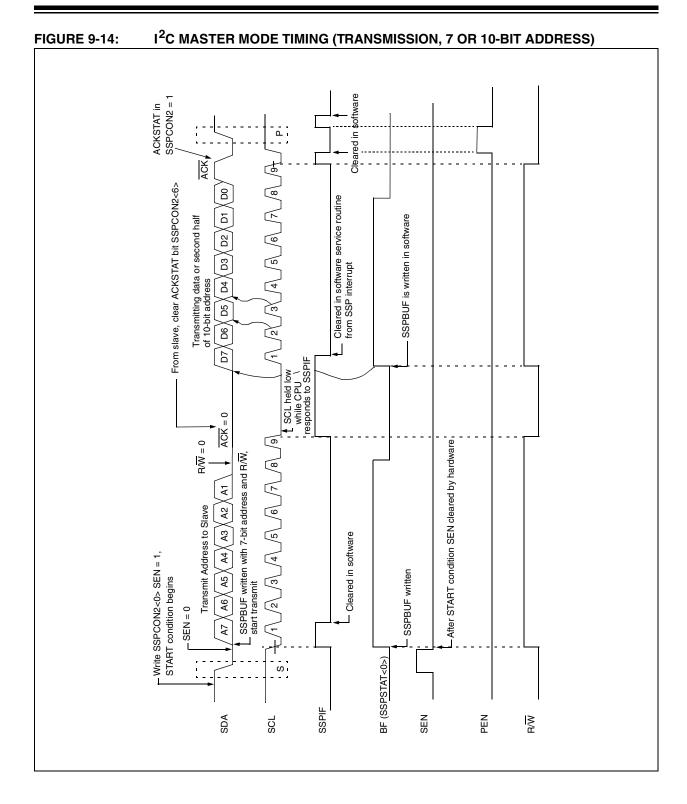

## 9.2.5 MASTER MODE

Master mode of operation is supported by interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared from a RESET or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is IDLE, with both the S and P bits clear.

In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware.

The following events will cause the SSP Interrupt Flag bit, SSPIF, to be set (an SSP Interrupt will occur if enabled):

- START condition

- STOP condition

- · Data transfer byte transmitted/received

- Acknowledge transmit

- Repeated START

# FIGURE 9-9: SSP BLOCK DIAGRAM (I<sup>2</sup>C MASTER MODE)

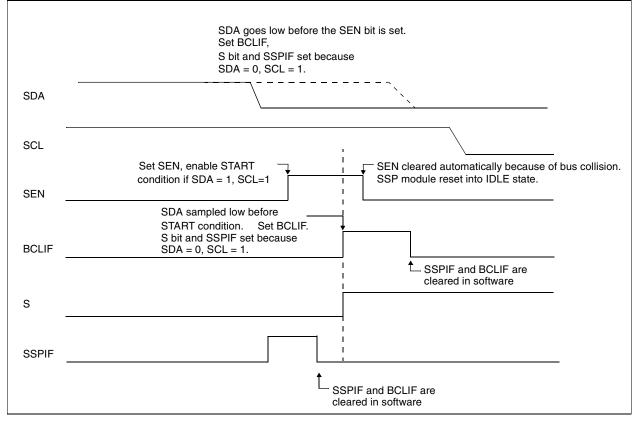

#### 9.2.6 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the START and STOP conditions allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a RESET or when the MSSP module is disabled. Control of the I<sup>2</sup>C bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is IDLE with both the S and P bits clear. When the bus is busy, enabling the SSP interrupt will generate the interrupt when the STOP condition occurs.

In Multi-Master operation, the SDA line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed in hardware, with the result placed in the BCLIF bit. The states where arbitration can be lost are:

- Address Transfer

- Data Transfer

- A START Condition

- A Repeated START Condition

- An Acknowledge Condition

# 9.2.7 I<sup>2</sup>C MASTER MODE SUPPORT

Master mode is enabled by setting and clearing the appropriate SSPM bits in SSPCON and by setting the SSPEN bit. Once Master mode is enabled, the user has six options.

- · Assert a START condition on SDA and SCL.

- Assert a Repeated START condition on SDA and SCL.

- Write to the SSPBUF register, initiating transmission of data/address.

- Generate a STOP condition on SDA and SCL.

- Configure the I<sup>2</sup>C port to receive data.

- Generate an Acknowledge condition at the end of a received byte of data.

- **Note:** The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a START condition and immediately write the SSPBUF register to initiate transmission, before the START condition is complete. In this case, the SSPBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur.

# 9.2.7.1 I<sup>2</sup>C Master Mode Operation

The master device generates all of the serial clock pulses and the START and STOP conditions. A transfer is ended with a STOP condition or with a Repeated START condition. Since the Repeated START condition is also the beginning of the next serial transfer, the  $l^2C$  bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write ( $R/\overline{W}$ ) bit. In this case, the  $R/\overline{W}$  bit will be logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an Acknowledge bit is received. START and STOP conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the R/W bit. In this case, the R/W bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate receive bit. Serial data is received via SDA, while SCL outputs the serial clock. Serial data is received 8 bits at a time. After each byte is received, an Acknowledge bit is transmitted. START and STOP conditions indicate the beginning and end of transmission.

The baud rate generator used for SPI mode operation is now used to set the SCL clock frequency for either 100 kHz, 400 kHz or 1 MHz  $I^2C$  operation. The baud rate generator reload value is contained in the lower 7 bits of the SSPADD register. The baud rate generator will automatically begin counting on a write to the SSPBUF. Once the given operation is complete (i.e., transmission of the last data bit is followed by ACK) the internal clock will automatically stop counting and the SCL pin will remain in its last state

A typical transmit sequence would go as follows:

- a) The user generates a Start Condition by setting the START enable bit (SEN) in SSPCON2.

- b) SSPIF is set. The module will wait the required start time before any other operation takes place.

- c) The user loads the SSPBUF with address to transmit.

- d) Address is shifted out the SDA pin until all 8 bits are transmitted.

- e) The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPCON2 register (SSPCON2<6>).

- f) The module generates an interrupt at the end of the ninth clock cycle by setting SSPIF.

- g) The user loads the SSPBUF with eight bits of data.

- h) DATA is shifted out the SDA pin until all 8 bits are transmitted.

- i) The MSSP module shifts in the ACK bit from the slave device, and writes its value into the SSPCON2 register (SSPCON2<6>).

- j) The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- k) The user generates a STOP condition by setting the STOP enable bit PEN in SSPCON2.

- I) Interrupt is generated once the STOP condition is complete.

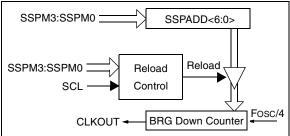

## 9.2.8 BAUD RATE GENERATOR

In  $I^2C$  Master mode, the reload value for the BRG is located in the lower 7 bits of the SSPADD register (Figure 9-10). When the BRG is loaded with this value, the BRG counts down to 0 and stops until another reload has taken place. The BRG count is decremented twice per instruction cycle (TCY), on the Q2 and Q4 clock.

In I<sup>2</sup>C Master mode, the BRG is reloaded automatically. If Clock Arbitration is taking place, for instance, the BRG will be reloaded when the SCL pin is sampled high (Figure 9-11).

FIGURE 9-10:

#### BAUD RATE GENERATOR BLOCK DIAGRAM

# PIC16F872

#### 9.2.18.1 Bus Collision During a START Condition

During a START condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the START condition (Figure 9-20).

- b) SCL is sampled low before SDA is asserted low. (Figure 9-21).

During a START condition, both the SDA and the SCL pins are monitored. If either the SDA pin <u>or</u> the SCL pin is already low, then these events all occur:

- the START condition is aborted,

- and the BCLIF flag is set

- <u>and</u> the SSP module is reset to its IDLE state (Figure 9-20).

The START condition begins with the SDA and SCL pins de-asserted. When the SDA pin is sampled high, the baud rate generator is loaded from SSPADD<6:0> and counts down to 0. If the SCL pin is sampled low while SDA is high, a bus collision occurs, because it is assumed that another master is attempting to drive a data '1' during the START condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 9-22). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The baud rate generator is then reloaded and counts down to 0. During this time, if the SCL pins are sampled as '0', a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a START condition, is that no two bus masters can assert a START condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision, because the two masters must be allowed to arbitrate the first address following the START condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated START or STOP conditions.

# FIGURE 9-20: BUS COLLISION DURING START CONDITION (SDA ONLY)

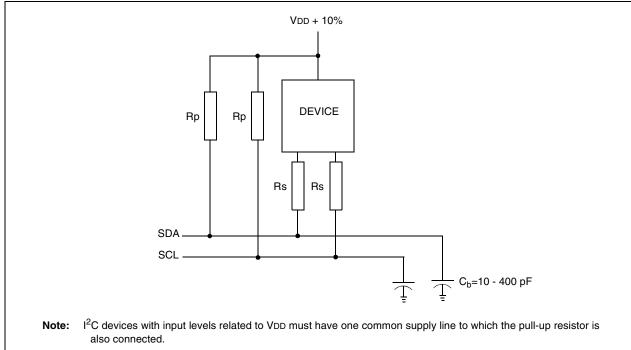

# 9.3 Connection Considerations for I<sup>2</sup>C Bus

For standard mode  $I^2C$  bus devices, the values of resistors  $R_p$  and  $R_s$  in Figure 9-27 depend on the following parameters:

- Supply voltage

- Bus capacitance

- Number of connected devices (input current + leakage current).

The supply voltage limits the minimum value of resistor  $R_p$ , due to the specified minimum sink current of 3 mA at VoL max = 0.4V, for the specified output stages. For example, with a supply voltage of VDD =  $5V\pm10\%$  and

VoL max = 0.4V at 3 mA,  $R_{p \text{ min}} = (5.5-0.4)/0.003 = 1.7 \text{ k}\Omega$ . VDD, as a function of  $R_p$ , is shown in Figure 9-27. The desired noise margin of 0.1 VDD for the low level limits the maximum value of  $R_s$ . Series resistors are optional and used to improve ESD susceptibility.

The bus capacitance is the total capacitance of wire, connections, and pins. This capacitance limits the maximum value of  $R_{p}$ , due to the specified rise time (Figure 9-27).

The SMP bit is the slew rate control enabled bit. This bit is in the SSPSTAT register, and controls the slew rate of the I/O pins when in  $I^2C$  mode (master or slave).

# FIGURE 9-27: SAMPLE DEVICE CONFIGURATION FOR I<sup>2</sup>C BUS

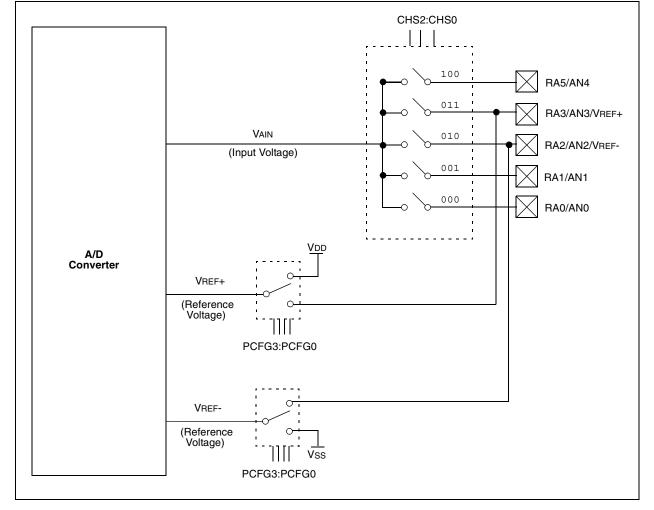

The ADRESH:ADRESL registers contain the 10-bit result of the A/D conversion. When the A/D conversion is complete, the result is loaded into this A/D result register pair, the GO/DONE bit (ADCON0<2>) is cleared and the A/D interrupt flag bit ADIF is set. The block diagram of the A/D module is shown in Figure 10-1.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as inputs.

To determine sample time, see Section 10.1. After this acquisition time has elapsed, the A/D conversion can be started.

These steps should be followed for doing an A/D conversion:

- 1. Configure the A/D module:

- Configure analog pins/voltage reference and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- Clear ADIF bit

- Set ADIE bit

- Set PEIE bit

- · Set GIE bit

- 3. Wait the required acquisition time.

- 4. Start conversion:

- Set GO/DONE bit (ADCON0)

- 5. Wait for A/D conversion to complete, by either:

- Polling for the GO/DONE bit to be cleared (with interrupts enabled); OR

- Waiting for the A/D interrupt

- 6. Read A/D Result register pair (ADRESH:ADRESL), clear bit ADIF if required.

- 7. For the next conversion, go to step 1 or step 2, as required. The A/D conversion time per bit is defined as TAD.

#### TABLE 12-2: PIC16F872 INSTRUCTION SET

| Mnemonic,<br>Operands                  |         | Description                                       | Cycles          |        | 14-Bit    | Opcode   | Status    | Notes        |         |

|----------------------------------------|---------|---------------------------------------------------|-----------------|--------|-----------|----------|-----------|--------------|---------|

|                                        |         | Description                                       |                 | MSb    |           |          | LSb       | Affected     | Notes   |

| BYTE-ORIENTED FILE REGISTER OPERATIONS |         |                                                   |                 |        |           |          |           |              |         |

| ADDWF                                  | f, d    | Add W and f                                       | 1               | 00     | 0111      | dfff     | ffff      | C,DC,Z       | 1,2     |

| ANDWF                                  | f, d    | AND W with f                                      | 1               | 00     | 0101      | dfff     | ffff      | Z            | 1,2     |

| CLRF                                   | f       | Clear f                                           | 1               | 00     | 0001      | lfff     | ffff      | Z            | 2       |

| CLRW                                   | -       | Clear W                                           | 1               | 00     | 0001      | 0xxx     | xxxx      | Z            |         |

| COMF                                   | f, d    | Complement f                                      | 1               | 00     | 1001      | dfff     | ffff      | Z            | 1,2     |

| DECF                                   | f, d    | Decrement f                                       | 1               | 00     | 0011      | dfff     | ffff      | Z            | 1,2     |

| DECFSZ                                 | f, d    | Decrement f, Skip if 0                            | 1(2)            | 00     | 1011      | dfff     | ffff      |              | 1,2,3   |

| INCF                                   | f, d    | Increment f                                       | 1               | 00     | 1010      | dfff     | ffff      | Z            | 1,2     |

| INCFSZ                                 | f, d    | Increment f, Skip if 0                            | 1(2)            | 00     | 1111      | dfff     | ffff      |              | 1,2,3   |

| IORWF                                  | f, d    | Inclusive OR W with f                             | 1               | 00     | 0100      | dfff     | ffff      | Z            | 1,2     |

| MOVF                                   | f, d    | Move f                                            | 1               | 00     | 1000      | dfff     | ffff      | Z            | 1,2     |

| MOVWF                                  | f       | Move W to f                                       | 1               | 00     | 0000      | lfff     | ffff      |              |         |

| NOP                                    | -       | No Operation                                      | 1               | 00     | 0000      | 0xx0     | 0000      |              |         |

| RLF                                    | f, d    | Rotate Left f through Carry                       | 1               | 00     | 1101      | dfff     | ffff      | С            | 1,2     |

| RRF                                    | f, d    | Rotate Right f through Carry                      | 1               | 00     | 1100      | dfff     | ffff      | С            | 1,2     |

| SUBWF                                  | f, d    | Subtract W from f                                 | 1               | 00     | 0010      | dfff     | ffff      | C,DC,Z       | 1,2     |

| SWAPF                                  | f, d    | Swap nibbles in f                                 | 1               | 00     | 1110      | dfff     | ffff      |              | 1,2     |

| XORWF                                  | f, d    | Exclusive OR W with f                             | 1               | 00     | 0110      | dfff     | ffff      | Z            | 1,2     |

|                                        |         | BIT-ORIENTED FILE RI                              | EGISTER OPEF    | RATION | IS        |          |           |              |         |

| BCF                                    | f, b    | Bit Clear f                                       | 1               | 01     | 00bb      | bfff     | ffff      |              | 1,2     |

| BSF                                    | f, b    | Bit Set f                                         | 1               | 01     | 01bb      | bfff     | ffff      |              | 1,2     |

| BTFSC                                  | f, b    | Bit Test f, Skip if Clear                         | 1 (2)           | 01     | 10bb      | bfff     | ffff      |              | 3       |

| BTFSS                                  | f, b    | Bit Test f, Skip if Set                           | 1 (2)           | 01     | 11bb      | bfff     | ffff      |              | 3       |

|                                        |         |                                                   | TROL OPERAT     | IONS   |           |          |           |              |         |

| ADDLW                                  | k       | Add literal and W                                 | 1               | 11     | 111x      | kkkk     | kkkk      | C,DC,Z       |         |

| ANDLW                                  | k       | AND literal with W                                | 1               | 11     | 1001      | kkkk     | kkkk      | Z            |         |

| CALL                                   | k       | Call subroutine                                   | 2               | 10     | 0kkk      | kkkk     | kkkk      |              |         |

| CLRWDT                                 | -       | Clear Watchdog Timer                              | 1               | 00     | 0000      | 0110     | 0100      | TO,PD        |         |

| GOTO                                   | k       | Go to address                                     | 2               | 10     | 1kkk      | kkkk     | kkkk      |              |         |

| IORLW                                  | k       | Inclusive OR literal with W                       | 1               | 11     | 1000      | kkkk     | kkkk      | Z            |         |

| MOVLW                                  | k       | Move literal to W                                 | 1               | 11     | 00xx      | kkkk     | kkkk      |              |         |

| RETFIE                                 | -       | Return from interrupt                             | 2               | 00     | 0000      | 0000     | 1001      |              |         |

| RETLW                                  | k       | Return with literal in W                          | 2               | 11     | 01xx      | kkkk     | kkkk      |              |         |

| RETURN                                 | -       | Return from Subroutine                            | 2               | 00     | 0000      | 0000     | 1000      |              |         |

| SLEEP                                  | -       | Go into Standby mode                              | 1               | 00     | 0000      | 0110     | 0011      | TO,PD        |         |

| SUBLW                                  | k       | Subtract W from literal                           | 1               | 11     | 110x      | kkkk     | kkkk      | C,DC,Z       |         |

| XORLW                                  | k       | Exclusive OR literal with W                       | 1               | 11     | 1010      | kkkk     | kkkk      | Z            |         |

| Note 1:                                | When an | /O register is modified as a function of itself ( | (e.g., MOVF POP | RTB, I | 1), the v | alue use | ed will b | e that value | present |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 module.

3: If Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

Note: Additional information on the mid-range instruction set is available in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023).

# PIC16F872

| MOVF             | Move f                                                                                                                                                                                                                                                                            |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                         |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                                                                                                                                                 |

| Operation:       | (f) $\rightarrow$ (destination)                                                                                                                                                                                                                                                   |

| Status Affected: | Z                                                                                                                                                                                                                                                                                 |

| Description:     | The contents of register f are<br>moved to a destination dependant<br>upon the status of d. If $d = 0$ ,<br>destination is W register. If $d = 1$ ,<br>the destination is file register f itself.<br>d = 1 is useful to test a file register,<br>since status flag Z is affected. |

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| MOVLW            | Move Literal to W                                                                                |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                         |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                |  |  |  |  |  |  |

| Operation:       | $k \to (W)$                                                                                      |  |  |  |  |  |  |

| Status Affected: | None                                                                                             |  |  |  |  |  |  |

| Description:     | The eight-bit literal 'k' is loaded<br>into W register. The don't cares<br>will assemble as 0's. |  |  |  |  |  |  |

| RETFIE           | Return from Interrupt                                   |

|------------------|---------------------------------------------------------|

| Syntax:          | [label] RETFIE                                          |

| Operands:        | None                                                    |

| Operation:       | $\begin{array}{l} TOS \to PC, \\ 1 \to GIE \end{array}$ |

| Status Affected: | None                                                    |

| MOVWF            | Move W to f                                |  |  |  |  |  |  |

|------------------|--------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] MOVWF f                            |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$                          |  |  |  |  |  |  |

| Operation:       | $(W) \rightarrow (f)$                      |  |  |  |  |  |  |

| Status Affected: | None                                       |  |  |  |  |  |  |

| Description:     | Move data from W register to register 'f'. |  |  |  |  |  |  |

| RETLW            | Return with Literal in W                                                                                                                                                            |  |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                            |  |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                                                                                   |  |  |  |  |  |  |  |

| Operation:       | $\begin{array}{l} k \rightarrow (W);\\ TOS \rightarrow PC \end{array}$                                                                                                              |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                |  |  |  |  |  |  |  |

| Description:     | The W register is loaded with the<br>eight-bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address).<br>This is a two-cycle instruction. |  |  |  |  |  |  |  |

# TABLE 13-1: DEVELOPMENT TOOLS FROM MICROCHIP

| Definition   Image: processing state   Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PIC12CXXX                             | PIC16C5X | PIC16C6X | PIC16CXXX | PIC16F62X | X7OðfOld | PIC16C7XX | X8O91OId | PIC16F8XX | XX6O9FOI9 | X4271219 | XX7371319 | PIC18FXXX | 54CXX | 63CXX<br>SeCXX/ | XXXSOH | МСВЕХХХ |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------|----------|-----------|-----------|----------|-----------|----------|-----------|-----------|----------|-----------|-----------|-------|-----------------|--------|---------|

| IntrAd <sup>®</sup> C 1 C Complier   IntrAd <sup>®</sup> C 1 C C Complier   IntrAd <sup>®</sup> C 1 C C C C C C C C C C C C C C C C C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | >                                     |          |          | >         | >         | >        | >         | >        | >         | >         |          |           |           |       |                 |        |         |

| WPLAB* Complet   >                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | C Compiler                            |          |          |           |           |          |           |          |           |           |          |           |           |       |                 |        |         |

| MPCARIW   Messame   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   V   <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | C Compiler                            |          |          |           |           |          |           |          |           |           |          | `         |           |       |                 |        |         |

| MPLAB*/GE Inclorent Emulator   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /   /                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | >                                     |          |          | >         | >         | >        | >         | >        | >         | >         |          |           |           |       | ~               | ~      |         |

| International conditional condi | imulator 🗸                            |          |          | >         | **/       | >        | >         | >        | >         | >         |          | _         |           |       |                 |        |         |