Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | C166                                                                         |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 20MHz                                                                        |

| Connectivity               | CANbus, EBI/EMI, SPI, SSC, UART/USART                                        |

| Peripherals                | POR, PWM, WDT                                                                |

| Number of I/O              | 59                                                                           |

| Program Memory Size        | 64KB (64K x 8)                                                               |

| Program Memory Type        | OTP                                                                          |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 4K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 4.75V ~ 5.5V                                                                 |

| Data Converters            | A/D 8x10b                                                                    |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 80-QFP                                                                       |

| Supplier Device Package    | PG-MQFP-80-7                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/c164ci8emcbkxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Edition 2001-05

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München, Germany © Infineon Technologies AG 2001. All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide.

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

| Table 2 | -   |       |            | anotions      |                                                                               |

|---------|-----|-------|------------|---------------|-------------------------------------------------------------------------------|

| Symbol  |     | Input | Function   |               |                                                                               |

|         | No. | Outp. |            |               |                                                                               |

| P5      |     | 1     |            |               | it-only port with Schmitt-Trigger charact.                                    |

|         |     |       |            |               | so serve as analog input channels for the                                     |

|         |     |       |            | erter, or the | ey serve as timer inputs:                                                     |

| P5.0    | 76  |       | AN0        |               |                                                                               |

| P5.1    | 77  |       | AN1        |               |                                                                               |

| P5.2    | 78  |       | AN2        |               |                                                                               |

| P5.3    | 79  |       | AN3        |               |                                                                               |

| P5.4    | 2   |       | AN4,       | T2EUD         | GPT1 Timer T2 Ext. Up/Down Ctrl. Inp.                                         |

| P5.5    | 3   |       | AN5,       | T4EUD         | GPT1 Timer T4 Ext. Up/Down Ctrl. Inp.                                         |

| P5.6    | 4   | 1     | AN6,       | T2IN          | GPT1 Timer T2 Input for                                                       |

|         |     |       |            |               | Count/Gate/Reload/Capture                                                     |

| P5.7    | 5   | I     | AN7,       | T4IN          | GPT1 Timer T4 Input for                                                       |

|         |     |       |            |               | Count/Gate/Reload/Capture                                                     |

| P3      |     | IO    |            |               | ectional I/O port. It is bit-wise put or output via direction bits. For a pin |

|         |     |       |            |               | the output driver is put into high-                                           |

|         |     |       | -          | -             | ort 3 outputs can be configured as push/                                      |

|         |     |       |            |               | ivers. The input threshold of Port 3 is                                       |

|         |     |       | selectable |               | -                                                                             |

|         |     |       | The follow | ing Port 3    | pins also serve for alternate functions:                                      |

| P3.4    | 8   | 1     | T3EUD      | GPT1 Ti       | mer T3 External Up/Down Control Input                                         |

| P3.6    | 9   | 1     | T3IN       | GPT1 T        | imer T3 Count/Gate Input                                                      |

| P3.8    | 10  | I/O   | MRST       | SSC Ma        | ster-Receive/Slave-Transmit Inp./Outp.                                        |

| P3.9    | 11  | I/O   | MTSR       | SSC Ma        | ster-Transmit/Slave-Receive Outp./Inp.                                        |

| P3.10   | 12  | 0     | TxD0       | ASC0 C        | lock/Data Output (Async./Sync.)                                               |

| P3.11   | 13  | I/O   | RxD0       |               | ata Input (Async.) or Inp./Outp. (Sync.)                                      |

| P3.12   | 14  | 0     | BHE        | External      | Memory High Byte Enable Signal,                                               |

|         |     | 0     | WRH        |               | Memory High Byte Write Strobe                                                 |

| P3.13   | 15  | I/O   | SCLK       |               | ster Clock Output / Slave Clock Input.                                        |

| P3.15   | 16  | 0     | CLKOUT     | -             | Clock Output (= CPU Clock),                                                   |

|         |     | 0     | FOUT       | Program       | mable Frequency Output                                                        |

# Table 2Pin Definitions and Functions

| Table 2                            | Pi         | Pin Definitions and Functions (cont'd) |                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                       |            |  |  |  |  |

|------------------------------------|------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------|--|--|--|--|

| Symbol                             | Pin<br>No. | Input<br>Outp.                         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                               |                       |            |  |  |  |  |

| ĒĀ/V <sub>PP</sub>                 | 28         | I                                      | External Access Enable pin.<br><b>A low level</b> at this pin during and after Reset forces the<br>C164CI to latch the configuration from PORT0 and pin RD,<br>and to begin instruction execution out of external memory.<br><b>A high level</b> forces the C164CI to latch the configuration<br>from pins RD and ALE, and to begin instruction execution out<br>of the internal program memory.<br>"ROMless" versions must have this pin tied to '0'. |                       |            |  |  |  |  |

|                                    |            |                                        | Note: This pin also accepts the programming voltage for the OTP derivatives.                                                                                                                                                                                                                                                                                                                                                                           |                       |            |  |  |  |  |

| <b>PORT0</b><br>P0L.0-7<br>P0H.0-7 | 36         | IO                                     | PORT0 consists of the two 8-bit bidirectional I/O ports P0L<br>and P0H. It is bit-wise programmable for input or output via<br>direction bits. For a pin configured as input, the output driver                                                                                                                                                                                                                                                        |                       |            |  |  |  |  |

|                                    | 42-46      |                                        | is put into high-impedance state.<br>In case of an external bus configuration, PORT0 serves as<br>the address (A) and address/data (AD) bus in multiplexed<br>bus modes and as the data (D) bus in demultiplexed bus<br>modes.                                                                                                                                                                                                                         |                       |            |  |  |  |  |

|                                    |            |                                        | Demultiplexed bus                                                                                                                                                                                                                                                                                                                                                                                                                                      | modes:                |            |  |  |  |  |

|                                    |            |                                        | Data Path Width:                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8-bit                 | 16-bit     |  |  |  |  |

|                                    |            |                                        | P0L.0 – P0L.7:                                                                                                                                                                                                                                                                                                                                                                                                                                         | D0 – D7               | D0 – D7    |  |  |  |  |

|                                    |            |                                        | P0H.0 – P0H.7:                                                                                                                                                                                                                                                                                                                                                                                                                                         | I/O                   | D8 – D15   |  |  |  |  |

|                                    |            |                                        | Multiplexed bus mo<br>Data Path Width:                                                                                                                                                                                                                                                                                                                                                                                                                 | odes:<br>8-bit        | 16-bit     |  |  |  |  |

|                                    |            |                                        | POL.0 - POL.7:                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8-Dil<br>AD0 – AD7    |            |  |  |  |  |

|                                    |            |                                        | P0H.0 – P0H.7:                                                                                                                                                                                                                                                                                                                                                                                                                                         | AB0 – AD7<br>A8 – A15 | AD8 – AD15 |  |  |  |  |

The C164CI also provides an excellent mechanism to identify and to process exceptions or error conditions that arise during run-time, so-called 'Hardware Traps'. Hardware traps cause immediate non-maskable system reaction which is similar to a standard interrupt service (branching to a dedicated vector table location). The occurrence of a hardware trap is additionally signified by an individual bit in the trap flag register (TFR). Except when another higher prioritized trap service is in progress, a hardware trap will interrupt any actual program execution. In turn, hardware trap services can normally not be interrupted by standard or PEC interrupts.

**Table 4** shows all of the possible exceptions or error conditions that can arise during runtime:

| Exception Condition                                                                          | Trap<br>Flag          | Trap<br>Vector                | Vector<br>Location                                                                      | Trap<br>Number                                        | Trap<br>Priority           |

|----------------------------------------------------------------------------------------------|-----------------------|-------------------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------|

| Reset Functions:<br>– Hardware Reset<br>– Software Reset<br>– W-dog Timer Overflow           | -                     | RESET<br>RESET<br>RESET       | 00'0000 <sub>H</sub><br>00'0000 <sub>H</sub><br>00'0000 <sub>H</sub>                    | 00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub> | <br>   <br>                |

| Class A Hardware Traps:<br>– Non-Maskable Interrupt<br>– Stack Overflow<br>– Stack Underflow | NMI<br>STKOF<br>STKUF | NMITRAP<br>STOTRAP<br>STUTRAP | 00'0008 <sub>H</sub><br>00'0010 <sub>H</sub><br>00'0018 <sub>H</sub>                    | 02 <sub>H</sub><br>04 <sub>H</sub><br>06 <sub>H</sub> | <br>  <br>                 |

| Class B Hardware Traps:<br>– Undefined Opcode<br>– Protected Instruction<br>Fault            | UNDOPC<br>PRTFLT      | BTRAP<br>BTRAP                | 00'0028 <sub>H</sub><br>00'0028 <sub>H</sub>                                            | 0A <sub>H</sub><br>0A <sub>H</sub>                    | 1                          |

| <ul> <li>Illegal Word Operand<br/>Access</li> </ul>                                          | ILLOPA                | BTRAP                         | 00'0028 <sub>H</sub>                                                                    | 0A <sub>H</sub>                                       | I                          |

| <ul> <li>Illegal Instruction<br/>Access</li> </ul>                                           | ILLINA                | BTRAP                         | 00'0028 <sub>H</sub>                                                                    | 0A <sub>H</sub>                                       | 1                          |

| <ul> <li>Illegal External Bus<br/>Access</li> </ul>                                          | ILLBUS                | BTRAP                         | 00'0028 <sub>H</sub>                                                                    | 0A <sub>H</sub>                                       | 1                          |

| Reserved                                                                                     | _                     | _                             | [2C <sub>H</sub> –<br>3C <sub>H</sub> ]                                                 | [0B <sub>H</sub> –<br>0F <sub>H</sub> ]               | -                          |

| Software Traps<br>– TRAP Instruction                                                         | _                     | _                             | Any<br>[00'0000 <sub>H</sub><br>00'01FC <sub>H</sub> ]<br>in steps<br>of 4 <sub>H</sub> | Any<br>[00 <sub>H</sub> –<br>7F <sub>H</sub> ]        | Current<br>CPU<br>Priority |

### Table 4Hardware Trap Summary

### A/D Converter

For analog signal measurement, a 10-bit A/D converter with 8 multiplexed input channels and a sample and hold circuit has been integrated on-chip. It uses the method of successive approximation. The sample time (for loading the capacitors) and the conversion time is programmable and can so be adjusted to the external circuitry.

Overrun error detection/protection is provided for the conversion result register (ADDAT): either an interrupt request will be generated when the result of a previous conversion has not been read from the result register at the time the next conversion is complete, or the next conversion is suspended in such a case until the previous result has been read.

For applications which require less than 8 analog input channels, the remaining channel inputs can be used as digital input port pins.

The A/D converter of the C164CI supports four different conversion modes. In the standard Single Channel conversion mode, the analog level on a specified channel is sampled once and converted to a digital result. In the Single Channel Continuous mode, the analog level on a specified channel is repeatedly sampled and converted without software intervention. In the Auto Scan mode, the analog levels on a prespecified number of channels (standard or extension) are sequentially sampled and converted. In the Auto Scan Continuous mode, the number of prespecified channels is repeatedly sampled and converted. In the Auto Scan Continuous mode, the conversion of a specific channel can be inserted (injected) into a running sequence without disturbing this sequence. This is called Channel Injection Mode.

The Peripheral Event Controller (PEC) may be used to automatically store the conversion results into a table in memory for later evaluation, without requiring the overhead of entering and exiting interrupt routines for each data transfer.

After each reset and also during normal operation the ADC automatically performs calibration cycles. This automatic self-calibration constantly adjusts the converter to changing operating conditions (e.g. temperature) and compensates process variations.

These calibration cycles are part of the conversion cycle, so they do not affect the normal operation of the A/D converter.

In order to decouple analog inputs from digital noise and to avoid input trigger noise those pins used for analog input can be disconnected from the digital IO or input stages under software control. This can be selected for each pin separately via register P5DIDIS (Port 5 Digital Input Disable).

## **Parallel Ports**

The C164CI provides up to 59 I/O lines which are organized into five input/output ports and one input port. All port lines are bit-addressable, and all input/output lines are individually (bit-wise) programmable as inputs or outputs via direction registers. The I/O ports are true bidirectional ports which are switched to high impedance state when configured as inputs. The output drivers of three I/O ports can be configured (pin by pin) for push/pull operation or open-drain operation via control registers. During the internal reset, all port pins are configured as inputs.

The input threshold of Port 3, Port 4, and Port 8 is selectable (TTL or CMOS like), where the special CMOS like input threshold reduces noise sensitivity due to the input hysteresis. The input threshold may be selected individually for each byte of the respective ports.

All port lines have programmable alternate input or output functions associated with them. All port lines that are not used for these alternate functions may be used as general purpose IO lines.

PORT0 and PORT1 may be used as address and data lines when accessing external memory, while Port 4 outputs the additional segment address bits A21/19/17 ... A16 and the optional chip select signals in systems where segmentation is enabled to access more than 64 KBytes of memory.

Ports P1L, P1H, and P8 are associated with the capture inputs or compare outputs of the CAPCOM units and/or serve as external interrupt inputs.

Port 3 includes alternate functions of timers, serial interfaces, the optional bus control signal BHE/WRH, and the system clock output CLKOUT (or the programmable frequency output FOUT).

Port 5 is used for the analog input channels to the A/D converter or timer control signals.

The edge characteristics (transition time) and driver characteristics (output current) of the C164CI's port drivers can be selected via the Port Output Control registers (POCONx).

#### Power Management

The C164CI provides several means to control the power it consumes either at a given time or averaged over a certain timespan. Three mechanisms can be used (partly in parallel):

• **Power Saving Modes** switch the C164CI into a special operating mode (control via instructions).

Idle Mode stops the CPU while the peripherals can continue to operate.

Sleep Mode and Power Down Mode stop all clock signals and all operation (RTC may optionally continue running). Sleep Mode can be terminated by external interrupt signals.

Clock Generation Management controls the distribution and the frequency of internal and external clock signals (control via register SYSCON2).

Slow Down Mode lets the C164CI run at a CPU clock frequency of f<sub>OSC</sub>/1 ... 32 (half for prescaler operation) which drastically reduces the consumed power. The PLL can be optionally disabled while operating in Slow Down Mode.

External circuitry can be controlled via the programmable frequency output FOUT.

• **Peripheral Management** permits temporary disabling of peripheral modules (control via register SYSCON3).

Each peripheral can separately be disabled/enabled. A group control option disables a major part of the peripheral set by setting one single bit.

The on-chip RTC supports intermittend operation of the C164CI by generating cyclic wakeup signals. This offers full performance to quickly react on action requests while the intermittend sleep phases greatly reduce the average power consumption of the system.

#### **Special Function Registers Overview**

**Table 7** lists all SFRs which are implemented in the C164CI in alphabetical order. **Bit-addressable** SFRs are marked with the letter "**b**" in column "Name". SFRs within the **Extended SFR-Space** (ESFRs) are marked with the letter "**E**" in column "Physical Address". Registers within on-chip X-peripherals are marked with the letter "**X**" in column "Physical Address".

An SFR can be specified via its individual mnemonic name. Depending on the selected addressing mode, an SFR can be accessed via its physical address (using the Data Page Pointers), or via its short 8-bit address (without using the Data Page Pointers).

| Name     |   | Physica<br>Address |   | 8-Bit<br>Addr.  | Description                                                   | Reset<br>Value    |

|----------|---|--------------------|---|-----------------|---------------------------------------------------------------|-------------------|

| ADCIC    | b | FF98 <sub>H</sub>  |   | CCH             | A/D Converter End of Conversion<br>Interrupt Control Register | 0000 <sub>H</sub> |

| ADCON    | b | FFA0 <sub>H</sub>  |   | D0 <sub>H</sub> | A/D Converter Control Register                                | 0000 <sub>H</sub> |

| ADDAT    |   | FEA0 <sub>H</sub>  |   | 50 <sub>H</sub> | A/D Converter Result Register                                 | 0000 <sub>H</sub> |

| ADDAT2   |   | F0A0 <sub>H</sub>  | Ε | 50 <sub>H</sub> | A/D Converter 2 Result Register                               | 0000 <sub>H</sub> |

| ADDRSEL1 |   | FE18 <sub>H</sub>  |   | 0C <sub>H</sub> | Address Select Register 1                                     | 0000 <sub>H</sub> |

| ADDRSEL2 |   | FE1A <sub>H</sub>  |   | 0D <sub>H</sub> | Address Select Register 2                                     | 0000 <sub>H</sub> |

| ADDRSEL3 |   | FE1C <sub>H</sub>  |   | 0E <sub>H</sub> | Address Select Register 3                                     | 0000 <sub>H</sub> |

| ADDRSEL4 | • | FE1E <sub>H</sub>  |   | 0F <sub>H</sub> | Address Select Register 4                                     | 0000 <sub>H</sub> |

| ADEIC    | b | FF9A <sub>H</sub>  |   | CD <sub>H</sub> | A/D Converter Overrun Error Interrupt<br>Control Register     | 0000 <sub>H</sub> |

| BUSCON0  | b | FF0C <sub>H</sub>  |   | 86 <sub>H</sub> | Bus Configuration Register 0                                  | 0000 <sub>H</sub> |

| BUSCON1  | b | FF14 <sub>H</sub>  |   | 8A <sub>H</sub> | Bus Configuration Register 1                                  | 0000 <sub>H</sub> |

| BUSCON2  | b | FF16 <sub>H</sub>  |   | 8B <sub>H</sub> | Bus Configuration Register 2                                  | 0000 <sub>H</sub> |

| BUSCON3  | b | FF18 <sub>H</sub>  |   | 8C <sub>H</sub> | Bus Configuration Register 3                                  | 0000 <sub>H</sub> |

| BUSCON4  | b | FF1A <sub>H</sub>  |   | 8D <sub>H</sub> | Bus Configuration Register 4                                  | 0000 <sub>H</sub> |

| C1BTR    |   | EF04 <sub>H</sub>  | Χ |                 | CAN1 Bit Timing Register                                      | UUUU <sub>H</sub> |

| C1CSR    |   | EF00 <sub>H</sub>  | Χ |                 | CAN1 Control / Status Register                                | XX01 <sub>H</sub> |

| C1GMS    |   | EF06 <sub>H</sub>  | Χ |                 | CAN1 Global Mask Short                                        | UFUU <sub>H</sub> |

| C1LARn   |   | EFn4 <sub>H</sub>  | Χ |                 | CAN Lower Arbitration Register (msg. n)                       | UUUU <sub>H</sub> |

| C1LGML   |   | EF0A <sub>H</sub>  | Χ |                 | CAN Lower Global Mask Long                                    | UUUU <sub>H</sub> |

| C1LMLM   |   | EF0E <sub>H</sub>  | Χ |                 | CAN Lower Mask of Last Message                                | UUUU <sub>H</sub> |

#### Table 7 C164Cl Registers, Ordered by Name

| Table 7C164Cl Registers, Ordered by Name (cont'd) |   |                    |   |                 |                                         |                   |  |

|---------------------------------------------------|---|--------------------|---|-----------------|-----------------------------------------|-------------------|--|

| Name                                              |   | Physica<br>Address |   | 8-Bit<br>Addr.  | Description                             | Reset<br>Value    |  |

| CTCON                                             | b | FF30 <sub>H</sub>  |   | 98 <sub>H</sub> | CAPCOM 6 Compare Timer Ctrl. Reg.       | 1010 <sub>H</sub> |  |

| DP0H                                              | b | F102 <sub>H</sub>  | Ε | 81 <sub>H</sub> | P0H Direction Control Register          | 00 <sub>H</sub>   |  |

| DP0L                                              | b | F100 <sub>H</sub>  | Ε | 80 <sub>H</sub> | P0L Direction Control Register          | 00 <sub>H</sub>   |  |

| DP1H                                              | b | F106 <sub>H</sub>  | Ε | 83 <sub>H</sub> | P1H Direction Control Register          | 00 <sub>H</sub>   |  |

| DP1L                                              | b | F104 <sub>H</sub>  | Ε | 82 <sub>H</sub> | P1L Direction Control Register          | 00 <sub>H</sub>   |  |

| DP3                                               | b | FFC6 <sub>H</sub>  |   | E3 <sub>H</sub> | Port 3 Direction Control Register       | 0000 <sub>H</sub> |  |

| DP4                                               | b | FFCA <sub>H</sub>  |   | E5 <sub>H</sub> | Port 4 Direction Control Register       | 00 <sub>H</sub>   |  |

| DP8                                               | b | FFD6 <sub>H</sub>  |   | EB <sub>H</sub> | Port 8 Direction Control Register       | 00 <sub>H</sub>   |  |

| DPP0                                              |   | FE00 <sub>H</sub>  |   | 00 <sub>H</sub> | CPU Data Page Pointer 0 Reg. (10 bits)  | 0000 <sub>H</sub> |  |

| DPP1                                              |   | FE02 <sub>H</sub>  |   | 01 <sub>H</sub> | CPU Data Page Pointer 1 Reg. (10 bits)  | 0001 <sub>H</sub> |  |

| DPP2                                              |   | FE04 <sub>H</sub>  |   | 02 <sub>H</sub> | CPU Data Page Pointer 2 Reg. (10 bits)  | 0002 <sub>H</sub> |  |

| DPP3                                              |   | FE06 <sub>H</sub>  |   | 03 <sub>H</sub> | CPU Data Page Pointer 3 Reg. (10 bits)  | 0003 <sub>H</sub> |  |

| EXICON                                            | b | F1C0 <sub>H</sub>  | Ε | E0 <sub>H</sub> | External Interrupt Control Register     | 0000 <sub>H</sub> |  |

| EXISEL                                            | b | F1DA <sub>H</sub>  | Ε | ED <sub>H</sub> | External Interrupt Source Select Reg.   | 0000 <sub>H</sub> |  |

| FOCON                                             | b | FFAA <sub>H</sub>  |   | D5 <sub>H</sub> | Frequency Output Control Register       | 0000 <sub>H</sub> |  |

| IDCHIP                                            |   | F07C <sub>H</sub>  | Ε | 3E <sub>H</sub> | Identifier                              | XXXX <sub>H</sub> |  |

| IDMANUF                                           |   | F07E <sub>H</sub>  | Ε | 3F <sub>H</sub> | Identifier                              | 1820 <sub>H</sub> |  |

| IDMEM                                             |   | F07A <sub>H</sub>  | Ε | 3D <sub>H</sub> | Identifier                              | XXXX <sub>H</sub> |  |

| IDPROG                                            |   | F078 <sub>H</sub>  | Ε | 3C <sub>H</sub> | Identifier                              | XXXX <sub>H</sub> |  |

| IDMEM2                                            |   | F076 <sub>H</sub>  | Ε | 3B <sub>H</sub> | Identifier                              | XXXX <sub>H</sub> |  |

| ISNC                                              | b | F1DE <sub>H</sub>  | Ε | EF <sub>H</sub> | Interrupt Subnode Control Register      | 0000 <sub>H</sub> |  |

| MDC                                               | b | FF0E <sub>H</sub>  |   | 87 <sub>H</sub> | CPU Multiply Divide Control Register    | 0000 <sub>H</sub> |  |

| MDH                                               |   | FE0C <sub>H</sub>  |   | 06 <sub>H</sub> | CPU Multiply Divide Reg. – High Word    | 0000 <sub>H</sub> |  |

| MDL                                               |   | FE0E <sub>H</sub>  |   | 07 <sub>H</sub> | CPU Multiply Divide Reg. – Low Word     | 0000 <sub>H</sub> |  |

| ODP3                                              | b | F1C6 <sub>H</sub>  | Ε | E3 <sub>H</sub> | Port 3 Open Drain Control Register      | 0000 <sub>H</sub> |  |

| ODP4                                              | b | F1CA <sub>H</sub>  | Ε | E5 <sub>H</sub> | Port 4 Open Drain Control Register      | 00 <sub>H</sub>   |  |

| ODP8                                              | b | F1D6 <sub>H</sub>  | Ε | EB <sub>H</sub> | Port 8 Open Drain Control Register      | 00 <sub>H</sub>   |  |

| ONES                                              | b | FF1E <sub>H</sub>  |   | 8F <sub>H</sub> | Constant Value 1's Register (read only) | FFFF <sub>H</sub> |  |

| OPAD                                              |   | EDC2 <sub>H</sub>  | Χ |                 | OTP Progr. Interface Address Register   | 0000 <sub>H</sub> |  |

|                                                   |   |                    |   |                 |                                         |                   |  |

# ......

OPCTRL

EDC0<sub>H</sub> X

---

0007<sub>H</sub>

OTP Progr. Interface Control Register

# Table 7C164Cl Registers, Ordered by Name (cont'd)

| Name Physical<br>Address |   |                   | 8-Bit<br>Addr. | Description     | Reset<br>Value                         |                   |

|--------------------------|---|-------------------|----------------|-----------------|----------------------------------------|-------------------|

| OPDAT                    |   | EDC4 <sub>H</sub> | X              |                 | OTP Progr. Interface Data Register     | 0000 <sub>H</sub> |

| P0H                      | b | FF02 <sub>H</sub> |                | 81 <sub>H</sub> | Port 0 High Reg. (Upper half of PORT0) | 00 <sub>H</sub>   |

| P0L                      | b | FF00 <sub>H</sub> |                | 80 <sub>H</sub> | Port 0 Low Reg. (Lower half of PORT0)  | 00 <sub>H</sub>   |

| P1H                      | b | FF06 <sub>H</sub> |                | 83 <sub>H</sub> | Port 1 High Reg. (Upper half of PORT1) | 00 <sub>H</sub>   |

| P1L                      | b | FF04 <sub>H</sub> |                | 82 <sub>H</sub> | Port 1 Low Reg. (Lower half of PORT1)  | 00 <sub>H</sub>   |

| P3                       | b | FFC4 <sub>H</sub> |                | E2 <sub>H</sub> | Port 3 Register                        | 0000 <sub>H</sub> |

| P4                       | b | FFC8 <sub>H</sub> |                | E4 <sub>H</sub> | Port 4 Register (7 bits)               | 00 <sub>H</sub>   |

| P5                       | b | FFA2 <sub>H</sub> |                | D1 <sub>H</sub> | Port 5 Register (read only)            | XXXX <sub>H</sub> |

| P5DIDIS                  | b | FFA4 <sub>H</sub> |                | D2 <sub>H</sub> | Port 5 Digital Input Disable Register  | 0000 <sub>H</sub> |

| P8                       | b | FFD4 <sub>H</sub> |                | EA <sub>H</sub> | Port 8 Register (8 bits)               | 00 <sub>H</sub>   |

| PECC0                    |   | FEC0 <sub>H</sub> |                | 60 <sub>H</sub> | PEC Channel 0 Control Register         | 0000 <sub>H</sub> |

| PECC1                    |   | FEC2 <sub>H</sub> |                | 61 <sub>H</sub> | PEC Channel 1 Control Register         | 0000 <sub>H</sub> |

| PECC2                    |   | FEC4 <sub>H</sub> |                | 62 <sub>H</sub> | PEC Channel 2 Control Register         | 0000 <sub>H</sub> |

| PECC3                    |   | FEC6 <sub>H</sub> |                | 63 <sub>H</sub> | PEC Channel 3 Control Register         | 0000 <sub>H</sub> |

| PECC4                    |   | FEC8 <sub>H</sub> |                | 64 <sub>H</sub> | PEC Channel 4 Control Register         | 0000 <sub>H</sub> |

| PECC5                    |   | FECA <sub>H</sub> |                | 65 <sub>H</sub> | PEC Channel 5 Control Register         | 0000 <sub>H</sub> |

| PECC6                    |   | FECC <sub>H</sub> |                | 66 <sub>H</sub> | PEC Channel 6 Control Register         | 0000 <sub>H</sub> |

| PECC7                    |   | FECE <sub>H</sub> |                | 67 <sub>H</sub> | PEC Channel 7 Control Register         | 0000 <sub>H</sub> |

| PICON                    | b | F1C4 <sub>H</sub> | Ε              | E2 <sub>H</sub> | Port Input Threshold Control Register  | 0000 <sub>H</sub> |

| POCON0H                  |   | F082 <sub>H</sub> | Ε              | 41 <sub>H</sub> | Port P0H Output Control Register       | 0011 <sub>H</sub> |

| POCON0L                  |   | F080 <sub>H</sub> | Ε              | 40 <sub>H</sub> | Port P0L Output Control Register       | 0011 <sub>H</sub> |

| POCON1H                  |   | F086 <sub>H</sub> | Ε              | 43 <sub>H</sub> | Port P1H Output Control Register       | 0011 <sub>H</sub> |

| POCON1L                  |   | F084 <sub>H</sub> | Ε              | 42 <sub>H</sub> | Port P1L Output Control Register       | 0011 <sub>H</sub> |

| POCON20                  |   | F0AA <sub>H</sub> | Ε              | 55 <sub>H</sub> | Dedicated Pin Output Control Register  | 0000 <sub>H</sub> |

| POCON3                   |   | F08A <sub>H</sub> | Ε              | 45 <sub>H</sub> | Port P3 Output Control Register        | 2222 <sub>H</sub> |

| POCON4                   |   | F08C <sub>H</sub> | Ε              | 46 <sub>H</sub> | Port P4 Output Control Register        | 0010 <sub>H</sub> |

| POCON8                   |   | F092 <sub>H</sub> | Ε              | 49 <sub>H</sub> | Port P8 Output Control Register        | 0022 <sub>H</sub> |

| PSW                      | b | FF10 <sub>H</sub> |                | 88 <sub>H</sub> | CPU Program Status Word                | 0000 <sub>H</sub> |

| RP0H                     | b | F108 <sub>H</sub> | Ε              | 84 <sub>H</sub> | System Startup Config. Reg. (Rd. only) | XXH               |

| RSTCON                   | b | F1E0 <sub>H</sub> | m              |                 | Reset Control Register                 | 00XX <sub>H</sub> |

| Table 7C164Cl Registers | , Ordered by Name (cont'd) |

|-------------------------|----------------------------|

|-------------------------|----------------------------|

| Name Physical<br>Address |   | 8-Bit<br>Addr.    | Description | Reset<br>Value  |                                         |                                 |

|--------------------------|---|-------------------|-------------|-----------------|-----------------------------------------|---------------------------------|

| T12IC                    | b | F190 <sub>H</sub> | Е           | C8 <sub>H</sub> | CAPCOM 6 Timer 12 Interrupt Ctrl. Reg.  | 0000 <sub>H</sub>               |

| T12OF                    |   | F034 <sub>H</sub> | Ε           | 1A <sub>H</sub> | CAPCOM 6 Timer 12 Offset Register       | 0000 <sub>H</sub>               |

| T12P                     |   | F030 <sub>H</sub> | Ε           | 18 <sub>H</sub> | CAPCOM 6 Timer 12 Period Register       | 0000 <sub>H</sub>               |

| T13IC                    | b | F198 <sub>H</sub> | Ε           | CCH             | CAPCOM 6 Timer 13 Interrupt Ctrl. Reg.  | 0000 <sub>H</sub>               |

| T13P                     |   | F032 <sub>H</sub> | Ε           | 19 <sub>H</sub> | CAPCOM 6 Timer 13 Period Register       | 0000 <sub>H</sub>               |

| T14                      |   | F0D2 <sub>H</sub> | Ε           | 69 <sub>H</sub> | RTC Timer 14 Register                   | no                              |

| T14REL                   |   | F0D0 <sub>H</sub> | Ε           | 68 <sub>H</sub> | RTC Timer 14 Reload Register            | no                              |

| T2                       |   | FE40 <sub>H</sub> |             | 20 <sub>H</sub> | GPT1 Timer 2 Register                   | 0000 <sub>H</sub>               |

| T2CON                    | b | FF40 <sub>H</sub> |             | A0 <sub>H</sub> | GPT1 Timer 2 Control Register           | 0000 <sub>H</sub>               |

| T2IC                     | b | FF60 <sub>H</sub> |             | B0 <sub>H</sub> | GPT1 Timer 2 Interrupt Control Register | 0000 <sub>H</sub>               |

| Т3                       |   | FE42 <sub>H</sub> |             | 21 <sub>H</sub> | GPT1 Timer 3 Register                   | 0000 <sub>H</sub>               |

| T3CON                    | b | FF42 <sub>H</sub> |             | A1 <sub>H</sub> | GPT1 Timer 3 Control Register           | 0000 <sub>H</sub>               |

| T3IC                     | b | FF62 <sub>H</sub> |             | B1 <sub>H</sub> | GPT1 Timer 3 Interrupt Control Register | 0000 <sub>H</sub>               |

| Т4                       |   | FE44 <sub>H</sub> |             | 22 <sub>H</sub> | GPT1 Timer 4 Register                   | 0000 <sub>H</sub>               |

| T4CON                    | b | FF44 <sub>H</sub> |             | A2 <sub>H</sub> | GPT1 Timer 4 Control Register           | 0000 <sub>H</sub>               |

| T4IC                     | b | FF64 <sub>H</sub> |             | B2 <sub>H</sub> | GPT1 Timer 4 Interrupt Control Register | 0000 <sub>H</sub>               |

| T7                       |   | F050 <sub>H</sub> | Ε           | 28 <sub>H</sub> | CAPCOM Timer 7 Register                 | 0000 <sub>H</sub>               |

| T78CON                   | b | FF20 <sub>H</sub> |             | 90 <sub>H</sub> | CAPCOM Timer 7 and 8 Ctrl. Reg.         | 0000 <sub>H</sub>               |

| T7IC                     | b | F17A <sub>H</sub> | Ε           | BD <sub>H</sub> | CAPCOM Timer 7 Interrupt Ctrl. Reg.     | 0000 <sub>H</sub>               |

| T7REL                    |   | F054 <sub>H</sub> | Ε           | 2A <sub>H</sub> | CAPCOM Timer 7 Reload Register          | 0000 <sub>H</sub>               |

| Т8                       |   | F052 <sub>H</sub> | Ε           | 29 <sub>H</sub> | CAPCOM Timer 8 Register                 | 0000 <sub>H</sub>               |

| T8IC                     | b | F17C <sub>H</sub> | Ε           | BE <sub>H</sub> | CAPCOM Timer 8 Interrupt Ctrl. Reg.     | 0000 <sub>H</sub>               |

| T8REL                    |   | F056 <sub>H</sub> | Ε           | 2B <sub>H</sub> | CAPCOM Timer 8 Reload Register          | 0000 <sub>H</sub>               |

| TFR                      | b | FFAC <sub>H</sub> |             | D6 <sub>H</sub> | Trap Flag Register                      | 0000 <sub>H</sub>               |

| TRCON                    | b | FF34 <sub>H</sub> |             | 9A <sub>H</sub> | CAPCOM 6 Trap Enable Ctrl. Reg.         | 00XX <sub>H</sub>               |

| WDT                      |   | FEAE <sub>H</sub> |             | 57 <sub>H</sub> | Watchdog Timer Register (read only)     | 0000 <sub>H</sub>               |

| WDTCON                   |   | FFAE <sub>H</sub> |             | D7 <sub>H</sub> | Watchdog Timer Control Register         | <sup>2)</sup> 00xx <sub>H</sub> |

| XPOIC                    | b | F186 <sub>H</sub> | Ε           | C3 <sub>H</sub> | CAN1 Module Interrupt Control Register  | 0000 <sub>H</sub>               |

| XP1IC                    | b | F18E <sub>H</sub> | Ε           | C7 <sub>H</sub> | Unassigned Interrupt Control Reg.       | 0000 <sub>H</sub>               |

### **Absolute Maximum Ratings**

| Parameter                                                            | Symbol            | Limit | Values                | Unit | Notes      |

|----------------------------------------------------------------------|-------------------|-------|-----------------------|------|------------|

|                                                                      |                   | min.  | max.                  |      |            |

| Storage temperature                                                  | T <sub>ST</sub>   | -65   | 150                   | °C   | -          |

| Junction temperature                                                 | TJ                | -40   | 150                   | °C   | under bias |

| Voltage on $V_{\rm DD}$ pins with respect to ground ( $V_{\rm SS}$ ) | V <sub>DD</sub>   | -0.5  | 6.5                   | V    | -          |

| Voltage on any pin with respect to ground $(V_{SS})$                 | V <sub>IN</sub>   | -0.5  | V <sub>DD</sub> + 0.5 | V    | -          |

| Input current on any pin during overload condition                   | -                 | -10   | 10                    | mA   | -          |

| Absolute sum of all input<br>currents during overload<br>condition   | _                 | -     | 100                   | mA   | -          |

| Power dissipation                                                    | P <sub>DISS</sub> | _     | 1.5                   | W    | _          |

# Table 8 Absolute Maximum Rating Parameters

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. During absolute maximum rating overload conditions ( $V_{IN} > V_{DD}$  or  $V_{IN} < V_{SS}$ ) the voltage on  $V_{DD}$  pins with respect to ground ( $V_{SS}$ ) must not exceed the values defined by the absolute maximum ratings.

| Port Output Driver<br>Mode | Maximum Output Current $(I_{OLmax}, -I_{OHmax})^{1}$ | Nominal Output Current<br>( <i>I</i> <sub>OLnom</sub> , - <i>I</i> <sub>OHnom</sub> ) <sup>2)</sup> |  |  |

|----------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--|--|

| Strong driver              | 10 mA                                                | 2.5 mA                                                                                              |  |  |

| Medium driver              | 4.0 mA                                               | 1.0 mA                                                                                              |  |  |

| Weak driver                | 0.5 mA                                               | 0.1 mA                                                                                              |  |  |

#### Table 10 Current Limits for Port Output Drivers

<sup>1)</sup> An output current above II<sub>OXnom</sub>I may be drawn from up to three pins at the same time. For any group of 16 neighboring port output pins the total output current in each direction (ΣI<sub>OL</sub> and Σ-I<sub>OH</sub>) must remain below 50 mA.

<sup>2)</sup> The current ROM-version of the C164CI (step Ax) is equipped with port drivers, which provide reduced driving capability and reduced control. Please refer to the actual errata sheet for details.

## Power Consumption C164CI (ROM)

(Operating Conditions apply)

| Parameter                                                                                 | Sym-                           | Limit | Values                         | Unit | Test                                                                                      |

|-------------------------------------------------------------------------------------------|--------------------------------|-------|--------------------------------|------|-------------------------------------------------------------------------------------------|

|                                                                                           | bol                            | min.  | max.                           |      | Conditions                                                                                |

| Power supply current (active) with all peripherals active                                 | I <sub>DD</sub>                | _     | 1 +<br>2.5 × f <sub>CPU</sub>  | mA   | $\overline{\text{RSTIN}} = V_{\text{IL}}$ $f_{\text{CPU}} \text{ in } [\text{MHz}]^{1)}$  |

| Idle mode supply current<br>with all peripherals active                                   | I <sub>IDX</sub>               | _     | 1 +<br>1.1 × f <sub>CPU</sub>  | mA   | $\overline{\text{RSTIN}} = V_{\text{IH1}}$ $f_{\text{CPU}} \text{ in [MHz]}^{1)}$         |

| Idle mode supply current<br>with all peripherals deactivated,<br>PLL off, SDD factor = 32 | I <sub>IDO</sub> <sup>2)</sup> | _     | 500 +<br>50 × f <sub>OSC</sub> | μA   | $\overline{\text{RSTIN}} = V_{\text{IH1}}$ $f_{\text{OSC}} \text{ in } [\text{MHz}]^{1)}$ |

| Sleep and Power-down mode supply current with RTC running                                 | I <sub>PDR</sub> <sup>2)</sup> | -     | 200 +<br>25 × f <sub>OSC</sub> | μA   | $V_{\text{DD}} = V_{\text{DDmax}}$<br>$f_{\text{OSC}}$ in [MHz] <sup>3)</sup>             |

| Sleep and Power-down mode supply current with RTC disabled                                | I <sub>PDO</sub>               | _     | 50                             | μA   | $V_{\rm DD} = V_{\rm DDmax}^{3)}$                                                         |

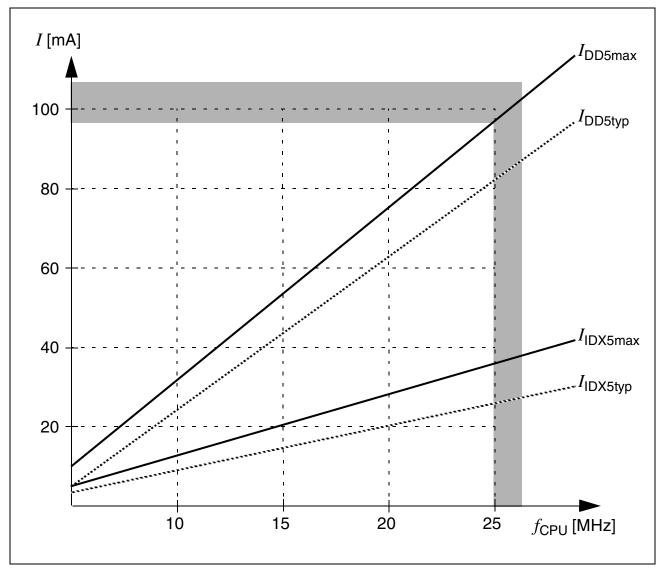

<sup>1)</sup> The supply current is a function of the operating frequency. This dependency is illustrated in Figure 9. These parameters are tested at V<sub>DDmax</sub> and maximum CPU clock with all outputs disconnected and all inputs at V<sub>IL</sub> or V<sub>IH</sub>.

<sup>2)</sup> This parameter is determined mainly by the current consumed by the oscillator (see Figure 8). This current, however, is influenced by the external oscillator circuitry (crystal, capacitors). The values given refer to a typical circuitry and may change in case of a not optimized external oscillator circuitry.

<sup>3)</sup> This parameter is tested including leakage currents. All inputs (including pins configured as inputs) at 0 V to 0.1 V or at  $V_{DD}$  - 0.1 V to  $V_{DD}$ ,  $V_{REF}$  = 0 V, all outputs (including pins configured as outputs) disconnected.

# Power Consumption C164CI (OTP)

(Operating Conditions apply)

| Parameter                                                                                 | Sym-                           | Lim       | it Values                      | Unit | Test                                                                                      |  |

|-------------------------------------------------------------------------------------------|--------------------------------|-----------|--------------------------------|------|-------------------------------------------------------------------------------------------|--|

|                                                                                           | bol                            | min. max. |                                |      | Conditions                                                                                |  |

| Power supply current (active) with all peripherals active                                 | I <sub>DD</sub>                | _         | 10 +<br>3.5 × f <sub>CPU</sub> | mA   | $\overline{\text{RSTIN}} = V_{\text{IL}}$ $f_{\text{CPU}} \text{ in } [\text{MHz}]^{1)}$  |  |

| Idle mode supply current<br>with all peripherals active                                   | I <sub>IDX</sub>               | -         | 5 +<br>1.25 × f <sub>CPU</sub> | mA   | $\overline{\text{RSTIN}} = V_{\text{IH1}}$ $f_{\text{CPU}} \text{ in } [\text{MHz}]^{1)}$ |  |

| Idle mode supply current<br>with all peripherals deactivated,<br>PLL off, SDD factor = 32 | I <sub>IDO</sub> <sup>2)</sup> | _         | 500 +<br>50 × f <sub>OSC</sub> | μA   | $\overline{\text{RSTIN}} = V_{\text{IH1}}$ $f_{\text{OSC}} \text{ in } [\text{MHz}]^{1)}$ |  |

| Sleep and Power-down mode supply current with RTC running                                 | $I_{\rm PDR}^{2)}$             | -         | 200 +<br>25 × f <sub>OSC</sub> | μA   | $V_{\text{DD}} = V_{\text{DDmax}}$<br>$f_{\text{OSC}}$ in [MHz] <sup>3)</sup>             |  |

| Sleep and Power-down mode supply current with RTC disabled                                | I <sub>PDO</sub>               | -         | 50                             | μA   | $V_{\rm DD} = V_{\rm DDmax}^{3)}$                                                         |  |

<sup>1)</sup> The supply current is a function of the operating frequency. This dependency is illustrated in Figure 10. These parameters are tested at V<sub>DDmax</sub> and maximum CPU clock with all outputs disconnected and all inputs at V<sub>IL</sub> or V<sub>IH</sub>.

<sup>2)</sup> This parameter is determined mainly by the current consumed by the oscillator (see **Figure 8**). This current, however, is influenced by the external oscillator circuitry (crystal, capacitors). The values given refer to a typical circuitry and may change in case of a not optimized external oscillator circuitry.

<sup>3)</sup> This parameter is tested including leakage currents. All inputs (including pins configured as inputs) at 0 V to 0.1 V or at  $V_{DD}$  - 0.1 V to  $V_{DD}$ ,  $V_{REF}$  = 0 V, all outputs (including pins configured as outputs) disconnected.

Figure 10 Supply/Idle Current as a Function of Operating Frequency for OTP Derivatives

# A/D Converter Characteristics

(Operating Conditions apply)

| Table 13 | A/D Converter Characteristics |

|----------|-------------------------------|

|----------|-------------------------------|

| Parameter                                       | Symbol            |     | Limit                 | Values                         | Unit | Test                                           |  |

|-------------------------------------------------|-------------------|-----|-----------------------|--------------------------------|------|------------------------------------------------|--|

|                                                 |                   |     | min.                  | max.                           |      | Conditions                                     |  |

| Analog reference supply                         | VAREF             | SR  | 4.0                   | V <sub>DD</sub> + 0.1          | V    | 1)                                             |  |

| Analog reference ground                         | VAGNE             | SR  | V <sub>SS</sub> - 0.1 | $V_{\rm SS}$ + 0.2             | V    | _                                              |  |

| Analog input voltage range                      | $V_{AIN}$         | SR  | V <sub>AGND</sub>     | V <sub>AREF</sub>              | V    | 2)                                             |  |

| Basic clock frequency                           | f <sub>BC</sub>   |     | 0.5                   | 6.25                           | MHz  | 3)                                             |  |

| Conversion time                                 | t <sub>C</sub>    | CC  | _                     | 40 t <sub>BC</sub> +           | _    | 4)                                             |  |

|                                                 |                   |     |                       | $t_{\rm S} + 2t_{\rm CPU}$     |      | $t_{CPU} = 1 / f_{CPU}$                        |  |

| Calibration time after reset                    | t <sub>CAL</sub>  | CC  | -                     | 3328 t <sub>BC</sub>           | -    | 5)                                             |  |

| Total unadjusted error                          | TUE               | CC  | -                     | ±2                             | LSB  | 1)                                             |  |

| Internal resistance of reference voltage source | R <sub>AREF</sub> | SR  | -                     | t <sub>BC</sub> / 60<br>- 0.25 | kΩ   | <i>t</i> <sub>BC</sub> in [ns] <sup>6)7)</sup> |  |

| Internal resistance of analog source            | R <sub>ASRC</sub> | ;SR | _                     | t <sub>S</sub> / 450<br>- 0.25 | kΩ   | t <sub>S</sub> in [ns] <sup>7)8)</sup>         |  |

| ADC input capacitance                           | $C_{AIN}$         | CC  | -                     | 33                             | pF   | 7)                                             |  |

<sup>1)</sup> TUE is tested at  $V_{AREF} = 5.0 \text{ V}$ ,  $V_{AGND} = 0 \text{ V}$ ,  $V_{DD} = 4.9 \text{ V}$ . It is guaranteed by design for all other voltages within the defined voltage range.

If the analog reference supply voltage exceeds the power supply voltage by up to 0.2 V

(i.e.  $V_{ABEF} = V_{DD} = +0.2 \text{ V}$ ) the maximum TUE is increased to ±3 LSB. This range is not 100% tested.

The specified TUE is guaranteed only if the absolute sum of input overload currents on Port 5 pins (see  $I_{OV}$  specification) does not exceed 10 mA.

During the reset calibration sequence the maximum TUE may be  $\pm$ 4 LSB.

- <sup>2)</sup> V<sub>AIN</sub> may exceed V<sub>AGND</sub> or V<sub>AREF</sub> up to the absolute maximum ratings. However, the conversion result in these cases will be X000<sub>H</sub> or X3FF<sub>H</sub>, respectively.

- <sup>3)</sup> The limit values for  $f_{BC}$  must not be exceeded when selecting the CPU frequency and the ADCTC setting.

- <sup>4)</sup> This parameter includes the sample time  $t_{\rm S}$ , the time for determining the digital result and the time to load the result register with the conversion result.

Values for the basic clock  $t_{BC}$  depend on programming and can be taken from Table 14.

This parameter depends on the ADC control logic. It is not a real maximum value, but rather a fixum.

- <sup>5)</sup> During the reset calibration conversions can be executed (with the current accuracy). The time required for these conversions is added to the total reset calibration time.

- <sup>6)</sup> During the conversion the ADC's capacitance must be repeatedly charged or discharged. The internal resistance of the reference voltage source must allow the capacitance to reach its respective voltage level within each conversion step. The maximum internal resistance results from the programmed conversion timing.

- <sup>7)</sup> Not 100% tested, guaranteed by design and characterization.

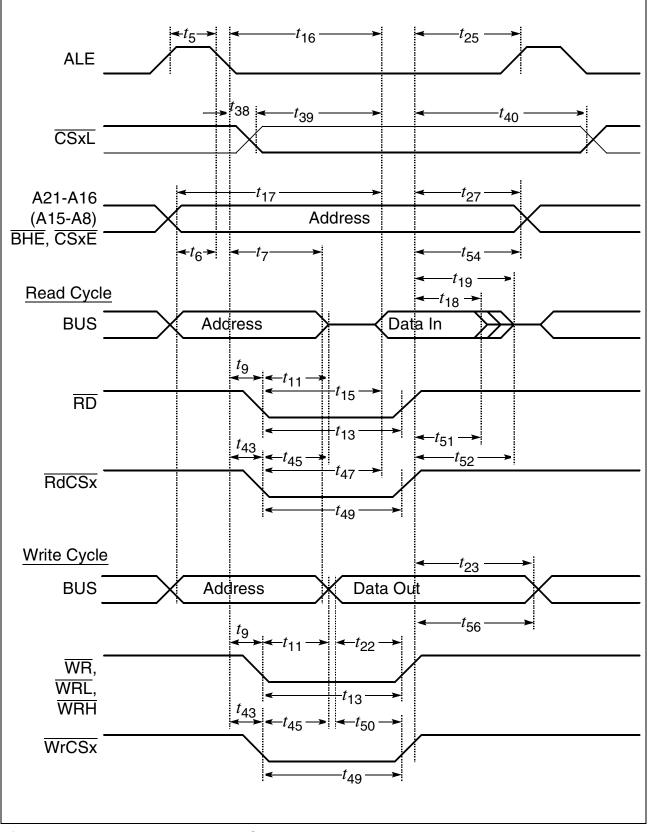

# Multiplexed Bus (cont'd)

(Operating Conditions apply)

ALE cycle time = 6 TCL +  $2t_A$  +  $t_C$  +  $t_F$  (120 ns at 25 MHz CPU clock without waitstates)

| Parameter                                                                              | Symbol                 |    | Max. CPU Clock<br>= 25 MHz |                                       | Variable (<br>1 / 2TCL =             | Unit                                                                              |    |

|----------------------------------------------------------------------------------------|------------------------|----|----------------------------|---------------------------------------|--------------------------------------|-----------------------------------------------------------------------------------|----|

|                                                                                        |                        |    | min.                       | max.                                  | min.                                 | max.                                                                              |    |

| RD, WR low time<br>(no RW-delay)                                                       | <i>t</i> <sub>13</sub> | CC | $50 + t_{\rm C}$           | -                                     | 3TCL - 10<br>+ <i>t</i> <sub>C</sub> | -                                                                                 | ns |

| RD to valid data in<br>(with RW-delay)                                                 | <i>t</i> <sub>14</sub> | SR | -                          | $20 + t_{\rm C}$                      | _                                    | 2TCL - 20<br>+ <i>t</i> <sub>C</sub>                                              | ns |

| RD to valid data in<br>(no RW-delay)                                                   | t <sub>15</sub>        | SR | -                          | $40 + t_{\rm C}$                      | _                                    | 3TCL - 20<br>+ <i>t</i> <sub>C</sub>                                              | ns |

| ALE low to valid data in                                                               | <i>t</i> <sub>16</sub> | SR | -                          | $40 + t_{A} + t_{C}$                  | _                                    | 3TCL - 20<br>+ <i>t</i> <sub>A</sub> + <i>t</i> <sub>C</sub>                      | ns |

| Address to valid data in                                                               | t <sub>17</sub>        | SR | _                          | $50 + 2t_A + t_C$                     | _                                    | $\begin{array}{c} 4\text{TCL} - 30 \\ + 2t_{\text{A}} + t_{\text{C}} \end{array}$ | ns |

| Data hold after RD rising edge                                                         | t <sub>18</sub>        | SR | 0                          | _                                     | 0                                    | _                                                                                 | ns |

| Data float after RD                                                                    | t <sub>19</sub>        | SR | -                          | 26 + $t_{\rm F}$                      | -                                    | 2TCL - 14<br>+ <i>t</i> <sub>F</sub>                                              | ns |

| Data valid to WR                                                                       | t <sub>22</sub>        | CC | $20 + t_{\rm C}$           | -                                     | 2TCL - 20<br>+ <i>t</i> <sub>C</sub> | _                                                                                 | ns |

| Data hold after WR                                                                     | t <sub>23</sub>        | CC | 26 + <i>t</i> <sub>F</sub> | -                                     | 2TCL - 14<br>+ <i>t</i> <sub>F</sub> | _                                                                                 | ns |

| ALE rising edge after $\overline{RD}$ , $\overline{WR}$                                | t <sub>25</sub>        | CC | 26 + <i>t</i> <sub>F</sub> | -                                     | 2TCL - 14<br>+ <i>t</i> <sub>F</sub> | _                                                                                 | ns |

| Address hold after $\overline{RD}$ , $\overline{WR}$                                   | t <sub>27</sub>        | CC | 26 + <i>t</i> <sub>F</sub> | -                                     | 2TCL - 14<br>+ <i>t</i> <sub>F</sub> | _                                                                                 | ns |

| ALE falling edge to $\overline{\text{CS}}^{1)}$                                        | t <sub>38</sub>        | CC | -4 - t <sub>A</sub>        | 10 - <i>t</i> <sub>A</sub>            | -4 - t <sub>A</sub>                  | 10 - <i>t</i> <sub>A</sub>                                                        | ns |

| $\overline{CS}$ low to Valid Data In <sup>1)</sup>                                     | t <sub>39</sub>        | SR | -                          | 40<br>+ $t_{\rm C}$<br>+ $2t_{\rm A}$ | -                                    | $3TCL - 20 + t_C + 2t_A$                                                          | ns |

| $\overline{\text{CS}}$ hold after $\overline{\text{RD}}$ , $\overline{\text{WR}}^{1)}$ | <i>t</i> <sub>40</sub> | CC | $46 + t_{F}$               | -                                     | 3TCL - 14<br>+ <i>t</i> <sub>F</sub> | -                                                                                 | ns |

| ALE fall. edge to RdCS,<br>WrCS (with RW delay)                                        | <i>t</i> <sub>42</sub> | CC | $16 + t_A$                 | -                                     | TCL - 4<br>+ <i>t</i> <sub>A</sub>   | -                                                                                 | ns |

Figure 18 External Memory Cycle: Multiplexed Bus, No Read/Write Delay, Normal ALE

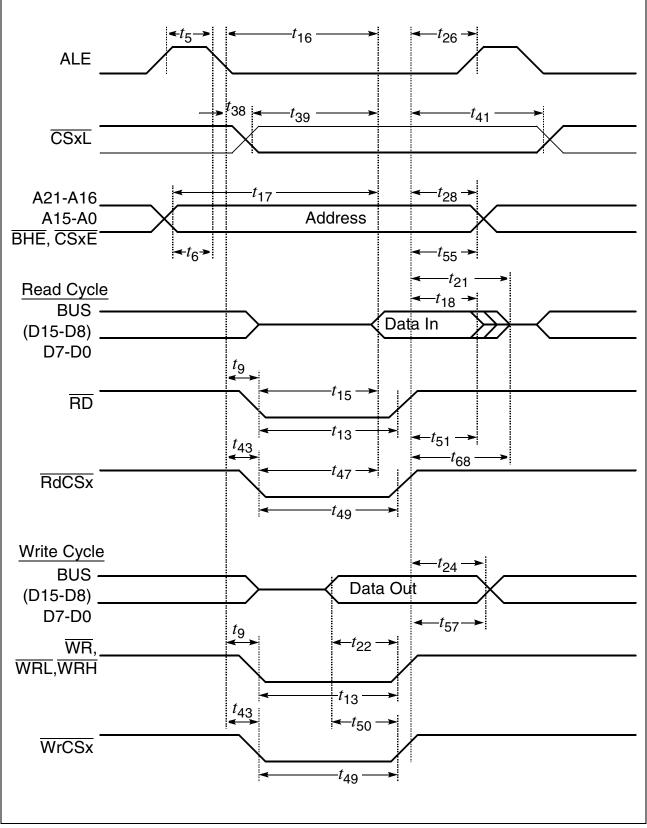

## **AC Characteristics**

#### **Demultiplexed Bus**

(Operating Conditions apply)

ALE cycle time = 4 TCL +  $2t_A$  +  $t_C$  +  $t_F$  (80 ns at 25 MHz CPU clock without waitstates)

| Parameter                                                                   |                        | nbol | Max. CPU Clock<br>= 25 MHz |                         | Variable<br>1 / 2TCL =               | Unit                                                                              |    |

|-----------------------------------------------------------------------------|------------------------|------|----------------------------|-------------------------|--------------------------------------|-----------------------------------------------------------------------------------|----|

|                                                                             |                        |      | min.                       | max.                    | min.                                 | max.                                                                              |    |

| ALE high time                                                               | <i>t</i> <sub>5</sub>  | CC   | $10 + t_{A}$               | -                       | TCL - 10<br>+ <i>t</i> <sub>A</sub>  | -                                                                                 | ns |

| Address setup to ALE                                                        | <i>t</i> <sub>6</sub>  | CC   | $4 + t_A$                  | -                       | TCL - 16<br>+ <i>t</i> <sub>A</sub>  | -                                                                                 | ns |

| ALE falling edge to RD,<br>WR (with RW-delay)                               | <i>t</i> 8             | CC   | $10 + t_{A}$               | -                       | TCL - 10<br>+ <i>t</i> <sub>A</sub>  | -                                                                                 | ns |

| ALE falling edge to RD,<br>WR (no RW-delay)                                 | t <sub>9</sub>         | CC   | $-10 + t_{A}$              | -                       | -10<br>+ <i>t</i> <sub>A</sub>       | -                                                                                 | ns |

| RD, WR low time<br>(with RW-delay)                                          | <i>t</i> <sub>12</sub> | CC   | $30 + t_{\rm C}$           | -                       | 2TCL - 10<br>+ <i>t</i> <sub>C</sub> | -                                                                                 | ns |

| RD, WR low time<br>(no RW-delay)                                            | t <sub>13</sub>        | CC   | $50 + t_{\rm C}$           | -                       | 3TCL - 10<br>+ <i>t</i> <sub>C</sub> | -                                                                                 | ns |

| RD to valid data in (with RW-delay)                                         | <i>t</i> <sub>14</sub> | SR   | _                          | $20 + t_{\rm C}$        | _                                    | 2TCL - 20<br>+ <i>t</i> <sub>C</sub>                                              | ns |

| RD to valid data in (no RW-delay)                                           | t <sub>15</sub>        | SR   | _                          | $40 + t_{\rm C}$        | _                                    | 3TCL - 20<br>+ <i>t</i> <sub>C</sub>                                              | ns |

| ALE low to valid data in                                                    | <i>t</i> <sub>16</sub> | SR   | _                          | $40 + t_A + t_C$        | -                                    | 3TCL - 20<br>+ <i>t</i> <sub>A</sub> + <i>t</i> <sub>C</sub>                      | ns |

| Address to valid data in                                                    | <i>t</i> <sub>17</sub> | SR   | -                          | $50 + 2t_A + t_C$       | _                                    | $\begin{array}{c} 4\text{TCL} - 30 \\ + 2t_{\text{A}} + t_{\text{C}} \end{array}$ | ns |

| Data hold after RD rising edge                                              | <i>t</i> <sub>18</sub> | SR   | 0                          | -                       | 0                                    | -                                                                                 | ns |

| Data float after $\overline{RD}$ rising edge (with RW-delay <sup>1)</sup> ) | t <sub>20</sub>        | SR   | -                          | $26 + 2t_A + t_F^{(1)}$ | _                                    | 2TCL - 14<br>+ $22t_A$<br>+ $t_F^{(1)}$                                           | ns |

| Data float after RD rising edge (no RW-delay <sup>1)</sup> )                | <i>t</i> <sub>21</sub> | SR   | _                          | $10 + 2t_A + t_F^{(1)}$ | -                                    | TCL - 10<br>+ $22t_A$<br>+ $t_F^{(1)}$                                            | ns |

Figure 22 External Memory Cycle: Demultiplexed Bus, No Read/Write Delay, Normal ALE