Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | C166                                                                         |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 20MHz                                                                        |

| Connectivity               | CANbus, EBI/EMI, SPI, SSC, UART/USART                                        |

| Peripherals                | POR, PWM, WDT                                                                |

| Number of I/O              | 59                                                                           |

| Program Memory Size        | 64KB (64K x 8)                                                               |

| Program Memory Type        | ОТР                                                                          |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 4K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 4.75V ~ 5.5V                                                                 |

| Data Converters            | A/D 8x10b                                                                    |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 80-QFP                                                                       |

| Supplier Device Package    | PG-MQFP-80-7                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/c164ci8emdbfxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Supported by a Large Range of Development Tools like C-Compilers, Macro-Assembler Packages, Emulators, Evaluation Boards, HLL-Debuggers, Simulators, Logic Analyzer Disassemblers, Programming Boards

- On-Chip Bootstrap Loader

- 80-Pin MQFP Package, 0.65 mm pitch

This document describes several derivatives of the C164 group. **Table 1** enumerates these derivatives and summarizes the differences. As this document refers to all of these derivatives, some descriptions may not apply to a specific product.

| Derivative <sup>1)</sup>                 | Program<br>Memory | CAPCOM6       | CAN Interf. | Operating<br>Frequency |

|------------------------------------------|-------------------|---------------|-------------|------------------------|

| SAK-C164CI-8R[25]M<br>SAF-C164CI-8R[25]M | 64 KByte ROM      | Full function | CAN1        | 20 MHz,<br>[25 MHz]    |

| SAK-C164SI-8R[25]M<br>SAF-C164SI-8R[25]M | 64 KByte ROM      | Full function |             | 20 MHz,<br>[25 MHz]    |

| SAK-C164CL-8R[25]M<br>SAF-C164CL-8R[25]M | 64 KByte ROM      | Reduced fct.  | CAN1        | 20 MHz,<br>[25 MHz]    |

| SAK-C164SL-8R[25]M<br>SAF-C164SL-8R[25]M | 64 KByte ROM      | Reduced fct.  |             | 20 MHz,<br>[25 MHz]    |

| SAK-C164CL-6R[25]M<br>SAF-C164CL-6R[25]M | 48 KByte ROM      | Reduced fct.  | CAN1        | 20 MHz,<br>[25 MHz]    |

| SAK-C164SL-6R[25]M<br>SAF-C164SL-6R[25]M | 48 KByte ROM      | Reduced fct.  |             | 20 MHz,<br>[25 MHz]    |

| SAK-C164CI-L[25]M<br>SAF-C164CI-L[25]M   |                   | Full function | CAN1        | 20 MHz,<br>[25 MHz]    |

| SAK-C164CI-8EM<br>SAF-C164CI-8EM         | 64 KByte OTP      | Full function | CAN1        | 20 MHz                 |

#### Table 1 C164CI Derivative Synopsis

<sup>1)</sup> This Data Sheet is valid for ROM(less) devices starting with and including design step AB, and for OTP devices starting with and including design step DA.

For simplicity all versions are referred to by the term C164CI throughout this document.

| Table 2 | Pin Definitions and Functions (cont'd) |       |                                                                                                                               |  |  |  |  |  |

|---------|----------------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Symbol  | Pin                                    | Input | Function                                                                                                                      |  |  |  |  |  |

|         | No.                                    | Outp. |                                                                                                                               |  |  |  |  |  |

| PORT1   |                                        | 10    | PORT1 consists of the two 8-bit bidirectional I/O ports P1L                                                                   |  |  |  |  |  |

| P1L.0-7 | 47-52,<br>57-59                        |       | and P1H. It is bit-wise programmable for input or output via direction bits. For a pin configured as input, the output driver |  |  |  |  |  |

| P1H.0-7 |                                        |       | is put into high-impedance state. PORT1 is used as the<br>16-bit address bus (A) in demultiplexed bus modes and also          |  |  |  |  |  |

|         |                                        |       | after switching from a demultiplexed bus mode to a                                                                            |  |  |  |  |  |

|         |                                        |       | multiplexed bus mode.                                                                                                         |  |  |  |  |  |

|         |                                        |       | The following PORT1 pins also serve for alt. functions:                                                                       |  |  |  |  |  |

| P1L.0   | 47                                     | I/O   | CC60 CAPCOM6: Input / Output of Channel 0                                                                                     |  |  |  |  |  |

| P1L.1   | 48                                     | 0     | COUT60 CAPCOM6: Output of Channel 0                                                                                           |  |  |  |  |  |

| P1L.2   | 49                                     | I/O   | CC61 CAPCOM6: Input / Output of Channel 1                                                                                     |  |  |  |  |  |

| P1L.3   | 50                                     | 0     | COUT61 CAPCOM6: Output of Channel 1                                                                                           |  |  |  |  |  |

| P1L.4   | 51                                     | I/O   | CC62 CAPCOM6: Input / Output of Channel 2                                                                                     |  |  |  |  |  |

| P1L.5   | 52                                     | 0     | COUT62 CAPCOM6: Output of Channel 2                                                                                           |  |  |  |  |  |

| P1L.6   | 57                                     | 0     | COUT63 Output of 10-bit Compare Channel                                                                                       |  |  |  |  |  |

| P1L.7   | 58                                     | 1     | CTRAP CAPCOM6: Trap Input                                                                                                     |  |  |  |  |  |

|         |                                        |       | CTRAP is an input pin with an internal pullup resistor. A low                                                                 |  |  |  |  |  |

|         |                                        |       | level on this pin switches the compare outputs of the                                                                         |  |  |  |  |  |

|         |                                        |       | CAPCOM6 unit to the logic level defined by software.                                                                          |  |  |  |  |  |

| P1H.0   | 59                                     | 1     | CC6POS0 CAPCOM6: Position 0 Input, **)                                                                                        |  |  |  |  |  |

|         |                                        | 1     | EX0IN Fast External Interrupt 0 Input                                                                                         |  |  |  |  |  |

| P1H.1   | 62                                     | 1     | CC6POS1 CAPCOM6: Position 1 Input, **)                                                                                        |  |  |  |  |  |

|         |                                        | 1     | EX1IN Fast External Interrupt 1 Input                                                                                         |  |  |  |  |  |

| P1H.2   | 63                                     | 1     | CC6POS2 CAPCOM6: Position 2 Input, **)                                                                                        |  |  |  |  |  |

|         |                                        | 1     | EX2IN Fast External Interrupt 2 Input                                                                                         |  |  |  |  |  |

| P1H.3   | 64                                     | 1     | EX3IN Fast External Interrupt 3 Input,                                                                                        |  |  |  |  |  |

|         |                                        |       | T7IN CAPCOM2: Timer T7 Count Input                                                                                            |  |  |  |  |  |

| P1H.4   | 65                                     | I/O   | CC24IO CAPCOM2: CC24 Capture Inp./Compare Outp.                                                                               |  |  |  |  |  |

| P1H.5   | 66                                     | I/O   | CC25IO CAPCOM2: CC25 Capture Inp./Compare Outp.                                                                               |  |  |  |  |  |

| P1H.6   | 67                                     | I/O   | CC26IO CAPCOM2: CC26 Capture Inp./Compare Outp.                                                                               |  |  |  |  |  |

| P1H.7   | 68                                     | I/O   | CC27IO CAPCOM2: CC27 Capture Inp./Compare Outp.                                                                               |  |  |  |  |  |

|         |                                        |       | Note: The marked (**) input signals are available only in devices with a full function CAPCOM6.                               |  |  |  |  |  |

| Table 2           | Piı                     | n Definit      | ions and Functions (cont'd)                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|-------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol            | Pin<br>No.              | Input<br>Outp. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P8                |                         | 10             | Port 8 is a 4-bit bidirectional I/O port. It is bit-wise<br>programmable for input or output via direction bits. For a pin<br>configured as input, the output driver is put into high-<br>impedance state. Port 8 outputs can be configured as push/<br>pull or open drain drivers. The input threshold of Port 8 is<br>selectable (TTL or special). Port 8 pins provide inputs/<br>outputs for CAPCOM2 and serial interface lines. <sup>1)</sup> |

| P8.0              | 72                      | I/O<br>I       | CC16IO CAPCOM2: CC16 Capture Inp./Compare Outp.,<br>CAN1_RxD CAN 1 Receive Data Input                                                                                                                                                                                                                                                                                                                                                             |

| P8.1              | 73                      | I/O<br>O       | CC17IO CAPCOM2: CC17 Capture Inp./Compare Outp.,<br>CAN1_TxD CAN 1 Transmit Data Output                                                                                                                                                                                                                                                                                                                                                           |

| P8.2              | 74                      | I/O<br>I       | CC18IO CAPCOM2: CC18 Capture Inp./Compare Outp.,<br>CAN1_RxD CAN 1 Receive Data Input                                                                                                                                                                                                                                                                                                                                                             |

| P8.3              | 75                      | I/O<br>O       | CC19IO CAPCOM2: CC19 Capture Inp./Compare Outp.,<br>CAN1_TxD CAN 1 Transmit Data Output                                                                                                                                                                                                                                                                                                                                                           |

| V <sub>AREF</sub> | 1                       | -              | Reference voltage for the A/D converter.                                                                                                                                                                                                                                                                                                                                                                                                          |

| V <sub>AGND</sub> | 80                      | -              | Reference ground for the A/D converter.                                                                                                                                                                                                                                                                                                                                                                                                           |

| V <sub>DD</sub>   | 7, 21,<br>40, 53,<br>61 | -              | Digital Supply Voltage:<br>+5 V during normal operation and idle mode.<br>≥2.5 V during power down mode.                                                                                                                                                                                                                                                                                                                                          |

| V <sub>SS</sub>   | 6, 20,<br>41, 56,<br>60 | _              | Digital Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

<sup>1)</sup> The CAN interface lines are assigned to ports P4 and P8 under software control. Within the CAN module several assignments can be selected.

Note: The following behavioural differences must be observed when the bidirectional reset is active:

- Bit BDRSTEN in register SYSCON cannot be changed after EINIT and is cleared automatically after a reset.

- The reset indication flags always indicate a long hardware reset.

- The PORT0 configuration is treated as if it were a hardware reset. In particular, the bootstrap loader may be activated when P0L.4 is low.

- Pin RSTIN may only be connected to external reset devices with an open drain output driver.

- A short hardware reset is extended to the duration of the internal reset sequence.

## Real Time Clock

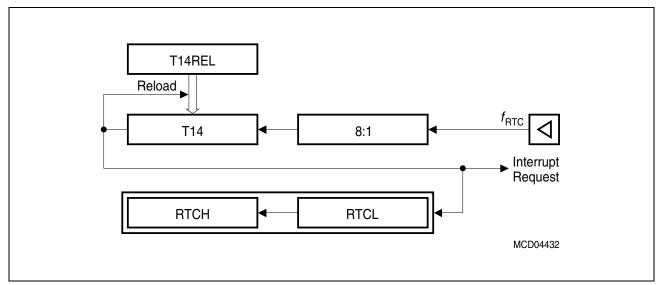

The Real Time Clock (RTC) module of the C164Cl consists of a chain of 3 divider blocks, a fixed 8:1 divider, the reloadable 16-bit timer T14, and the 32-bit RTC timer (accessible via registers RTCH and RTCL). The RTC module is directly clocked with the on-chip oscillator frequency divided by 32 via a separate clock driver ( $f_{\rm RTC} = f_{\rm OSC}/32$ ) and is therefore independent from the selected clock generation mode of the C164Cl. All timers count up.

The RTC module can be used for different purposes:

- System clock to determine the current time and date

- Cyclic time based interrupt

- 48-bit timer for long term measurements

### Figure 7 RTC Block Diagram

Note: The registers associated with the RTC are not affected by a reset in order to maintain the correct system time even when intermediate resets are executed.

## **Parallel Ports**

The C164CI provides up to 59 I/O lines which are organized into five input/output ports and one input port. All port lines are bit-addressable, and all input/output lines are individually (bit-wise) programmable as inputs or outputs via direction registers. The I/O ports are true bidirectional ports which are switched to high impedance state when configured as inputs. The output drivers of three I/O ports can be configured (pin by pin) for push/pull operation or open-drain operation via control registers. During the internal reset, all port pins are configured as inputs.

The input threshold of Port 3, Port 4, and Port 8 is selectable (TTL or CMOS like), where the special CMOS like input threshold reduces noise sensitivity due to the input hysteresis. The input threshold may be selected individually for each byte of the respective ports.

All port lines have programmable alternate input or output functions associated with them. All port lines that are not used for these alternate functions may be used as general purpose IO lines.

PORT0 and PORT1 may be used as address and data lines when accessing external memory, while Port 4 outputs the additional segment address bits A21/19/17 ... A16 and the optional chip select signals in systems where segmentation is enabled to access more than 64 KBytes of memory.

Ports P1L, P1H, and P8 are associated with the capture inputs or compare outputs of the CAPCOM units and/or serve as external interrupt inputs.

Port 3 includes alternate functions of timers, serial interfaces, the optional bus control signal BHE/WRH, and the system clock output CLKOUT (or the programmable frequency output FOUT).

Port 5 is used for the analog input channels to the A/D converter or timer control signals.

The edge characteristics (transition time) and driver characteristics (output current) of the C164CI's port drivers can be selected via the Port Output Control registers (POCONx).

#### **Instruction Set Summary**

Table 6 lists the instructions of the C164CI in a condensed way.

The various addressing modes that can be used with a specific instruction, the operation of the instructions, parameters for conditional execution of instructions, and the opcodes for each instruction can be found in the "C166 Family Instruction Set Manual".

This document also provides a detailled description of each instruction.

| Mnemonic           | Description                                                                                          | Bytes |  |  |  |  |

|--------------------|------------------------------------------------------------------------------------------------------|-------|--|--|--|--|

| ADD(B)             | Add word (byte) operands                                                                             | 2/4   |  |  |  |  |

| ADDC(B)            | Add word (byte) operands with Carry                                                                  | 2/4   |  |  |  |  |

| SUB(B)             | Subtract word (byte) operands                                                                        | 2/4   |  |  |  |  |

| SUBC(B)            | Subtract word (byte) operands with Carry                                                             | 2/4   |  |  |  |  |

| MUL(U)             | (Un)Signed multiply direct GPR by direct GPR (16-16-bit)                                             | 2     |  |  |  |  |

| DIV(U)             | (Un)Signed divide register MDL by direct GPR (16-/16-bit)                                            |       |  |  |  |  |

| DIVL(U)            | (Un)Signed long divide reg. MD by direct GPR (32-/16-bit)                                            | 2     |  |  |  |  |

| CPL(B)             | Complement direct word (byte) GPR                                                                    | 2     |  |  |  |  |

| NEG(B)             | Negate direct word (byte) GPR                                                                        | 2     |  |  |  |  |

| AND(B)             | Bitwise AND, (word/byte operands)                                                                    | 2/4   |  |  |  |  |

| OR(B)              | Bitwise OR, (word/byte operands)                                                                     | 2/4   |  |  |  |  |

| XOR(B)             | Bitwise XOR, (word/byte operands)                                                                    | 2/4   |  |  |  |  |

| BCLR               | Clear direct bit                                                                                     | 2     |  |  |  |  |

| BSET               | Set direct bit                                                                                       | 2     |  |  |  |  |

| BMOV(N)            | Move (negated) direct bit to direct bit                                                              | 4     |  |  |  |  |

| BAND, BOR,<br>BXOR | AND/OR/XOR direct bit with direct bit                                                                | 4     |  |  |  |  |

| BCMP               | Compare direct bit to direct bit                                                                     | 4     |  |  |  |  |

| BFLDH/L            | Bitwise modify masked high/low byte of bit-addressable direct word memory with immediate data        | 4     |  |  |  |  |

| CMP(B)             | Compare word (byte) operands                                                                         | 2/4   |  |  |  |  |

| CMPD1/2            | Compare word data to GPR and decrement GPR by 1/2                                                    | 2/4   |  |  |  |  |

| CMPI1/2            | Compare word data to GPR and increment GPR by 1/2                                                    | 2/4   |  |  |  |  |

| PRIOR              | Determine number of shift cycles to normalize direct<br>word GPR and store result in direct word GPR | 2     |  |  |  |  |

| SHL / SHR          | Shift left/right direct word GPR                                                                     | 2     |  |  |  |  |

| ROL / ROR          | Rotate left/right direct word GPR                                                                    | 2     |  |  |  |  |

| ASHR               | Arithmetic (sign bit) shift right direct word GPR                                                    | 2     |  |  |  |  |

#### Table 6 Instruction Set Summary

| Table 6 In             | struction Set Summary (cont'd)                                                      |       |

|------------------------|-------------------------------------------------------------------------------------|-------|

| Mnemonic               | Description                                                                         | Bytes |

| MOV(B)                 | Move word (byte) data                                                               | 2/4   |

| MOVBS                  | Move byte operand to word operand with sign extension                               | 2/4   |

| MOVBZ                  | Move byte operand to word operand with zero extension                               | 2/4   |

| JMPA, JMPI,<br>JMPR    | Jump absolute/indirect/relative if condition is met                                 | 4     |

| JMPS                   | Jump absolute to a code segment                                                     | 4     |

| J(N)B                  | Jump relative if direct bit is (not) set                                            | 4     |

| JBC                    | Jump relative and clear bit if direct bit is set                                    | 4     |

| JNBS                   | Jump relative and set bit if direct bit is not set                                  | 4     |

| CALLA, CALLI,<br>CALLR | Call absolute/indirect/relative subroutine if condition is met                      | 4     |

| CALLS                  | Call absolute subroutine in any code segment                                        | 4     |

| PCALL                  | Push direct word register onto system stack and call absolute subroutine            | 4     |

| TRAP                   | Call interrupt service routine via immediate trap number                            | 2     |

| PUSH, POP              | Push/pop direct word register onto/from system stack                                | 2     |

| SCXT                   | Push direct word register onto system stack und update register with word operand   | 4     |

| RET                    | Return from intra-segment subroutine                                                | 2     |

| RETS                   | Return from inter-segment subroutine                                                | 2     |

| RETP                   | Return from intra-segment subroutine and pop direct word register from system stack | 2     |

| RETI                   | Return from interrupt service subroutine                                            | 2     |

| SRST                   | Software Reset                                                                      | 4     |

| IDLE                   | Enter Idle Mode                                                                     | 4     |

| PWRDN                  | Enter Power Down Mode (supposes MMI-pin being low)                                  | 4     |

| SRVWDT                 | Service Watchdog Timer                                                              | 4     |

| DISWDT                 | Disable Watchdog Timer                                                              | 4     |

| EINIT                  | Signify End-of-Initialization on RSTOUT-pin                                         | 4     |

| ATOMIC                 | Begin ATOMIC sequence                                                               | 2     |

| EXTR                   | Begin EXTended Register sequence                                                    | 2     |

| EXTP(R)                | Begin EXTended Page (and Register) sequence                                         | 2/4   |

| EXTS(R)                | Begin EXTended Segment (and Register) sequence                                      | 2/4   |

| NOP                    | Null operation                                                                      | 2     |

#### **Special Function Registers Overview**

**Table 7** lists all SFRs which are implemented in the C164CI in alphabetical order. **Bit-addressable** SFRs are marked with the letter "**b**" in column "Name". SFRs within the **Extended SFR-Space** (ESFRs) are marked with the letter "**E**" in column "Physical Address". Registers within on-chip X-peripherals are marked with the letter "**X**" in column "Physical Address".

An SFR can be specified via its individual mnemonic name. Depending on the selected addressing mode, an SFR can be accessed via its physical address (using the Data Page Pointers), or via its short 8-bit address (without using the Data Page Pointers).

| Name Physic<br>Addres |   |                   |   | 8-Bit<br>Addr.                                 | Description                                                   | Reset<br>Value    |

|-----------------------|---|-------------------|---|------------------------------------------------|---------------------------------------------------------------|-------------------|

| ADCIC                 | b | FF98 <sub>H</sub> |   | CCH                                            | A/D Converter End of Conversion<br>Interrupt Control Register | 0000 <sub>H</sub> |

| ADCON                 | b | FFA0 <sub>H</sub> |   | D0 <sub>H</sub> A/D Converter Control Register |                                                               |                   |

| ADDAT                 |   | FEA0 <sub>H</sub> |   | 50 <sub>H</sub>                                | A/D Converter Result Register                                 | 0000 <sub>H</sub> |

| ADDAT2                |   | F0A0 <sub>H</sub> | Ε | 50 <sub>H</sub>                                | A/D Converter 2 Result Register                               | 0000 <sub>H</sub> |

| ADDRSEL1              |   | FE18 <sub>H</sub> |   | 0C <sub>H</sub>                                | Address Select Register 1                                     | 0000 <sub>H</sub> |

| ADDRSEL2              |   | FE1A <sub>H</sub> |   | 0D <sub>H</sub>                                | Address Select Register 2                                     | 0000 <sub>H</sub> |

| ADDRSEL3              |   | FE1C <sub>H</sub> |   | 0E <sub>H</sub>                                | Address Select Register 3                                     | 0000 <sub>H</sub> |

| ADDRSEL4              | • | FE1E <sub>H</sub> |   | 0F <sub>H</sub>                                | Address Select Register 4                                     | 0000 <sub>H</sub> |

| ADEIC                 | b | FF9A <sub>H</sub> |   | CD <sub>H</sub>                                | A/D Converter Overrun Error Interrupt<br>Control Register     | 0000 <sub>H</sub> |

| BUSCON0               | b | FF0C <sub>H</sub> |   | 86 <sub>H</sub>                                | Bus Configuration Register 0                                  | 0000 <sub>H</sub> |

| BUSCON1               | b | FF14 <sub>H</sub> |   | 8A <sub>H</sub>                                | Bus Configuration Register 1                                  | 0000 <sub>H</sub> |

| BUSCON2               | b | FF16 <sub>H</sub> |   | 8B <sub>H</sub>                                | Bus Configuration Register 2                                  | 0000 <sub>H</sub> |

| BUSCON3               | b | FF18 <sub>H</sub> |   | 8C <sub>H</sub>                                | Bus Configuration Register 3                                  | 0000 <sub>H</sub> |

| BUSCON4               | b | FF1A <sub>H</sub> |   | 8D <sub>H</sub>                                | Bus Configuration Register 4                                  | 0000 <sub>H</sub> |

| C1BTR                 |   | EF04 <sub>H</sub> | Χ |                                                | CAN1 Bit Timing Register                                      | UUUU <sub>H</sub> |

| C1CSR                 |   | EF00 <sub>H</sub> | Χ |                                                | CAN1 Control / Status Register                                | XX01 <sub>H</sub> |

| C1GMS                 |   | EF06 <sub>H</sub> | Χ |                                                | CAN1 Global Mask Short                                        | UFUU <sub>H</sub> |

| C1LARn                |   | EFn4 <sub>H</sub> | Χ |                                                | CAN Lower Arbitration Register (msg. n)                       | UUUU <sub>H</sub> |

| C1LGML                |   | EF0A <sub>H</sub> | Χ |                                                | CAN Lower Global Mask Long                                    | UUUU <sub>H</sub> |

| C1LMLM                |   | EF0E <sub>H</sub> | Χ |                                                | CAN Lower Mask of Last Message                                | UUUU <sub>H</sub> |

#### Table 7 C164Cl Registers, Ordered by Name

# Table 7C164Cl Registers, Ordered by Name (cont'd)

| Name    |   | Physica<br>Address |   | 8-Bit<br>Addr.  | Description                                                    | Reset<br>Value                  |

|---------|---|--------------------|---|-----------------|----------------------------------------------------------------|---------------------------------|

| RTCH    |   | F0D6 <sub>H</sub>  | Ε | 6B <sub>H</sub> | RTC High Register                                              | no                              |

| RTCL    |   | F0D4 <sub>H</sub>  | Ε | 6A <sub>H</sub> | RTC Low Register                                               | no                              |

| S0BG    |   | FEB4 <sub>H</sub>  |   | 5A <sub>H</sub> | Serial Channel 0 Baud Rate Generator<br>Reload Register        | 0000 <sub>H</sub>               |

| SOCON   | b | FFB0 <sub>H</sub>  |   | D8 <sub>H</sub> | Serial Channel 0 Control Register                              | 0000 <sub>H</sub>               |

| SOEIC   | b | FF70 <sub>H</sub>  |   | B8 <sub>H</sub> | Serial Channel 0 Error Interrupt Ctrl.<br>Reg.                 | 0000 <sub>H</sub>               |

| SORBUF  |   | FEB2 <sub>H</sub>  |   | 59 <sub>H</sub> | Serial Channel 0 Receive Buffer Reg.<br>(read only)            | XXXX <sub>H</sub>               |

| SORIC   | b | FF6E <sub>H</sub>  |   | B7 <sub>H</sub> | Serial Channel 0 Receive Interrupt<br>Control Register         | 0000 <sub>H</sub>               |

| SOTBIC  | b | F19C <sub>H</sub>  | Ε | CEH             | Serial Channel 0 Transmit Buffer<br>Interrupt Control Register | 0000 <sub>H</sub>               |

| SOTBUF  |   | FEB0 <sub>H</sub>  |   | 58 <sub>H</sub> | Serial Channel 0 Transmit Buffer Reg.<br>(write only)          | 0000 <sub>H</sub>               |

| SOTIC   | b | FF6C <sub>H</sub>  |   | B6 <sub>H</sub> | Serial Channel 0 Transmit Interrupt<br>Control Register        | 0000 <sub>H</sub>               |

| SP      |   | FE12 <sub>H</sub>  |   | 09 <sub>H</sub> | CPU System Stack Pointer Register                              | FC00 <sub>H</sub>               |

| SSCBR   |   | F0B4 <sub>H</sub>  | Ε | 5A <sub>H</sub> | SSC Baudrate Register                                          | 0000 <sub>H</sub>               |

| SSCCON  | b | FFB2 <sub>H</sub>  |   | D9 <sub>H</sub> | SSC Control Register                                           | 0000 <sub>H</sub>               |

| SSCEIC  | b | FF76 <sub>H</sub>  |   | BB <sub>H</sub> | SSC Error Interrupt Control Register                           | 0000 <sub>H</sub>               |

| SSCRB   |   | F0B2 <sub>H</sub>  | Ε | 59 <sub>H</sub> | SSC Receive Buffer                                             | XXXX <sub>H</sub>               |

| SSCRIC  | b | FF74 <sub>H</sub>  |   | BA <sub>H</sub> | SSC Receive Interrupt Control Register                         | 0000 <sub>H</sub>               |

| SSCTB   |   | F0B0 <sub>H</sub>  | Ε | 58 <sub>H</sub> | SSC Transmit Buffer                                            | 0000 <sub>H</sub>               |

| SSCTIC  | b | FF72 <sub>H</sub>  |   | B9 <sub>H</sub> | SSC Transmit Interrupt Control Register                        | 0000 <sub>H</sub>               |

| STKOV   |   | FE14 <sub>H</sub>  |   | 0A <sub>H</sub> | CPU Stack Overflow Pointer Register                            | FA00 <sub>H</sub>               |

| STKUN   |   | FE16 <sub>H</sub>  |   | 0B <sub>H</sub> | CPU Stack Underflow Pointer Register                           | FC00 <sub>H</sub>               |

| SYSCON  | b | FF12 <sub>H</sub>  |   | 89 <sub>H</sub> | CPU System Configuration Register                              | <sup>1)</sup> 0xx0 <sub>H</sub> |

| SYSCON1 | b | F1DC <sub>H</sub>  | Ε | EEH             | CPU System Configuration Register 1                            | 0000 <sub>H</sub>               |

| SYSCON2 | b | F1D0 <sub>H</sub>  | Ε | E8 <sub>H</sub> | CPU System Configuration Register 2                            | 0000 <sub>H</sub>               |

| SYSCON3 | b | F1D4 <sub>H</sub>  | Ε | EA <sub>H</sub> | CPU System Configuration Register 3                            | 0000 <sub>H</sub>               |

## **Absolute Maximum Ratings**

| Parameter                                                            | Symbol            | Limit | Values                | Unit | Notes      |  |

|----------------------------------------------------------------------|-------------------|-------|-----------------------|------|------------|--|

|                                                                      |                   | min.  | max.                  |      |            |  |

| Storage temperature                                                  | T <sub>ST</sub>   | -65   | 150                   | °C   | _          |  |

| Junction temperature                                                 | TJ                | -40   | 150                   | °C   | under bias |  |

| Voltage on $V_{\rm DD}$ pins with respect to ground ( $V_{\rm SS}$ ) | V <sub>DD</sub>   | -0.5  | 6.5                   | V    | -          |  |

| Voltage on any pin with respect to ground $(V_{SS})$                 | V <sub>IN</sub>   | -0.5  | V <sub>DD</sub> + 0.5 | V    | -          |  |

| Input current on any pin during overload condition                   | -                 | -10   | 10                    | mA   | -          |  |

| Absolute sum of all input<br>currents during overload<br>condition   | _                 | -     | 100                   | mA   | -          |  |

| Power dissipation                                                    | P <sub>DISS</sub> | _     | 1.5                   | W    | _          |  |

# Table 8 Absolute Maximum Rating Parameters

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. During absolute maximum rating overload conditions ( $V_{IN} > V_{DD}$  or  $V_{IN} < V_{SS}$ ) the voltage on  $V_{DD}$  pins with respect to ground ( $V_{SS}$ ) must not exceed the values defined by the absolute maximum ratings.

### Parameter Interpretation

The parameters listed in the following partly represent the characteristics of the C164Cl and partly its demands on the system. To aid in interpreting the parameters right, when evaluating them for a design, they are marked in column "Symbol":

CC (Controller Characteristics):

The logic of the C164CI will provide signals with the respective characteristics.

#### SR (System Requirement):

The external system must provide signals with the respective characteristics to the C164CI.

#### **DC Characteristics**

(Operating Conditions apply)<sup>1)</sup>

| Parameter                                            | Sym              | bol | Limit                        | Values                       | Unit | Test Conditions                |

|------------------------------------------------------|------------------|-----|------------------------------|------------------------------|------|--------------------------------|

|                                                      |                  |     | min.                         | max.                         |      |                                |

| Input low voltage (TTL,<br>all except XTAL1)         | V <sub>IL</sub>  | SR  | -0.5                         | 0.2 V <sub>DD</sub><br>- 0.1 | V    | -                              |

| Input low voltage XTAL1                              | $V_{IL2}$        | SR  | -0.5                         | 0.3 V <sub>DD</sub>          | V    | -                              |

| Input low voltage<br>(Special Threshold)             | V <sub>ILS</sub> | SR  | -0.5                         | 2.0                          | V    | -                              |

| Input high voltage (TTL,<br>all except RSTIN, XTAL1) | V <sub>IH</sub>  | SR  | 0.2 V <sub>DD</sub><br>+ 0.9 | V <sub>DD</sub> + 0.5        | V    | -                              |

| Input high voltage RSTIN<br>(when operated as input) | V <sub>IH1</sub> | SR  | 0.6 V <sub>DD</sub>          | V <sub>DD</sub> + 0.5        | V    | -                              |

| Input high voltage XTAL1                             | V <sub>IH2</sub> | SR  | 0.7 V <sub>DD</sub>          | V <sub>DD</sub> + 0.5        | V    | -                              |

| Input high voltage<br>(Special Threshold)            | V <sub>IHS</sub> | SR  | 0.8 V <sub>DD</sub><br>- 0.2 | V <sub>DD</sub> + 0.5        | V    | -                              |

| Input Hysteresis<br>(Special Threshold)              | HYS              |     | 400                          | _                            | mV   | Series resistance = $0 \Omega$ |

| Output low voltage <sup>2)</sup>                     | V <sub>OL</sub>  | CC  | _                            | 1.0                          | V    | $I_{OL} \le I_{OLmax}^{3)}$    |

|                                                      |                  |     | _                            | 0.45                         | V    | $I_{OL} \le I_{OLnom}^{3)4)}$  |

| Output high voltage <sup>5)</sup>                    | V <sub>OH</sub>  | CC  | V <sub>DD</sub> -<br>1.0     | _                            | V    | $I_{OH} \ge I_{OHmax}^{3)}$    |

|                                                      |                  |     | V <sub>DD</sub> -<br>0.45    | _                            | V    | $I_{OH} \ge I_{OHnom}^{3)4)$   |

| Input leakage current (Port 5)                       | I <sub>OZ1</sub> | CC  | _                            | ±200                         | nA   | $0 V < V_{IN} < V_{DD}$        |

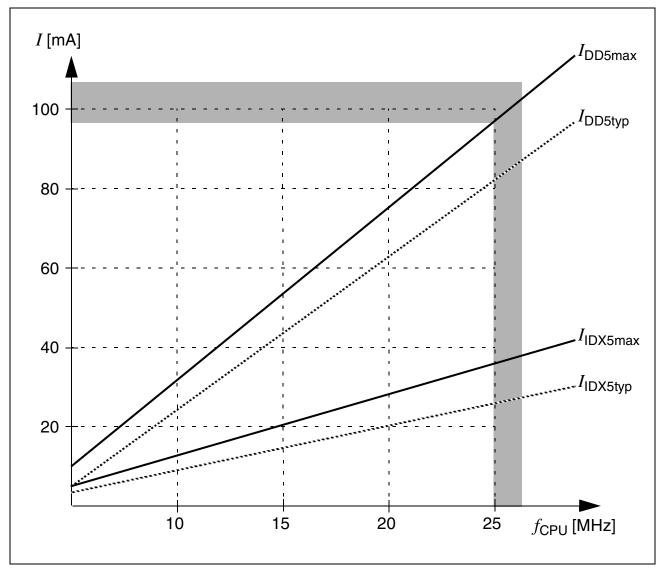

Figure 10 Supply/Idle Current as a Function of Operating Frequency for OTP Derivatives

### AC Characteristics Definition of Internal Timing

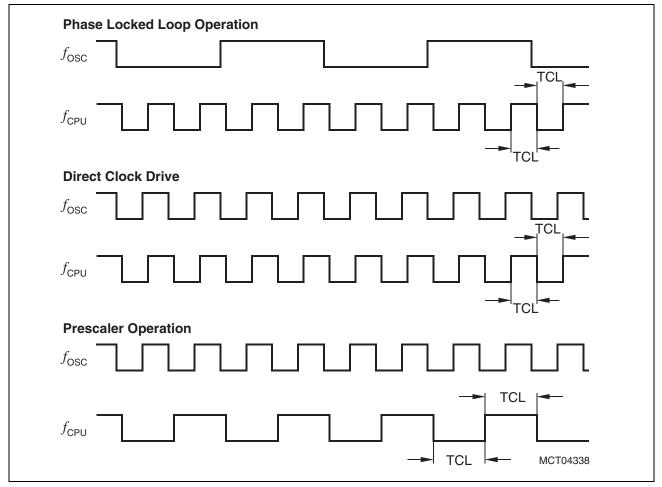

The internal operation of the C164CI is controlled by the internal CPU clock  $f_{CPU}$ . Both edges of the CPU clock can trigger internal (e.g. pipeline) or external (e.g. bus cycles) operations.

The specification of the external timing (AC Characteristics) therefore depends on the time between two consecutive edges of the CPU clock, called "TCL" (see Figure 11).

Figure 11 Generation Mechanisms for the CPU Clock

The CPU clock signal  $f_{CPU}$  can be generated from the oscillator clock signal  $f_{OSC}$  via different mechanisms. The duration of TCLs and their variation (and also the derived external timing) depends on the used mechanism to generate  $f_{CPU}$ . This influence must be regarded when calculating the timings for the C164CI.

Note: The example for PLL operation shown in Figure 11 refers to a PLL factor of 4.

The used mechanism to generate the basic CPU clock is selected by bitfield CLKCFG in register RP0H.7-5.

Upon a long hardware reset register RP0H is loaded with the logic levels present on the upper half of PORT0 (P0H), i.e. bitfield CLKCFG represents the logic levels on pins

P0.15-13 (P0H.7-5). Register RP0H can be loaded from the upper half of register RSTCON under software control.

**Table 11** associates the combinations of these three bits with the respective clock generation mode.

| CLKCFG <sup>1)</sup><br>(RP0H.7-5) | CPU Frequency $f_{CPU} = f_{OSC} \times F$ | External Clock<br>Input Range <sup>2)</sup> | Notes                      |

|------------------------------------|--------------------------------------------|---------------------------------------------|----------------------------|

| 1 1 1                              | $f_{OSC} \times 4$                         | 2.5 to 6.25 MHz                             | Default configuration      |

| 1 1 0                              | $f_{OSC} \times 3$                         | 3.33 to 8.33 MHz                            | -                          |

| 1 0 1                              | $f_{OSC} \times 2$                         | 5 to 12.5 MHz                               | -                          |

| 1 0 0                              | $f_{OSC} \times 5$                         | 2 to 5 MHz                                  | -                          |

| 0 1 1                              | $f_{\rm OSC} \times 1$                     | 1 to 25 MHz                                 | Direct drive <sup>3)</sup> |

| 0 1 0                              | $f_{\rm OSC} 	imes$ 1.5                    | 6.66 to 16.66 MHz                           | -                          |

| 0 0 1                              | f <sub>OSC</sub> / 2                       | 2 to 50 MHz                                 | CPU clock via prescaler    |

| 0 0 0                              | $f_{\rm OSC} \times 2.5$                   | 4 to 10 MHz                                 | -                          |

Table 11

C164Cl Clock Generation Modes

<sup>1)</sup> Please note that pin P0.15 (corresponding to RP0H.7) is inverted in emulation mode, and thus also in EHM.

<sup>2)</sup> The external clock input range refers to a CPU clock range of 10 ... 25 MHz.

<sup>3)</sup> The maximum frequency depends on the duty cycle of the external clock signal.

### Prescaler Operation

When prescaler operation is configured (CLKCFG =  $001_B$ ) the CPU clock is derived from the internal oscillator (input clock signal) by a 2:1 prescaler.

The frequency of  $f_{CPU}$  is half the frequency of  $f_{OSC}$  and the high and low time of  $f_{CPU}$  (i.e. the duration of an individual TCL) is defined by the period of the input clock  $f_{OSC}$ .

The timings listed in the AC Characteristics that refer to TCLs therefore can be calculated using the period of  $f_{OSC}$  for any TCL.

### Phase Locked Loop

When PLL operation is configured (via CLKCFG) the on-chip phase locked loop is enabled and provides the CPU clock (see **Table 11**). The PLL multiplies the input frequency by the factor **F** which is selected via the combination of pins P0.15-13 (i.e.  $f_{CPU} = f_{OSC} \times F$ ). With every **F**'th transition of  $f_{OSC}$  the PLL circuit synchronizes the CPU clock to the input clock. This synchronization is done smoothly, i.e. the CPU clock frequency does not change abruptly.

Due to this adaptation to the input clock the frequency of  $f_{CPU}$  is constantly adjusted so it is locked to  $f_{OSC}$ . The slight variation causes a jitter of  $f_{CPU}$  which also effects the duration of individual TCLs.

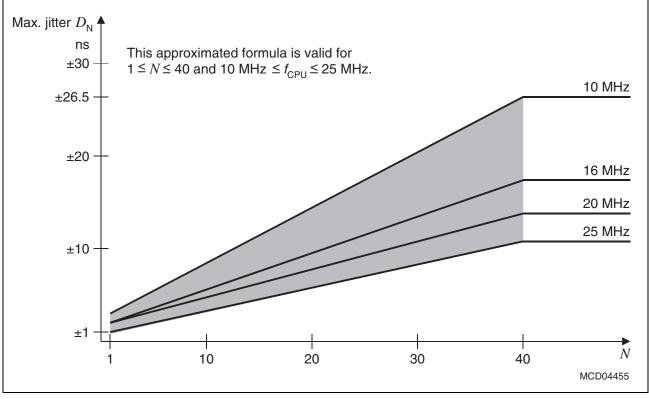

The timings listed in the AC Characteristics that refer to TCLs therefore must be calculated using the minimum TCL that is possible under the respective circumstances. The actual minimum value for TCL depends on the jitter of the PLL. As the PLL is constantly adjusting its output frequency so it corresponds to the applied input frequency (crystal or oscillator) the relative deviation for periods of more than one TCL is lower than for one single TCL (see formula and Figure 12).

For a period of  $N \times \text{TCL}$  the minimum value is computed using the corresponding deviation  $D_N$ :

$$(N \times \text{TCL})_{\text{min}} = N \times \text{TCL}_{\text{NOM}} - D_N; D_N [\text{ns}] = \pm (13.3 + N \times 6.3) / f_{\text{CPU}} [\text{MHz}],$$

where N = number of consecutive TCLs and 1  $\leq N \leq$  40.

So for a period of 3 TCLs @ 25 MHz (i.e. N = 3): D<sub>3</sub> = (13.3 + 3 × 6.3)/25 = 1.288 ns, and (3TCL)<sub>min</sub> = 3TCL<sub>NOM</sub> - 1.288 ns = 58.7 ns (@  $f_{CPU}$  = 25 MHz).

This is especially important for bus cycles using waitstates and e.g. for the operation of timers, serial interfaces, etc. For all slower operations and longer periods (e.g. pulse train generation or measurement, lower baudrates, etc.) the deviation caused by the PLL jitter is neglectible.

Note: For all periods longer than 40 TCL the N = 40 value can be used (see Figure 12).

Figure 12 Approximated Maximum Accumulated PLL Jitter

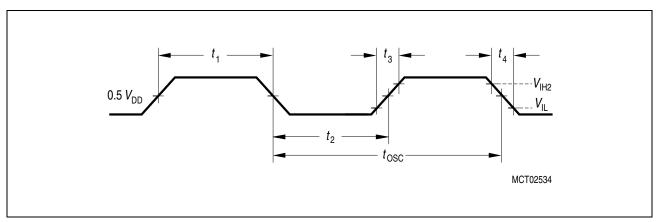

# AC Characteristics External Clock Drive XTAL1

(Operating Conditions apply)

| Parameter Symbol        |                       | Direct Drive<br>1:1 |                  | Prescaler<br>2:1 |      | PLL<br>1:N |                  | Unit              |    |

|-------------------------|-----------------------|---------------------|------------------|------------------|------|------------|------------------|-------------------|----|

|                         |                       |                     | min.             | max.             | min. | max.       | min.             | max.              |    |

| Oscillator period       | t <sub>OSC</sub>      | SR                  | 40               | _                | 20   | _          | 60 <sup>1)</sup> | 500 <sup>1)</sup> | ns |

| High time <sup>2)</sup> | <i>t</i> <sub>1</sub> | SR                  | 20 <sup>3)</sup> | _                | 6    | _          | 10               | _                 | ns |

| Low time <sup>2)</sup>  | <i>t</i> <sub>2</sub> | SR                  | 20 <sup>3)</sup> | _                | 6    | _          | 10               | -                 | ns |

| Rise time <sup>2)</sup> | t <sub>3</sub>        | SR                  | _                | 8                | _    | 5          | -                | 10                | ns |

| Fall time <sup>2)</sup> | <i>t</i> <sub>4</sub> | SR                  | -                | 8                | -    | 5          | -                | 10                | ns |

## Table 12 External Clock Drive Characteristics

The minimum and maximum oscillator periods for PLL operation depend on the selected CPU clock generation mode. Please see respective table above.

<sup>2)</sup> The clock input signal must reach the defined levels  $V_{\text{IL2}}$  and  $V_{\text{IH2}}$ .

<sup>3)</sup> The minimum high and low time refers to a duty cycle of 50%. The maximum operating freqency ( $f_{CPU}$ ) in direct drive mode depends on the duty cycle of the clock input signal.

### Figure 13 External Clock Drive XTAL1

Note: If the on-chip oscillator is used together with a crystal, the oscillator frequency is limited to a range of 4 MHz to 16 MHz.

It is strongly recommended to measure the oscillation allowance (or margin) in the final target system (layout) to determine the optimum parameters for the oscillator operation. Please refer to the limits specified by the crystal supplier.

When driven by an external clock signal it will accept the specified frequency range. Operation at lower input frequencies is possible but is guaranteed by design only (not 100% tested).

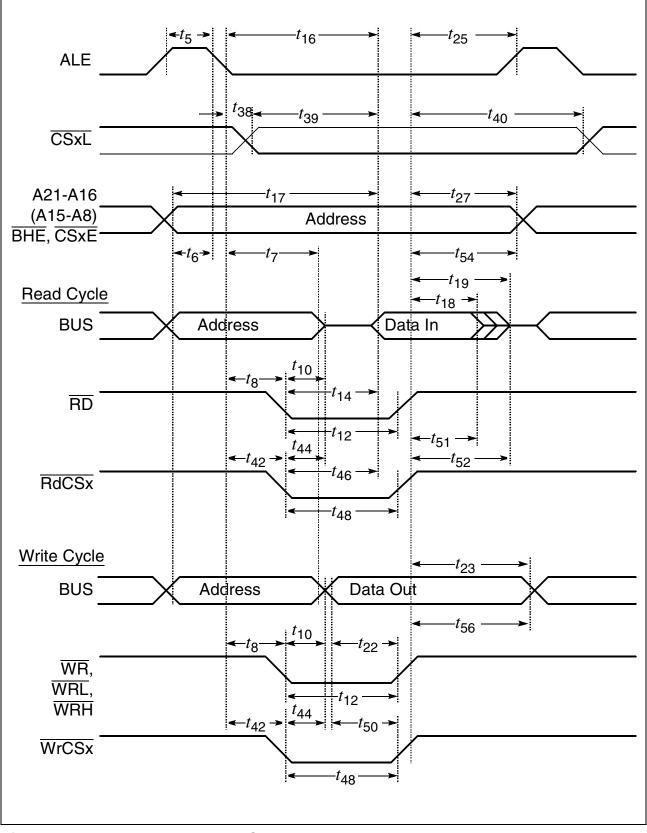

Figure 16 External Memory Cycle: Multiplexed Bus, With Read/Write Delay, Normal ALE

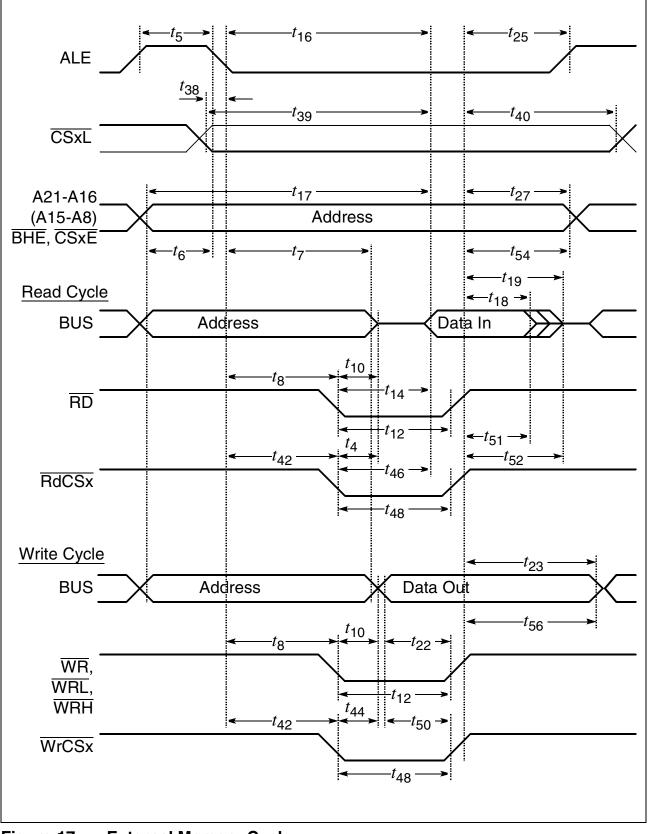

Figure 17 External Memory Cycle: Multiplexed Bus, With Read/Write Delay, Extended ALE

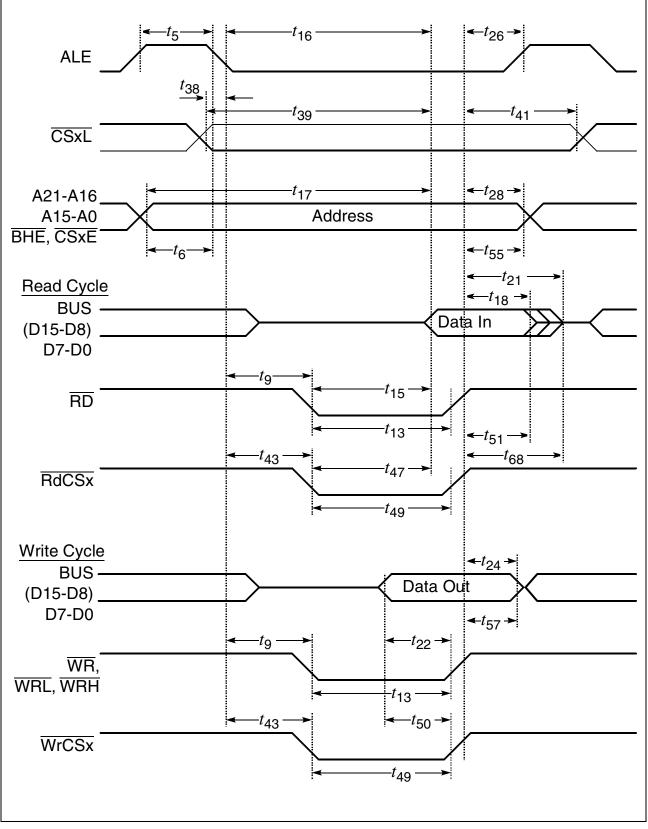

#### Figure 23 External Memory Cycle: Demultiplexed Bus, No Read/Write Delay, Extended ALE

# Infineon goes for Business Excellence

"Business excellence means intelligent approaches and clearly defined processes, which are both constantly under review and ultimately lead to good operating results.

Better operating results and business excellence mean less idleness and wastefulness for all of us, more professional success, more accurate information, a better overview and, thereby, less frustration and more satisfaction."

Dr. Ulrich Schumacher

http://www.infineon.com