#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | C166                                                                        |

| Core Size                  | 16-Bit                                                                      |

| Speed                      | 20MHz                                                                       |

| Connectivity               | CANbus, EBI/EMI, SPI, SSC, UART/USART                                       |

| Peripherals                | POR, PWM, WDT                                                               |

| Number of I/O              | 59                                                                          |

| Program Memory Size        | -                                                                           |

| Program Memory Type        | ROMIess                                                                     |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 4K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 4.75V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 80-QFP                                                                      |

| Supplier Device Package    | PG-MQFP-80-7                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/sab-c164ci-lm-ca |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# C164CI/SI C164CL/SL

16-Bit Single-Chip Microcontroller

# Microcontrollers

Never stop thinking.

#### C164CI

| <b>Revision History:</b>                   |                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                             | V2.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| ersion:                                    | 1999-08<br>1998-02<br>04.97                                                                                                                                | (Preliminary)<br>(Advance Information)                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| Subjects                                   | (major change                                                                                                                                              | es since last revision) <sup>1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| Converted                                  | l to Infineon lay                                                                                                                                          | rout                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| Operating                                  | frequency up t                                                                                                                                             | o 25 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| References to Flash removed                |                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| Timer Unit with three timers               |                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| On-chip X                                  | RAM described                                                                                                                                              | ł                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| Derivative                                 | table updated                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| Supply voltage is 5 V                      |                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| Functionality of reduced CAPCOM6 corrected |                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| Timer description improved                 |                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| Sections "                                 | Oscillator Watc                                                                                                                                            | hdog" and "Power Management" added                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| POCON reset values adjusted                |                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| Parameter                                  | r section reworl                                                                                                                                           | ked                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|                                            | ersion:<br>Subjects<br>Converted<br>Operating<br>Reference<br>Timer Unit<br>On-chip X<br>Derivative<br>Supply vol<br>Functional<br>Timer des<br>Sections " | Tersion:       1999-08         1998-02       04.97         Subjects (major change         Converted to Infineon lay         Operating frequency up t         References to Flash rem         Timer Unit with three time         On-chip XRAM described         Derivative table updated         Supply voltage is 5 V         Functionality of reduced of         Timer description improv         Sections "Oscillator Wate         POCON reset values adj | Yersion:       1999-08<br>1998-02<br>04.97       (Preliminary)<br>(Advance Information)         Subjects (major changes since last revision) <sup>1)</sup> Converted to Infineon layout         Operating frequency up to 25 MHz         References to Flash removed         Timer Unit with three timers         On-chip XRAM described         Derivative table updated         Supply voltage is 5 V         Functionality of reduced CAPCOM6 corrected         Timer description improved         Sections "Oscillator Watchdog" and "Power Management" added |  |  |

These changes refer to the last two versions. Version 1998-02 covers OTP and ROM derivatives, while version 1999-08 ist the most recent one.

#### Controller Area Network (CAN): License of Robert Bosch GmbH

#### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

#### mcdocu.comments@infineon.com

## 16-Bit Single-Chip Microcontroller C166 Family

C164CI

# C164CI/SI, C164CL/SL

- High Performance 16-bit CPU with 4-Stage Pipeline

- 80 ns Instruction Cycle Time at 25 MHz CPU Clock

- 400 ns Multiplication (16  $\times$

- Supported by a Large Range of Development Tools like C-Compilers, Macro-Assembler Packages, Emulators, Evaluation Boards, HLL-Debuggers, Simulators, Logic Analyzer Disassemblers, Programming Boards

- On-Chip Bootstrap Loader

- 80-Pin MQFP Package, 0.65 mm pitch

This document describes several derivatives of the C164 group. **Table 1** enumerates these derivatives and summarizes the differences. As this document refers to all of these derivatives, some descriptions may not apply to a specific product.

| Derivative <sup>1)</sup>                 | Program<br>Memory | CAPCOM6       | CAN Interf. | Operating<br>Frequency |

|------------------------------------------|-------------------|---------------|-------------|------------------------|

| SAK-C164CI-8R[25]M<br>SAF-C164CI-8R[25]M | 64 KByte ROM      | Full function | CAN1        | 20 MHz,<br>[25 MHz]    |

| SAK-C164SI-8R[25]M<br>SAF-C164SI-8R[25]M | 64 KByte ROM      | Full function |             | 20 MHz,<br>[25 MHz]    |

| SAK-C164CL-8R[25]M<br>SAF-C164CL-8R[25]M | 64 KByte ROM      | Reduced fct.  | CAN1        | 20 MHz,<br>[25 MHz]    |

| SAK-C164SL-8R[25]M<br>SAF-C164SL-8R[25]M | 64 KByte ROM      | Reduced fct.  |             | 20 MHz,<br>[25 MHz]    |

| SAK-C164CL-6R[25]M<br>SAF-C164CL-6R[25]M | 48 KByte ROM      | Reduced fct.  | CAN1        | 20 MHz,<br>[25 MHz]    |

| SAK-C164SL-6R[25]M<br>SAF-C164SL-6R[25]M | 48 KByte ROM      | Reduced fct.  |             | 20 MHz,<br>[25 MHz]    |

| SAK-C164CI-L[25]M<br>SAF-C164CI-L[25]M   |                   | Full function | CAN1        | 20 MHz,<br>[25 MHz]    |

| SAK-C164CI-8EM<br>SAF-C164CI-8EM         | 64 KByte OTP      | Full function | CAN1        | 20 MHz                 |

#### Table 1 C164CI Derivative Synopsis

<sup>1)</sup> This Data Sheet is valid for ROM(less) devices starting with and including design step AB, and for OTP devices starting with and including design step DA.

For simplicity all versions are referred to by the term C164CI throughout this document.

| Table 2 | -   |       |            | anotions      |                                                                               |

|---------|-----|-------|------------|---------------|-------------------------------------------------------------------------------|

| Symbol  |     | Input | Function   |               |                                                                               |

|         | No. | Outp. |            |               |                                                                               |

| P5      |     | 1     |            |               | it-only port with Schmitt-Trigger charact.                                    |

|         |     |       |            |               | so serve as analog input channels for the                                     |

|         |     |       |            | erter, or the | ey serve as timer inputs:                                                     |

| P5.0    | 76  |       | AN0        |               |                                                                               |

| P5.1    | 77  |       | AN1        |               |                                                                               |

| P5.2    | 78  |       | AN2        |               |                                                                               |

| P5.3    | 79  |       | AN3        |               |                                                                               |

| P5.4    | 2   |       | AN4,       | T2EUD         | GPT1 Timer T2 Ext. Up/Down Ctrl. Inp.                                         |

| P5.5    | 3   |       | AN5,       | T4EUD         | GPT1 Timer T4 Ext. Up/Down Ctrl. Inp.                                         |

| P5.6    | 4   | 1     | AN6,       | T2IN          | GPT1 Timer T2 Input for                                                       |

|         |     |       |            |               | Count/Gate/Reload/Capture                                                     |

| P5.7    | 5   | I     | AN7,       | T4IN          | GPT1 Timer T4 Input for                                                       |

|         |     |       |            |               | Count/Gate/Reload/Capture                                                     |

| P3      |     | IO    |            |               | ectional I/O port. It is bit-wise put or output via direction bits. For a pin |

|         |     |       |            |               | the output driver is put into high-                                           |

|         |     |       | -          | -             | ort 3 outputs can be configured as push/                                      |

|         |     |       |            |               | ivers. The input threshold of Port 3 is                                       |

|         |     |       | selectable |               | -                                                                             |

|         |     |       | The follow | ing Port 3    | pins also serve for alternate functions:                                      |

| P3.4    | 8   | 1     | T3EUD      | GPT1 T        | mer T3 External Up/Down Control Input                                         |

| P3.6    | 9   | 1     | T3IN       | GPT1 T        | imer T3 Count/Gate Input                                                      |

| P3.8    | 10  | I/O   | MRST       | SSC Ma        | ster-Receive/Slave-Transmit Inp./Outp.                                        |

| P3.9    | 11  | I/O   | MTSR       | SSC Ma        | ster-Transmit/Slave-Receive Outp./Inp.                                        |

| P3.10   | 12  | 0     | TxD0       | ASC0 C        | lock/Data Output (Async./Sync.)                                               |

| P3.11   | 13  | I/O   | RxD0       |               | ata Input (Async.) or Inp./Outp. (Sync.)                                      |

| P3.12   | 14  | 0     | BHE        | External      | Memory High Byte Enable Signal,                                               |

|         |     | 0     | WRH        |               | Memory High Byte Write Strobe                                                 |

| P3.13   | 15  | I/O   | SCLK       |               | ster Clock Output / Slave Clock Input.                                        |

| P3.15   | 16  | 0     | CLKOUT     | -             | Clock Output (= CPU Clock),                                                   |

|         |     | 0     | FOUT       | Program       | mable Frequency Output                                                        |

#### Table 2Pin Definitions and Functions

| Table 2                            | Pin Definitions and Functions (cont'd) |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                              |                     |  |  |  |  |

|------------------------------------|----------------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|---------------------|--|--|--|--|

| Symbol                             | Pin<br>No.                             | Input<br>Outp. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                              |                     |  |  |  |  |

| ĒĀ/V <sub>PP</sub>                 | 28                                     | I              | External Access Enable pin.<br><b>A low level</b> at this pin during and after Reset forces the<br>C164CI to latch the configuration from PORT0 and pin RD,<br>and to begin instruction execution out of external memory.<br><b>A high level</b> forces the C164CI to latch the configuration<br>from pins RD and ALE, and to begin instruction execution out<br>of the internal program memory.<br>"ROMless" versions must have this pin tied to '0'. |                                                                              |                     |  |  |  |  |

|                                    |                                        |                | -                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Note: This pin also accepts the programming voltage for the OTP derivatives. |                     |  |  |  |  |

| <b>PORT0</b><br>P0L.0-7<br>P0H.0-7 | 36                                     | IO             | PORT0 consists of the two 8-bit bidirectional I/O ports P0L<br>and P0H. It is bit-wise programmable for input or output via<br>direction bits. For a pin configured as input, the output driver<br>is put into high-impedance state.                                                                                                                                                                                                                   |                                                                              |                     |  |  |  |  |

|                                    | 42-46                                  |                | In case of an external bus configuration, PORT0 serves as<br>the address (A) and address/data (AD) bus in multiplexed<br>bus modes and as the data (D) bus in demultiplexed bus<br>modes.                                                                                                                                                                                                                                                              |                                                                              |                     |  |  |  |  |

|                                    |                                        |                | Demultiplexed bus                                                                                                                                                                                                                                                                                                                                                                                                                                      | modes:                                                                       |                     |  |  |  |  |

|                                    |                                        |                | Data Path Width:                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8-bit                                                                        | 16-bit              |  |  |  |  |

|                                    |                                        |                | P0L.0 – P0L.7:                                                                                                                                                                                                                                                                                                                                                                                                                                         | D0 – D7                                                                      | D0 – D7             |  |  |  |  |

|                                    |                                        |                | P0H.0 – P0H.7: I/O D8 – D15                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                              |                     |  |  |  |  |

|                                    |                                        |                | Multiplexed bus modes:                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                              |                     |  |  |  |  |

|                                    |                                        |                | Data Path Width:<br>P0L.0 – P0L.7:                                                                                                                                                                                                                                                                                                                                                                                                                     | 8-bit<br>AD0 – AD7                                                           | 16-bit<br>AD0 – AD7 |  |  |  |  |

|                                    |                                        |                | P0H.0 – P0H.7:                                                                                                                                                                                                                                                                                                                                                                                                                                         | AB0 – AD7<br>A8 – A15                                                        | AD8 – AD15          |  |  |  |  |

| lable 2 | Table 2Pin Definitions and Functions (cont'd) |       |                                                                                                                               |  |  |  |  |

|---------|-----------------------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Symbol  | Pin                                           | Input | Function                                                                                                                      |  |  |  |  |

|         | No.                                           | Outp. |                                                                                                                               |  |  |  |  |

| PORT1   |                                               | 10    | PORT1 consists of the two 8-bit bidirectional I/O ports P1L                                                                   |  |  |  |  |

| P1L.0-7 | 47-52,<br>57-59                               |       | and P1H. It is bit-wise programmable for input or output via direction bits. For a pin configured as input, the output driver |  |  |  |  |

| P1H.0-7 |                                               |       | is put into high-impedance state. PORT1 is used as the<br>16-bit address bus (A) in demultiplexed bus modes and also          |  |  |  |  |

|         |                                               |       | after switching from a demultiplexed bus mode to a                                                                            |  |  |  |  |

|         |                                               |       | multiplexed bus mode.                                                                                                         |  |  |  |  |

|         |                                               |       | The following PORT1 pins also serve for alt. functions:                                                                       |  |  |  |  |

| P1L.0   | 47                                            | I/O   | CC60 CAPCOM6: Input / Output of Channel 0                                                                                     |  |  |  |  |

| P1L.1   | 48                                            | 0     | COUT60 CAPCOM6: Output of Channel 0                                                                                           |  |  |  |  |

| P1L.2   | 49                                            | I/O   | CC61 CAPCOM6: Input / Output of Channel 1                                                                                     |  |  |  |  |

| P1L.3   | 50                                            | 0     | COUT61 CAPCOM6: Output of Channel 1                                                                                           |  |  |  |  |

| P1L.4   | 51                                            | I/O   | CC62 CAPCOM6: Input / Output of Channel 2                                                                                     |  |  |  |  |

| P1L.5   | 52                                            | 0     | COUT62 CAPCOM6: Output of Channel 2                                                                                           |  |  |  |  |

| P1L.6   | 57                                            | 0     | COUT63 Output of 10-bit Compare Channel                                                                                       |  |  |  |  |

| P1L.7   | 58                                            | 1     | CTRAP CAPCOM6: Trap Input                                                                                                     |  |  |  |  |

|         |                                               |       | CTRAP is an input pin with an internal pullup resistor. A low                                                                 |  |  |  |  |

|         |                                               |       | level on this pin switches the compare outputs of the                                                                         |  |  |  |  |

|         |                                               |       | CAPCOM6 unit to the logic level defined by software.                                                                          |  |  |  |  |

| P1H.0   | 59                                            | 1     | CC6POS0 CAPCOM6: Position 0 Input, **)                                                                                        |  |  |  |  |

|         |                                               | 1     | EX0IN Fast External Interrupt 0 Input                                                                                         |  |  |  |  |

| P1H.1   | 62                                            | 1     | CC6POS1 CAPCOM6: Position 1 Input, **)                                                                                        |  |  |  |  |

|         |                                               | 1     | EX1IN Fast External Interrupt 1 Input                                                                                         |  |  |  |  |

| P1H.2   | 63                                            | 1     | CC6POS2 CAPCOM6: Position 2 Input, **)                                                                                        |  |  |  |  |

|         |                                               | 1     | EX2IN Fast External Interrupt 2 Input                                                                                         |  |  |  |  |

| P1H.3   | 64                                            | 1     | EX3IN Fast External Interrupt 3 Input,                                                                                        |  |  |  |  |

|         |                                               |       | T7IN CAPCOM2: Timer T7 Count Input                                                                                            |  |  |  |  |

| P1H.4   | 65                                            | I/O   | CC24IO CAPCOM2: CC24 Capture Inp./Compare Outp.                                                                               |  |  |  |  |

| P1H.5   | 66                                            | I/O   | CC25IO CAPCOM2: CC25 Capture Inp./Compare Outp.                                                                               |  |  |  |  |

| P1H.6   | 67                                            | I/O   | CC26IO CAPCOM2: CC26 Capture Inp./Compare Outp.                                                                               |  |  |  |  |

| P1H.7   | 68                                            | I/O   | CC27IO CAPCOM2: CC27 Capture Inp./Compare Outp.                                                                               |  |  |  |  |

|         |                                               |       | Note: The marked (**) input signals are available only in devices with a full function CAPCOM6.                               |  |  |  |  |

| Table 2           | Piı                     | n Definit      | ions and Functions (cont'd)                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|-------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol            | Pin<br>No.              | Input<br>Outp. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P8                |                         | 10             | Port 8 is a 4-bit bidirectional I/O port. It is bit-wise<br>programmable for input or output via direction bits. For a pin<br>configured as input, the output driver is put into high-<br>impedance state. Port 8 outputs can be configured as push/<br>pull or open drain drivers. The input threshold of Port 8 is<br>selectable (TTL or special). Port 8 pins provide inputs/<br>outputs for CAPCOM2 and serial interface lines. <sup>1)</sup> |

| P8.0              | 72                      | I/O<br>I       | CC16IO CAPCOM2: CC16 Capture Inp./Compare Outp.,<br>CAN1_RxD CAN 1 Receive Data Input                                                                                                                                                                                                                                                                                                                                                             |

| P8.1              | 73                      | I/O<br>O       | CC17IO CAPCOM2: CC17 Capture Inp./Compare Outp.,<br>CAN1_TxD CAN 1 Transmit Data Output                                                                                                                                                                                                                                                                                                                                                           |

| P8.2              | 74                      | I/O<br>I       | CC18IO CAPCOM2: CC18 Capture Inp./Compare Outp.,<br>CAN1_RxD CAN 1 Receive Data Input                                                                                                                                                                                                                                                                                                                                                             |

| P8.3              | 75                      | I/O<br>O       | CC19IO CAPCOM2: CC19 Capture Inp./Compare Outp.,<br>CAN1_TxD CAN 1 Transmit Data Output                                                                                                                                                                                                                                                                                                                                                           |

| V <sub>AREF</sub> | 1                       | -              | Reference voltage for the A/D converter.                                                                                                                                                                                                                                                                                                                                                                                                          |

| V <sub>AGND</sub> | 80                      | -              | Reference ground for the A/D converter.                                                                                                                                                                                                                                                                                                                                                                                                           |

| V <sub>DD</sub>   | 7, 21,<br>40, 53,<br>61 | -              | Digital Supply Voltage:<br>+5 V during normal operation and idle mode.<br>≥2.5 V during power down mode.                                                                                                                                                                                                                                                                                                                                          |

| V <sub>SS</sub>   | 6, 20,<br>41, 56,<br>60 | _              | Digital Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

<sup>1)</sup> The CAN interface lines are assigned to ports P4 and P8 under software control. Within the CAN module several assignments can be selected.

Note: The following behavioural differences must be observed when the bidirectional reset is active:

- Bit BDRSTEN in register SYSCON cannot be changed after EINIT and is cleared automatically after a reset.

- The reset indication flags always indicate a long hardware reset.

- The PORT0 configuration is treated as if it were a hardware reset. In particular, the bootstrap loader may be activated when P0L.4 is low.

- Pin RSTIN may only be connected to external reset devices with an open drain output driver.

- A short hardware reset is extended to the duration of the internal reset sequence.

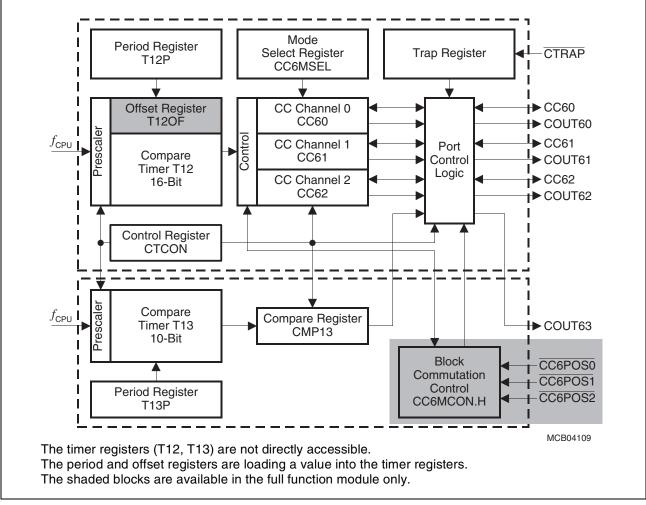

### The Capture/Compare Unit CAPCOM6

The CAPCOM6 unit supports generation and control of timing sequences on up to three 16-bit capture/compare channels plus one 10-bit compare channel.

In compare mode the CAPCOM6 unit provides two output signals per channel which have inverted polarity and non-overlapping pulse transitions. The compare channel can generate a single PWM output signal and is further used to modulate the capture/ compare output signals.

In capture mode the contents of compare timer 12 is stored in the capture registers upon a signal transition at pins CCx.

Compare timers T12 (16-bit) and T13 (10-bit) are free running timers which are clocked by the prescaled CPU clock.

#### Figure 5 CAPCOM6 Block Diagram

For motor control applications both subunits may generate versatile multichannel PWM signals which are basically either controlled by compare timer 12 or by a typical hall sensor pattern at the interrupt inputs (block commutation).

Note: Multichannel signal generation is provided only in devices with a full CAPCOM6.

#### **CAN-Module**

The integrated CAN-Module handles the completely autonomous transmission and reception of CAN frames in accordance with the CAN specification V2.0 part B (active), i.e. the on-chip CAN-Modules can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers.

The module provides Full CAN functionality on up to 15 message objects. Message object 15 may be configured for Basic CAN functionality. Both modes provide separate masks for acceptance filtering which allows to accept a number of identifiers in Full CAN mode and also allows to disregard a number of identifiers in Basic CAN mode. All message objects can be updated independent from the other objects and are equipped for the maximum message length of 8 bytes.

The bit timing is derived from the XCLK and is programmable up to a data rate of 1 Mbit/ s. Each CAN-Module uses two pins of Port 4 or Port 8 to interface to an external bus transceiver. The interface pins are assigned via software.

Note: When the CAN interface is assigned to Port 4, the respective segment address lines on Port 4 cannot be used. This will limit the external address space.

#### Watchdog Timer

The Watchdog Timer represents one of the fail-safe mechanisms which have been implemented to prevent the controller from malfunctioning for longer periods of time.

The Watchdog Timer is always enabled after a reset of the chip, and can only be disabled in the time interval until the EINIT (end of initialization) instruction has been executed. Thus, the chip's start-up procedure is always monitored. The software has to be designed to service the Watchdog Timer before it overflows. If, due to hardware or software related failures, the software fails to do so, the Watchdog Timer overflows and generates an internal hardware reset and pulls the RSTOUT pin low in order to allow external hardware components to be reset.

The Watchdog Timer is a 16-bit timer, clocked with the system clock divided by 2/4/128/256. The high byte of the Watchdog Timer register can be set to a prespecified reload value (stored in WDTREL) in order to allow further variation of the monitored time interval. Each time it is serviced by the application software, the high byte of the Watchdog Timer is reloaded. Thus, time intervals between 20  $\mu$ s and 336 ms can be monitored (@ 25 MHz).

The default Watchdog Timer interval after reset is 5.24 ms (@ 25 MHz).

#### **Parallel Ports**

The C164CI provides up to 59 I/O lines which are organized into five input/output ports and one input port. All port lines are bit-addressable, and all input/output lines are individually (bit-wise) programmable as inputs or outputs via direction registers. The I/O ports are true bidirectional ports which are switched to high impedance state when configured as inputs. The output drivers of three I/O ports can be configured (pin by pin) for push/pull operation or open-drain operation via control registers. During the internal reset, all port pins are configured as inputs.

The input threshold of Port 3, Port 4, and Port 8 is selectable (TTL or CMOS like), where the special CMOS like input threshold reduces noise sensitivity due to the input hysteresis. The input threshold may be selected individually for each byte of the respective ports.

All port lines have programmable alternate input or output functions associated with them. All port lines that are not used for these alternate functions may be used as general purpose IO lines.

PORT0 and PORT1 may be used as address and data lines when accessing external memory, while Port 4 outputs the additional segment address bits A21/19/17 ... A16 and the optional chip select signals in systems where segmentation is enabled to access more than 64 KBytes of memory.

Ports P1L, P1H, and P8 are associated with the capture inputs or compare outputs of the CAPCOM units and/or serve as external interrupt inputs.

Port 3 includes alternate functions of timers, serial interfaces, the optional bus control signal BHE/WRH, and the system clock output CLKOUT (or the programmable frequency output FOUT).

Port 5 is used for the analog input channels to the A/D converter or timer control signals.

The edge characteristics (transition time) and driver characteristics (output current) of the C164CI's port drivers can be selected via the Port Output Control registers (POCONx).

#### **Oscillator Watchdog**

The Oscillator Watchdog (OWD) monitors the clock signal generated by the on-chip oscillator (either with a crystal or via external clock drive). For this operation the PLL provides a clock signal which is used to supervise transitions on the oscillator clock. This PLL clock is independent from the XTAL1 clock. When the expected oscillator clock transitions are missing the OWD activates the PLL Unlock/OWD interrupt node and supplies the CPU with the PLL clock signal. Under these circumstances the PLL will oscillate with its basic frequency.

In direct drive mode the PLL base frequency is used directly ( $f_{CPU} = 2 \dots 5 \text{ MHz}$ ). In prescaler mode the PLL base frequency is divided by 2 ( $f_{CPU} = 1 \dots 2.5 \text{ MHz}$ ).

Note: The CPU clock source is only switched back to the oscillator clock after a hardware reset.

**The oscillator watchdog can be disabled** by setting bit OWDDIS in register SYSCON. In this case (OWDDIS = '1') the PLL remains idle and provides no clock signal, while the CPU clock signal is derived directly from the oscillator clock or via prescaler or SDD. Also no interrupt request will be generated in case of a missing oscillator clock.

Note: At the end of a reset bit OWDDIS reflects the inverted level of pin RD at that time. Thus the oscillator watchdog may also be disabled via hardware by (externally) pulling the RD line low upon a reset, similar to the standard reset configuration via PORT0.

#### **Special Function Registers Overview**

**Table 7** lists all SFRs which are implemented in the C164CI in alphabetical order. **Bit-addressable** SFRs are marked with the letter "**b**" in column "Name". SFRs within the **Extended SFR-Space** (ESFRs) are marked with the letter "**E**" in column "Physical Address". Registers within on-chip X-peripherals are marked with the letter "**X**" in column "Physical Address".

An SFR can be specified via its individual mnemonic name. Depending on the selected addressing mode, an SFR can be accessed via its physical address (using the Data Page Pointers), or via its short 8-bit address (without using the Data Page Pointers).

| Name     |   | Physica<br>Address |   | 8-Bit<br>Addr.  | Description                                                   | Reset<br>Value    |

|----------|---|--------------------|---|-----------------|---------------------------------------------------------------|-------------------|

| ADCIC    | b | FF98 <sub>H</sub>  |   | CCH             | A/D Converter End of Conversion<br>Interrupt Control Register | 0000 <sub>H</sub> |

| ADCON    | b | FFA0 <sub>H</sub>  |   | D0 <sub>H</sub> | A/D Converter Control Register                                | 0000 <sub>H</sub> |

| ADDAT    |   | FEA0 <sub>H</sub>  |   | 50 <sub>H</sub> | A/D Converter Result Register                                 | 0000 <sub>H</sub> |

| ADDAT2   |   | F0A0 <sub>H</sub>  | Ε | 50 <sub>H</sub> | A/D Converter 2 Result Register                               | 0000 <sub>H</sub> |

| ADDRSEL1 |   | FE18 <sub>H</sub>  |   | 0C <sub>H</sub> | Address Select Register 1                                     | 0000 <sub>H</sub> |

| ADDRSEL2 |   | FE1A <sub>H</sub>  |   | 0D <sub>H</sub> | Address Select Register 2                                     | 0000 <sub>H</sub> |

| ADDRSEL3 |   | FE1C <sub>H</sub>  |   | 0E <sub>H</sub> | Address Select Register 3                                     | 0000 <sub>H</sub> |

| ADDRSEL4 | • | FE1E <sub>H</sub>  |   | 0F <sub>H</sub> | Address Select Register 4                                     | 0000 <sub>H</sub> |

| ADEIC    | b | FF9A <sub>H</sub>  |   | CD <sub>H</sub> | A/D Converter Overrun Error Interrupt<br>Control Register     | 0000 <sub>H</sub> |

| BUSCON0  | b | FF0C <sub>H</sub>  |   | 86 <sub>H</sub> | Bus Configuration Register 0                                  | 0000 <sub>H</sub> |

| BUSCON1  | b | FF14 <sub>H</sub>  |   | 8A <sub>H</sub> | Bus Configuration Register 1                                  | 0000 <sub>H</sub> |

| BUSCON2  | b | FF16 <sub>H</sub>  |   | 8B <sub>H</sub> | Bus Configuration Register 2                                  | 0000 <sub>H</sub> |

| BUSCON3  | b | FF18 <sub>H</sub>  |   | 8C <sub>H</sub> | Bus Configuration Register 3                                  | 0000 <sub>H</sub> |

| BUSCON4  | b | FF1A <sub>H</sub>  |   | 8D <sub>H</sub> | Bus Configuration Register 4                                  | 0000 <sub>H</sub> |

| C1BTR    |   | EF04 <sub>H</sub>  | Χ |                 | CAN1 Bit Timing Register                                      | UUUU <sub>H</sub> |

| C1CSR    |   | EF00 <sub>H</sub>  | Χ |                 | CAN1 Control / Status Register                                | XX01 <sub>H</sub> |

| C1GMS    |   | EF06 <sub>H</sub>  | Χ |                 | CAN1 Global Mask Short                                        | UFUU <sub>H</sub> |

| C1LARn   |   | EFn4 <sub>H</sub>  | Χ |                 | CAN Lower Arbitration Register (msg. n)                       | UUUU <sub>H</sub> |

| C1LGML   |   | EF0A <sub>H</sub>  | Χ |                 | CAN Lower Global Mask Long                                    | UUUU <sub>H</sub> |

| C1LMLM   |   | EF0E <sub>H</sub>  | Χ |                 | CAN Lower Mask of Last Message                                | UUUU <sub>H</sub> |

#### Table 7 C164Cl Registers, Ordered by Name

| Table 7 C164CI Registers, Ordered by Name (cont d) |   |                     |   |                 |                                         |                   |  |

|----------------------------------------------------|---|---------------------|---|-----------------|-----------------------------------------|-------------------|--|

| Name                                               |   | Physical<br>Address |   | 8-Bit<br>Addr.  | Description                             | Reset<br>Value    |  |

| XP3IC                                              | b | F19E <sub>H</sub>   | Ε | CF <sub>H</sub> | PLL/RTC Interrupt Control Register      | 0000 <sub>H</sub> |  |

| ZEROS                                              | b | FF1C <sub>H</sub>   |   | 8E <sub>H</sub> | Constant Value 0's Register (read only) | 0000 <sub>H</sub> |  |

#### Table 7 C164Cl Registers, Ordered by Name (cont'd)

<sup>1)</sup> The system configuration is selected during reset.

<sup>2)</sup> The reset value depends on the indicated reset source.

Note: The three registers of the OTP programming interface are, of course, only implemented in the OTP versions of the C164CI.

#### **Operating Conditions**

The following operating conditions must not be exceeded in order to ensure correct operation of the C164CI. All parameters specified in the following sections refer to these operating conditions, unless otherwise noticed.

| Parameter                         | Symbol            | Limit             | Values | Unit | Notes                                              |

|-----------------------------------|-------------------|-------------------|--------|------|----------------------------------------------------|

|                                   |                   | min.              | max.   |      |                                                    |

| Digital supply voltage            | V <sub>DD</sub>   | 4.75              | 5.5    | V    | Active mode,<br>$f_{CPUmax} = 25 \text{ MHz}$      |

|                                   |                   | 2.5 <sup>1)</sup> | 5.5    | V    | PowerDown mode                                     |

| Digital ground voltage            | V <sub>SS</sub>   |                   | 0      | V    | Reference voltage                                  |

| Overload current                  | I <sub>OV</sub>   | _                 | ±5     | mA   | Per pin <sup>2)3)</sup>                            |

| Absolute sum of overload currents | $\Sigma  I_{OV} $ | _                 | 50     | mA   | 3)                                                 |

| External Load<br>Capacitance      | CL                | _                 | 100    | pF   | Pin drivers in <b>default</b> mode <sup>4)5)</sup> |

| Ambient temperature               | T <sub>A</sub>    | 0                 | 70     | °C   | SAB-C164CI                                         |

|                                   |                   | -40               | 85     | °C   | SAF-C164CI                                         |

|                                   |                   | -40               | 125    | °C   | SAK-C164CI                                         |

#### Table 9 Operating Condition Parameters

<sup>1)</sup> Output voltages and output currents will be reduced when  $V_{\text{DD}}$  leaves the range defined for active mode.

- <sup>2)</sup> Overload conditions occur if the standard operatings conditions are exceeded, i.e. the voltage on any pin exceeds the specified range (i.e. V<sub>OV</sub> > V<sub>DD</sub> + 0.5 V or V<sub>OV</sub> < V<sub>SS</sub> 0.5 V). The absolute sum of input overload currents on all pins may not exceed **50 mA**. The supply voltage must remain within the specified limits. Proper operation is not guaranteed if overload conditions occur on functional pins line XTAL1, RD, WR, etc.

- <sup>3)</sup> Not 100% tested, guaranteed by design and characterization.

- <sup>4)</sup> The timing is valid for pin drivers operating in default current mode (selected after reset). Reducing the output current may lead to increased delays or reduced driving capability ( $C_L$ ).

- <sup>5)</sup> The current ROM-version of the C164CI is equipped with port drivers, which provide reduced driving capability and reduced control. Please refer to the actual errata sheet for details.

| Port Output Driver<br>Mode | Maximum Output Current $(I_{OLmax}, -I_{OHmax})^{1}$ | Nominal Output Current<br>( <i>I</i> <sub>OLnom</sub> , - <i>I</i> <sub>OHnom</sub> ) <sup>2)</sup> |

|----------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Strong driver              | 10 mA                                                | 2.5 mA                                                                                              |

| Medium driver              | 4.0 mA                                               | 1.0 mA                                                                                              |

| Weak driver                | 0.5 mA                                               | 0.1 mA                                                                                              |

#### Table 10 Current Limits for Port Output Drivers

<sup>1)</sup> An output current above II<sub>OXnom</sub>I may be drawn from up to three pins at the same time. For any group of 16 neighboring port output pins the total output current in each direction (ΣI<sub>OL</sub> and Σ-I<sub>OH</sub>) must remain below 50 mA.

<sup>2)</sup> The current ROM-version of the C164CI (step Ax) is equipped with port drivers, which provide reduced driving capability and reduced control. Please refer to the actual errata sheet for details.

#### Power Consumption C164CI (ROM)

(Operating Conditions apply)

| Parameter                                                                                 | Sym-                           | Limit | Values                         | Unit | Test                                                                                      |

|-------------------------------------------------------------------------------------------|--------------------------------|-------|--------------------------------|------|-------------------------------------------------------------------------------------------|

|                                                                                           | bol                            | min.  | max.                           |      | Conditions                                                                                |

| Power supply current (active) with all peripherals active                                 | I <sub>DD</sub>                | _     | 1 +<br>2.5 × f <sub>CPU</sub>  | mA   | $\overline{\text{RSTIN}} = V_{\text{IL}}$ $f_{\text{CPU}} \text{ in } [\text{MHz}]^{1)}$  |

| Idle mode supply current<br>with all peripherals active                                   | I <sub>IDX</sub>               | _     | 1 +<br>1.1 × f <sub>CPU</sub>  | mA   | $\overline{\text{RSTIN}} = V_{\text{IH1}}$ $f_{\text{CPU}} \text{ in [MHz]}^{1)}$         |

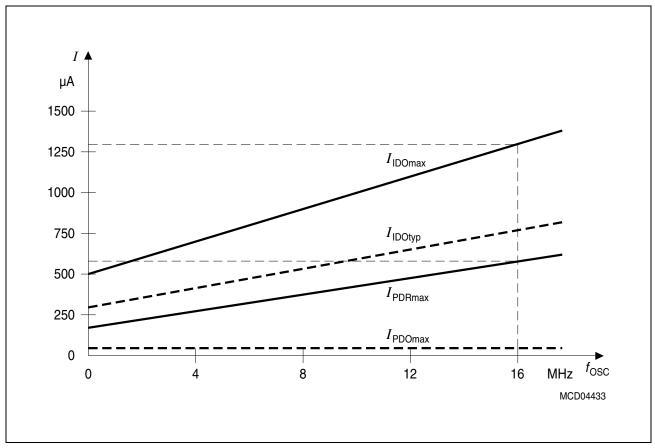

| Idle mode supply current<br>with all peripherals deactivated,<br>PLL off, SDD factor = 32 | I <sub>IDO</sub> <sup>2)</sup> | _     | 500 +<br>50 × f <sub>OSC</sub> | μA   | $\overline{\text{RSTIN}} = V_{\text{IH1}}$ $f_{\text{OSC}} \text{ in } [\text{MHz}]^{1)}$ |

| Sleep and Power-down mode supply current with RTC running                                 | I <sub>PDR</sub> <sup>2)</sup> | -     | 200 +<br>25 × f <sub>OSC</sub> | μA   | $V_{\text{DD}} = V_{\text{DDmax}}$<br>$f_{\text{OSC}}$ in [MHz] <sup>3)</sup>             |

| Sleep and Power-down mode supply current with RTC disabled                                | I <sub>PDO</sub>               | _     | 50                             | μA   | $V_{\rm DD} = V_{\rm DDmax}^{3)}$                                                         |

<sup>1)</sup> The supply current is a function of the operating frequency. This dependency is illustrated in Figure 9. These parameters are tested at V<sub>DDmax</sub> and maximum CPU clock with all outputs disconnected and all inputs at V<sub>IL</sub> or V<sub>IH</sub>.

<sup>2)</sup> This parameter is determined mainly by the current consumed by the oscillator (see Figure 8). This current, however, is influenced by the external oscillator circuitry (crystal, capacitors). The values given refer to a typical circuitry and may change in case of a not optimized external oscillator circuitry.

<sup>3)</sup> This parameter is tested including leakage currents. All inputs (including pins configured as inputs) at 0 V to 0.1 V or at  $V_{DD}$  - 0.1 V to  $V_{DD}$ ,  $V_{REF}$  = 0 V, all outputs (including pins configured as outputs) disconnected.

Figure 8 Idle and Power Down Supply Current as a Function of Oscillator Frequency

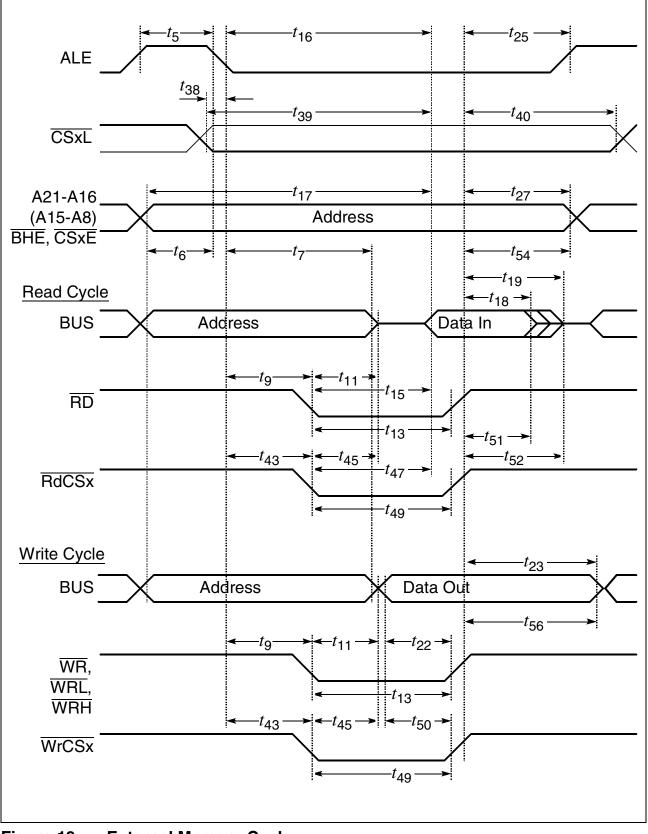

Figure 19 External Memory Cycle: Multiplexed Bus, No Read/Write Delay, Extended ALE

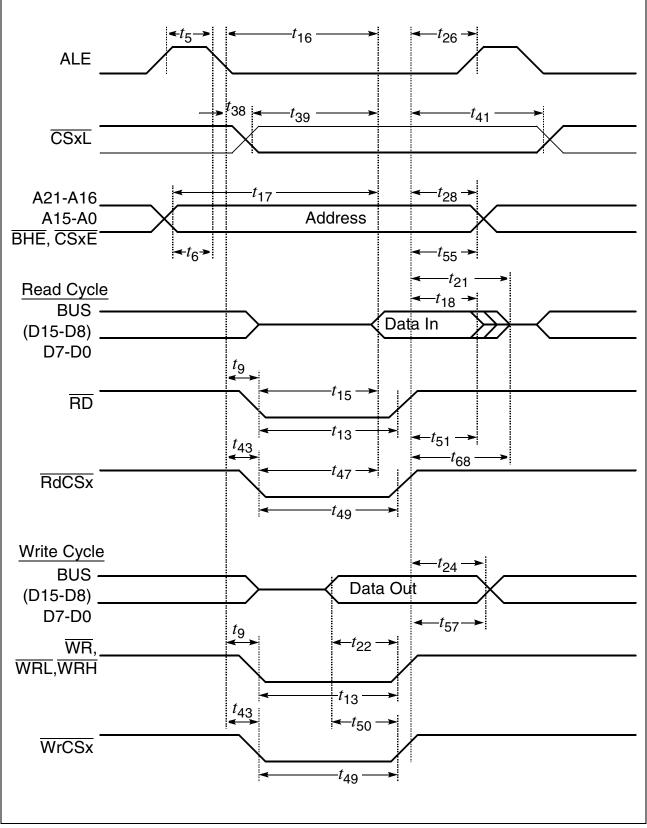

#### Demultiplexed Bus (cont'd)

(Operating Conditions apply)

ALE cycle time = 4 TCL +  $2t_A$  +  $t_C$  +  $t_F$  (80 ns at 25 MHz CPU clock without waitstates)

| Parameter                                            | Symbol                    | Max. CPU Clock<br>= 25 MHz |             | Variable CPU Clock<br>1 / 2TCL = 1 to 25 MHz |                                  | Unit |

|------------------------------------------------------|---------------------------|----------------------------|-------------|----------------------------------------------|----------------------------------|------|

|                                                      |                           | min.                       | max.        | min.                                         | max.                             |      |

| Data float after RdCS<br>(no RW-delay) <sup>1)</sup> | <i>t</i> <sub>68</sub> SR | _                          | $0 + t_{F}$ | _                                            | TCL - 20<br>+ $2t_A + t_F^{(1)}$ | ns   |

| Address hold after<br>RdCS, WrCS                     | <i>t</i> <sub>55</sub> CC | -6 + <i>t</i> <sub>F</sub> | _           | -6 + <i>t</i> <sub>F</sub>                   | _                                | ns   |

| Data hold after WrCS                                 | <i>t</i> <sub>57</sub> CC | 6 + <i>t</i> <sub>F</sub>  | _           | TCL - 14 +<br><i>t</i> <sub>F</sub>          | _                                | ns   |

<sup>1)</sup> RW-delay and  $t_A$  refer to the next following bus cycle (including an access to an on-chip X-Peripheral).

<sup>2)</sup> Read data are latched with the same clock edge that triggers the address change and the rising RD edge. Therefore address changes before the end of RD have no impact on read cycles.

<sup>3)</sup> These parameters refer to the latched chip select signals (CSxL). The early chip select signals (CSxE) are specified together with the address and signal BHE (see figures below).

Figure 22 External Memory Cycle: Demultiplexed Bus, No Read/Write Delay, Normal ALE