Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M4                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 80MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QSPI, SAI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, PWM, WDT                                   |

| Number of I/O              | 38                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 160K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                            |

| Data Converters            | A/D 10x12b; D/A 1x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 48-UFQFN Exposed Pad                                                    |

| Supplier Device Package    | 48-UFQFPN (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l452ccu6   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

STM32L452xx List of figures

|             | array package recommended footprint                                          | 103 |

|-------------|------------------------------------------------------------------------------|-----|

| Figure 46.  | UFBGA100 marking (package top view)                                          |     |

| Figure 47.  | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline            |     |

| Figure 48.  | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package                    | 193 |

| rigule 40.  |                                                                              | 106 |

| Figure 40   | recommended footprint                                                        |     |

| Figure 49.  | LQFP64 marking (package top view)                                            | 197 |

| Figure 50.  | UFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch ultra profile fine pitch ball grid |     |

|             | array package outline                                                        | 197 |

| Figure 51.  | UFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch ultra profile fine pitch ball grid |     |

|             | array package recommended footprint                                          | 198 |

| Figure 52.  | UFBGA64 marking (package top view)                                           | 199 |

| Figure 53.  | WLCSP64 - 64-ball, 3.357x3.657 mm 0.4 mm pitch wafer level chip scale        |     |

| J           | package outline                                                              | 200 |

| Figure 54.  | WLCSP64 - 64-pin, 3.357x3.657 mm 0.4 mm pitch wafer level chip scale         |     |

|             | recommended footprint                                                        | 201 |

| Figure 55.  | WLCSP64 marking (package top view)                                           |     |

| Figure 56.  | UFQFPN48 - 48-lead, 7x7 mm, 0.5 mm pitch, ultra thin fine pitch quad flat    |     |

| i iguio co. | package outline                                                              | 203 |

| Figure 57.  | UFQFPN48 - 48-lead, 7x7 mm, 0.5 mm pitch, ultra thin fine pitch quad flat    | 200 |

| i iguie 57. |                                                                              | 204 |

| Ciarra EO   | package recommended footprint                                                |     |

| Figure 58.  | UFQFPN48 marking (package top view)                                          |     |

| Figure 59   | LOFP64 Pp max vs. T <sub>4</sub>                                             | 208 |

DS11912 Rev 4 11/212

STM32L452xx Description

## 2 Description

The STM32L452xx devices are the ultra-low-power microcontrollers based on the high-performance Arm<sup>®</sup> Cortex<sup>®</sup>-M4 32-bit RISC core operating at a frequency of up to 80 MHz. The Cortex-M4 core features a Floating point unit (FPU) single precision which supports all Arm<sup>®</sup> single-precision data-processing instructions and data types. It also implements a full set of DSP instructions and a memory protection unit (MPU) which enhances application security.

The STM32L452xx devices embed high-speed memories (Flash memory up to 512 Kbyte, 160 Kbyte of SRAM), a Quad SPI flash memories interface (available on all packages) and an extensive range of enhanced I/Os and peripherals connected to two APB buses, two AHB buses and a 32-bit multi-AHB bus matrix.

The STM32L452xx devices embed several protection mechanisms for embedded Flash memory and SRAM: readout protection, write protection, proprietary code readout protection and Firewall.

The devices offer a fast 12-bit ADC (5 Msps), two comparators, one operational amplifier, one DAC channel, an internal voltage reference buffer, a low-power RTC, one general-purpose 32-bit timer, one 16-bit PWM timer dedicated to motor control, four general-purpose 16-bit timers, and two 16-bit low-power timers.

In addition, up to 21 capacitive sensing channels are available.

They also feature standard and advanced communication interfaces.

- Four I2Cs

- Three SPIs

- Three USARTs, one UART and one Low-Power UART.

- One SAI (Serial Audio Interfaces)

- One SDMMC

- One CAN

- One USB full-speed device crystal less

The STM32L452xx operates in the -40 to +85 °C (+105 °C junction) and -40 to +125 °C (+130 °C junction) temperature ranges from a 1.71 to 3.6 V  $V_{DD}$  power supply when using internal LDO regulator and a 1.05 to 1.32V  $V_{DD12}$  power supply when using external SMPS supply. A comprehensive set of power-saving modes allows the design of low-power applications.

Some independent power supplies are supported: analog independent supply input for ADC, DAC, OPAMP and comparators. A VBAT input allows to backup the RTC and backup registers. Dedicated  $V_{DD12}$  power supplies can be used to bypass the internal LDO regulator when connected to an external SMPS.

The STM32L452xx family offers six packages from 48 to 100-pin packages.

DS11912 Rev 4 13/212

Functional overview STM32L452xx

## 3.4 Embedded Flash memory

STM32L452xx devices feature up to 512 Kbyte of embedded Flash memory available for storing programs and data in single bank architecture. The Flash memory contains 256 pages of 2 Kbyte.

Flexible protections can be configured thanks to option bytes:

- Readout protection (RDP) to protect the whole memory. Three levels are available:

- Level 0: no readout protection

- Level 1: memory readout protection: the Flash memory cannot be read from or written to if either debug features are connected, boot in RAM or bootloader is selected

- Level 2: chip readout protection: debug features (Cortex-M4 JTAG and serial wire), boot in RAM and bootloader selection are disabled (JTAG fuse). This selection is irreversible.

| Area      | Protection | U    | ser executio | on                 | •    | oot from RA<br>tem memor |                    |

|-----------|------------|------|--------------|--------------------|------|--------------------------|--------------------|

|           | level      | Read | Write        | Erase              | Read | Write                    | Erase              |

| Main      | 1          | Yes  | Yes          | Yes                | No   | No                       | No                 |

| memory    | 2          | Yes  | Yes          | Yes                | N/A  | N/A                      | N/A                |

| System    | 1          | Yes  | No           | No                 | Yes  | No                       | No                 |

| memory    | 2          | Yes  | No           | No                 | N/A  | N/A                      | N/A                |

| Option    | 1          | Yes  | Yes          | Yes                | Yes  | Yes                      | Yes                |

| bytes     | 2          | Yes  | No           | No                 | N/A  | N/A                      | N/A                |

| Backup    | 1          | Yes  | Yes          | N/A <sup>(1)</sup> | No   | No                       | N/A <sup>(1)</sup> |

| registers | 2          | Yes  | Yes          | N/A                | N/A  | N/A                      | N/A                |

|           | 1          |      |              |                    |      |                          |                    |

Yes<sup>(1)</sup>

Yes

No

N/A

Table 3. Access status versus readout protection level and execution modes

SRAM2

Yes

Yes

• Write protection (WRP): the protected area is protected against erasing and programming. Two areas can be selected, with 2-Kbyte granularity.

Yes

Yes

Proprietary code readout protection (PCROP): a part of the flash memory can be protected against read and write from third parties. The protected area is execute-only: it can only be reached by the STM32 CPU, as an instruction code, while all other accesses (DMA, debug and CPU data read, write and erase) are strictly prohibited. The PCROP area granularity is 64-bit wide. An additional option bit (PCROP\_RDP) allows to select if the PCROP area is erased or not when the RDP protection is changed from Level 1 to Level 0.

18/212 DS11912 Rev 4

No<sup>(1)</sup>

N/A

No

N/A

<sup>1.</sup> Erased when RDP change from Level 1 to Level 0.

Functional overview STM32L452xx

#### 3.23.1 Advanced-control timer (TIM1)

The advanced-control timer can each be seen as a three-phase PWM multiplexed on 6 channels. They have complementary PWM outputs with programmable inserted dead-times. They can also be seen as complete general-purpose timers. The 4 independent channels can be used for:

- Input capture

- Output compare

- PWM generation (edge or center-aligned modes) with full modulation capability (0-100%)

- One-pulse mode output

In debug mode, the advanced-control timer counter can be frozen and the PWM outputs disabled to turn off any power switches driven by these outputs.

Many features are shared with those of the general-purpose TIMx timers (described in Section 3.23.2) using the same architecture, so the advanced-control timer can work together with the TIMx timers via the Timer Link feature for synchronization or event chaining.

#### 3.23.2 General-purpose timers (TIM2, TIM3, TIM15, TIM16)

There are up to three synchronizable general-purpose timers embedded in the STM32L452xx (see *Table 11* for differences). Each general-purpose timer can be used to generate PWM outputs, or act as a simple time base.

TIM2, TIM3

They are full-featured general-purpose timers:

- TIM2 has a 32-bit auto-reload up/downcounter and 32-bit prescaler.

- TIM3 has 16-bit auto-reload up/downcounter and 16-bit prescaler.

These timers feature 4 independent channels for input capture/output compare, PWM or one-pulse mode output. They can work with the other general-purpose timers via the Timer Link feature for synchronization or event chaining.

The counters can be frozen in debug mode.

All have independent DMA request generation and support quadrature encoder.

TIM15 and 16

They are general-purpose timers with mid-range features:

They have 16-bit auto-reload upcounters and 16-bit prescalers.

- TIM15 has 2 channels and 1 complementary channel

- TIM16 has 1 channel and 1 complementary channel

All channels can be used for input capture/output compare, PWM or one-pulse mode output.

The timers can work together via the Timer Link feature for synchronization or event chaining. The timers have independent DMA request generation.

The counters can be frozen in debug mode.

### 3.23.3 Basic timer (TIM6)

The basic timer is mainly used for DAC trigger generation. It can also be used as generic 16-bit timebase.

Functional overview STM32L452xx

### 3.28 Serial peripheral interface (SPI)

Three SPI interfaces allow communication up to 40 Mbits/s in master and up to 24 Mbits/s slave modes, in half-duplex, full-duplex and simplex modes. The 3-bit prescaler gives 8 master mode frequencies and the frame size is configurable from 4 bits to 16 bits. The SPI interfaces support NSS pulse mode, TI mode and Hardware CRC calculation.

All SPI interfaces can be served by the DMA controller.

### 3.29 Serial audio interfaces (SAI)

The device embeds 1 SAI. Refer to *Table 14: SAI implementation* for the features implementation. The SAI bus interface handles communications between the microcontroller and the serial audio protocol.

The SAI peripheral supports:

- Two independent audio sub-blocks which can be transmitters or receivers with their respective FIFO.

- 8-word integrated FIFOs for each audio sub-block.

- Synchronous or asynchronous mode between the audio sub-blocks.

- Master or slave configuration independent for both audio sub-blocks.

- Clock generator for each audio block to target independent audio frequency sampling when both audio sub-blocks are configured in master mode.

- Data size configurable: 8-, 10-, 16-, 20-, 24-, 32-bit.

- Peripheral with large configurability and flexibility allowing to target as example the following audio protocol: I2S, LSB or MSB-justified, PCM/DSP, TDM, AC'97 and SPDIF out

- Up to 16 slots available with configurable size and with the possibility to select which

ones are active in the audio frame.

- Number of bits by frame may be configurable.

- Frame synchronization active level configurable (offset, bit length, level).

- First active bit position in the slot is configurable.

- LSB first or MSB first for data transfer.

- Mute mode.

- Stereo/Mono audio frame capability.

- Communication clock strobing edge configurable (SCK).

- Error flags with associated interrupts if enabled respectively.

- Overrun and underrun detection.

- Anticipated frame synchronization signal detection in slave mode.

- Late frame synchronization signal detection in slave mode.

- Codec not ready for the AC'97 mode in reception.

- Interruption sources when enabled:

- Errors.

- FIFO requests.

- DMA interface with 2 dedicated channels to handle access to the dedicated integrated FIFO of each SAI audio sub-block.

1 2 11 12 H3-BOOT( PB4 (NJTRST) PB3 (JTDO/ TRACESWO) PA14 (JTCK/ SWCLK) PA13 (JTMS SWDIO) PE3 PE1 PB8 PD7 PD5 PA15 (JTDI) PA12 PE2 PB7 PC10 PE4 PB6 PD6 PD4 PD3 PC12 PA11 PB9 VDD PC13 PE5 PE0 PB5 PD2 PD0 PC11 VDDUSB PA10 PE6 VSS PA9 PA8 PC9 PC15-OSC32\_OUT (PC15) VBAT VSS PC8 PC7 PC6 vss vss VSS UFBGA100 VDD VDD VDD PC0 NRST VDD PD15 PD14 PD13 VSSA PC2 PD12 PD11 PD10 VREF-PC4 PB15 PB14 PB13 VREF+ MSv40961V1

Figure 7. STM32L452Vx UFBGA100 ballout<sup>(1)</sup>

1. The above figure shows the package top view.

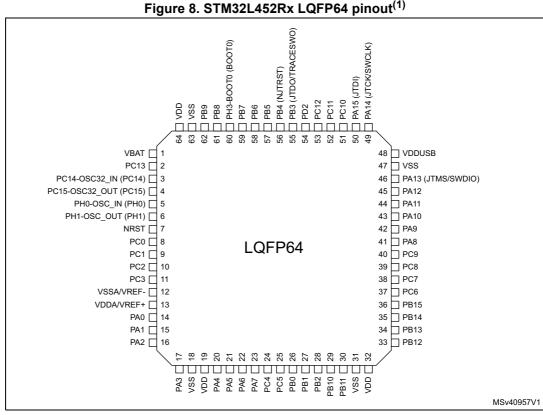

Figure 8. STM32L452Rx LQFP64 pinout<sup>(1)</sup>

1. The above figure shows the package top view.

Pinouts and pin description

| r      |      |         | 1                   |                         | Tunction Art to           | •                      | <del>, , , , , , , , , , , , , , , , , , , </del> |                      |                              |

|--------|------|---------|---------------------|-------------------------|---------------------------|------------------------|---------------------------------------------------|----------------------|------------------------------|

|        |      | AF0     | AF1                 | AF2                     | AF3                       | AF4                    | AF5                                               | AF6                  | AF7                          |

| Po     | ort  | SYS_AF  | TIM1/TIM2<br>LPTIM1 | I2C4/TIM1/<br>TIM2/TIM3 | I2C4/USART2/<br>CAN1/TIM1 | 2C1/ 2C2/<br> 2C3/ 2C4 | SPI1/SPI2/I2C4                                    | SPI3/DFSDM/<br>COMP1 | USART1/<br>USART2/<br>USART3 |

|        | PC0  | -       | LPTIM1_IN1          | I2C4_SCL                | -                         | I2C3_SCL               | -                                                 | -                    | -                            |

|        | PC1  | TRACED0 | LPTIM1_OUT          | I2C4_SDA                | -                         | I2C3_SDA               | -                                                 | -                    | -                            |

|        | PC2  | -       | LPTIM1_IN2          | -                       | -                         | -                      | SPI2_MISO                                         | DFSDM1_<br>CKOUT     | -                            |

|        | PC3  | -       | LPTIM1_ETR          | -                       | -                         | -                      | SPI2_MOSI                                         | -                    | -                            |

|        | PC4  | -       | -                   | -                       | -                         | -                      | -                                                 | -                    | USART3_TX                    |

|        | PC5  | -       | -                   | -                       | -                         | -                      | -                                                 | -                    | USART3_RX                    |

|        | PC6  | -       | -                   | TIM3_CH1                | -                         | -                      | -                                                 | DFSDM1_<br>CKIN3     | -                            |

| Port C | PC7  | -       | -                   | TIM3_CH2                | -                         | -                      | -                                                 | DFSDM1_<br>DATIN3    | -                            |

|        | PC8  | -       | -                   | TIM3_CH3                | -                         | -                      | -                                                 | -                    | -                            |

|        | PC9  | -       | -                   | TIM3_CH4                | -                         | -                      | -                                                 | -                    | -                            |

|        | PC10 | TRACED1 | -                   | -                       | -                         | -                      | -                                                 | SPI3_SCK             | USART3_TX                    |

|        | PC11 | -       | -                   | -                       | -                         | -                      | -                                                 | SPI3_MISO            | USART3_RX                    |

|        | PC12 | TRACED3 | -                   | -                       | -                         | -                      | -                                                 | SPI3_MOSI            | USART3_CK                    |

|        | PC13 | -       | -                   | -                       | -                         | -                      | -                                                 | -                    | -                            |

|        | PC14 | -       | -                   | -                       | -                         | -                      | -                                                 | -                    | -                            |

|        | PC15 | -       | -                   | -                       | -                         | -                      | -                                                 | -                    | -                            |

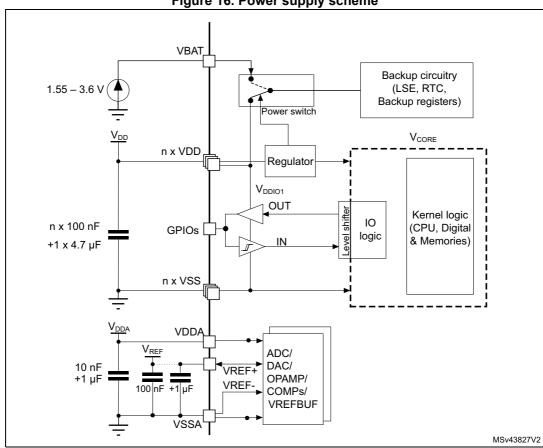

#### 6.1.6 Power supply scheme

Figure 16. Power supply scheme

Caution:

Each power supply pair ( $V_{DD}/V_{SS}$ ,  $V_{DDA}/V_{SSA}$  etc.) must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below, the appropriate pins on the underside of the PCB to ensure the good functionality of the device.

| Table 20. Voltage characteristics <sup>(1)</sup> (continued) |

|--------------------------------------------------------------|

|--------------------------------------------------------------|

| Symbol                            | Ratings                                                                     | Min | Max | Unit |

|-----------------------------------|-----------------------------------------------------------------------------|-----|-----|------|

| $ \Delta V_{DDx} $                | Variations between different V <sub>DDX</sub> power pins of the same domain | -   | 50  | mV   |

| V <sub>SSx</sub> -V <sub>SS</sub> | Variations between all the different ground pins <sup>(5)</sup>             | -   | 50  | mV   |

- All main power (V<sub>DD</sub>, V<sub>DDA</sub>, V<sub>DDUSB</sub>, V<sub>BAT</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

- V<sub>IN</sub> maximum must always be respected. Refer to Table 21: Current characteristics for the maximum allowed injected current values.

- 3. This formula has to be applied only on the power supplies related to the IO structure described in the pin definition table.

- 4. To sustain a voltage higher than 4 V the internal pull-up/pull-down resistors must be disabled.

- 5. Include VREF- pin.

**Table 21. Current characteristics**

| Symbol                    | Ratings                                                                              | Max                  | Unit |

|---------------------------|--------------------------------------------------------------------------------------|----------------------|------|

| $\Sigma IV_{DD}$          | Total current into sum of all V <sub>DD</sub> power lines (source) <sup>(1)(2)</sup> | 140                  |      |

| ΣIV <sub>SS</sub>         | Total current out of sum of all V <sub>SS</sub> ground lines (sink) <sup>(1)</sup>   | 140                  |      |

| IV <sub>DD(PIN)</sub>     | Maximum current into each V <sub>DD</sub> power pin (source) <sup>(1)</sup>          | 100                  |      |

| IV <sub>SS(PIN)</sub>     | Maximum current out of each V <sub>SS</sub> ground pin (sink) <sup>(1)</sup>         | 100                  |      |

|                           | Output current sunk by any I/O and control pin except FT_f                           | 20                   |      |

| $I_{IO(PIN)}$             | Output current sunk by any FT_f pin                                                  | 20                   |      |

|                           | Output current sourced by any I/O and control pin                                    | 20                   | mA   |

| <b>~</b> 1                | Total output current sunk by sum of all I/Os and control pins <sup>(3)</sup>         | 100                  |      |

| $\Sigma I_{IO(PIN)}$      | Total output current sourced by sum of all I/Os and control pins <sup>(3)</sup>      | 100                  |      |

| I <sub>INJ(PIN)</sub> (4) | Injected current on FT_xxx, TT_xx, RST and B pins, except PA4, PA5                   | -5/+0 <sup>(5)</sup> |      |

|                           | Injected current on PA4, PA5                                                         | -5/0                 |      |

| $\Sigma  I_{INJ(PIN)} $   | Total injected current (sum of all I/Os and control pins) <sup>(6)</sup>             | 25                   |      |

- All main power (V<sub>DD</sub>, V<sub>DDA</sub>, V<sub>DDUSB</sub>, V<sub>BAT</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supplies, in the permitted range.

- 2. Valid also for V<sub>DD12</sub> on SMPS packages.

- 3. This current consumption must be correctly distributed over all I/Os and control pins. The total output current must not be sunk/sourced between two consecutive power supply pins referring to high pin count QFP packages.

- Positive injection (when V<sub>IN</sub> > V<sub>DDIOx</sub>) is not possible on these I/Os and does not occur for input voltages lower than the specified maximum value.

- A negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer also to *Table 20: Voltage characteristics* for the maximum allowed input voltage values.

- When several inputs are submitted to a current injection, the maximum ∑|I<sub>INJ(PIN)</sub>| is the absolute sum of the negative injected currents (instantaneous values).

DS11912 Rev 4 91/212

Electrical characteristics

Table 31. Current consumption in Run and Low-power run modes, code with data processing running from SRAM1

|                                                |                              | Condi                                                          | tions           |                   |       |       | TYP   |           |           |       |       | MAX <sup>(1)</sup> |           |           |      |

|------------------------------------------------|------------------------------|----------------------------------------------------------------|-----------------|-------------------|-------|-------|-------|-----------|-----------|-------|-------|--------------------|-----------|-----------|------|

| Symbol                                         | Parameter                    | -                                                              | Voltage scaling | f <sub>HCLK</sub> | 25 °C | 55 °C | 85 °C | 105<br>°C | 125<br>°C | 25 °C | 55 °C | 85 °C              | 105<br>°C | 125<br>°C | Unit |

|                                                |                              |                                                                |                 | 26 MHz            | 2.40  | 2.40  | 2.55  | 2.70      | 3.05      | 2.70  | 2.75  | 2.90               | 3.20      | 3.80      |      |

|                                                | £ _£                         |                                                                |                 | 16 MHz            | 1.50  | 1.55  | 1.65  | 1.80      | 2.15      | 1.70  | 1.80  | 1.95               | 2.25      | 2.80      |      |

|                                                |                              |                                                                |                 | 8 MHz             | 0.820 | 0.850 | 0.950 | 1.10      | 1.45      | 0.95  | 1.00  | 1.15               | 1.45      | 2.00      |      |

|                                                |                              |                                                                | Range 2         | 4 MHz             | 0.470 | 0.500 | 0.600 | 0.765     | 1.10      | 0.55  | 0.60  | 0.75               | 1.05      | 1.60      |      |

|                                                |                              | f <sub>HCLK</sub> = f <sub>HSE</sub> up to                     |                 | 2 MHz             | 0.295 | 0.325 | 0.420 | 0.585     | 0.915     | 0.35  | 0.40  | 0.55               | 0.85      | 1.40      |      |

|                                                | Committee                    | 48MHz included,                                                |                 | 1 MHz             | 0.210 | 0.235 | 0.330 | 0.495     | 0.825     | 0.25  | 0.30  | 0.45               | 0.75      | 1.30      |      |

| I <sub>DD_ALL</sub> Supply current in Run mode | bypass mode<br>PLL ON above  |                                                                | 100 kHz         | 0.130             | 0.155 | 0.250 | 0.415 | 0.750     | 0.15      | 0.25  | 0.35  | 0.65               | 1.25      | mA        |      |

|                                                |                              |                                                                | 80 MHz          | 8.55              | 8.60  | 8.75  | 8.95  | 9.35      | 9.55      | 9.65  | 9.85  | 10.5               | 11.0      | '''' \    |      |

|                                                | 48 MHz all                   | peripherals disable                                            | Range 1         | 72 MHz            | 7.70  | 7.80  | 7.90  | 8.15      | 8.50      | 8.60  | 8.70  | 8.90               | 9.25      | 9.95      |      |

|                                                |                              |                                                                |                 | 64 MHz            | 6.90  | 6.95  | 7.10  | 7.30      | 7.70      | 7.70  | 7.75  | 7.95               | 8.35      | 9.00      |      |

|                                                |                              |                                                                |                 | 48 MHz            | 5.15  | 5.20  | 5.30  | 5.55      | 5.90      | 5.75  | 5.85  | 6.05               | 6.40      | 7.05      |      |

|                                                |                              |                                                                |                 | 32 MHz            | 3.45  | 3.50  | 3.65  | 3.85      | 4.25      | 3.90  | 4.00  | 4.20               | 4.50      | 5.15      |      |

|                                                |                              |                                                                |                 | 24 MHz            | 2.65  | 2.70  | 2.80  | 3.00      | 3.40      | 3.00  | 3.05  | 3.25               | 3.55      | 4.20      |      |

|                                                |                              |                                                                |                 | 16 MHz            | 1.80  | 1.85  | 1.95  | 2.15      | 2.55      | 2.05  | 2.10  | 2.30               | 2.60      | 3.25      |      |

|                                                | IDD ALL   Current in   all i |                                                                |                 | 2 MHz             | 220   | 255   | 360   | 540       | 895       | 270   | 330   | 460                | 760       | 1400      |      |

|                                                |                              | f <sub>HCLK</sub> = f <sub>MSI</sub><br>all peripherals disabl | ۵               | 1 MHz             | 120   | 155   | 260   | 440       | 795       | 165   | 215   | 370                | 660       | 1300      | μΑ   |

| (LPRun)                                        | low-power run mode           | FLASH in power-dov                                             |                 | 400 kHz           | 60.0  | 92.0  | 195   | 375       | 730       | 100   | 160   | 330                | 585       | 1250      | μΛ   |

|                                                | Tan mode                     |                                                                |                 | 100 kHz           | 36.0  | 62.5  | 165   | 345       | 695       | 63.0  | 130   | 305                | 555       | 1200      |      |

<sup>1.</sup> Guaranteed by characterization results, unless otherwise specified.

Table 45. Current consumption in Stop 2 mode

| Symbol                                         | Parameter                                              | Conditions                                                                     |                 |       |       | TYP   |        |        |       |       | MAX <sup>(1)</sup> |        |        | Unit  |

|------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------------------------------|-----------------|-------|-------|-------|--------|--------|-------|-------|--------------------|--------|--------|-------|

| Syllibol                                       | Parameter                                              | -                                                                              | V <sub>DD</sub> | 25 °C | 55 °C | 85 °C | 105 °C | 125 °C | 25 °C | 55 °C | 85 °C              | 105 °C | 125 °C | Ullit |

|                                                |                                                        |                                                                                | 1.8 V           | 2.05  | 5.40  | 19.0  | 44.0   | 97.0   | 4.00  | 11.5  | 41.5               | 100    | 220    |       |

| I <sub>DD_ALL</sub>                            | Supply current in Stop 2 mode,                         | _                                                                              | 2.4 V           | 2.10  | 5.45  | 19.0  | 44.5   | 98.5   | 4.05  | 11.5  | 42.0               | 100    | 225    | μA    |

| (Stop 2)                                       | RTC disabled                                           |                                                                                | 3 V             | 2.05  | 5.55  | 19.5  | 45.0   | 100    | 4.10  | 12.0  | 43.0               | 105    | 230    | μπ    |

|                                                |                                                        |                                                                                | 3.6 V           | 2.05  | 5.65  | 20.0  | 46.5   | 105    | 4.20  | 12.0  | 44.0               | 105    | 235    |       |

|                                                |                                                        |                                                                                | 1.8 V           | 2.30  | 5.65  | 19.0  | 44.0   | 97.0   | 4.50  | 12.0  | 42.0               | 100    | 220    |       |

|                                                |                                                        | RTC clocked by LSI                                                             | 2.4 V           | 2.35  | 5.80  | 19.5  | 44.5   | 99.0   | 4.65  | 12.0  | 42.5               | 100    | 225    |       |

|                                                |                                                        | TATO GOOKED by LST                                                             | 3 V             | 2.50  | 5.90  | 20.0  | 45.5   | 100    | 4.90  | 12.5  | 43.5               | 105    | 230    |       |

|                                                |                                                        |                                                                                | 3.6 V           | 2.60  | 6.15  | 20.5  | 47.0   | 105    | 5.20  | 13.0  | 44.5               | 105    | 235    |       |

|                                                |                                                        |                                                                                | 1.8 V           | 2.60  | 6.05  | 21.0  | 48.0   | 97.0   | -     | -     | -                  | -      | -      |       |

| I <sub>DD_ALL</sub><br>(Stop 2 with            | Supply current in Stop 2 mode,                         | RTC clocked by LSE                                                             | 2.4 V           | 2.55  | 6.20  | 21.0  | 49.0   | 98.5   | -     | -     | -                  | -      | -      |       |

| RTC)                                           | RTC enabled                                            | bypassed at 32768 Hz                                                           | 3 V             | 2.80  | 6.35  | 21.5  | 49.5   | 100    | -     | -     | -                  | -      | -      | μA    |

| ,                                              |                                                        |                                                                                | 3.6 V           | 2.85  | 6.60  | 22.5  | 51.5   | 105    | -     | -     | -                  | -      | -      |       |

|                                                |                                                        |                                                                                | 1.8 V           | 2.40  | 5.70  | 19.0  | 44.5   | 98.0   | -     | -     | -                  | -      | -      |       |

|                                                |                                                        | RTC clocked by LSE guartz <sup>(2)</sup>                                       | 2.4 V           | 2.50  | 5.85  | 19.5  | 45.0   | 99.5   | -     | -     | -                  | -      | -      |       |

|                                                |                                                        | in low drive mode                                                              | 3 V             | 2.60  | 6.00  | 20.0  | 46.0   | 100    | -     | -     | -                  | -      | -      |       |

|                                                |                                                        |                                                                                | 3.6 V           | 2.65  | 6.25  | 20.5  | 47.0   | 105    | -     | -     | -                  | -      | -      |       |

|                                                |                                                        | Wakeup clock is<br>MSI = 48 MHz,<br>voltage Range 1.<br>See <sup>(3)</sup> .   | 3 V             | 1.85  | -     | -     | -      | -      | -     | -     | -                  | -      | -      |       |

| I <sub>DD_ALL</sub><br>(wakeup from<br>Stop 2) | Supply current<br>during wakeup<br>from Stop 2<br>mode | Wakeup clock is<br>MSI = 4 MHz,<br>voltage Range 2.<br>See <sup>(3)</sup> .    | 3 V             | 1.50  | -     | -     | -      | -      | -     | -     | -                  | -      | -      | mA    |

|                                                |                                                        | Wakeup clock is<br>HSI16 = 16 MHz,<br>voltage Range 1.<br>See <sup>(3)</sup> . | 3 V             | 1.55  | -     | -     | -      | -      | -     | -     | -                  | -      | -      |       |

<sup>1.</sup> Guaranteed based on test during characterization, unless otherwise specified.

<sup>2.</sup> Based on characterization done with a 32.768 kHz crystal (MC306-G-06Q-32.768, manufacturer JFVNY) with two 6.8 pF loading capacitors.

Electrical characteristics

3. Wakeup with code execution from Flash. Average value given for a typical wakeup time as specified in *Table 52: Low-power mode wakeup timings*.

Table 48. Current consumption in Standby mode (continued)

| Symbol                                             | Parameter                                               | Conditions                                              |                 |       |       | TYP   |        |        |       |       | MAX <sup>(1)</sup> |        |        | Unit  |

|----------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|-----------------|-------|-------|-------|--------|--------|-------|-------|--------------------|--------|--------|-------|

| Gymbol                                             | i arameter                                              | -                                                       | V <sub>DD</sub> | 25 °C | 55 °C | 85 °C | 105 °C | 125 °C | 25 °C | 55 °C | 85 °C              | 105 °C | 125 °C | _     |

|                                                    | Supply current                                          |                                                         | 1.8 V           | 250   | 730   | 2700  | 6350   | 13850  | 575   | 1800  | 6350               | 14500  | 32000  |       |

| I <sub>DD_ALL</sub><br>(SRAM2) <sup>(3)</sup>      | to be added in Standby mode                             | _                                                       | 2.4 V           | 250   | 740   | 2700  | 6150   | 14000  | 620   | 1800  | 6450               | 14500  | 32000  | nA    |

| (SRAM2) <sup>(3)</sup>                             | when SRAM2                                              |                                                         | 3 V             | 255   | 740   | 2700  | 6450   | 13500  | 645   | 1850  | 6500               | 15000  | 32500  | ] ''' |

|                                                    | is retained                                             |                                                         | 3.6 V           | 255   | 755   | 2800  | 6500   | 13500  | 790   | 1950  | 6500               | 15000  | 33000  |       |

| I <sub>DD_ALL</sub><br>(wakeup<br>from<br>Standby) | Supply current<br>during wakeup<br>from Standby<br>mode | Wakeup clock is<br>MSI = 4 MHz.<br>See <sup>(4)</sup> . | 3 V             | 2.00  | -     | -     | -      | -      | -     | -     | -                  | -      | -      | mA    |

- 1. Guaranteed by characterization results, unless otherwise specified.

- 2. Based on characterization done with a 32.768 kHz crystal (MC306-G-06Q-32.768, manufacturer JFVNY) with two 6.8 pF loading capacitors.

- 3. The supply current in Standby with SRAM2 mode is: I<sub>DD\_ALL</sub>(Standby) + I<sub>DD\_ALL</sub>(SRAM2). The supply current in Standby with RTC with SRAM2 mode is: I<sub>DD\_ALL</sub>(Standby + RTC) + I<sub>DD\_ALL</sub>(SRAM2).

- 4. Wakeup with code execution from Flash. Average value given for a typical wakeup time as specified in Table 52: Low-power mode wakeup timings.

Table 49. Current consumption in Shutdown mode

| Symbol                            | Parameter                              | Conditions |          |       |       | TYP   |        |        |       |       | MAX <sup>(1)</sup> |        |        | Unit |

|-----------------------------------|----------------------------------------|------------|----------|-------|-------|-------|--------|--------|-------|-------|--------------------|--------|--------|------|

| Symbol                            | Farameter                              | -          | $V_{DD}$ | 25 °C | 55 °C | 85 °C | 105 °C | 125 °C | 25 °C | 55 °C | 85 °C              | 105 °C | 125 °C |      |

|                                   | Supply current                         |            | 1.8 V    | 19.0  | 120   | 720   | 2200   | 6400   | 38.0  | 350   | 2050               | 6350   | 19500  |      |

|                                   | in Shutdown<br>mode                    |            | 2.4 V    | 26.0  | 145   | 855   | 2600   | 7450   | 62.0  | 400   | 2400               | 7450   | 22500  |      |

| I <sub>DD_ALL</sub><br>(Shutdown) | (backup                                | -          | 3 V      | 37.0  | 185   | 1050  | 3100   | 8700   | 105   | 500   | 2850               | 8750   | 26000  | nA   |

| (Grididowii)                      | registers<br>retained) RTC<br>disabled |            | 3.6 V    | 67.0  | 260   | 1350  | 3950   | 11000  | 160   | 650   | 3500               | 10500  | 30000  |      |

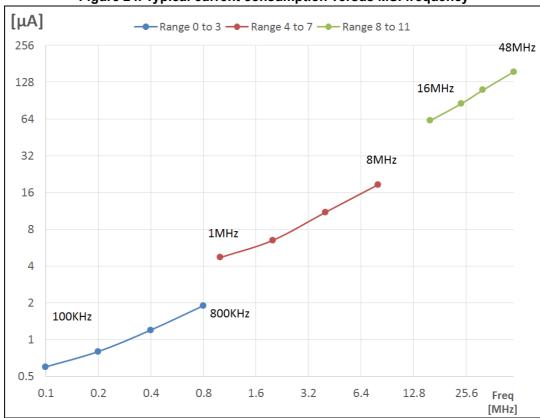

Figure 24. Typical current consumption versus MSI frequency

High-speed internal 48 MHz (HSI48) RC oscillator

Table 61. HSI48 oscillator characteristics<sup>(1)</sup>

| Symbol                   | Parameter                             | Conditions                                                           | Min               | Тур                  | Max                 | Unit |

|--------------------------|---------------------------------------|----------------------------------------------------------------------|-------------------|----------------------|---------------------|------|

| f <sub>HSI48</sub>       | HSI48 Frequency                       | V <sub>DD</sub> =3.0V, T <sub>A</sub> =30°C                          | -                 | 48                   | -                   | MHz  |

| TRIM                     | HSI48 user trimming step              | -                                                                    | -                 | 0.11 <sup>(2)</sup>  | 0.18 <sup>(2)</sup> | %    |

| USER TRIM<br>COVERAGE    | HSI48 user trimming coverage          | ±32 steps                                                            | ±3 <sup>(3)</sup> | ±3.5 <sup>(3)</sup>  | -                   | %    |

| DuCy(HSI48)              | Duty Cycle                            | -                                                                    | 45 <sup>(2)</sup> | -                    | 55 <sup>(2)</sup>   | %    |

| ACC                      | Accuracy of the HSI48 oscillator      | V <sub>DD</sub> = 3.0 V to 3.6 V,<br>T <sub>A</sub> = -15 to 85 °C   | -                 | -                    | ±3 <sup>(3)</sup>   | %    |

| ACC <sub>HSI48_REL</sub> | over temperature (factory calibrated) | V <sub>DD</sub> = 1.65 V to 3.6 V,<br>T <sub>A</sub> = -40 to 125 °C | -                 | -                    | ±4.5 <sup>(3)</sup> | 70   |

| D (HCI40)                | HSI48 oscillator frequency drift      | V <sub>DD</sub> = 3 V to 3.6 V                                       | -                 | 0.025 <sup>(3)</sup> | 0.05 <sup>(3)</sup> | %    |

| D <sub>VDD</sub> (HSI48) | with V <sub>DD</sub>                  | V <sub>DD</sub> = 1.65 V to 3.6 V                                    | -                 | 0.05 <sup>(3)</sup>  | 0.1 <sup>(3)</sup>  | 70   |

| t <sub>su</sub> (HSI48)  | HSI48 oscillator start-up time        | -                                                                    | -                 | 2.5 <sup>(2)</sup>   | 6 <sup>(2)</sup>    | μs   |

| I <sub>DD</sub> (HSI48)  | HSI48 oscillator power consumption    | -                                                                    | -                 | 340 <sup>(2)</sup>   | 380 <sup>(2)</sup>  | μA   |

Unless otherwise specified, the parameters given are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 23: General operating conditions*.

Table 73. I/O AC characteristics<sup>(1)(2)</sup>

| Speed | Symbol   | Parameter                     | Conditions                                 | Min | Max | Unit    |  |

|-------|----------|-------------------------------|--------------------------------------------|-----|-----|---------|--|

| F     | <b>-</b> | Maximum frequency             | C=50 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 5   |         |  |

|       |          |                               | C=50 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 1   | MHz     |  |

|       |          |                               | C=50 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 0.1 |         |  |

|       | Fmax     |                               | C=10 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 10  |         |  |

|       |          |                               | C=10 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 1.5 |         |  |

| 00    |          |                               | C=10 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 0.1 |         |  |

|       |          | Output rise and fall time     | C=50 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 25  |         |  |

|       |          |                               | C=50 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 52  |         |  |

|       | Tr/Tf    |                               | C=50 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 140 | ns      |  |

|       |          |                               | C=10 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 17  |         |  |

|       |          |                               | C=10 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 37  |         |  |

|       |          |                               | C=10 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 110 |         |  |

|       | Fmax     | Maximum frequency             | C=50 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 25  | MHz     |  |

|       |          |                               | C=50 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 10  |         |  |

|       |          |                               | C=50 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 1   |         |  |

|       |          |                               | C=10 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 50  |         |  |

|       |          |                               | C=10 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 15  |         |  |

| 01    |          |                               | C=10 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 1   |         |  |

| 01    |          | /Tf Output rise and fall time | C=50 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 9   | -       |  |

|       | Tr/Tf    |                               | C=50 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 16  |         |  |

|       |          |                               | C=50 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 40  |         |  |

|       |          |                               | C=10 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 4.5 | ns<br>- |  |

|       |          |                               | C=10 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 9   |         |  |

|       |          |                               | C=10 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 21  |         |  |

# 6.3.19 Digital-to-Analog converter characteristics

Table 83. DAC characteristics<sup>(1)</sup>

| Symbol                             | Parameter                                                                                                                                                                          | Co                                                                                | Min                           | Тур                | Max   | Unit                       |      |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------|--------------------|-------|----------------------------|------|

| $V_{DDA}$                          | Analog supply voltage for DAC ON                                                                                                                                                   | DAC output buffer OFF (no resistive load on DAC1_OUT1 pin or internal connection) |                               | 1.71               | -     | 3.6                        |      |

|                                    |                                                                                                                                                                                    | Other modes                                                                       |                               | 1.80               | -     |                            |      |

| V <sub>REF+</sub>                  | Positive reference voltage                                                                                                                                                         | DAC output buffer OFF (no resistive load on DAC1_OUT1 pin or internal connection) |                               | 1.71               | -     | $V_{DDA}$                  | V    |

|                                    |                                                                                                                                                                                    | Other modes                                                                       |                               | 1.80               | -     |                            |      |

| V <sub>REF-</sub>                  | Negative reference voltage                                                                                                                                                         | -                                                                                 |                               | - V <sub>SSA</sub> |       |                            |      |

| $R_{L}$                            | Resistive load                                                                                                                                                                     | DAC output                                                                        | connected to V <sub>SSA</sub> | 5                  | -     | -                          | kΩ   |

| 11                                 |                                                                                                                                                                                    | buffer ON                                                                         | connected to V <sub>DDA</sub> | 25                 | -     | -                          |      |

| R <sub>O</sub>                     | Output Impedance                                                                                                                                                                   | DAC output bu                                                                     | ffer OFF                      | 9.6                | 11.7  | 13.8                       | kΩ   |

| Ь                                  | Output impedance sample                                                                                                                                                            | V <sub>DD</sub> = 2.7 V                                                           |                               | -                  | -     | 2                          | kΩ   |

| R <sub>BON</sub>                   | and hold mode, output buffer ON                                                                                                                                                    | V <sub>DD</sub> = 2.0 V                                                           | -                             | -                  | 3.5   |                            |      |

|                                    | Output impedance sample                                                                                                                                                            | V <sub>DD</sub> = 2.7 V                                                           |                               | -                  | -     | 16.5                       | kΩ   |

| R <sub>BOFF</sub>                  | and hold mode, output buffer OFF                                                                                                                                                   | V <sub>DD</sub> = 2.0 V                                                           |                               | -                  | -     | 18.0                       |      |

| C <sub>L</sub>                     |                                                                                                                                                                                    | DAC output buffer ON                                                              |                               | -                  | -     | 50                         | pF   |

| C <sub>SH</sub>                    | Capacitive load                                                                                                                                                                    | Sample and hold mode                                                              |                               | -                  | 0.1   | 1                          | μF   |

| V <sub>DAC_OUT</sub>               | Voltage on DAC1_OUT1                                                                                                                                                               | DAC output buffer ON                                                              |                               | 0.2                | -     | V <sub>REF+</sub><br>- 0.2 | V    |

|                                    | output                                                                                                                                                                             | DAC output buffer OFF                                                             |                               | 0                  | -     | V <sub>REF+</sub>          |      |

|                                    | Settling time (full scale: for a 12-bit code transition between the lowest and the highest input codes when DAC1_OUT1 reaches final value ±0.5LSB, ±1 LSB, ±2 LSB, ±4 LSB, ±8 LSB) | Normal mode<br>DAC output<br>buffer ON<br>CL ≤ 50 pF,<br>RL ≥ 5 kΩ                | ±0.5 LSB                      | -                  | 1.7   | 3                          |      |

|                                    |                                                                                                                                                                                    |                                                                                   | ±1 LSB                        | -                  | 1.6   | 2.9                        |      |

|                                    |                                                                                                                                                                                    |                                                                                   | ±2 LSB                        | -                  | 1.55  | 2.85                       |      |

| t <sub>SETTLING</sub>              |                                                                                                                                                                                    |                                                                                   | ±4 LSB                        | -                  | 1.48  | 2.8                        | μs   |

|                                    |                                                                                                                                                                                    |                                                                                   | ±8 LSB                        | -                  | 1.4   | 2.75                       |      |

|                                    |                                                                                                                                                                                    | Normal mode DAC output buffer<br>OFF, ±1LSB, CL = 10 pF                           |                               | -                  | 2     | 2 2.5                      |      |

| t <sub>WAKEUP</sub> <sup>(2)</sup> | Wakeup time from off state<br>(setting the ENx bit in the<br>DAC Control register) until<br>final value ±1 LSB                                                                     | Normal mode DAC output buffer ON CL $\leq$ 50 pF, RL $\geq$ 5 k $\Omega$          |                               | -                  | 4.2   | 7.5                        |      |

|                                    |                                                                                                                                                                                    | Normal mode DAC output buffer<br>OFF, CL ≤ 10 pF                                  |                               | -                  | - 2 5 | 5                          | – µs |

| PSRR                               | V <sub>DDA</sub> supply rejection ratio                                                                                                                                            | Normal mode DAC output buffer ON CL ≤ 50 pF, RL = 5 kΩ, DC                        |                               | -                  | -80   | -28                        | dB   |

## 6.3.20 Voltage reference buffer characteristics

Table 85. VREFBUF characteristics<sup>(1)</sup>

| Symbol                | Parameter                                                                                       | Conditions                                       |                            | Min                      | Тур   | Max                                     | Unit    |

|-----------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------|--------------------------|-------|-----------------------------------------|---------|

| $V_{DDA}$             | Analog supply voltage                                                                           | Normal mode                                      | V <sub>RS</sub> = 0        | 2.4                      | -     | 3.6                                     | . V     |

|                       |                                                                                                 |                                                  | V <sub>RS</sub> = 1        | 2.8                      | -     | 3.6                                     |         |

|                       |                                                                                                 | Degraded mode <sup>(2)</sup>                     | V <sub>RS</sub> = 0        | 1.65                     | -     | 2.4                                     |         |

|                       |                                                                                                 |                                                  | V <sub>RS</sub> = 1        | 1.65                     | -     | 2.8                                     |         |

|                       | Voltage<br>reference                                                                            | Normal mode                                      | V <sub>RS</sub> = 0        | 2.046 <sup>(3)</sup>     | 2.048 | 2.049 <sup>(3)</sup>                    |         |

| V <sub>REFBUF</sub> _ |                                                                                                 |                                                  | V <sub>RS</sub> = 1        | 2.498 <sup>(3)</sup>     | 2.5   | 2.502 <sup>(3)</sup>                    |         |

| OUT                   | output                                                                                          | Degraded mode <sup>(2)</sup>                     | V <sub>RS</sub> = 0        | V <sub>DDA</sub> -150 mV | -     | $V_{DDA}$                               |         |

|                       |                                                                                                 | Degraded mode( )                                 | V <sub>RS</sub> = 1        | V <sub>DDA</sub> -150 mV | -     | $V_{DDA}$                               |         |

| TRIM                  | Trim step resolution                                                                            | -                                                | -                          | -                        | ±0.05 | ±0.1                                    | %       |

| CL                    | Load capacitor                                                                                  | -                                                | -                          | 0.5                      | 1     | 1.5                                     | μF      |

| esr                   | Equivalent<br>Serial Resistor<br>of Cload                                                       | -                                                | -                          | -                        | -     | 2                                       | Ω       |

| I <sub>load</sub>     | Static load current                                                                             | -                                                | -                          | -                        | -     | 4                                       | mA      |

|                       | Line regulation                                                                                 | 2.8 V ≤ V <sub>DDA</sub> ≤ 3.6 V                 | I <sub>load</sub> = 500 μA | -                        | 200   | 1000                                    | ppm/V   |

| I <sub>line_reg</sub> |                                                                                                 |                                                  | I <sub>load</sub> = 4 mA   | -                        | 100   | 500                                     |         |

| I <sub>load_reg</sub> | Load regulation                                                                                 | 500 μA ≤ I <sub>load</sub> ≤4 mA                 | Normal mode                | -                        | 50    | 500                                     | ppm/mA  |

| т                     | Temperature coefficient                                                                         | -40 °C < T <sub>J</sub> < +125 °C                | ;                          | -                        | -     | T <sub>coeff</sub> _<br>vrefint +       | ppm/ °C |

| T <sub>Coeff</sub>    |                                                                                                 | 0 °C < T <sub>J</sub> < +50 °C                   |                            | -                        | -     | T <sub>coeff</sub> _<br>vrefint +<br>50 | ррпі С  |

| PSRR                  | Power supply rejection                                                                          |                                                  |                            | 40                       | 60    | -                                       | dВ      |

| FORK                  |                                                                                                 |                                                  |                            | 25                       | 40    | -                                       | dB      |

|                       | Start-up time                                                                                   | CL = $0.5 \mu F^{(4)}$<br>CL = $1.1 \mu F^{(4)}$ |                            | -                        | 300   | 350                                     | μs      |

| t <sub>START</sub>    |                                                                                                 |                                                  |                            | -                        | 500   | 650                                     |         |

|                       |                                                                                                 | CL = 1.5 µF <sup>(4)</sup>                       |                            | -                        | 650   | 800                                     |         |

| I <sub>INRUSH</sub>   | Control of<br>maximum DC<br>current drive<br>on VREFBUF_<br>OUT during<br>start-up phase<br>(5) | -                                                | -                          | -                        | 8     | -                                       | mA      |

Table 97. QUADSPI characteristics in DDR mode<sup>(1)</sup>

| Symbol               | Parameter                             | Parameter Conditions                                                         |                        | Тур | Max                    | Unit    |

|----------------------|---------------------------------------|------------------------------------------------------------------------------|------------------------|-----|------------------------|---------|

|                      | Quad SPI clock<br>frequency           | 1.71 < V <sub>DD</sub> < 3.6 V, C <sub>LOAD</sub> = 20 pF<br>Voltage Range 1 | -                      | -   | 40                     |         |

| Fck                  |                                       | 2 < V <sub>DD</sub> < 3.6 V, C <sub>LOAD</sub> = 20 pF<br>Voltage Range 1    | -                      | -   | 48                     | N 41 1- |

| 1/t <sub>(CK)</sub>  |                                       | 1.71 < V <sub>DD</sub> < 3.6 V, C <sub>LOAD</sub> = 15 pF<br>Voltage Range 1 | -                      | -   | 48<br>26               | MHz     |

|                      |                                       | 1.71 < V <sub>DD</sub> < 3.6 V C <sub>LOAD</sub> = 20 pF<br>Voltage Range 2  | -                      | -   |                        |         |

| t <sub>w(CKH)</sub>  | Quad SPI clock high                   | f = 49 MHz proce=0                                                           | t <sub>(CK)</sub> /2-2 | -   | t <sub>(CK)</sub> /2   |         |

| t <sub>w(CKL)</sub>  | and low time                          | f <sub>AHBCLK</sub> = 48 MHz, presc=0                                        | t <sub>(CK)</sub> /2   | -   | t <sub>(CK)</sub> /2+2 |         |

|                      | Data input setup time on rising edge  | Voltage Range 1                                                              | 1                      |     | -                      | -       |

| t <sub>sr(IN)</sub>  |                                       | Voltage Range 2                                                              | 3.5                    | -   |                        |         |

|                      | Data input setup time on falling edge | Voltage Range 1                                                              | 1                      |     |                        |         |

| t <sub>sf(IN)</sub>  |                                       | Voltage Range 2                                                              | 1.5                    | -   | -                      |         |

|                      | Data input hold time on rising edge   | Voltage Range 1                                                              | 6                      |     |                        |         |

| t <sub>hr(IN)</sub>  |                                       | Voltage Range 2                                                              | 6.5                    | -   | -                      |         |

|                      | Data input hold time                  | Voltage Range 1                                                              | 5.5                    |     |                        |         |

| t <sub>hf(IN)</sub>  | on falling edge                       | Voltage Range 2                                                              | 5.5                    | _   | -                      | ns      |

| 4                    | Data output valid time                | Voltage Range 1                                                              |                        | 5   | 5.5                    |         |

| t <sub>vr(OUT)</sub> | on rising edge                        | Voltage Range 2                                                              | -                      | 9.5 | 14                     | †       |

|                      | Data output valid time                | Voltage Range 1                                                              |                        | 5   | 8.5                    |         |

| t <sub>vf(OUT)</sub> | on falling edge                       | Voltage Range 2                                                              | -                      | 15  | 19                     | Í       |

| 4                    | Data output hold time on rising edge  | Voltage Range 1                                                              | 3.5                    | -   |                        |         |

| t <sub>hr(OUT)</sub> |                                       | Voltage Range 2                                                              | 8                      | -   | -                      |         |

| +                    | Data output hold time                 | Voltage Range 1                                                              | 3.5                    | -   |                        |         |

| t <sub>hf(OUT)</sub> | on falling edge                       | Voltage Range 2                                                              | 13                     | -   |                        |         |

<sup>1.</sup> Guaranteed by characterization results.

182/212

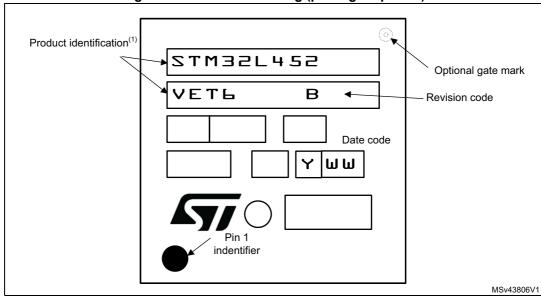

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Figure 43. LQFP100 marking (package top view)

Parts marked as ES or E or accompanied by an Engineering Sample notification letter are not yet qualified

and therefore not approved for use in production. ST is not responsible for any consequences resulting

from such use. In no event will ST be liable for the customer using any of these engineering samples in

production. ST's Quality department must be contacted prior to any decision to use these engineering

samples to run a qualification activity.

DS11912 Rev 4 191/212

STM32L452xx Package information

Table 103. UFBGA100 - 100-ball, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ball grid array package mechanical data (continued)

|        |      | !!!:        |       |      | inches <sup>(1)</sup> |        |

|--------|------|-------------|-------|------|-----------------------|--------|

| Symbol |      | millimeters |       |      | inches                |        |

| Symbol | Min. | Тур.        | Max.  | Min. | Тур.                  | Max.   |

| ddd    | -    | -           | 0.080 | -    | -                     | 0.0031 |

| eee    | -    | -           | 0.150 | -    | -                     | 0.0059 |

| fff    | -    | -           | 0.050 | -    | -                     | 0.0020 |

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

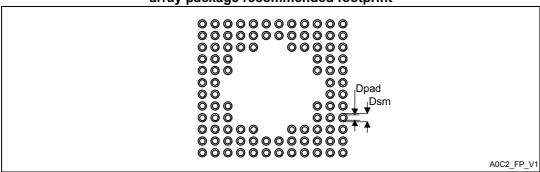

Figure 45. UFBGA100 - 100-ball, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ball grid array package recommended footprint

Table 104. UFBGA100 recommended PCB design rules (0.5 mm pitch BGA)

| Dimension         | Recommended values                                                |  |  |

|-------------------|-------------------------------------------------------------------|--|--|

| Pitch             | 0.5                                                               |  |  |

| Dpad              | 0.280 mm                                                          |  |  |

| Dsm               | 0.370 mm typ. (depends on the solder mask registration tolerance) |  |  |

| Stencil opening   | 0.280 mm                                                          |  |  |

| Stencil thickness | Between 0.100 mm and 0.125 mm                                     |  |  |

#### **Device marking**

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.