Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M4                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 80MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QSPI, SAI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, PWM, WDT                                   |

| Number of I/O              | 38                                                                      |

| Program Memory Size        | 512KB (512K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 160K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                            |

| Data Converters            | A/D 10x12b; D/A 1x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 48-UFQFN Exposed Pad                                                    |

| Supplier Device Package    | 48-UFQFPN (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l452ceu3   |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 3.17  | Voltage reference buffer (VREFBUF) 4                                | 1 |

|-------|---------------------------------------------------------------------|---|

| 3.18  | Comparators (COMP) 4                                                | 2 |

| 3.19  | Operational amplifier (OPAMP) 4                                     | 2 |

| 3.20  | Touch sensing controller (TSC) 4                                    | 2 |

| 3.21  | Digital filter for Sigma-Delta Modulators (DFSDM) 4                 | 3 |

| 3.22  | Random number generator (RNG) 4                                     | 5 |

| 3.23  | Timers and watchdogs 4                                              | 5 |

|       | 3.23.1 Advanced-control timer (TIM1)4                               | 6 |

|       | 3.23.2 General-purpose timers (TIM2, TIM3, TIM15, TIM16)4           | 6 |

|       | 3.23.3 Basic timer (TIM6) 4                                         | 6 |

|       | 3.23.4 Low-power timer (LPTIM1 and LPTIM2)4                         | 7 |

|       | 3.23.5 Infrared interface (IRTIM)                                   |   |

|       | 3.23.6 Independent watchdog (IWDG) 4                                |   |

|       | 3.23.7 System window watchdog (WWDG)                                |   |

|       | 3.23.8 SysTick timer                                                |   |

| 3.24  | Real-time clock (RTC) and backup registers                          |   |

| 3.25  | Inter-integrated circuit interface (I <sup>2</sup> C) 4             |   |

| 3.26  | Universal synchronous/asynchronous receiver transmitter (USART) 5   | 0 |

| 3.27  | Low-power universal asynchronous receiver transmitter (LPUART) 5    | 1 |

| 3.28  | Serial peripheral interface (SPI) 5                                 | 2 |

| 3.29  | Serial audio interfaces (SAI) 5                                     | 2 |

| 3.30  | Controller area network (CAN) 5                                     | 3 |

| 3.31  | Secure digital input/output and MultiMediaCards Interface (SDMMC) 5 | 3 |

| 3.32  | Universal serial bus (USB)                                          | 4 |

| 3.33  | Clock recovery system (CRS)                                         | 4 |

| 3.34  | Quad SPI memory interface (QUADSPI)                                 | 4 |

| 3.35  | Development support                                                 | 6 |

|       | 3.35.1 Serial wire JTAG debug port (SWJ-DP)                         | 6 |

|       | 3.35.2 Embedded Trace Macrocell <sup>™</sup> 5                      | 6 |

| Pinou | uts and pin description5                                            | 7 |

| Memo  | ory mapping                                                         | 4 |

| Elect | rical characteristics8                                              | 8 |

4

5

6

| Peripheral            | STM32L452Vx         | STM32L452Rx                                                                                                           | STM32L452Cx |  |  |  |  |  |  |

|-----------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|--|--|--|

| Operating voltage     |                     | 1.71 to 3.6 V                                                                                                         |             |  |  |  |  |  |  |

| Operating temperature |                     | nbient operating temperature:<br>40 to 85 °C / -40 to 125 °C<br>Junction temperature:<br>40 to 105 °C / -40 to 130 °C |             |  |  |  |  |  |  |

| Packages              | LQFP100<br>UFBGA100 | WLCSP64<br>LQFP64<br>UFBGA64                                                                                          | UFQFPN48    |  |  |  |  |  |  |

#### Table 2. STM32L452xx family device features and peripheral counts (continued)

1. WKUP5, ADC1\_IN14 and SDMMC interface are not supported by 64-pin packages with SMPS option.

2. In case external SMPS package type is used, 2 GPIO's are replaced by VDD12 pins to connect the SMPS power supplies hence reducing the number of available GPIO's by 2.

# 3 Functional overview

# 3.1 Arm<sup>®</sup> Cortex<sup>®</sup>-M4 core with FPU

The Arm<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU processor is the latest generation of Arm<sup>®</sup> processors for embedded systems. It was developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced response to interrupts.

The Arm<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU 32-bit RISC processor features exceptional codeefficiency, delivering the high-performance expected from an Arm<sup>®</sup> core in the memory size usually associated with 8- and 16-bit devices.

The processor supports a set of DSP instructions which allow efficient signal processing and complex algorithm execution.

Its single precision FPU speeds up software development by using metalanguage development tools, while avoiding saturation.

With its embedded  ${\rm Arm}^{\rm @}$  core, the STM32L452xx family is compatible with all  ${\rm Arm}^{\rm @}$  tools and software.

*Figure 1* shows the general block diagram of the STM32L452xx family devices.

## 3.2 Adaptive real-time memory accelerator (ART Accelerator<sup>™</sup>)

The ART Accelerator<sup>™</sup> is a memory accelerator which is optimized for STM32 industrystandard Arm<sup>®</sup> Cortex<sup>®</sup>-M4 processors. It balances the inherent performance advantage of the Arm<sup>®</sup> Cortex<sup>®</sup>-M4 over Flash memory technologies, which normally requires the processor to wait for the Flash memory at higher frequencies.

To release the processor near 100 DMIPS performance at 80MHz, the accelerator implements an instruction prefetch queue and branch cache, which increases program execution speed from the 64-bit Flash memory. Based on CoreMark benchmark, the performance achieved thanks to the ART accelerator is equivalent to 0 wait state program execution from Flash memory at a CPU frequency up to 80 MHz.

# 3.3 Memory protection unit

The memory protection unit (MPU) is used to manage the CPU accesses to memory to prevent one task to accidentally corrupt the memory or resources used by any other active task. This memory area is organized into up to 8 protected areas that can in turn be divided up into 8 subareas. The protection area sizes are between 32 bytes and the whole 4 gigabytes of addressable memory.

The MPU is especially helpful for applications where some critical or certified code has to be protected against the misbehavior of other tasks. It is usually managed by an RTOS (real-time operating system). If a program accesses a memory location that is prohibited by the MPU, the RTOS can detect it and take action. In an RTOS environment, the kernel can dynamically update the MPU area setting, based on the process to be executed.

The MPU is optional and can be bypassed for applications that do not need it.

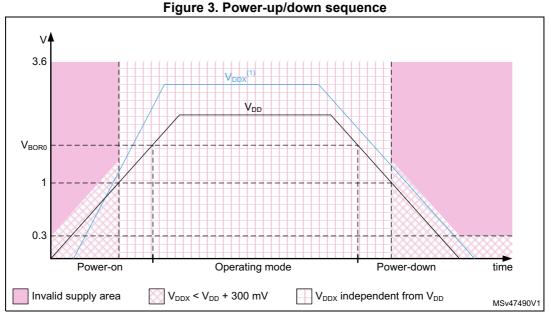

1.  $V_{DDX}$  refers to  $V_{DDA}$ .

## 3.9.2 Power supply supervisor

The device has an integrated ultra-low-power brown-out reset (BOR) active in all modes except Shutdown and ensuring proper operation after power-on and during power down. The device remains in reset mode when the monitored supply voltage  $V_{DD}$  is below a specified threshold, without the need for an external reset circuit.

The lowest BOR level is 1.71V at power on, and other higher thresholds can be selected through option bytes. The device features an embedded programmable voltage detector (PVD) that monitors the V<sub>DD</sub> power supply and compares it to the VPVD threshold. An interrupt can be generated when V<sub>DD</sub> drops below the VPVD threshold and/or when V<sub>DD</sub> is higher than the VPVD threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

In addition, the device embeds a Peripheral Voltage Monitor which compares the independent supply voltage  $V_{DDA}$  with a fixed threshold in order to ensure that the peripheral is in its functional supply range.

|                      |                                                 |   |   |                   | Stop | o 0/1             | Sto | op 2              | Star | ndby              | Shut | down              |   |

|----------------------|-------------------------------------------------|---|---|-------------------|------|-------------------|-----|-------------------|------|-------------------|------|-------------------|---|

| Peripheral           | Run Sleep Low- Low-<br>power power<br>run sleep |   | - | Wakeup capability | -    | Wakeup capability | -   | Wakeup capability | -    | Wakeup capability | VBAT |                   |   |

| CRC calculation unit | 0                                               | 0 | 0 | 0                 | -    | -                 | -   | -                 | -    | -                 | -    | -                 | - |

| GPIOs                | 0                                               | 0 | 0 | 0                 | 0    | 0                 | 0   | 0                 | (9)  | 5<br>pins<br>(10) | (11) | 5<br>pins<br>(10) | - |

Table 5. Functionalities depending on the working mode<sup>(1)</sup> (continued)

1. Legend: Y = Yes (Enable). O = Optional (Disable by default. Can be enabled by software). - = Not available.

- 2. The Flash can be configured in power-down mode. By default, it is not in power-down mode.

- 3. The SRAM clock can be gated on or off.

- 4. SRAM2 content is preserved when the bit RRS is set in PWR\_CR3 register.

- Some peripherals with wakeup from Stop capability can request HSI16 to be enabled. In this case, HSI16 is woken up by the peripheral, and only feeds the peripheral which requested it. HSI16 is automatically put off when the peripheral does not need it anymore.

- 6. UART and LPUART reception is functional in Stop mode, and generates a wakeup interrupt on Start, address match or received frame event.

- 7. I2C address detection is functional in Stop mode, and generates a wakeup interrupt in case of address match.

- 8. Voltage scaling Range 1 only.

- 9. I/Os can be configured with internal pull-up, pull-down or floating in Standby mode.

- 10. The I/Os with wakeup from Standby/Shutdown capability are: PA0, PC13, PE6, PA2, PC5.

- 11. I/Os can be configured with internal pull-up, pull-down or floating in Shutdown mode but the configuration is lost when exiting the Shutdown mode.

### 3.9.5 Reset mode

In order to improve the consumption under reset, the I/Os state under and after reset is "analog state" (the I/O schmitt trigger is disable). In addition, the internal reset pull-up is deactivated when the reset source is internal.

### 3.9.6 VBAT operation

The VBAT pin allows to power the device VBAT domain from an external battery, an external supercapacitor, or from  $V_{DD}$  when no external battery and an external supercapacitor are present. The VBAT pin supplies the RTC with LSE and the backup registers. Three anti-tamper detection pins are available in VBAT mode.

VBAT operation is automatically activated when  $V_{DD}$  is not present.

An internal VBAT battery charging circuit is embedded and can be activated when  $\mathsf{V}_{\mathsf{DD}}$  is present.

*Note:* When the microcontroller is supplied from VBAT, external interrupts and RTC alarm/events do not exit it from VBAT operation.

# 3.35 Development support

## 3.35.1 Serial wire JTAG debug port (SWJ-DP)

The Arm<sup>®</sup> SWJ-DP interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target.

Debug is performed using 2 pins only instead of 5 required by the JTAG (JTAG pins could be re-use as GPIO with alternate function): the JTAG TMS and TCK pins are shared with SWDIO and SWCLK, respectively, and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

## 3.35.2 Embedded Trace Macrocell™

The Arm<sup>®</sup> Embedded Trace Macrocell<sup>™</sup> provides a greater visibility of the instruction and data flow inside the CPU core by streaming compressed data at a very high rate from the STM32L452xx through a small number of ETM pins to an external hardware trace port analyzer (TPA) device. Real-time instruction and data flow activity be recorded and then formatted for display on the host computer that runs the debugger software. TPA hardware is commercially available from common development tool vendors.

The Embedded Trace Macrocell<sup>™</sup> operates with third party debugger software tools.

| Na        | me                   | Abbreviation                                                                                  | Definition                                                                 |  |  |  |  |  |  |

|-----------|----------------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--|--|--|--|--|--|

| Pin ı     | name                 | Unless otherwise specified in reset is the same as the actu                                   | brackets below the pin name, the pin function during and after al pin name |  |  |  |  |  |  |

|           |                      | S Supply pin                                                                                  |                                                                            |  |  |  |  |  |  |

| Pin       | type                 | I                                                                                             | Input only pin                                                             |  |  |  |  |  |  |

|           |                      | I/O                                                                                           | Input / output pin                                                         |  |  |  |  |  |  |

|           |                      | FT                                                                                            | 5 V tolerant I/O                                                           |  |  |  |  |  |  |

|           |                      | TT 3.6 V tolerant I/O                                                                         |                                                                            |  |  |  |  |  |  |

|           |                      | RST Bidirectional reset pin with embedded weak pull-up resist                                 |                                                                            |  |  |  |  |  |  |

| I/O sti   | ructure              | Option for TT or FT I/Os                                                                      |                                                                            |  |  |  |  |  |  |

|           |                      | _f <sup>(1)</sup> I/O, Fm+ capable                                                            |                                                                            |  |  |  |  |  |  |

|           |                      | _u <sup>(2)</sup>                                                                             | I/O, with USB function supplied by V <sub>DDUSB</sub>                      |  |  |  |  |  |  |

|           |                      | _a <sup>(3)</sup>                                                                             | I/O, with Analog switch function supplied by V <sub>DDA</sub>              |  |  |  |  |  |  |

| No        | otes                 | Unless otherwise specified by a note, all I/Os are set as analog inputs during and after rese |                                                                            |  |  |  |  |  |  |

| Pin       | Alternate functions  | Functions selected through C                                                                  | GPIOx_AFR registers                                                        |  |  |  |  |  |  |

| functions | Additional functions | Functions directly selected/enabled through peripheral registers                              |                                                                            |  |  |  |  |  |  |

| Table 15. Legend/abbreviations used in the pinout tab |

|-------------------------------------------------------|

|-------------------------------------------------------|

1. The related I/O structures in *Table 16* are: FT\_f, FT\_fa.

2. The related I/O structures in *Table 16* are: FT\_u, FT\_fu.

3. The related I/O structures in *Table 16* are: FT\_a, FT\_fa, TT\_a.

|                 |         | Piı    | n Nu        | ımbe    | er      |          |                                          |          |               |       | Pin fund                                                                   | ctions               |

|-----------------|---------|--------|-------------|---------|---------|----------|------------------------------------------|----------|---------------|-------|----------------------------------------------------------------------------|----------------------|

| <b>UFQFPN48</b> | WLCSP64 | LQFP64 | LQFP64 SMPS | UFBGA64 | LQFP100 | UFBGA100 | Pin name<br>(function<br>after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                        | Additional functions |

| -               | -       | -      | -           | -       | 1       | B2       | PE2                                      | I/O      | FT            | -     | TRACECK, TIM3_ETR,<br>TSC_G7_IO1,<br>SAI1_MCLK_A,<br>EVENTOUT              | -                    |

| -               | -       | -      | -           | -       | 2       | A1       | PE3                                      | I/O      | FT            | -     | TRACED0, TIM3_CH1,<br>TSC_G7_IO2,<br>SAI1_SD_B, EVENTOUT                   | -                    |

| -               | -       | -      | -           | -       | 3       | B1       | PE4                                      | I/O      | FT            | -     | TRACED1, TIM3_CH2,<br>DFSDM1_DATIN3,<br>TSC_G7_IO3,<br>SAI1_FS_A, EVENTOUT | -                    |

|                 |         | Piı    | n Nu        | ımbe    | r       |          |                                          |          | -             |       | Pin functions                                                                                                                |                      |  |  |

|-----------------|---------|--------|-------------|---------|---------|----------|------------------------------------------|----------|---------------|-------|------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|

| <b>UFQFPN48</b> | WLCSP64 | LQFP64 | LQFP64 SMPS | UFBGA64 | LQFP100 | UFBGA100 | Pin name<br>(function<br>after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                                          | Additional functions |  |  |

| -               | B2      | -      | -           | -       | 75      | G11      | VDD                                      | S        | -             | -     | -                                                                                                                            | -                    |  |  |

| 37              | C3      | 49     | 49          | A7      | 76      | A10      | PA14<br>(JTCK/<br>SWCLK)                 | I/O      | FT            | (3)   | JTCK/SWCLK,<br>LPTIM1_OUT,<br>I2C1_SMBA,<br>I2C4_SMBA,<br>SAI1_FS_B, EVENTOUT                                                | -                    |  |  |

| 38              | A2      | 50     | 50          | A6      | 77      | A9       | PA15<br>(JTDI)                           | I/O      | FT            | (3)   | JTDI, TIM2_CH1,<br>TIM2_ETR, USART2_RX,<br>SPI1_NSS, SPI3_NSS,<br>USART3_RTS_DE,<br>UART4_RTS_DE,<br>TSC_G3_IO1,<br>EVENTOUT | -                    |  |  |

| -               | D4      | 51     | 51          | B7      | 78      | B11      | PC10                                     | I/O      | FT            | -     | TRACED1, SPI3_SCK,<br>USART3_TX,<br>UART4_TX,<br>TSC_G3_IO2,<br>SDMMC1_D2,<br>EVENTOUT                                       | -                    |  |  |

| -               | В3      | 52     | 52          | B6      | 79      | C10      | PC11                                     | I/O      | FT            | -     | SPI3_MISO,<br>USART3_RX,<br>UART4_RX,<br>TSC_G3_IO3,<br>SDMMC1_D3,<br>EVENTOUT                                               | -                    |  |  |

| -               | A3      | 53     | 53          | C5      | 80      | B10      | PC12                                     | I/O      | FT            | -     | TRACED3, SPI3_MOSI,<br>USART3_CK,<br>TSC_G3_IO4,<br>SDMMC1_CK,<br>EVENTOUT                                                   | -                    |  |  |

| -               | -       | -      | -           | -       | 81      | C9       | PD0                                      | I/O      | FT            | -     | SPI2_NSS, CAN1_RX,<br>EVENTOUT                                                                                               | -                    |  |  |

| -               | -       | -      | -           | -       | 82      | B9       | PD1                                      | I/O      | FT            | -     | SPI2_SCK, CAN1_TX,<br>EVENTOUT                                                                                               | -                    |  |  |

| -               | C4      | 54     | _           | B5      | 83      | C8       | PD2                                      | I/O      | FT            | -     | TRACED2, TIM3_ETR,<br>USART3_RTS_DE,<br>TSC_SYNC,<br>SDMMC1_CMD,<br>EVENTOUT                                                 | -                    |  |  |

Table 16. STM32L452xx pin definitions (continued)

| Symbol                                | Parameter                                         | Conditions <sup>(1)</sup> | Min  | Тур  | Max  | Unit |

|---------------------------------------|---------------------------------------------------|---------------------------|------|------|------|------|

| V                                     | V <sub>DDA</sub> peripheral voltage               | Rising edge               | 1.78 | 1.82 | 1.86 | V    |

| V <sub>PVM4</sub>                     | monitoring                                        | Falling edge              | 1.77 | 1.81 | 1.85 | v    |

| V <sub>hyst_PVM3</sub>                | PVM3 hysteresis                                   | -                         | -    | 10   | -    | mV   |

| V <sub>hyst_PVM4</sub>                | PVM4 hysteresis                                   | -                         | -    | 10   | -    | mV   |

| I <sub>DD</sub> (PVM1)<br>(2)         | PVM1 consumption from $V_{DD}$                    | -                         | -    | 0.2  | -    | μA   |

| I <sub>DD</sub><br>(PVM3/PVM4)<br>(2) | PVM3 and PVM4<br>consumption from V <sub>DD</sub> | -                         | -    | 2    | -    | μA   |

Table 25. Embedded reset and power control block characteristics (continued)

1. Continuous mode means Run/Sleep modes, or temperature sensor enable in Low-power run/Low-power sleep modes.

2. Guaranteed by design.

3. BOR0 is enabled in all modes (except shutdown) and its consumption is therefore included in the supply current characteristics tables.

| Symbol                                          | Parameter                                                | Conditions                                              |                 |       | TYP   |       |        | MAX <sup>(1)</sup> |       |       |       |        | Uni    |    |

|-------------------------------------------------|----------------------------------------------------------|---------------------------------------------------------|-----------------|-------|-------|-------|--------|--------------------|-------|-------|-------|--------|--------|----|

| Symbol                                          | Farameter                                                | -                                                       | V <sub>DD</sub> | 25 °C | 55 °C | 85 °C | 105 °C | 125 °C             | 25 °C | 55 °C | 85 °C | 105 °C | 125 °C |    |

|                                                 |                                                          |                                                         | 1.8 V           | 165   | 275   | 950   | 2600   | 6550               | -     | -     | -     | -      | -      |    |

|                                                 | Supply current                                           | RTC clocked by LSE                                      | 2.4 V           | 235   | 370   | 1150  | 3100   | 7650               | -     | -     | -     | -      | -      |    |

|                                                 | in Shutdown<br>mode                                      | h bypassed at 32768 Hz                                  | 3 V             | 325   | 485   | 1450  | 3750   | 9050               | -     | -     | -     | -      | -      |    |

| I <sub>DD_ALL</sub>                             |                                                          |                                                         | 3.6 V           | 445   | 655   | 1900  | 4800   | 11500              | -     | -     | -     | -      | -      | nA |

| (Shutdown with RTC)                             | (backup<br>registers                                     |                                                         | 1.8 V           | 290   | 410   | 1050  | 2550   | 6700               | -     | -     | -     | -      | -      |    |

| ,                                               | retained) RTC                                            |                                                         | 2.4 V           | 375   | 515   | 1250  | 3050   | 7800               | -     | -     | -     | -      | -      |    |

|                                                 | enabled                                                  |                                                         | 3 V             | 480   | 645   | 1550  | 3700   | 8800               | -     | -     | -     | -      | -      |    |

|                                                 |                                                          |                                                         | 3.6 V           | 625   | 840   | 1950  | 4950   | 11500              | -     | -     | -     | -      | -      |    |

| I <sub>DD_ALL</sub><br>wakeup from<br>Shutdown) | Supply current<br>during wakeup<br>from Shutdown<br>mode | Wakeup clock is<br>MSI = 4 MHz.<br>See <sup>(3)</sup> . | 3 V             | 1.00  | -     | -     | -      | -                  | -     | _     | -     | -      | -      | mA |

1. Guaranteed by characterization results, unless otherwise specified.

2. Based on characterization done with a 32.768 kHz crystal (MC306-G-06Q-32.768, manufacturer JFVNY) with two 6.8 pF loading capacitors.

3. Wakeup with code execution from Flash. Average value given for a typical wakeup time as specified in Table 52: Low-power mode wakeup timings.

| Symbol                                                      | Parameter                       | Conditions     | ТҮР              |       |       | MAX <sup>(1)</sup> |        |        |       | Unit  |       |        |        |      |

|-------------------------------------------------------------|---------------------------------|----------------|------------------|-------|-------|--------------------|--------|--------|-------|-------|-------|--------|--------|------|

|                                                             | Farameter                       | -              | V <sub>BAT</sub> | 25 °C | 55 °C | 85 °C              | 105 °C | 125 °C | 25 °C | 55 °C | 85 °C | 105 °C | 125 °C | Unit |

| I <sub>DD_VBAT</sub> Backup domain<br>(VBAT) supply current |                                 | 1.8 V          | 3.00             | -     | -     | -                  | -      | -      | -     | -     | -     | -      |        |      |

|                                                             | Backup domain<br>supply current | RTC disabled   | 2.4 V            | 4.00  | -     | -                  | -      | -      | -     | -     | -     | -      | -      |      |

|                                                             |                                 |                | 3 V              | 5.00  | -     | -                  | -      | -      | -     | -     | -     | -      | -      |      |

|                                                             |                                 |                | 3.6 V            | 11.0  | -     | -                  | -      | -      | -     | -     | -     | -      | -      | nA   |

|                                                             |                                 |                | 1.8 V            | 145   | 165   | 285                | 550    | -      | -     | -     | -     | -      | -      |      |

|                                                             |                                 | clocked by LSE | 2.4 V            | 205   | 235   | 370                | 670    | -      | -     | -     | -     | -      | -      |      |

|                                                             |                                 |                | 3 V              | 285   | 315   | 470                | 820    | -      | -     | -     | -     | -      | -      |      |

|                                                             |                                 |                | 3.6 V            | 375   | 430   | 715                | 1350   | -      | -     | -     | -     | -      | -      |      |

1. Guaranteed by characterization results, unless otherwise specified.

DS11912 Rev 4

|      | Peripheral                      | Range 1 | Range 2 | Low-power run<br>and sleep | Unit   |

|------|---------------------------------|---------|---------|----------------------------|--------|

|      | AHB to APB2 <sup>(4)</sup>      | 1.0     | 0.9     | 0.9                        |        |

| APB2 | FW                              | 0.2     | 0.2     | 0.2                        |        |

|      | SAI1 independent clock domain   | 2.3     | 1.8     | 1.9                        |        |

|      | SAI1 clock domain               | 2.1     | 1.8     | 2.0                        |        |

|      | SDMMC1 independent clock domain | 4.7     | 3.9     | 3.9                        |        |

|      | SDMMC1 clock domain             | 2.5     | 1.9     | 1.9                        |        |

|      | SPI1                            | 1.8     | 1.6     | 1.7                        |        |

| APDZ | SYSCFG/VREFBUF/COMP             | 0.6     | 0.5     | 0.6                        | µA/MHz |

|      | TIM1                            | 8.1     | 6.5     | 7.6                        |        |

|      | TIM15                           | 3.7     | 3.0     | 3.4                        |        |

|      | TIM16                           | 2.7     | 2.1     | 2.6                        |        |

|      | USART1 independent clock domain | 4.8     | 4.2     | 4.6                        |        |

|      | USART1 clock domain             | 1.5     | 1.3     | 1.7                        |        |

|      | All APB2 on                     | 24.2    | 19.9    | 22.6                       |        |

|      | ALL                             | 100.9   | 77.1    | 94.8                       |        |

Table 51. Peripheral current consumption (continued)

1. The BusMatrix is automatically active when at least one master is ON (CPU, DMA).

2. The GPIOx (x= A...H) dynamic current consumption is approximately divided by a factor two versus this table values when the GPIO port is locked thanks to LCKK and LCKy bits in the GPIOx\_LCKR register. In order to save the full GPIOx current consumption, the GPIOx clock should be disabled in the RCC when all port I/Os are used in alternate function or analog mode (clock is only required to read or write into GPIO registers, and is not used in AF or analog modes).

3. The AHB to APB1 Bridge is automatically active when at least one peripheral is ON on the APB1.

4. The AHB to APB2 Bridge is automatically active when at least one peripheral is ON on the APB2.

# 6.3.6 Wakeup time from low-power modes and voltage scaling transition times

The wakeup times given in *Table 52* are the latency between the event and the execution of the first user instruction.

The device goes in low-power mode after the WFE (Wait For Event) instruction.

| Symbol               | Parameter                                                           | Conditions                                                                                                                      | Тур | Мах | Unit          |

|----------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----|-----|---------------|

| t <sub>WUSLEEP</sub> | Wakeup time from Sleep mode to Run mode                             | -                                                                                                                               | 6   | 6   | Nb of         |

| twulpsleep           | Wakeup time from Low-<br>power sleep mode to Low-<br>power run mode | Wakeup in Flash with Flash in power-down<br>during low-power sleep mode (SLEEP_PD=1<br>in FLASH_ACR) and with clock MSI = 2 MHz | 6   | 9   | CPU<br>cycles |

#### Table 52. Low-power mode wakeup timings<sup>(1)</sup>

## 6.3.7 External clock source characteristics

## High-speed external user clock generated from an external source

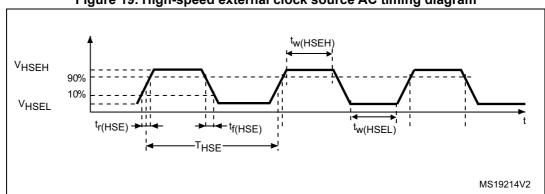

In bypass mode the HSE oscillator is switched off and the input pin is a standard GPIO.

The external clock signal has to respect the I/O characteristics in *Section 6.3.14*. However, the recommended clock input waveform is shown in *Figure 19: High-speed external clock source AC timing diagram*.

| Symbol                                       | Parameter                            | Conditions                 | Min                    | Тур | Max                    | Unit |

|----------------------------------------------|--------------------------------------|----------------------------|------------------------|-----|------------------------|------|

| f                                            | User external clock source frequency | Voltage scaling<br>Range 1 | -                      | 8   | 48                     | MHz  |

| f <sub>HSE_ext</sub>                         |                                      | Voltage scaling<br>Range 2 | -                      | 8   | 26                     |      |

| V <sub>HSEH</sub>                            | OSC_IN input pin high level voltage  | -                          | $0.7 V_{\text{DDIOx}}$ | -   | V <sub>DDIOx</sub>     | V    |

| V <sub>HSEL</sub>                            | OSC_IN input pin low level voltage   | -                          | V <sub>SS</sub>        | -   | 0.3 V <sub>DDIOx</sub> |      |

| t <sub>w(HSEH)</sub><br>t <sub>w(HSEL)</sub> | OSC_IN high or low time              | Voltage scaling<br>Range 1 | 7                      | -   | -                      | 2    |

|                                              |                                      | Voltage scaling<br>Range 2 | 18                     | -   | -                      | ns   |

| Table 55. High-speed | l external use | r clock charac | cteristics <sup>(1)</sup> |

|----------------------|----------------|----------------|---------------------------|

|----------------------|----------------|----------------|---------------------------|

1. Guaranteed by design.

Figure 19. High-speed external clock source AC timing diagram

## 6.3.9 PLL characteristics

The parameters given in *Table 63* are derived from tests performed under temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 23: General operating conditions*.

| Symbol                 | Parameter                               | Conditions                   | Min    | Тур | Max   | Unit |  |

|------------------------|-----------------------------------------|------------------------------|--------|-----|-------|------|--|

| £                      | PLL input clock <sup>(2)</sup>          | -                            | 4      | -   | 16    | MHz  |  |

| f <sub>PLL_IN</sub>    | PLL input clock duty cycle -            |                              | 45     | -   | 55    | %    |  |

| £                      | DLL multiplier output clock D           | Voltage scaling Range 1      | 3.0968 | -   | 80    | MHz  |  |

| <sup>f</sup> PLL_P_OUT | PLL multiplier output clock P           | Voltage scaling Range 2      | 3.0968 | -   | 26    |      |  |

| f <sub>PLL_Q_OUT</sub> | DLL multiplier output clock O           | Voltage scaling Range 1      | 12     | -   | 80    | MHz  |  |

|                        | PLL multiplier output clock Q           | Voltage scaling Range 2      | 12     | -   | 26    |      |  |

| f <sub>PLL_R_OUT</sub> | DLL multiplier output clock D           | Voltage scaling Range 1      | 12     | -   | 80    | MHz  |  |

|                        | PLL multiplier output clock R           | Voltage scaling Range 2      | 12     | -   | 26    |      |  |

| 4                      |                                         | Voltage scaling Range 1 96 - |        | -   | 344   | MHz  |  |

| fvco_out               | PLL VCO output                          | Voltage scaling Range 2      | 96     | -   | 128   |      |  |

| t <sub>LOCK</sub>      | PLL lock time                           | -                            | -      | 15  | 40    | μs   |  |

| Jitter                 | RMS cycle-to-cycle jitter               | Svetom clock 20 Miliz        | -      | 40  | -     | 100  |  |

| Jiller                 | RMS period jitter                       | System clock 80 MHz          | -      | 30  | - ±p: | ±ρs  |  |

|                        |                                         | VCO freq = 96 MHz            | -      | 200 | 260   |      |  |

| I <sub>DD</sub> (PLL)  | PLL power consumption on $V_{DD}^{(1)}$ | VCO freq = 192 MHz           | -      | 300 | 380   | 0 μΑ |  |

|                        |                                         | VCO freq = 344 MHz           | -      | 520 | 650   |      |  |

|  | Table 63. | PLL, | PLLSAI1 | characteristics <sup>(1)</sup> |

|--|-----------|------|---------|--------------------------------|

|--|-----------|------|---------|--------------------------------|

1. Guaranteed by design.

2. Take care of using the appropriate division factor M to obtain the specified PLL input clock values. The M factor is shared between the 2 PLLs.

#### **Electrical characteristics**

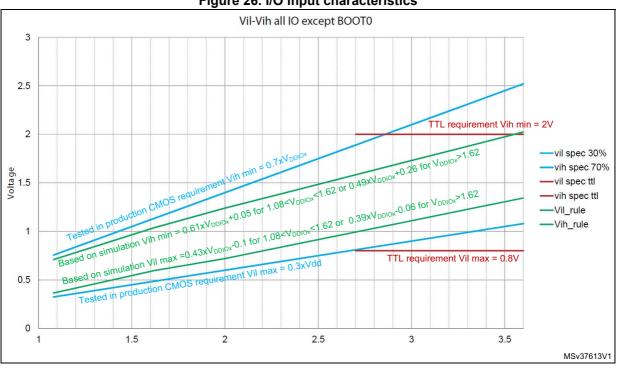

- 1. Refer to Figure 26: I/O input characteristics.

- 2. Tested in production.

- 3. Guaranteed by design.

- 4. All FT\_xx IO except FT\_u and PC3 I/O.

- 5.  $Max(V_{DDXXX})$  is the maximum value of all the I/O supplies.

- To sustain a voltage higher than Min(V<sub>DD</sub>, V<sub>DDA</sub>, V<sub>DDUSB</sub>) +0.3 V, the internal Pull-up and Pull-Down resistors must be disabled.

- 7. This value represents the pad leakage of the IO itself. The total product pad leakage is provided by this formula:  $I_{Total\_Ileak\_max} = 10 \ \mu A + [number of IOs where V_{IN} is applied on the pad] \times I_{Ikg}(Max).$

- Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This PMOS/NMOS contribution to the series resistance is minimal (~10% order).

All I/Os are CMOS- and TTL-compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements is shown in *Figure 26* for standard I/Os, and in *Figure 26* for 5 V tolerant I/Os.

Figure 26. I/O input characteristics

### Output driving current

The GPIOs (general purpose input/outputs) can sink or source up to ±8 mA, and sink or source up to ± 20 mA (with a relaxed  $V_{OL}/V_{OH}$ ).

| Speed | Symbol | Parameter                       | Conditions                                 | Min                                      | Max                | Unit  |  |

|-------|--------|---------------------------------|--------------------------------------------|------------------------------------------|--------------------|-------|--|

|       |        |                                 |                                            | C=50 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V | -                  | 50    |  |

|       |        |                                 | C=50 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -                                        | 25                 |       |  |

|       | Fmax   | Maximum fraguanay               | C=50 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -                                        | 5                  | MHz   |  |

|       | Fillax | Maximum frequency               | C=10 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -                                        | 100 <sup>(3)</sup> | IVINZ |  |

| 10    |        |                                 | C=10 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -                                        | 37.5               |       |  |

|       |        |                                 | C=10 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -                                        | 5                  |       |  |

|       |        |                                 | C=50 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -                                        | 5.8                |       |  |

|       |        | Output rise and fall time       | C=50 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -                                        | 11                 |       |  |

|       | Tr/Tf  |                                 | C=50 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -                                        | 28                 | 20    |  |

|       |        |                                 | C=10 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -                                        | 2.5                | ns    |  |

|       |        |                                 | C=10 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -                                        | 5                  |       |  |

|       |        |                                 | C=10 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -                                        | 12                 |       |  |

|       |        |                                 | C=30 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -                                        | 120 <sup>(3)</sup> |       |  |

|       |        | Fmax Maximum frequency          | C=30 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -                                        | 50                 | - MHz |  |

|       | Fmax   |                                 | C=30 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -                                        | 10                 |       |  |

|       | Fmax   |                                 | C=10 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -                                        | 180 <sup>(3)</sup> |       |  |

| 11    |        |                                 | C=10 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -                                        | 75                 |       |  |

|       |        |                                 | C=10 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -                                        | 10                 |       |  |

|       |        |                                 | C=30 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -                                        | 3.3                |       |  |

|       | Tr/Tf  | Output rise and fall time       | C=30 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -                                        | 6                  | ns    |  |

|       |        |                                 | C=30 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -                                        | 16                 |       |  |

| [m]   | Fmax   | Maximum frequency               |                                            | -                                        | 1                  | MHz   |  |

| Fm+   | Tf     | Output fall time <sup>(4)</sup> | C=50 pF, 1.6 V≤V <sub>DDIOx</sub> ≤3.6 V   | -                                        | 5                  | ns    |  |

The I/O speed is configured using the OSPEEDRy[1:0] bits. The Fm+ mode is configured in the SYSCFG\_CFGR1 register. Refer to the RM0394 reference manual for a description of GPIO Port configuration register.

2. Guaranteed by design.

3. This value represents the I/O capability but the maximum system frequency is limited to 80 MHz.

4. The fall time is defined between 70% and 30% of the output waveform accordingly to I<sup>2</sup>C specification.

| Symbol                 | Parameter                                                                                                                                                                                                                                             | Co                                                                    | onditions                                          | Min | Тур                                | Max                                | Unit |  |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------|-----|------------------------------------|------------------------------------|------|--|

| T <sub>W_to_W</sub>    | Minimal time between two<br>consecutive writes into the<br>DAC_DORx register to<br>guarantee a correct<br>DAC1_OUT1 for a small<br>variation of the input code<br>(1 LSB)<br>DAC_MCR:MODEx[2:0] =<br>000 or 001<br>DAC_MCR:MODEx[2:0] =<br>010 or 011 | CL ≤ 50 pF, RL ≥ 5 kΩ<br>CL ≤ 10 pF                                   |                                                    | 1   | -                                  | -                                  | μs   |  |

|                        |                                                                                                                                                                                                                                                       | DAC1_OUT1                                                             | DAC output buffer<br>ON, C <sub>SH</sub> = 100 nF  | -   | 0.7                                | 3.5                                | ms   |  |

|                        | Sampling time in sample<br>and hold mode (code<br>transition between the                                                                                                                                                                              | pin connected                                                         | DAC output buffer<br>OFF, C <sub>SH</sub> = 100 nF | -   | 10.5                               | 18                                 | 1115 |  |

| t <sub>SAMP</sub>      | lowest input code and the<br>highest input code when<br>DAC1_OUT1 reaches final<br>value ±1LSB)                                                                                                                                                       | DAC1_OUT1<br>pin not<br>connected<br>(internal<br>connection<br>only) | DAC output buffer<br>OFF                           | -   | 2                                  | 3.5                                | μs   |  |

| I <sub>leak</sub>      | Output leakage current                                                                                                                                                                                                                                | Sample and hold mode,<br>DAC1_OUT1 pin connected                      |                                                    | -   | -                                  | _(3)                               | nA   |  |

| Cl <sub>int</sub>      | Internal sample and hold capacitor                                                                                                                                                                                                                    | -                                                                     |                                                    | 5.2 | 7                                  | 8.8                                | pF   |  |

| t <sub>TRIM</sub>      | Middle code offset trim<br>time                                                                                                                                                                                                                       | DAC output bu                                                         | ffer ON                                            | 50  | -                                  | -                                  | μs   |  |

| V <sub>offset</sub>    | Middle code offset for 1                                                                                                                                                                                                                              | V <sub>REF+</sub> = 3.6 V                                             |                                                    | -   | 1500                               | -                                  | μV   |  |

| • offset               | trim code step                                                                                                                                                                                                                                        | V <sub>REF+</sub> = 1.8 V                                             |                                                    | -   | 750                                | -                                  | μ۷   |  |

|                        |                                                                                                                                                                                                                                                       | DAC output                                                            | No load, middle<br>code (0x800)                    | -   | 315                                | 500                                |      |  |

|                        |                                                                                                                                                                                                                                                       | buffer ON                                                             | No load, worst code<br>(0xF1C)                     | -   | 450                                | 670                                |      |  |

| I <sub>DDA</sub> (DAC) | DAC consumption from<br>V <sub>DDA</sub>                                                                                                                                                                                                              | DAC output<br>buffer OFF                                              | No load, middle<br>code (0x800)                    | -   | -                                  | 0.2                                | μA   |  |

|                        |                                                                                                                                                                                                                                                       | Sample and hold mode, C <sub>SH</sub> = 100 nF                        |                                                    | -   | 315 x<br>Ton/(Ton<br>+Toff)<br>(4) | 670 x<br>Ton/(Ton<br>+Toff)<br>(4) |      |  |

Table 83. DAC characteristics<sup>(1)</sup> (continued)

1. Measurement points are done at CMOS levels: 0.3  $V_{\text{DD}}$  and 0.7  $V_{\text{DD}}.$

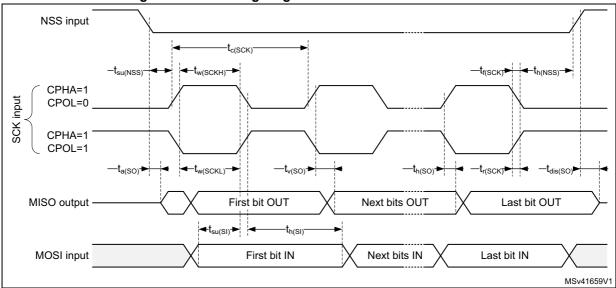

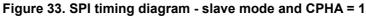

#### Figure 34. SPI timing diagram - master mode

1. Measurement points are done at CMOS levels: 0.3  $\rm V_{DD}$  and 0.7  $\rm V_{DD}.$

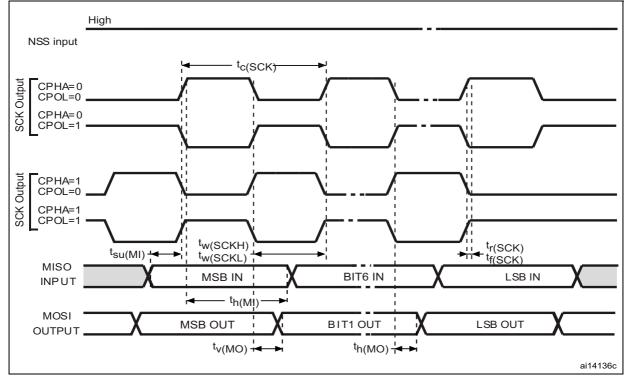

Figure 38. SAI slave timing waveforms

### **SDMMC** characteristics

Unless otherwise specified, the parameters given in *Table 99* for SDIO are derived from tests performed under the ambient temperature, f<sub>PCLKx</sub> frequency and V<sub>DD</sub> supply voltage conditions summarized in *Table 23: General operating conditions*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 11

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5 x V<sub>DD</sub>

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output characteristics.

| Symbol                                                 | Parameter                             | Conditions               | Min | Тур | Max | Unit |  |  |  |  |

|--------------------------------------------------------|---------------------------------------|--------------------------|-----|-----|-----|------|--|--|--|--|

| f <sub>PP</sub>                                        | Clock frequency in data transfer mode | -                        | 0   | -   | 50  | MHz  |  |  |  |  |

| -                                                      | SDIO_CK/fPCLK2 frequency ratio        | -                        | -   | -   | 4/3 | -    |  |  |  |  |

| t <sub>W(CKL)</sub>                                    | Clock low time                        | f <sub>PP</sub> = 50 MHz | 8   | 10  | -   | ns   |  |  |  |  |

| t <sub>W(CKH)</sub>                                    | Clock high time                       | f <sub>PP</sub> = 50 MHz | 8   | 10  | -   | ns   |  |  |  |  |

| CMD, D inputs (referenced to CK) in MMC and SD HS mode |                                       |                          |     |     |     |      |  |  |  |  |

| t <sub>ISU</sub>                                       | Input setup time HS                   | f <sub>PP</sub> = 50 MHz | 3.5 | -   | -   | ns   |  |  |  |  |

| t <sub>IH</sub>                                        | Input hold time HS                    | f <sub>PP</sub> = 50 MHz | 2.5 | -   | -   | ns   |  |  |  |  |

| CMD, D outp                                            | uts (referenced to CK) in MMC and SD  | HS mode                  |     |     |     |      |  |  |  |  |

| t <sub>OV</sub>                                        | Output valid time HS                  | f <sub>PP</sub> = 50 MHz | -   | 12  | 13  | ns   |  |  |  |  |

| t <sub>ОН</sub>                                        | Output hold time HS                   | f <sub>PP</sub> = 50 MHz | 10  | -   | -   | ns   |  |  |  |  |

| CMD, D inputs (referenced to CK) in SD default mode    |                                       |                          |     |     |     |      |  |  |  |  |

| t <sub>ISUD</sub>                                      | Input setup time SD                   | f <sub>PP</sub> = 50 MHz | 3.5 | -   | -   | ns   |  |  |  |  |

| t <sub>IHD</sub>                                       | Input hold time SD                    | f <sub>PP</sub> = 50 MHz | 3   | -   | -   | ns   |  |  |  |  |

Table 99. SD / MMC dynamic characteristics,  $V_{DD}$ =2.7 V to 3.6 V<sup>(1)</sup>

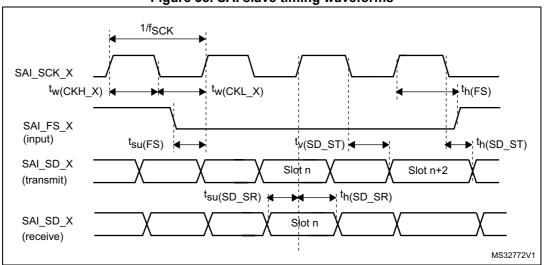

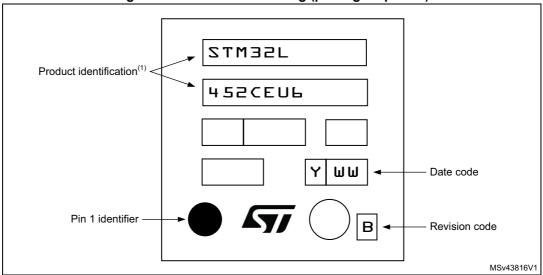

Figure 46. UFBGA100 marking (package top view)

Parts marked as ES or E or accompanied by an Engineering Sample notification letter are not yet qualified and therefore not approved for use in production. ST is not responsible for any consequences resulting from such use. In no event will ST be liable for the customer using any of these engineering samples in production. ST's Quality department must be contacted prior to any decision to use these engineering samples to run a qualification activity. 1.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as ES or E or accompanied by an Engineering Sample notification letter are not yet qualified and therefore not approved for use in production. ST is not responsible for any consequences resulting from such use. In no event will ST be liable for the customer using any of these engineering samples in production. ST's Quality department must be contacted prior to any decision to use these engineering samples to run a qualification activity.