Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | ARM® Cortex®-M4                                                                 |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, PWM, WDT                                           |

| Number of I/O              | 52                                                                              |

| Program Memory Size        | 512KB (512K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 160K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                    |

| Data Converters            | A/D 16x12b; D/A 1x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-UFBGA                                                                        |

| Supplier Device Package    | 64-UFBGA (5x5)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l452rei3           |

List of figures STM32L452xx

## **List of figures**

| Figure 1.   | STM32L452xx block diagram                                                | 16    |

|-------------|--------------------------------------------------------------------------|-------|

| Figure 2.   | Power supply overview                                                    | 21    |

| Figure 3.   | Power-up/down sequence                                                   | 22    |

| Figure 4.   | Clock tree                                                               | 36    |

| Figure 5.   | Voltage reference buffer                                                 | 41    |

| Figure 6.   | STM32L452Vx LQFP100 pinout <sup>(1)</sup>                                |       |

| Figure 7.   | STM32L452Vx UFBGA100 ballout <sup>(1)</sup>                              | 58    |

| Figure 8.   | STM32L452Rx LQFP64 pinout <sup>(1)</sup>                                 | 58    |

| Figure 9.   | STM32L452Rx, external SMPS device, LQFP64 pinout <sup>(1)</sup>          | 59    |

| Figure 10.  | STM32L452Rx UFBGA64 ballout <sup>(1)</sup>                               | 59    |

| Figure 11.  | STM32L452Rx WLCSP64 pinout <sup>(1)</sup>                                | 60    |

| Figure 12.  | STM32L452Cx UFQFPN48 pinout <sup>(1)</sup>                               | 60    |

| Figure 13.  | STM32L452xx memory map                                                   |       |

| Figure 14.  | Pin loading conditions                                                   |       |

| Figure 15.  | Pin input voltage                                                        |       |

| Figure 16.  | Power supply scheme                                                      |       |

| Figure 17.  | Current consumption measurement scheme with and without external         |       |

| Ü           | SMPS power supply                                                        | 90    |

| Figure 18.  | VREFINT versus temperature                                               |       |

| Figure 19.  | High-speed external clock source AC timing diagram                       |       |

| Figure 20.  | Low-speed external clock source AC timing diagram                        |       |

| Figure 21.  | Typical application with an 8 MHz crystal                                |       |

| Figure 22.  | Typical application with a 32.768 kHz crystal                            |       |

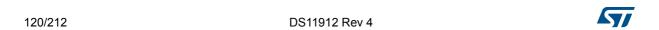

| Figure 23.  | HSI16 frequency versus temperature                                       |       |

| Figure 24.  | Typical current consumption versus MSI frequency                         |       |

| Figure 25.  | HSI48 frequency versus temperature                                       |       |

| Figure 26.  | I/O input characteristics                                                |       |

| Figure 27.  | I/O AC characteristics definition <sup>(1)</sup>                         | . 148 |

| Figure 28.  | Recommended NRST pin protection                                          |       |

| Figure 29.  | ADC accuracy characteristics                                             |       |

| Figure 30.  | Typical connection diagram using the ADC                                 |       |

| Figure 31.  | 12-bit buffered / non-buffered DAC                                       |       |

| Figure 32.  | SPI timing diagram - slave mode and CPHA = 0                             |       |

| Figure 33.  | SPI timing diagram - slave mode and CPHA = 1                             |       |

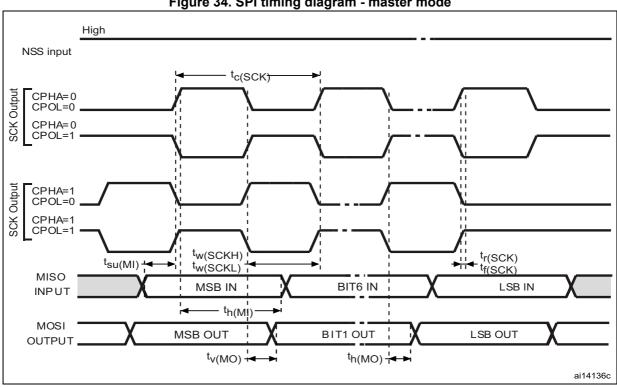

| Figure 34.  | SPI timing diagram - master mode                                         |       |

| Figure 35.  | Quad SPI timing diagram - SDR mode                                       |       |

| Figure 36.  | Quad SPI timing diagram - DDR mode                                       |       |

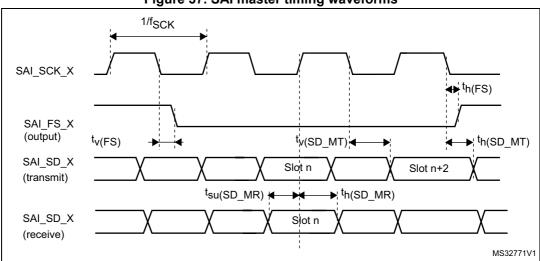

| Figure 37.  | SAI master timing waveforms                                              |       |

| Figure 38.  | SAI slave timing waveforms                                               |       |

| Figure 39.  | SDIO high-speed mode                                                     |       |

| Figure 40.  | SD default mode                                                          |       |

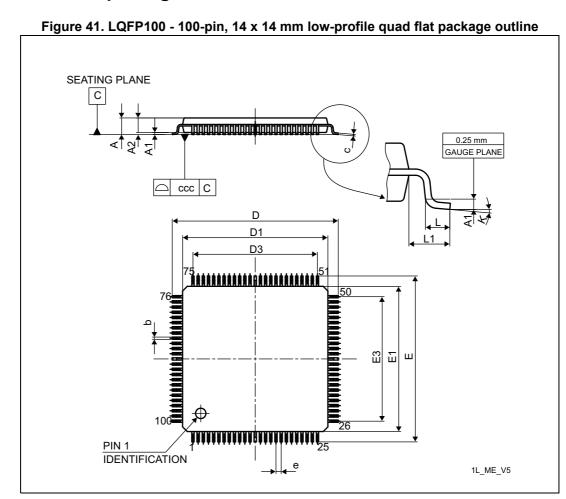

| Figure 41.  | LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat package outline      |       |

| Figure 42.  | LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat                      | . 100 |

| . igaio TE. | recommended footprint                                                    | 190   |

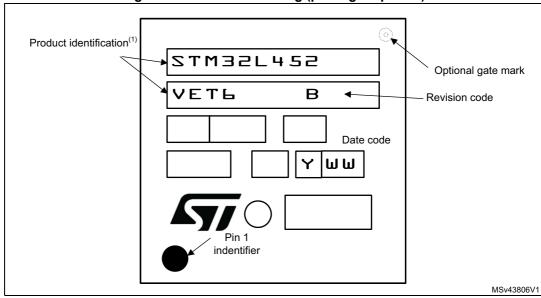

| Figure 43.  | LQFP100 marking (package top view)                                       | 191   |

| Figure 44.  | UFBGA100 - 100-ball, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ball grid |       |

| . igui 5    | array package outline                                                    | . 192 |

| Figure 45.  | UFBGA100 - 100-ball, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ball grid | 02    |

| . 194.5 10. | e. 2 c c c can, . x                                                      |       |

#### 3 Functional overview

## 3.1 Arm® Cortex®-M4 core with FPU

The Arm<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU processor is the latest generation of Arm<sup>®</sup> processors for embedded systems. It was developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced response to interrupts.

The Arm<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU 32-bit RISC processor features exceptional codeefficiency, delivering the high-performance expected from an Arm<sup>®</sup> core in the memory size usually associated with 8- and 16-bit devices.

The processor supports a set of DSP instructions which allow efficient signal processing and complex algorithm execution.

Its single precision FPU speeds up software development by using metalanguage development tools, while avoiding saturation.

With its embedded Arm<sup>®</sup> core, the STM32L452xx family is compatible with all Arm<sup>®</sup> tools and software.

*Figure 1* shows the general block diagram of the STM32L452xx family devices.

## 3.2 Adaptive real-time memory accelerator (ART Accelerator™)

The ART Accelerator™ is a memory accelerator which is optimized for STM32 industry-standard Arm® Cortex®-M4 processors. It balances the inherent performance advantage of the Arm® Cortex®-M4 over Flash memory technologies, which normally requires the processor to wait for the Flash memory at higher frequencies.

To release the processor near 100 DMIPS performance at 80MHz, the accelerator implements an instruction prefetch queue and branch cache, which increases program execution speed from the 64-bit Flash memory. Based on CoreMark benchmark, the performance achieved thanks to the ART accelerator is equivalent to 0 wait state program execution from Flash memory at a CPU frequency up to 80 MHz.

## 3.3 Memory protection unit

The memory protection unit (MPU) is used to manage the CPU accesses to memory to prevent one task to accidentally corrupt the memory or resources used by any other active task. This memory area is organized into up to 8 protected areas that can in turn be divided up into 8 subareas. The protection area sizes are between 32 bytes and the whole 4 gigabytes of addressable memory.

The MPU is especially helpful for applications where some critical or certified code has to be protected against the misbehavior of other tasks. It is usually managed by an RTOS (real-time operating system). If a program accesses a memory location that is prohibited by the MPU, the RTOS can detect it and take action. In an RTOS environment, the kernel can dynamically update the MPU area setting, based on the process to be executed.

The MPU is optional and can be bypassed for applications that do not need it.

DS11912 Rev 4 17/212

Shutdown **Stop 0/1** Stop 2 Standby Wakeup capability Wakeup capability capability Wakeup capabili Low-Low-**VBAT Peripheral** Run Sleep power power run sleep Wakeup CRC calculation unit 0 0 0 0 5 5 (9)(11)**GPIOs** pins  $\circ$ 0 0 0 0 0 0 0 pins (10)(10)

Table 5. Functionalities depending on the working mode<sup>(1)</sup> (continued)

- 1. Legend: Y = Yes (Enable). O = Optional (Disable by default. Can be enabled by software). = Not available.

- 2. The Flash can be configured in power-down mode. By default, it is not in power-down mode.

- 3. The SRAM clock can be gated on or off.

- 4. SRAM2 content is preserved when the bit RRS is set in PWR CR3 register.

- Some peripherals with wakeup from Stop capability can request HSI16 to be enabled. In this case, HSI16 is woken up by the peripheral, and only feeds the peripheral which requested it. HSI16 is automatically put off when the peripheral does not need it anymore.

- 6. UART and LPUART reception is functional in Stop mode, and generates a wakeup interrupt on Start, address match or received frame event.

- 7. I2C address detection is functional in Stop mode, and generates a wakeup interrupt in case of address match.

- 8. Voltage scaling Range 1 only.

- 9. I/Os can be configured with internal pull-up, pull-down or floating in Standby mode.

- 10. The I/Os with wakeup from Standby/Shutdown capability are: PA0, PC13, PE6, PA2, PC5.

- 11. I/Os can be configured with internal pull-up, pull-down or floating in Shutdown mode but the configuration is lost when exiting the Shutdown mode.

#### 3.9.5 Reset mode

In order to improve the consumption under reset, the I/Os state under and after reset is "analog state" (the I/O schmitt trigger is disable). In addition, the internal reset pull-up is deactivated when the reset source is internal.

#### 3.9.6 VBAT operation

The VBAT pin allows to power the device VBAT domain from an external battery, an external supercapacitor, or from  $V_{DD}$  when no external battery and an external supercapacitor are present. The VBAT pin supplies the RTC with LSE and the backup registers. Three antitamper detection pins are available in VBAT mode.

VBAT operation is automatically activated when V<sub>DD</sub> is not present.

An internal VBAT battery charging circuit is embedded and can be activated when  $V_{DD}$  is present.

Note: When the microcontroller is supplied from VBAT, external interrupts and RTC alarm/events do not exit it from VBAT operation.

577

DS11912 Rev 4 31/212

interrupt is generated if enabled. LSE failure can also be detected and generated an interrupt.

- Clock-out capability:

- MCO: microcontroller clock output: it outputs one of the internal clocks for external use by the application. Low frequency clocks (LSI, LSE) are available down to Stop 1 low power state.

- LSCO: low speed clock output: it outputs LSI or LSE in all low-power modes down to Standby mode. LSE can also be output on LSCO in Shutdown mode. LSCO is not available in VBAT mode.

Several prescalers allow to configure the AHB frequency, the high speed APB (APB2) and the low speed APB (APB1) domains. The maximum frequency of the AHB and the APB domains is 80 MHz.

DS11912 Rev 4 35/212

| 14.0.0                                                 |                        |

|--------------------------------------------------------|------------------------|

| SAI features                                           | Support <sup>(1)</sup> |

| I2S, LSB or MSB-justified, PCM/DSP, TDM, AC'97         | Х                      |

| Mute mode                                              | X                      |

| Stereo/Mono audio frame capability.                    | X                      |

| 16 slots                                               | X                      |

| Data size configurable: 8-, 10-, 16-, 20-, 24-, 32-bit | X                      |

| FIFO Size                                              | X (8 Word)             |

| SPDIF                                                  | X                      |

**Table 14. SAI implementation**

### 3.30 Controller area network (CAN)

The CAN is compliant with specifications 2.0A and B (active) with a bit rate up to 1 Mbit/s. It can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers. It has three transmit mailboxes, two receive FIFOs with 3 stages and 14 scalable filter banks.

The CAN peripheral supports:

- Supports CAN protocol version 2.0 A, B Active

- Bit rates up to 1 Mbit/s

- Transmission

- Three transmit mailboxes

- Configurable transmit priority

- Reception

- Two receive FIFOs with three stages

- 14 Scalable filter banks

- Identifier list feature

- Configurable FIFO overrun

- Time-triggered communication option

- Disable automatic retransmission mode

- 16-bit free running timer

- Time Stamp sent in last two data bytes

- Management

- Maskable interrupts

- Software-efficient mailbox mapping at a unique address space

# 3.31 Secure digital input/output and MultiMediaCards Interface (SDMMC)

The card host interface (SDMMC) provides an interface between the APB peripheral bus and MultiMediaCards (MMCs), SD memory cards and SDIO cards.

DS11912 Rev 4 53/212

<sup>1.</sup> X: supported

Table 16. STM32L452xx pin definitions (continued)

|          |         | Pir    | n Nu        | mbe     | r       |          |                                          |          |               |       | Pin fund                                                                                                              | ctions               |

|----------|---------|--------|-------------|---------|---------|----------|------------------------------------------|----------|---------------|-------|-----------------------------------------------------------------------------------------------------------------------|----------------------|

| UFQFPN48 | WLCSP64 | LQFP64 | LQFP64 SMPS | UFBGA64 | LQFP100 | UFBGA100 | Pin name<br>(function<br>after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                                   | Additional functions |

| -        | F3      | 39     | 39          | E8      | 65      | E10      | PC8                                      | I/O      | FT            | ı     | TIM3_CH3,<br>TSC_G4_IO3,<br>SDMMC1_D0,<br>EVENTOUT                                                                    | -                    |

| -        | E2      | 40     | 40          | D8      | 66      | D12      | PC9                                      | I/O      | FT            | 1     | TIM3_CH4,<br>TSC_G4_IO4,<br>USB_NOE,<br>SDMMC1_D1,<br>EVENTOUT                                                        | -                    |

| 29       | E3      | 41     | 41          | D7      | 67      | D11      | PA8                                      | I/O      | FT            | 1     | MCO, TIM1_CH1, DFSDM1_CKIN1, USART1_CK, SAI1_SCK_A, LPTIM2_OUT, EVENTOUT                                              | -                    |

| 30       | D1      | 42     | 42          | C7      | 68      | D10      | PA9                                      | I/O      | FT_f          | 1     | TIM1_CH2, I2C1_SCL, DFSDM1_DATIN1, USART1_TX, SAI1_FS_A, TIM15_BKIN, EVENTOUT                                         | -                    |

| 31       | C1      | 43     | 43          | C6      | 69      | C12      | PA10                                     | I/O      | FT_f          | 1     | TIM1_CH3, I2C1_SDA,<br>USART1_RX,<br>USB_CRS_SYNC,<br>SAI1_SD_A, EVENTOUT                                             | -                    |

| 32       | D2      | 44     | 44          | C8      | 70      | B12      | PA11                                     | I/O      | FT_u          | ı     | TIM1_CH4, TIM1_BKIN2,<br>SPI1_MISO,<br>COMP1_OUT,<br>USART1_CTS,<br>CAN1_RX, USB_DM,<br>TIM1_BKIN2_COMP1,<br>EVENTOUT | -                    |

| 33       | D3      | 45     | 45          | В8      | 71      | A12      | PA12                                     | I/O      | FT_u          | 1     | TIM1_ETR, SPI1_MOSI,<br>USART1_RTS_DE,<br>CAN1_TX, USB_DP,<br>EVENTOUT                                                | -                    |

| 34       | C2      | 46     | 46          | A8      | 72      | A11      | PA13<br>(JTMS/<br>SWDIO)                 | I/O      | FT            | (3)   | JTMS/SWDAT, IR_OUT,<br>USB_NOE, SAI1_SD_B,<br>EVENTOUT                                                                | -                    |

| 35       |         | 47     |             | D5      | -       | -        | VSS                                      | S        | -             | -     | -                                                                                                                     | -                    |

| 36       | A1      | 48     | 48          | E5      | 73      | C11      | VDDUSB                                   | S        | -             | -     | -                                                                                                                     | -                    |

| _        | -       | -      | -           | -       | 74      | F11      | VSS                                      | S        | -             | -     | -                                                                                                                     | -                    |

68/212 DS11912 Rev 4

**Electrical characteristics**

Table 29. Current consumption in Run and Low-power run modes, code with data processing running from Flash, ART disable

|                              |                                                                                              | Condi                          | itions          |                   |       |       | TYP   |        |        |       |       | MAX <sup>(1)</sup> |        |        |      |

|------------------------------|----------------------------------------------------------------------------------------------|--------------------------------|-----------------|-------------------|-------|-------|-------|--------|--------|-------|-------|--------------------|--------|--------|------|

| Symbol                       | Parameter                                                                                    | -                              | Voltage scaling | f <sub>HCLK</sub> | 25 °C | 55 °C | 85 °C | 105 °C | 125 °C | 25 °C | 55 °C | 85 °C              | 105 °C | 125 °C | Unit |

|                              |                                                                                              |                                |                 | 26 MHz            | 2.75  | 2.80  | 2.90  | 3.10   | 3.40   | 3.15  | 3.25  | 3.40               | 3.70   | 4.30   |      |

|                              |                                                                                              |                                |                 | 16 MHz            | 1.95  | 2.00  | 2.10  | 2.25   | 2.60   | 2.25  | 2.30  | 2.50               | 2.75   | 3.35   |      |

|                              |                                                                                              |                                |                 | 8 MHz             | 1.10  | 1.15  | 1.25  | 1.40   | 1.75   | 1.25  | 1.35  | 1.50               | 1.75   | 2.35   |      |

|                              |                                                                                              |                                | Range 2         | 4 MHz             | 0.640 | 0.670 | 0.765 | 0.935  | 1.25   | 0.75  | 0.80  | 0.95               | 1.25   | 1.80   |      |

|                              |                                                                                              | f = f up to                    |                 | 2 MHz             | 0.380 | 0.405 | 0.505 | 0.670  | 1.00   | 0.45  | 0.50  | 0.65               | 0.95   | 1.50   |      |

|                              |                                                                                              | t in Dypass mode               |                 | 1 MHz             | 0.250 | 0.275 | 0.375 | 0.540  | 0.865  | 0.30  | 0.35  | 0.50               | 0.80   | 1.35   |      |

| I <sub>DD_ALL</sub><br>(Run) | Supply                                                                                       |                                |                 | 100 kHz           | 0.135 | 0.160 | 0.255 | 0.420  | 0.750  | 0.15  | 0.25  | 0.40               | 0.65   | 1.25   | mA   |

| (Run)                        | Run mode PLL ON abov                                                                         | PLL ON above                   |                 | 80 MHz            | 8.85  | 8.90  | 9.05  | 9.30   | 9.70   | 10.0  | 10.5  | 10.5               | 11.0   | 11.5   |      |

|                              |                                                                                              | 48 MHz all peripherals disable | nle             | 72 MHz            | 8.00  | 8.05  | 8.20  | 8.40   | 8.85   | 9.05  | 9.15  | 9.35               | 9.70   | 10.5   |      |

|                              |                                                                                              | poriprioraio diodolo           |                 | 64 MHz            | 7.90  | 7.95  | 8.10  | 8.35   | 8.75   | 8.95  | 9.10  | 9.35               | 9.70   | 10.5   |      |

|                              |                                                                                              |                                | Range 1         | 48 MHz            | 6.60  | 6.65  | 6.80  | 7.05   | 7.45   | 7.55  | 7.65  | 7.90               | 8.30   | 9.00   |      |

|                              |                                                                                              |                                |                 | 32 MHz            | 4.75  | 4.80  | 4.95  | 5.15   | 5.55   | 5.40  | 5.50  | 5.75               | 6.10   | 6.80   |      |

|                              |                                                                                              |                                |                 | 24 MHz            | 3.60  | 3.65  | 3.80  | 4.00   | 4.35   | 4.10  | 4.20  | 4.40               | 4.75   | 5.40   |      |

|                              |                                                                                              |                                |                 | 16 MHz            | 2.60  | 2.65  | 2.75  | 2.95   | 3.35   | 3.00  | 3.05  | 3.25               | 3.60   | 4.25   |      |

|                              | Supply                                                                                       |                                |                 | 2 MHz             | 340   | 360   | 470   | 650    | 1000   | 400   | 455   | 575                | 880    | 1550   |      |

| I <sub>DD ALL</sub>          | Supply current in Low-power run f <sub>HCLK</sub> = f <sub>MSI</sub> all peripherals disable |                                | 1 MHz           | 175               | 215   | 320   | 500   | 855    | 225    | 285   | 420   | 720                | 1350   |        |      |

| (LPRun)                      |                                                                                              |                                | le              | 400 kHz           | 89.5  | 120   | 225   | 405    | 760    | 130   | 185   | 340                | 620    | 1250   | μA   |

|                              |                                                                                              |                                | 100 kHz         | 42.5              | 75.5  | 180   | 360   | 715    | 75     | 145   | 320   | 575                | 1200   |        |      |

<sup>1.</sup> Guaranteed by characterization results, unless otherwise specified.

Table 42. Current consumption in Sleep and Low-power sleep modes, Flash ON

|                     |                                                | Cond                                                 | ditions         |                   |       |        | TYP   |        |        |       |       | MAX <sup>(1)</sup> |        |        |        |      |  |

|---------------------|------------------------------------------------|------------------------------------------------------|-----------------|-------------------|-------|--------|-------|--------|--------|-------|-------|--------------------|--------|--------|--------|------|--|

| Symbol              | Parameter                                      | -                                                    | Voltage scaling | f <sub>HCLK</sub> | 25 °C | 55 °C  | 85 °C | 105 °C | 125 °C | 25 °C | 55 °C | 85 °C              | 105 °C | 125 °C | Unit   |      |  |

|                     |                                                |                                                      |                 | 26 MHz            | 0.700 | 0.730  | 0.830 | 1.00   | 1.35   | 0.80  | 0.90  | 1.05               | 1.30   | 1.90   |        |      |  |

|                     |                                                |                                                      |                 | 16 MHz            | 0.475 | 0.505  | 0.605 | 0.775  | 1.10   | 0.55  | 0.65  | 0.80               | 1.05   | 1.65   |        |      |  |

|                     |                                                |                                                      |                 | 8 MHz             | 0.300 | 0.325  | 0.425 | 0.590  | 0.920  | 0.35  | 0.45  | 0.60               | 0.85   | 1.45   |        |      |  |

|                     |                                                |                                                      | Range 2         | 4 MHz             | 0.210 | 0.235  | 0.335 | 0.500  | 0.830  | 0.25  | 0.30  | 0.45               | 0.75   | 1.35   |        |      |  |

|                     |                                                | f <sub>HCLK</sub> = f <sub>HSE</sub> up<br>to 48 MHz |                 | 2 MHz             | 0.165 | 0.190  | 0.290 | 0.455  | 0.785  | 0.20  | 0.25  | 0.40               | 0.70   | 1.25   |        |      |  |

|                     | Supply                                         | included, bypass                                     |                 | 1 MHz             | 0.145 | 0.170  | 0.265 | 0.430  | 0.760  | 0.15  | 0.25  | 0.40               | 0.65   | 1.25   |        |      |  |

| I <sub>DD_ALL</sub> | current in mode sleep pll ON abov              |                                                      |                 | 100 kHz           | 0.125 | 0.150  | 0.245 | 0.410  | 0.740  | 0.15  | 0.20  | 0.35               | 0.65   | 1.20   | mA     |      |  |

| (Sleep)             |                                                | pll ON above                                         | Range 1         | 80 MHz            | 2.30  | 2.35   | 2.45  | 2.65   | 3.05   | 2.55  | 2.65  | 2.85               | 3.15   | 3.80   | 1117 ( |      |  |

|                     | mode,                                          | 48 MHz all peripherals                               |                 | 72 MHz            | 2.10  | 2.15   | 2.25  | 2.45   | 2.80   | 2.35  | 2.40  | 2.60               | 2.90   | 3.55   |        |      |  |

|                     |                                                | disable                                              |                 | 64 MHz            | 1.90  | 1.90   | 2.05  | 2.25   | 2.60   | 2.10  | 2.20  | 2.35               | 2.70   | 3.35   |        |      |  |

|                     |                                                |                                                      |                 | 48 MHz            | 1.40  | 1.40   | 1.55  | 1.75   | 2.15   | 1.60  | 1.65  | 1.85               | 2.15   | 2.80   |        |      |  |

|                     |                                                |                                                      |                 | 32 MHz            | 0.970 | 1.00   | 1.15  | 1.30   | 1.70   | 1.10  | 1.20  | 1.40               | 1.70   | 2.35   |        |      |  |

|                     |                                                |                                                      |                 |                   |       | 24 MHz | 0.765 | 0.800  | 0.920  | 1.10  | 1.50  | 0.90               | 0.95   | 1.15   | 1.45   | 2.10 |  |

|                     |                                                |                                                      |                 | 16 MHz            | 0.555 | 0.590  | 0.705 | 0.895  | 1.25   | 0.65  | 0.75  | 0.90               | 1.20   | 1.85   |        |      |  |

|                     | Supply                                         |                                                      |                 | 2 MHz             | 76.0  | 110    | 215   | 395    | 745    | 120   | 185   | 355                | 610    | 1250   |        |      |  |

| I <sub>DD ALL</sub> | Current in I I I I I I I I I I I I I I I I I I |                                                      | 1 MHz           | 54.0              | 86.5  | 195    | 370   | 725    | 88.5   | 160   | 335   | 585                | 1250   | ^      |        |      |  |

| (LPSleep)           |                                                |                                                      | able            | 400 kHz           | 39.0  | 70.5   | 175   | 355    | 710    | 68.5  | 140   | 320                | 570    | 1200   | μA     |      |  |

|                     | mode                                           |                                                      |                 | 100 kHz           | 35.5  | 75.0   | 195   | 345    | 715    | 66.0  | 130   | 305                | 560    | 1200   |        |      |  |

<sup>1.</sup> Guaranteed by characterization results, unless otherwise specified.

Table 47. Current consumption in Stop 0

| Symbol              | Baramatar    | Parameter Conditions |       |       | TYP   |        |        |       |       | MAX <sup>(1)</sup> |        |                     |      |  |

|---------------------|--------------|----------------------|-------|-------|-------|--------|--------|-------|-------|--------------------|--------|---------------------|------|--|

| Symbol              | Parameter    | $V_{DD}$             | 25 °C | 55 °C | 85 °C | 105 °C | 125 °C | 25 °C | 55 °C | 85 °C              | 105 °C | 125 °C              | Unit |  |

|                     | Supply       | 1.8 V                | 125   | 150   | 240   | 390    | 645    | 145   | 190   | 350                | 600    | 1150                |      |  |

| I <sub>DD_ALL</sub> | current in   | 2.4 V                | 125   | 150   | 240   | 390    | 645    | 150   | 195   | 355                | 605    | 1150                | μA   |  |

| (Stop 0)            | Stop 0 mode, | 3 V                  | 125   | 150   | 245   | 395    | 650    | 155   | 195   | 360                | 610    | 1150                | μΑ   |  |

|                     | RTC disabled | 3.6 V                | 125   | 155   | 245   | 400    | 655    | 155   | 200   | 365                | 615    | 1150 <sup>(2)</sup> |      |  |

<sup>1.</sup> Guaranteed by characterization results, unless otherwise specified.

<sup>2.</sup> Guaranteed by test in production.

#### I/O system current consumption

The current consumption of the I/O system has two components: static and dynamic.

#### I/O static current consumption

All the I/Os used as inputs with pull-up generate current consumption when the pin is externally held low. The value of this current consumption can be simply computed by using the pull-up/pull-down resistors values given in *Table 71: I/O static characteristics*.

For the output pins, any external pull-down or external load must also be considered to estimate the current consumption.

Additional I/O current consumption is due to I/Os configured as inputs if an intermediate voltage level is externally applied. This current consumption is caused by the input Schmitt trigger circuits used to discriminate the input value. Unless this specific configuration is required by the application, this supply current consumption can be avoided by configuring these I/Os in analog mode. This is notably the case of ADC input pins which should be configured as analog inputs.

Caution:

Any floating input pin can also settle to an intermediate voltage level or switch inadvertently, as a result of external electromagnetic noise. To avoid current consumption related to floating pins, they must either be configured in analog mode, or forced internally to a definite digital value. This can be done either by using pull-up/down resistors or by configuring the pins in output mode.

#### I/O dynamic current consumption

In addition to the internal peripheral current consumption measured previously (see *Table 51: Peripheral current consumption*), the I/Os used by an application also contribute to the current consumption. When an I/O pin switches, it uses the current from the I/O supply voltage to supply the I/O pin circuitry and to charge/discharge the capacitive load (internal or external) connected to the pin:

$$I_{SW} = V_{DDIOx} \times f_{SW} \times C$$

where

$I_{\mbox{\scriptsize SW}}$  is the current sunk by a switching I/O to charge/discharge the capacitive load

V<sub>DDIOx</sub> is the I/O supply voltage

$f_{\mbox{SW}}$  is the I/O switching frequency

C is the total capacitance seen by the I/O pin:  $C = C_{INT} + C_{EXT} + C_{S}$

$C_S$  is the PCB board capacitance including the pad pin.

The test pin is configured in push-pull output mode and is toggled by software at a fixed frequency.

Figure 23. HSI16 frequency versus temperature

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in Section 6.2:

- The sum of the currents sourced by all the I/Os on V<sub>DDIOx</sub>, plus the maximum consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating ΣI<sub>VDD</sub> (see *Table 20: Voltage characteristics*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub>, plus the maximum consumption of the MCU sunk on V<sub>SS</sub>, cannot exceed the absolute maximum rating ΣI<sub>VSS</sub> (see Table 20: Voltage characteristics).

#### **Output voltage levels**

Unless otherwise specified, the parameters given in the table below are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 23: General operating conditions*. All I/Os are CMOS- and TTL-compliant (FT OR TT unless otherwise specified).

Table 72. Output voltage characteristics<sup>(1)</sup>

| Symbol                         | Parameter                                                                       | Conditions                                                       | Min                      | Max               | Unit |

|--------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------|--------------------------|-------------------|------|

| V <sub>OL</sub>                | Output low level voltage for an I/O pin                                         | CMOS port <sup>(2)</sup>                                         | -                        | 0.4               |      |

| V <sub>OH</sub>                | Output high level voltage for an I/O pin                                        | I <sub>IO</sub>   = 8 mA<br>V <sub>DDIOx</sub> ≥ 2.7 V           | V <sub>DDIOx</sub> -0.4  | -                 |      |

| V <sub>OL</sub> <sup>(3)</sup> | Output low level voltage for an I/O pin                                         | TTL port <sup>(2)</sup>                                          | -                        | 0.4               |      |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin                                        | I <sub>IO</sub>   = 8 mA<br> V <sub>DDIOx</sub> ≥ 2.7 V          | 2.4                      | -                 |      |

| V <sub>OL</sub> <sup>(3)</sup> | Output low level voltage for an I/O pin                                         | I <sub>IO</sub>   = 20 mA                                        | -                        | 1.3               |      |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin                                        | V <sub>DDIOx</sub> ≥ 2.7 V                                       | V <sub>DDIOx</sub> -1.3  | -                 |      |

| V <sub>OL</sub> <sup>(3)</sup> | Output low level voltage for an I/O pin                                         | I <sub>IO</sub>   = 4 mA                                         | -                        | 0.45              |      |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin                                        | V <sub>DDIOx</sub> ≥ 1.62 V                                      | V <sub>DDIOx</sub> -0.45 | -                 | V    |

| V <sub>OL</sub> <sup>(3)</sup> | Output low level voltage for an I/O pin                                         | I <sub>IO</sub>   = 2 mA                                         | -                        | $0.35_xV_{DDIOx}$ |      |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin                                        | 1.62 V ≥ V <sub>DDIOx</sub> ≥ 1.08 V                             | $0.65_xV_{DDIOx}$        | -                 |      |

|                                |                                                                                 | $ I_{IO}  = 20 \text{ mA}$<br>$V_{DDIOx} \ge 2.7 \text{ V}$      | -                        | 0.4               |      |

| V <sub>OLFM+</sub>             | Output low level voltage for an FT I/O pin in FM+ mode (FT I/O with "f" option) | I <sub>IO</sub>   = 10 mA<br>V <sub>DDIOx</sub> ≥ 1.62 V         | -                        | 0.4               |      |

|                                | . ,                                                                             | I <sub>IO</sub>   = 2 mA<br>1.62 V ≥ V <sub>DDIOx</sub> ≥ 1.08 V | -                        | 0.4               |      |

The I<sub>IO</sub> current sourced or sunk by the device must always respect the absolute maximum rating specified in *Table 20:* Voltage characteristics, and the sum of the currents sourced or sunk by all the I/Os (I/O ports and control pins) must always respect the absolute maximum ratings ΣI<sub>IO</sub>.

#### Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 27* and *Table 73*, respectively.

DS11912 Rev 4 145/212

<sup>2.</sup> TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

<sup>3.</sup> Guaranteed by design.

Table 81. ADC accuracy - limited test conditions  $3^{(1)(2)(3)}$  (continued)

| Sym-<br>bol | Parameter           | C                                                                       | Conditions <sup>(4</sup> | )                        | Min | Тур | Max | Unit |

|-------------|---------------------|-------------------------------------------------------------------------|--------------------------|--------------------------|-----|-----|-----|------|

|             |                     | ADC clock frequency ≤                                                   | Single                   | Fast channel (max speed) | -   | -69 | -67 |      |

|             | Total               | 80 MHz,<br>Sampling rate ≤ 5.33 Msps,                                   | ended                    | Slow channel (max speed) | -   | -71 | -67 |      |

| THD         | harmonic distortion | $1.65 \text{ V} \le \text{V}_{\text{DDA}} = \text{V}_{\text{REF+}} \le$ |                          | Fast channel (max speed) | -   | -72 | -71 | dB   |

|             | distortion          | 3.6 V,<br>Voltage scaling Range 1                                       | Differential             | Slow channel (max speed) | -   | -72 | -71 |      |

- 1. Guaranteed by design.

- 2. ADC DC accuracy values are measured after internal calibration.

- ADC accuracy vs. negative Injection Current: Injecting negative current on any analog input pins should be avoided as this

significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a

Schottky diode (pin to ground) to analog pins which may potentially inject negative current.

- 4. The I/O analog switch voltage booster is enable when  $V_{DDA}$  < 2.4 V (BOOSTEN = 1 in the SYSCFG\_CFGR1 when  $V_{DDA}$  < 2.4 V). It is disable when  $V_{DDA} \ge 2.4$  V. No oversampling.

## 6.3.21 Comparator characteristics

Table 86. COMP characteristics<sup>(1)</sup>

| Symbol                         | Parameter                      | Co                     | onditions                | Min  | Тур                 | Max              | Unit |

|--------------------------------|--------------------------------|------------------------|--------------------------|------|---------------------|------------------|------|

| V <sub>DDA</sub>               | Analog supply voltage          |                        | -                        | 1.62 | -                   | 3.6              |      |

| V <sub>IN</sub>                | Comparator input voltage range |                        | -                        |      | -                   | V <sub>DDA</sub> | V    |

| V <sub>BG</sub> <sup>(2)</sup> | Scaler input voltage           |                        | -                        |      | V <sub>REFINT</sub> | -                |      |

| V <sub>SC</sub>                | Scaler offset voltage          |                        | -                        | -    | ±5                  | ±10              | mV   |

| I <sub>DDA</sub> (SCALER)      | Scaler static consumption      | BRG_EN=0 (bi           | ridge disable)           | -    | 200                 | 300              | nA   |

| IDDA(GUALEK)                   | from V <sub>DDA</sub>          | BRG_EN=1 (bi           | ridge enable)            | -    | 0.8                 | 1                | μA   |

| t <sub>START_SCALER</sub>      | Scaler startup time            |                        | -                        | -    | 100                 | 200              | μs   |

|                                |                                | High-speed             | V <sub>DDA</sub> ≥ 2.7 V | -    | -                   | 5                |      |

|                                | Comparator startup time to     | mode                   | V <sub>DDA</sub> < 2.7 V | -    | -                   | 7                |      |

| t <sub>START</sub>             | reach propagation delay        | Medium mode            | V <sub>DDA</sub> ≥ 2.7 V | -    | -                   | 15               | μs   |

|                                | specification                  | Medium mode            | V <sub>DDA</sub> < 2.7 V | -    | -                   | 25               |      |

|                                |                                | Ultra-low-powe         | ltra-low-power mode      |      | -                   | 40               |      |

|                                |                                | High-speed             | V <sub>DDA</sub> ≥ 2.7 V | -    | 55                  | 80               | ns   |

| t <sub>D</sub> <sup>(3)</sup>  | Propagation delay with         | mode                   | V <sub>DDA</sub> < 2.7 V | -    | 65                  | 100              | 115  |

| ,D, ,                          | 100 mV overdrive               | Medium mode            |                          | -    | 0.55                | 0.9              |      |

|                                |                                | Ultra-low-powe         | er mode                  | -    | 4                   | 7                | μs   |

| V <sub>offset</sub>            | Comparator offset error        | Full common mode range | -                        | -    | ±5                  | ±20              | mV   |

|                                |                                | No hysteresis          |                          | -    | 0                   | -                |      |

| V                              | Comparator hyptoropia          | Low hysteresis         | ;                        | -    | 8                   | -                | m\/  |

| $V_{hys}$                      | Comparator hysteresis          | Medium hyster          | -                        | 15   | -                   | mV               |      |

|                                |                                | High hysteresis        | 8                        | -    | 27                  | -                |      |

Table 87. OPAMP characteristics<sup>(1)</sup> (continued)

| Symbol                            | Parameter                                | Con            | iditions                                                                      | Min                       | Тур  | Max  | Unit   |

|-----------------------------------|------------------------------------------|----------------|-------------------------------------------------------------------------------|---------------------------|------|------|--------|

|                                   | Daire                                    | Normal mode    | V > 0 V                                                                       | -                         | -    | 500  |        |

| I <sub>LOAD</sub>                 | Drive current                            | Low-power mode | V <sub>DDA</sub> ≥ 2 V                                                        | -                         | -    | 100  |        |

|                                   | Drive current in                         | Normal mode    | V > 0.V                                                                       | -                         | -    | 450  | μA     |

| I <sub>LOAD_PGA</sub>             | PGA mode                                 | Low-power mode | - V <sub>DDA</sub> ≥ 2 V                                                      | -                         | -    | 50   |        |

| R <sub>LOAD</sub>                 | Resistive load (connected to             | Normal mode    | - V <sub>DDA</sub> < 2 V                                                      | 4                         | -    | -    |        |

| NLOAD                             | VSSA or to<br>VDDA)                      | Low-power mode | VDDA 12 V                                                                     | 20                        | ı    | -    | kΩ     |

| P                                 | Resistive load in PGA mode (connected to | Normal mode    | - V <sub>DDA</sub> < 2 V                                                      | 4.5                       | ı    | 1    | K22    |

| R <sub>LOAD_PGA</sub>             | VSSA or to<br>V <sub>DDA</sub> )         | Low-power mode | VDDA 12 V                                                                     | 40                        | ı    | 1    |        |

| C <sub>LOAD</sub>                 | Capacitive load                          |                | -                                                                             | -                         | 1    | 50   | pF     |

| CMRR                              | Common mode                              | Normal mode    |                                                                               | -                         | -85  | -    | dB     |

| OWINT                             | rejection ratio                          | Low-power mode |                                                                               | ı                         | -90  | ı    | ų D    |

| PSRR                              | Power supply                             | Normal mode    | $C_{LOAD} \le 50 \text{ pf},$<br>$R_{LOAD} \ge 4 \text{ k}\Omega \text{ DC}$  | 70                        | 85   | 1    | dB     |

| 1 SIXIX                           | rejection ratio                          | Low-power mode | $C_{LOAD} \le 50 \text{ pf},$<br>$R_{LOAD} \ge 20 \text{ k}\Omega \text{ DC}$ | 72                        | 90   | -    | uБ     |

|                                   |                                          | Normal mode    | V <sub>DDA</sub> ≥ 2.4 V                                                      | 550                       | 1600 | 2200 |        |

| GBW                               | Gain Bandwidth                           | Low-power mode | (OPA_RANGE = 1)                                                               | 100                       | 420  | 600  | kHz    |

| GBVV                              | Product                                  | Normal mode    | V <sub>DDA</sub> < 2.4 V                                                      | 250                       | 700  | 950  | KIZ    |

|                                   |                                          | Low-power mode | (OPA_RANGE = 0)                                                               | 40                        | 180  | 280  |        |

|                                   | Slew rate                                | Normal mode    | - V <sub>DDA</sub> ≥ 2.4 V                                                    | -                         | 700  | -    |        |

| SR <sup>(3)</sup>                 | (from 10 and                             | Low-power mode | VDDA = 2.4 V                                                                  | -                         | 180  | -    | V/ms   |

| SIX 7                             | 90% of output voltage)                   | Normal mode    | V                                                                             | ı                         | 300  | -    | V/IIIS |

|                                   | voltage)                                 | Low-power mode | - V <sub>DDA</sub> < 2.4 V                                                    | ı                         | 80   | ı    |        |

| AO                                | Open loop gain                           | Normal mode    |                                                                               | 55                        | 110  | -    | dB     |

| AO                                | Open loop gain                           | Low-power mode |                                                                               | 45                        | 110  | -    | ų b    |

| V <sub>OHSAT</sub> <sup>(3)</sup> | High saturation                          | Normal mode    | I <sub>load</sub> = max or R <sub>load</sub> =                                | V <sub>DDA</sub> -<br>100 | i    | ı    |        |

| VOHSAT                            | voltage                                  | Low-power mode | min Input at V <sub>DDA</sub> .                                               | V <sub>DDA</sub> -<br>50  | ı    | ı    | mV     |

| V <sub>OLSAT</sub> <sup>(3)</sup> | Low saturation                           | Normal mode    | I <sub>load</sub> = max or R <sub>load</sub> =                                | -                         | -    | 100  |        |

| VOLSAT`                           | voltage                                  | Low-power mode | min Input at 0.                                                               | -                         |      | 50   |        |

| <u></u>                           | Phase margin                             | Normal mode    |                                                                               | -                         | 74   |      | 0      |

| Φm                                | i nasc margin                            | Low-power mode |                                                                               | -                         | 66   | -    |        |

172/212 DS11912 Rev 4

## 6.3.24 V<sub>BAT</sub> monitoring characteristics

Table 89. V<sub>BAT</sub> monitoring characteristics

| Symbol                             | Parameter                               | Min | Тур | Max | Unit |

|------------------------------------|-----------------------------------------|-----|-----|-----|------|

| R                                  | Resistor bridge for V <sub>BAT</sub>    | -   | 39  | -   | kΩ   |

| Q                                  | Ratio on V <sub>BAT</sub> measurement   | -   | 3   | -   | -    |

| Er <sup>(1)</sup>                  | Error on Q                              | -10 | -   | 10  | %    |

| t <sub>S_vbat</sub> <sup>(1)</sup> | ADC sampling time when reading the VBAT | 12  | -   | -   | μs   |

<sup>1.</sup> Guaranteed by design.

Table 90. V<sub>BAT</sub> charging characteristics

| Symbol          | Parameter                       | Conditions | Min | Тур | Max | Unit |

|-----------------|---------------------------------|------------|-----|-----|-----|------|

| R <sub>BC</sub> | Battery<br>charging<br>resistor | VBRS = 0   | -   | 5   | -   | kΩ   |

|                 |                                 | VBRS = 1   | -   | 1.5 | -   |      |

#### 6.3.25 Timer characteristics

The parameters given in the following tables are guaranteed by design.

Refer to *Section 6.3.14: I/O port characteristics* for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

Table 91. TIMx<sup>(1)</sup> characteristics

| Symbol                 | Parameter               | Conditions                    | Min    | Max                     | Unit                 |  |

|------------------------|-------------------------|-------------------------------|--------|-------------------------|----------------------|--|

| t <sub>res(TIM)</sub>  | Timer resolution time   | -                             | 1      | -                       | t <sub>TIMxCLK</sub> |  |

|                        | Timer resolution time   | f <sub>TIMxCLK</sub> = 80 MHz | 12.5   | -                       | ns                   |  |

| f <sub>EXT</sub>       | Timer external clock    | -                             | 0      | f <sub>TIMxCLK</sub> /2 | MHz                  |  |

|                        | frequency on CH1 to CH4 | f <sub>TIMxCLK</sub> = 80 MHz | 0      | 40                      | MHz                  |  |

| Res <sub>TIM</sub>     | Timer resolution        | TIMx (except<br>TIM2)         | -      | 16                      | bit                  |  |

|                        |                         | TIM2                          | -      | 32                      |                      |  |

| tcounter               | 16-bit counter clock    | -                             | 1      | 65536                   | t <sub>TIMxCLK</sub> |  |

|                        | period                  | f <sub>TIMxCLK</sub> = 80 MHz | 0.0125 | 819.2                   | μs                   |  |

| t <sub>MAX_COUNT</sub> | Maximum possible count  | -                             | -      | 65536 × 65536           | t <sub>TIMxCLK</sub> |  |

|                        | with 32-bit counter     | f <sub>TIMxCLK</sub> = 80 MHz | -      | 53.68                   | s                    |  |

<sup>1.</sup> TIMx is used as a general term in which x stands for 1,2,3,4,5,6,7,8,15,16 or 17.

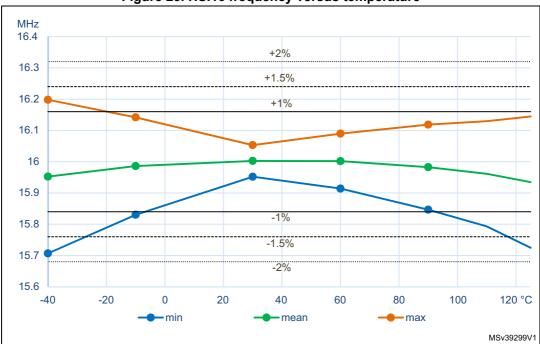

Figure 33. SPI timing diagram - slave mode and CPHA = 1

1. Measurement points are done at CMOS levels: 0.3  $\rm V_{DD}$  and 0.7  $\rm V_{DD}$ .

Figure 34. SPI timing diagram - master mode

1. Measurement points are done at CMOS levels: 0.3  $\rm V_{DD}$  and 0.7  $\rm V_{DD}$

**Symbol Conditions** Min Unit **Parameter** Max Slave transmitter (after enable edge) 22  $2.7 \leq V_{\text{DD}} \leq 3.6$ Data output valid time ns  $t_{v(SD\_B\_ST)}$ Slave transmitter (after enable edge) 34  $1.71 \le V_{DD} \le 3.6$ Data output hold time Slave transmitter (after enable edge) 10 ns t<sub>h(SD\_B\_ST)</sub> Master transmitter (after enable edge) 27  $2.7 \le V_{DD} \le 3.6$ Data output valid time ns t<sub>v(SD A MT)</sub> Master transmitter (after enable edge) 40  $1.71 \leq V_{DD} \leq 3.6$ Master transmitter (after enable edge) Data output hold time 10 ns

Table 98. SAI characteristics<sup>(1)</sup> (continued)

1. Guaranteed by characterization results.

t<sub>h(SD\_A\_MT)</sub>

2. APB clock frequency must be at least twice SAI clock frequency.

Figure 37. SAI master timing waveforms

## 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: <a href="https://www.st.com">www.st.com</a>. ECOPACK<sup>®</sup> is an ST trademark.

## 7.1 LQFP100 package information

1. Drawing is not to scale.

Table 102. LQPF100 - 100-pin, 14 x 14 mm low-profile quad flat package mechanical data

| Symbol | millimeters |     |       | inches <sup>(1)</sup> |     |        |

|--------|-------------|-----|-------|-----------------------|-----|--------|

|        | Min         | Тур | Max   | Min                   | Тур | Max    |

| Α      | -           | -   | 1.600 | -                     | -   | 0.0630 |

| A1     | 0.050       | -   | 0.150 | 0.0020                | -   | 0.0059 |

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Figure 43. LQFP100 marking (package top view)

Parts marked as ES or E or accompanied by an Engineering Sample notification letter are not yet qualified

and therefore not approved for use in production. ST is not responsible for any consequences resulting

from such use. In no event will ST be liable for the customer using any of these engineering samples in

production. ST's Quality department must be contacted prior to any decision to use these engineering

samples to run a qualification activity.

DS11912 Rev 4 191/212