Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                 |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, PWM, WDT                                           |

| Number of I/O              | 83                                                                              |

| Program Memory Size        | 256KB (256K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 160K × 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                    |

| Data Converters            | A/D 16x12b; D/A 1x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-UFBGA                                                                       |

| Supplier Device Package    | 100-UFBGA (7x7)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l452vci6           |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

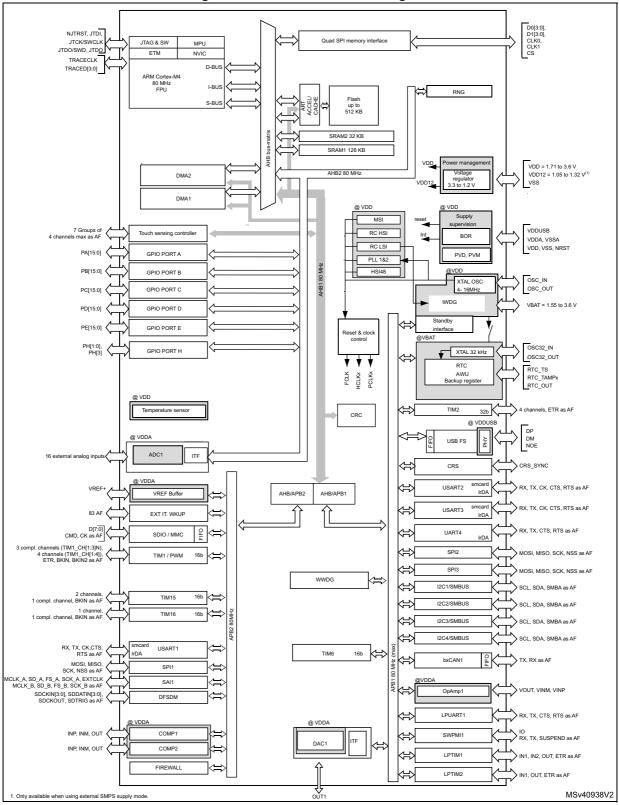

# 2 Description

The STM32L452xx devices are the ultra-low-power microcontrollers based on the highperformance Arm<sup>®</sup> Cortex<sup>®</sup>-M4 32-bit RISC core operating at a frequency of up to 80 MHz. The Cortex-M4 core features a Floating point unit (FPU) single precision which supports all Arm<sup>®</sup> single-precision data-processing instructions and data types. It also implements a full set of DSP instructions and a memory protection unit (MPU) which enhances application security.

The STM32L452xx devices embed high-speed memories (Flash memory up to 512 Kbyte, 160 Kbyte of SRAM), a Quad SPI flash memories interface (available on all packages) and an extensive range of enhanced I/Os and peripherals connected to two APB buses, two AHB buses and a 32-bit multi-AHB bus matrix.

The STM32L452xx devices embed several protection mechanisms for embedded Flash memory and SRAM: readout protection, write protection, proprietary code readout protection and Firewall.

The devices offer a fast 12-bit ADC (5 Msps), two comparators, one operational amplifier, one DAC channel, an internal voltage reference buffer, a low-power RTC, one general-purpose 32-bit timer, one 16-bit PWM timer dedicated to motor control, four general-purpose 16-bit timers, and two 16-bit low-power timers.

In addition, up to 21 capacitive sensing channels are available.

They also feature standard and advanced communication interfaces.

- Four I2Cs

- Three SPIs

- Three USARTs, one UART and one Low-Power UART.

- One SAI (Serial Audio Interfaces)

- One SDMMC

- One CAN

- One USB full-speed device crystal less

The STM32L452xx operates in the -40 to +85 °C (+105 °C junction) and -40 to +125 °C (+130 °C junction) temperature ranges from a 1.71 to 3.6 V V<sub>DD</sub> power supply when using internal LDO regulator and a 1.05 to 1.32V V<sub>DD12</sub> power supply when using external SMPS supply. A comprehensive set of power-saving modes allows the design of low-power applications.

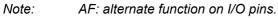

Some independent power supplies are supported: analog independent supply input for ADC, DAC, OPAMP and comparators. A VBAT input allows to backup the RTC and backup registers. Dedicated  $V_{DD12}$  power supplies can be used to bypass the internal LDO regulator when connected to an external SMPS.

The STM32L452xx family offers six packages from 48 to 100-pin packages.

|                                   | able 2. STM32<br>ripheral                      |             | <br>L452Vx | STM32I              |        | 1     | L452Cx  |  |  |  |  |  |

|-----------------------------------|------------------------------------------------|-------------|------------|---------------------|--------|-------|---------|--|--|--|--|--|

| Flash mem                         | nory                                           | 256KB       | 512KB      | 256KB               | 512KB  | 256KB | 512KB   |  |  |  |  |  |

| SRAM                              |                                                |             |            | 160                 | KB     |       |         |  |  |  |  |  |

| Quad SPI                          |                                                | Yes         |            |                     |        |       |         |  |  |  |  |  |

|                                   | Advanced control                               |             |            | 1 (16               | S-bit) |       |         |  |  |  |  |  |

|                                   | General<br>purpose                             |             |            | 2 (16<br>1 (32      |        |       |         |  |  |  |  |  |

|                                   | Basic                                          |             |            | 2 (16               | S-bit) |       |         |  |  |  |  |  |

| Timers                            | Low -power                                     |             |            | 2 (16               | S-bit) |       |         |  |  |  |  |  |

|                                   | SysTick timer                                  |             |            | 1                   |        |       |         |  |  |  |  |  |

|                                   | Watchdog<br>timers<br>(independent,<br>window) |             | 2          |                     |        |       |         |  |  |  |  |  |

|                                   | SPI                                            |             | 3          |                     |        |       |         |  |  |  |  |  |

|                                   | l <sup>2</sup> C                               | 4           |            |                     |        |       |         |  |  |  |  |  |

| Comm.                             | USART<br>UART<br>LPUART                        | 3<br>1<br>1 |            |                     |        |       |         |  |  |  |  |  |

| interfaces                        | SAI                                            | 1           |            |                     |        |       |         |  |  |  |  |  |

|                                   | CAN                                            | 1           |            |                     |        |       |         |  |  |  |  |  |

|                                   | USB FS                                         |             |            | Ye                  | es     |       |         |  |  |  |  |  |

|                                   | SDMMC                                          |             | Ye         | s <sup>(1)</sup>    |        | N     | 10      |  |  |  |  |  |

| RTC                               |                                                |             |            | Ye                  | es     |       |         |  |  |  |  |  |

| Tamper pir                        | IS                                             |             | 3          | 2                   | 2      |       | 2       |  |  |  |  |  |

| Random g                          | enerator                                       |             |            | Ye                  | es     |       |         |  |  |  |  |  |

| GPIOs <sup>(2)</sup><br>Wakeup pi | ns                                             |             | 33<br>5    | 5<br>4 <sup>(</sup> |        |       | 38<br>3 |  |  |  |  |  |

| Capacitive<br>Number of           | -                                              | 2           | 21         | 1                   | 2      |       | 6       |  |  |  |  |  |

| 12-bit ADC<br>Number of           |                                                |             | 1<br>6     | 1<br>16             |        |       | 1<br> 0 |  |  |  |  |  |

| 12-bit DAC                        | channels                                       |             |            | 1                   |        |       |         |  |  |  |  |  |

| Internal vol<br>buffer            | Itage reference                                | Yes No      |            |                     |        |       |         |  |  |  |  |  |

| Analog cor                        | nparator                                       |             |            | 2                   | 2      |       |         |  |  |  |  |  |

| Operationa                        | al amplifiers                                  |             |            | 1                   |        |       |         |  |  |  |  |  |

| Max. CPU                          | frequency                                      |             |            | 80 N                | ЛНz    |       |         |  |  |  |  |  |

Table 2. STM32L452xx family device features and peripheral counts

Figure 1. STM32L452xx block diagram

#### STM32L452xx

- *Note:* If these supplies are tied to ground, the I/Os supplied by these power supplies are not 5 V tolerant.

- Note:  $V_{DDIOx}$  is the I/Os general purpose digital functions supply.  $V_{DDIOx}$  represents  $V_{DDIO1}$ , with  $V_{DDIO1} = V_{DD}$ .

Figure 2. Power supply overview

During power-up and power-down phases, the following power sequence requirements must be respected:

- When  $V_{DD}$  is below 1 V, other power supplies (V\_{DDA}) must remain below V\_{DD} + 300 mV.

- When V<sub>DD</sub> is above 1 V, all power supplies are independent.

During the power-down phase,  $V_{DD}$  can temporarily become lower than other supplies only if the energy provided to the MCU remains below 1 mJ; this allows external decoupling capacitors to be discharged with different time constants during the power- down transient phase.

#### • Shutdown mode

The Shutdown mode allows to achieve the lowest power consumption. The internal regulator is switched off so that the  $V_{CORE}$  domain is powered off. The PLL, the HSI16, the MSI, the LSI and the HSE oscillators are also switched off.

The RTC can remain active (Shutdown mode with RTC, Shutdown mode without RTC).

The BOR is not available in Shutdown mode. No power voltage monitoring is possible in this mode, therefore the switch to Backup domain is not supported.

SRAM1, SRAM2 and register contents are lost except for registers in the Backup domain.

The device exits Shutdown mode when an external reset (NRST pin), a WKUP pin event (configurable rising or falling edge), or an RTC event occurs (alarm, periodic wakeup, timestamp, tamper).

The system clock after wakeup is MSI at 4 MHz.

interrupt is generated if enabled. LSE failure can also be detected and generated an interrupt.

- Clock-out capability:

- MCO: microcontroller clock output: it outputs one of the internal clocks for external use by the application. Low frequency clocks (LSI, LSE) are available down to Stop 1 low power state.

- LSCO: low speed clock output: it outputs LSI or LSE in all low-power modes down to Standby mode. LSE can also be output on LSCO in Shutdown mode. LSCO is not available in VBAT mode.

Several prescalers allow to configure the AHB frequency, the high speed APB (APB2) and the low speed APB (APB1) domains. The maximum frequency of the AHB and the APB domains is 80 MHz.

# 3.14 Interrupts and events

# 3.14.1 Nested vectored interrupt controller (NVIC)

The devices embed a nested vectored interrupt controller able to manage 16 priority levels, and handle up to 67 maskable interrupt channels plus the 16 interrupt lines of the  $Cortex^{\mathbb{B}}$ -M4.

The NVIC benefits are the following:

- Closely coupled NVIC gives low latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Allows early processing of interrupts

- Processing of late arriving higher priority interrupts

- Support for tail chaining

- Processor state automatically saved on interrupt entry, and restored on interrupt exit, with no instruction overhead

The NVIC hardware block provides flexible interrupt management features with minimal interrupt latency.

# 3.14.2 Extended interrupt/event controller (EXTI)

The extended interrupt/event controller consists of 37 edge detector lines used to generate interrupt/event requests and wake-up the system from Stop mode. Each external line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The internal lines are connected to peripherals with wakeup from Stop mode capability. The EXTI can detect an external line with a pulse width shorter than the internal clock period. Up to 83 GPIOs can be connected to the 16 external interrupt lines.

|   |                              |      | -   |                      |          |     |                 |                         |             |                       |                       |      |

|---|------------------------------|------|-----|----------------------|----------|-----|-----------------|-------------------------|-------------|-----------------------|-----------------------|------|

|   | 1                            | 2    | 3   | 4                    | 5        | 6   | 7               | 8                       | 9           | 10                    | 11                    | 12   |

| A | PE3                          | PE1  | PB8 | PH3-BOOT0<br>(BOOT0) | PD7      | PD5 | PB4<br>(NJTRST) | PB3 (JTDO/<br>TRACESWO) | PA15 (JTDI) | PA14 (JTCK/<br>SWCLK) | PA13 (JTMS/<br>SWDIO) | PA12 |

| В | PE4                          | PE2  | PB9 | PB7                  | PB6      | PD6 | PD4             | PD3                     | PD1         | PC12                  | PC10                  | PA11 |

| с | PC13                         | PE5  | PE0 | VDD                  | PB5      |     |                 | PD2                     | PD0         | PC11                  | VDDUSB                | PA10 |

| D | PC14-<br>OSC32_IN<br>(PC14)  | PE6  | VSS |                      | UFBGA100 |     |                 |                         |             |                       |                       | PC9  |

| E | PC15-<br>OSC32_OUT<br>(PC15) | VBAT | vss |                      |          |     |                 |                         |             |                       |                       | PC6  |

| F | PH0-OSC_IN<br>(PH0)          | VSS  |     | -                    |          |     |                 |                         |             |                       |                       | VSS  |

| G | PH1-<br>OSC_OUT<br>(PH1)     | VDD  |     | _                    |          |     |                 |                         |             |                       |                       | VDD  |

| н | PC0                          | NRST | VDD |                      |          |     |                 |                         |             | PD15                  | PD14                  | PD13 |

| J | VSSA                         | PC1  | PC2 |                      |          | _   |                 |                         |             | PD12                  | PD11                  | PD10 |

| к | VREF-                        | PC3  | PA2 | PA5                  | PC4      |     |                 | PD9                     | PD8         | PB15                  | PB14                  | PB13 |

| L | VREF+                        | PA0  | PA3 | PA6                  | PC5      | PB2 | PE8             | PE10                    | PE12        | PB10                  | PB11                  | PB12 |

| м | VDDA                         | PA1  | PA4 | PA7                  | PB0      | PB1 | PE7             | PE9                     | PE11        | PE13                  | PE14                  | PE15 |

|   |                              |      |     |                      |          |     |                 |                         |             |                       |                       | MSv4 |

Figure 7. STM32L452Vx UFBGA100 ballout<sup>(1)</sup>

1. The above figure shows the package top view.

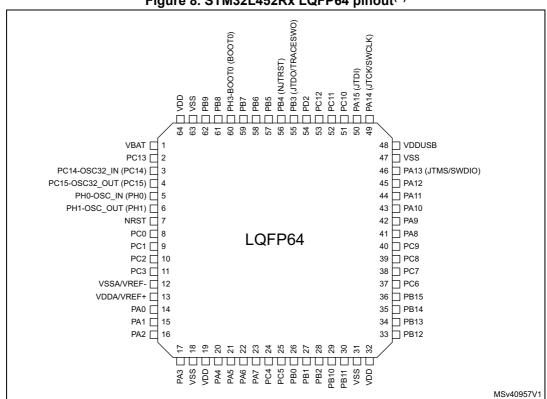

Figure 8. STM32L452Rx LQFP64 pinout<sup>(1)</sup>

1. The above figure shows the package top view.

|   | 1      | 2                     | 3                     | 4                       | 5   | 6                    | 7                            | 8                           |

|---|--------|-----------------------|-----------------------|-------------------------|-----|----------------------|------------------------------|-----------------------------|

| A | VDDUSB | PA15 (JTDI)           | PC12                  | PB4<br>(NJTRST)         | PB7 | PB8                  | VSS                          | VDD                         |

| В | vss    | VDD                   | PC11                  | PB3 (JTDO/<br>TRACESWO) | PB6 | PH3-BOOT0<br>(BOOT0) | VBAT                         | PC13                        |

| c | PA10   | PA13 (JTMS/<br>SWDIO) | PA14 (JTCK/<br>SWCLK) | PD2                     | PB5 | PB9                  | PC15-<br>OSC32_OUT<br>(PC15) | PC14-<br>OSC32_IN<br>(PC14) |

| D | PA9    | PA11                  | PA12                  | PC10                    | PC1 | PC2                  | PC0                          | PH0-OSC_IN<br>(PH0)         |

| E | PC7    | PC9                   | PA8                   | PC4                     | PA7 | PA1                  | PC3                          | PH1-<br>OSC_OUT<br>(PH1)    |

| F | PB15   | PC6                   | PC8                   | PB1                     | PA5 | PA3                  | VDDA/VREF+                   | NRST                        |

| G | PB14   | PB13                  | PB12                  | PB2                     | PC5 | PA4                  | PA2                          | VSSA/VREF-                  |

| н | VDD    | VSS                   | PB11                  | PB10                    | PB0 | PA6                  | VDD                          | PA0                         |

|   |        |                       |                       |                         |     |                      |                              |                             |

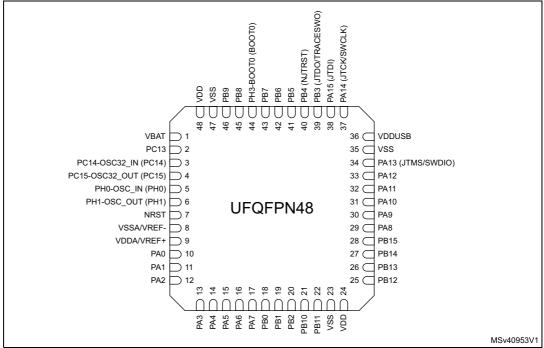

Figure 11. STM32L452Rx WLCSP64 pinout<sup>(1)</sup>

1. The above figure shows the package top view.

1. The above figure shows the package top view.

|                 |         | Piı    | n Nu        | ımbe    | r       |          |                                          |          | •             |       | Pin functions                                                                                               |                      |  |

|-----------------|---------|--------|-------------|---------|---------|----------|------------------------------------------|----------|---------------|-------|-------------------------------------------------------------------------------------------------------------|----------------------|--|

| <b>UFQFPN48</b> | WLCSP64 | LQFP64 | LQFP64 SMPS | UFBGA64 | LQFP100 | UFBGA100 | Pin name<br>(function<br>after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                         | Additional functions |  |

| 28              | F1      | 36     | 36          | F7      | 54      | K10      | PB15                                     | I/O      | FT            | -     | RTC_REFIN,<br>TIM1_CH3N,<br>SPI2_MOSI,<br>DFSDM1_CKIN2,<br>TSC_G1_IO4,<br>SAI1_SD_A,<br>TIM15_CH2, EVENTOUT | -                    |  |

| -               | -       | -      | -           | -       | 55      | K9       | PD8                                      | I/O      | FT            | -     | USART3_TX,<br>EVENTOUT                                                                                      | -                    |  |

| -               | -       | -      | -           | -       | 56      | K8       | PD9                                      | I/O      | FT            | -     | USART3_RX,<br>EVENTOUT                                                                                      | -                    |  |

| -               | -       | -      | -           | -       | 57      | J12      | PD10                                     | I/O      | FT            | -     | USART3_CK,<br>TSC_G6_IO1,<br>EVENTOUT                                                                       | -                    |  |

| -               | -       | -      | -           | -       | 58      | J11      | PD11                                     | I/O      | FT            | -     | I2C4_SMBA,<br>USART3_CTS,<br>TSC_G6_IO2,<br>LPTIM2_ETR,<br>EVENTOUT                                         | -                    |  |

| -               | -       | -      | -           | -       | 59      | J10      | PD12                                     | I/O      | FT            | -     | I2C4_SCL,<br>USART3_RTS_DE,<br>TSC_G6_IO3,<br>LPTIM2_IN1,<br>EVENTOUT                                       | -                    |  |

| -               | -       | -      | -           | -       | 60      | H12      | PD13                                     | I/O      | FT            | -     | I2C4_SDA,<br>TSC_G6_IO4,<br>LPTIM2_OUT,<br>EVENTOUT                                                         | -                    |  |

| -               | -       | -      | -           | -       | 61      | H11      | PD14                                     | I/O      | FT            | -     | EVENTOUT                                                                                                    | -                    |  |

| -               | -       | -      | -           | -       | 62      | H10      | PD15                                     | I/O      | FT            | -     | EVENTOUT                                                                                                    | -                    |  |

| -               | F2      | 37     | 37          | F6      | 63      | E12      | PC6                                      | I/O      | FT            | -     | TIM3_CH1,<br>DFSDM1_CKIN3,<br>TSC_G4_IO1,<br>SDMMC1_D6,<br>EVENTOUT                                         | -                    |  |

| -               | E1      | 38     | 38          | E7      | 64      | E11      | PC7                                      | I/O      | FT            | -     | TIM3_CH2,<br>DFSDM1_DATIN3,<br>TSC_G4_IO2,<br>SDMMC1_D7,<br>EVENTOUT                                        | _                    |  |

Table 16. STM32L452xx pin definitions (continued)

STM32L452xx

Pinouts and pin description

|        |      |                   | Tabl                | e 17. Alternate                | function AF0 to           | o AF7 <sup>(1)</sup> (conti | nued)          |                      |                              |  |

|--------|------|-------------------|---------------------|--------------------------------|---------------------------|-----------------------------|----------------|----------------------|------------------------------|--|

|        |      | AF0               | AF1                 | AF2                            | AF3                       | AF4                         | AF5            | AF6                  | AF7                          |  |

| Po     | ort  | SYS_AF            | TIM1/TIM2<br>LPTIM1 | <b>I2C4/TIM1/</b><br>TIM2/TIM3 | I2C4/USART2/<br>CAN1/TIM1 | 2C1/ 2C2/<br> 2C3/ 2C4      | SPI1/SPI2/I2C4 | SPI3/DFSDM/<br>COMP1 | USART1/<br>USART2/<br>USART3 |  |

|        | PB0  | -                 | TIM1_CH2N           | TIM3_CH3                       | -                         | -                           | SPI1_NSS       | DFSDM1_<br>CKIN0     | USART3_CK                    |  |

|        | PB1  | -                 | TIM1_CH3N           | TIM3_CH4                       | -                         | -                           | -              | DFSDM1_<br>DATIN0    | USART3_RTS_<br>DE            |  |

|        | PB2  | RTC_OUT           | LPTIM1_OUT          | -                              | -                         | I2C3_SMBA                   | -              | DFSDM1_<br>CKIN0     | -                            |  |

|        | PB3  | JTDO/<br>TRACESWO | TIM2_CH2            | -                              | -                         | -                           | SPI1_SCK       | SPI3_SCK             | USART1_RTS_<br>DE            |  |

|        | PB4  | NJTRST            | -                   | TIM3_CH1                       | -                         | I2C3_SDA                    | SPI1_MISO      | SPI3_MISO            | USART1_CTS                   |  |

|        | PB5  | -                 | LPTIM1_IN1          | TIM3_CH2                       | CAN1_RX                   | I2C1_SMBA                   | SPI1_MOSI      | SPI3_MOSI            | USART1_CK                    |  |

|        | PB6  | -                 | LPTIM1_ETR          | -                              | -                         | I2C1_SCL                    | I2C4_SCL       | -                    | USART1_TX                    |  |

| Port B | PB7  | -                 | LPTIM1_IN2          | -                              | -                         | I2C1_SDA                    | I2C4_SDA       | -                    | USART1_RX                    |  |

| POILE  | PB8  | -                 | -                   | -                              | -                         | I2C1_SCL                    | -              | -                    | -                            |  |

|        | PB9  | -                 | IR_OUT              | -                              | -                         | I2C1_SDA                    | SPI2_NSS       | -                    | -                            |  |

|        | PB10 | -                 | TIM2_CH3            | -                              | I2C4_SCL                  | I2C2_SCL                    | SPI2_SCK       | -                    | USART3_TX                    |  |

|        | PB11 | -                 | TIM2_CH4            | -                              | I2C4_SDA                  | I2C2_SDA                    | -              | -                    | USART3_RX                    |  |

|        | PB12 | -                 | TIM1_BKIN           | -                              | TIM1_BKIN_C<br>OMP2       | I2C2_SMBA                   | SPI2_NSS       | DFSDM1_<br>DATIN1    | USART3_CK                    |  |

|        | PB13 | -                 | TIM1_CH1N           | -                              | -                         | I2C2_SCL                    | SPI2_SCK       | DFSDM1_<br>CKIN1     | USART3_CTS                   |  |

|        | PB14 | -                 | TIM1_CH2N           | -                              | -                         | I2C2_SDA                    | SPI2_MISO      | DFSDM1_<br>DATIN2    | USART3_RTS_<br>DE            |  |

|        | PB15 | RTC_REFIN         | TIM1_CH3N           | -                              | -                         | -                           | SPI2_MOSI      | DFSDM1_<br>CKIN2     | -                            |  |

DS11912 Rev 4

577

73/212

#### **Prequalification trials**

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

## **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

| Symbol           | Parameter  | Conditions                                                                           | Monitored<br>frequency band | Max vs.<br>[f <sub>HSE</sub> /f <sub>HCLK</sub> ] | Unit |  |

|------------------|------------|--------------------------------------------------------------------------------------|-----------------------------|---------------------------------------------------|------|--|

|                  |            |                                                                                      | noquonoy bana               | 8 MHz/ 80 MHz                                     |      |  |

|                  | Peak level | $V_{DD}$ = 3.6 V, $T_A$ = 25 °C,<br>LQFP100 package<br>compliant with IEC<br>61967-2 | 0.1 MHz to 30 MHz           | -8                                                |      |  |

|                  |            |                                                                                      | 30 MHz to 130 MHz           | 2                                                 | dBµV |  |

| S <sub>EMI</sub> |            |                                                                                      | 130 MHz to 1 GHz            | 5                                                 |      |  |

|                  |            |                                                                                      | 1 GHz to 2 GHz              | 8                                                 |      |  |

|                  |            |                                                                                      | EMI Level                   | 2.5                                               | -    |  |

Table 67. EMI characteristics

# 6.3.12 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

## Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the ANSI/JEDEC standard.

| Symbol                | Ratings                                                     | Conditions                                                         | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------------|--------------------------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)          | $T_A = +25 \degree C$ , conforming<br>to ANSI/ESDA/JEDEC<br>JS-001 | 2     | 2000                            | V    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge<br>voltage (charge device<br>model) | $T_A = +25$ °C,<br>conforming to ANSI/ESD<br>STM5.3.1              | C3    | 250                             | v    |

1. Guaranteed by characterization results.

### Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin.

- A current injection is applied to each input, output and configurable I/O pin.

These tests are compliant with EIA/JESD 78A IC latch-up standard.

| Table | 69. | Electrical | sensitivities  |

|-------|-----|------------|----------------|

| Table | 00. | LICCUICAI  | 30113111411103 |

| Symbol | Parameter             | Conditions                            | Class |

|--------|-----------------------|---------------------------------------|-------|

| LU     | Static latch-up class | $T_A$ = +105 °C conforming to JESD78A | II    |

## 6.3.13 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DDIOx}$  (for standard, 3.3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (higher than 5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of the -5  $\mu$ A/+0  $\mu$ A range) or other functional failure (for example reset occurrence or oscillator frequency deviation).

The characterization results are given in *Table 70*.

Negative induced leakage current is caused by negative injection and positive induced leakage current is caused by positive injection.

| Symbol           | Description                                                              | Func<br>susce      | Unit               |      |

|------------------|--------------------------------------------------------------------------|--------------------|--------------------|------|

| Symbol           | Description                                                              | Negative injection | Positive injection | Unit |

|                  | Injected current on all pins except PA4, PA5, PE8, PE9, PE10, PE11, PE12 | -5                 | N/A <sup>(2)</sup> |      |

| I <sub>INJ</sub> | Injected current on PE8, PE9, PE10, PE11, PE12                           | -0                 | N/A <sup>(2)</sup> | mA   |

|                  | Injected current on PA4, PA5 pins                                        | -5                 | 0                  |      |

Table 70. I/O current injection susceptibility<sup>(1)</sup>

1. Guaranteed by characterization results.

2. Injection is not possible.

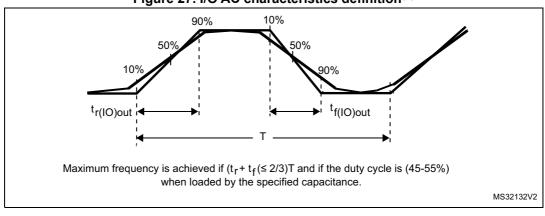

1. Refer to Table 73: I/O AC characteristics.

# 6.3.15 NRST pin characteristics

The NRST pin input driver uses the CMOS technology. It is connected to a permanent pull-up resistor,  $\mathsf{R}_{\mathsf{PU}}.$

Unless otherwise specified, the parameters given in the table below are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 23: General operating conditions*.

| Symbol                 | Parameter                                          | Conditions                        | Min                                 | Тур | Мах                                 | Unit |

|------------------------|----------------------------------------------------|-----------------------------------|-------------------------------------|-----|-------------------------------------|------|

| V <sub>IL(NRST)</sub>  | NRST input low level voltage                       | -                                 | -                                   | -   | 0.3 <sub>x</sub> V <sub>DDIOx</sub> | v    |

| V <sub>IH(NRST)</sub>  | NRST input high level voltage                      | -                                 | 0.7 <sub>x</sub> V <sub>DDIOx</sub> | -   | -                                   | v    |

| V <sub>hys(NRST)</sub> | NRST Schmitt trigger voltage hysteresis            | -                                 | -                                   | 200 | -                                   | mV   |

| R <sub>PU</sub>        | Weak pull-up<br>equivalent resistor <sup>(2)</sup> | V <sub>IN</sub> = V <sub>SS</sub> | 25                                  | 40  | 55                                  | kΩ   |

| V <sub>F(NRST)</sub>   | NRST input filtered<br>pulse                       | -                                 | -                                   | -   | 70                                  | ns   |

| V <sub>NF(NRST)</sub>  | NRST input not filtered pulse                      | 1.71 V ≤ V <sub>DD</sub> ≤ 3.6 V  | 350                                 | -   | -                                   | ns   |

Table 74. NRST pin characteristics<sup>(1)</sup>

1. Guaranteed by design.

2. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is minimal (~10% order).

- 2. The I/O analog switch voltage booster is enable when V<sub>DDA</sub> < 2.4 V (BOOSTEN = 1 in the SYSCFG\_CFGR1 when V<sub>DDA</sub> < 2.4V). It is disable when V<sub>DDA</sub>  $\geq$  2.4 V.

- 3. Fast channels are: PC0, PC1, PC2, PC3, PA0, PA1.

- 4. Slow channels are: all ADC inputs except the fast channels.

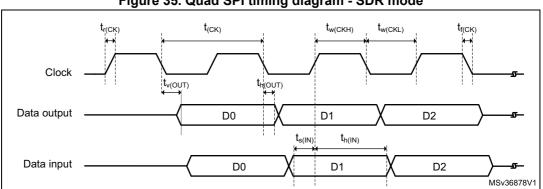

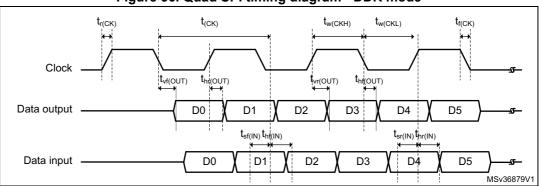

| Symbol               | Parameter                              | Conditions                                                                  | Min                    | Тур   | Max                    | Unit |

|----------------------|----------------------------------------|-----------------------------------------------------------------------------|------------------------|-------|------------------------|------|

| F <sub>ск</sub>      | Quad SPI clock<br>frequency            | $1.71 < V_{DD} < 3.6 V$ , $C_{LOAD} = 20 pF$<br>Voltage Range 1             | -                      | -     | 40                     | MHz  |

|                      |                                        | 2 < V <sub>DD</sub> < 3.6 V, C <sub>LOAD</sub> = 20 pF<br>Voltage Range 1   | -                      | -     | 48                     |      |

| 1/t <sub>(СК)</sub>  |                                        | $1.71 < V_{DD} < 3.6 V$ , $C_{LOAD} = 15 pF$<br>Voltage Range 1             | -                      | -     | 48                     |      |

|                      |                                        | 1.71 < V <sub>DD</sub> < 3.6 V C <sub>LOAD</sub> = 20 pF<br>Voltage Range 2 | -                      | -     | 26                     |      |

| t <sub>w(CKH)</sub>  | Quad SPI clock high                    | f 40 MUL=0                                                                  | t <sub>(CK)</sub> /2-2 | -     | t <sub>(СК)</sub> /2   | ns   |

| t <sub>w(CKL)</sub>  | and low time                           | f <sub>AHBCLK</sub> = 48 MHz, presc=0                                       | t <sub>(CK)</sub> /2   | -     | t <sub>(CK)</sub> /2+2 |      |

| +                    | Data input setup time on rising edge   | Voltage Range 1                                                             | 1                      |       | -                      |      |

| t <sub>sr(IN)</sub>  |                                        | Voltage Range 2                                                             | 3.5                    |       |                        |      |

| +                    | Data input setup time on falling edge  | Voltage Range 1                                                             | 1                      |       | -                      |      |

| t <sub>sf(IN)</sub>  |                                        | Voltage Range 2                                                             | 1.5                    | -     |                        |      |

| +                    | Data input hold time on rising edge    | Voltage Range 1                                                             | 6                      |       | -                      |      |

| t <sub>hr(IN)</sub>  |                                        | Voltage Range 2                                                             | 6.5                    | -     |                        |      |

| +                    | Data input hold time on falling edge   | Voltage Range 1                                                             | 5.5<br>5.5             |       |                        |      |

| t <sub>hf(IN)</sub>  |                                        | Voltage Range 2                                                             |                        | -     | -                      |      |

| 1                    | Data output valid time on rising edge  | Voltage Range 1                                                             |                        | 5     | 5.5                    |      |

| t <sub>vr(OUT)</sub> |                                        | Voltage Range 2                                                             | -                      | 9.5   | 14                     |      |

| 1                    | Data output valid time on falling edge | Voltage Range 1                                                             |                        | 5     | 8.5                    |      |

| t <sub>vf(OUT)</sub> |                                        | Voltage Range 2                                                             | 1 -                    | 15    | 19                     |      |

| +                    | Data output hold time on rising edge   | Voltage Range 1                                                             | 3.5                    |       |                        |      |

| t <sub>hr(OUT)</sub> |                                        | Voltage Range 2                                                             | 8                      |       |                        |      |

| +                    | Data output hold time                  | Voltage Range 1                                                             | 3.5                    | 3.5 - |                        |      |

| t <sub>hf(OUT)</sub> | on falling edge                        | Voltage Range 2                                                             | 13                     | -     |                        |      |

1. Guaranteed by characterization results.

### Figure 36. Quad SPI timing diagram - DDR mode

# **SAI characteristics**

Unless otherwise specified, the parameters given in *Table 98* for SAI are derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 23: General operating conditions*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels:  $0.5 \times V_{DD}$

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (CK,SD,FS).

| Symbol                   | Parameter                          | Conditions                                                            | Min | Мах  | Unit |

|--------------------------|------------------------------------|-----------------------------------------------------------------------|-----|------|------|

| f <sub>MCLK</sub>        | SAI Main clock output              | -                                                                     | -   | 50   | MHz  |

| fск                      | SAI clock frequency <sup>(2)</sup> | Master transmitter<br>2.7 ≤ V <sub>DD</sub> ≤ 3.6<br>Voltage Range 1  | -   | 18.5 | MHz  |

|                          |                                    | Master transmitter<br>1.71 ≤ V <sub>DD</sub> ≤ 3.6<br>Voltage Range 1 | -   | 12.5 |      |

|                          |                                    | Master receiver<br>Voltage Range 1                                    | -   | 25   |      |

|                          |                                    | Slave transmitter<br>2.7 ≤ V <sub>DD</sub> ≤ 3.6<br>Voltage Range 1   | -   | 22.5 |      |

|                          |                                    | Slave transmitter<br>1.71 ≤ V <sub>DD</sub> ≤ 3.6<br>Voltage Range 1  | -   | 14.5 |      |

|                          |                                    | Slave receiver<br>Voltage Range 1                                     | -   | 25   |      |

|                          |                                    | Voltage Range 2                                                       | -   | 12.5 |      |

| +                        | FS valid time                      | Master mode<br>2.7 $\leq$ V <sub>DD</sub> $\leq$ 3.6                  | -   | 22   |      |

| t <sub>v(FS)</sub>       |                                    | Master mode<br>$1.71 \le V_{DD} \le 3.6$                              | -   | 40   | ns   |

| t <sub>h(FS)</sub>       | FS hold time                       | Master mode                                                           | 10  | -    | ns   |

| t <sub>su(FS)</sub>      | FS setup time                      | Slave mode                                                            | 1   | -    | ns   |

| t <sub>h(FS)</sub>       | FS hold time                       | Slave mode                                                            | 2   | -    | ns   |

| t <sub>su(SD_A_MR)</sub> | Data input actus time              | Master receiver                                                       | 2   | -    | ns   |

| t <sub>su(SD_B_SR)</sub> | Data input setup time              | Slave receiver                                                        | 1.5 | -    |      |

| t <sub>h(SD_A_MR)</sub>  | Data input hold time               | Master receiver                                                       | 5   | -    | ns   |

| t <sub>h(SD_B_SR)</sub>  |                                    | Slave receiver                                                        | 2.5 | -    |      |

## Table 98. SAI characteristics<sup>(1)</sup>

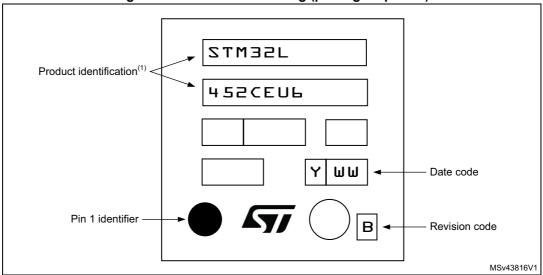

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as ES or E or accompanied by an Engineering Sample notification letter are not yet qualified and therefore not approved for use in production. ST is not responsible for any consequences resulting from such use. In no event will ST be liable for the customer using any of these engineering samples in production. ST's Quality department must be contacted prior to any decision to use these engineering samples to run a qualification activity.