Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                 |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, PWM, WDT                                           |

| Number of I/O              | 83                                                                              |

| Program Memory Size        | 512KB (512K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 160K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                    |

| Data Converters            | A/D 16x12b; D/A 1x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-UFBGA                                                                       |

| Supplier Device Package    | 100-UFBGA (7x7)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l452vei6           |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                                  |                  |                  | Ionantie             |                        |     | o 0/1             |     | p 2               | Stan             |                   | Shut | down              |      |

|--------------------------------------------------|------------------|------------------|----------------------|------------------------|-----|-------------------|-----|-------------------|------------------|-------------------|------|-------------------|------|

| Peripheral                                       | Run              | Sleep            | Low-<br>power<br>run | Low-<br>power<br>sleep | -   | Wakeup capability | -   | Wakeup capability | -                | Wakeup capability | -    | Wakeup capability | VBAT |

| CPU                                              | Y                | -                | Y                    | -                      | -   | -                 | -   | -                 | -                | -                 | -    | -                 | -    |

| Flash memory (up to 512 KB)                      | O <sup>(2)</sup> | O <sup>(2)</sup> | O <sup>(2)</sup>     | O <sup>(2)</sup>       | -   | -                 | -   | -                 | -                | -                 | -    | -                 | -    |

| SRAM1 (128 KB)                                   | Y                | Y <sup>(3)</sup> | Y                    | Y <sup>(3)</sup>       | Y   | -                 | Y   | -                 | -                | -                 | -    | -                 | -    |

| SRAM2 (32 KB)                                    | Y                | Y <sup>(3)</sup> | Y                    | Y <sup>(3)</sup>       | Y   | -                 | Y   | -                 | O <sup>(4)</sup> | -                 | -    | -                 | -    |

| Quad SPI                                         | 0                | 0                | 0                    | 0                      | -   | -                 | -   | -                 | -                | -                 | -    | -                 | -    |

| Backup Registers                                 | Y                | Y                | Y                    | Y                      | Y   | -                 | Y   | -                 | Y                | -                 | Y    | -                 | Y    |

| Brown-out reset<br>(BOR)                         | Y                | Y                | Y                    | Y                      | Y   | Y                 | Y   | Y                 | Y                | Y                 | -    | -                 | -    |

| Programmable<br>Voltage Detector<br>(PVD)        | 0                | 0                | 0                    | 0                      | 0   | 0                 | 0   | 0                 | -                | -                 | -    | -                 | -    |

| Peripheral Voltage<br>Monitor (PVMx;<br>x=1,3,4) | 0                | 0                | 0                    | 0                      | 0   | 0                 | 0   | 0                 | -                | -                 | -    | -                 | -    |

| DMA                                              | 0                | 0                | 0                    | 0                      | -   | -                 | -   | -                 | -                | -                 | -    | -                 | -    |

| High Speed Internal<br>(HSI16)                   | 0                | 0                | 0                    | 0                      | (5) | -                 | (5) | -                 | -                | -                 | -    | -                 | -    |

| Oscillator RC48                                  | 0                | 0                | -                    | -                      | -   | -                 | -   | -                 | -                | -                 | -    | -                 | -    |

| High Speed External<br>(HSE)                     | 0                | 0                | 0                    | 0                      | -   | -                 | -   | -                 | -                | -                 | -    | -                 | -    |

| Low Speed Internal<br>(LSI)                      | 0                | 0                | 0                    | 0                      | 0   | -                 | 0   | -                 | 0                | -                 | -    | -                 | -    |

| Low Speed External (LSE)                         | 0                | 0                | 0                    | 0                      | 0   | -                 | 0   | -                 | 0                | -                 | 0    | -                 | 0    |

| Multi-Speed Internal<br>(MSI)                    | 0                | 0                | 0                    | 0                      | -   | -                 | -   | -                 | -                | -                 | -    | -                 | -    |

| Clock Security<br>System (CSS)                   | 0                | 0                | 0                    | 0                      | -   | -                 | -   | -                 | -                | -                 | -    | -                 | -    |

| Clock Security<br>System on LSE                  | 0                | 0                | 0                    | 0                      | 0   | 0                 | 0   | 0                 | 0                | 0                 | -    | -                 | -    |

| RTC / Auto wakeup                                | 0                | 0                | 0                    | 0                      | 0   | 0                 | 0   | 0                 | 0                | 0                 | 0    | 0                 | 0    |

| Number of RTC<br>Tamper pins                     | 3                | 3                | 3                    | 3                      | 3   | 0                 | 3   | 0                 | 3                | 0                 | 3    | 0                 | 3    |

Table 5. Functionalities depending on the working mode<sup>(1)</sup>

# 3.14 Interrupts and events

### 3.14.1 Nested vectored interrupt controller (NVIC)

The devices embed a nested vectored interrupt controller able to manage 16 priority levels, and handle up to 67 maskable interrupt channels plus the 16 interrupt lines of the  $Cortex^{\mathbb{B}}$ -M4.

The NVIC benefits are the following:

- Closely coupled NVIC gives low latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Allows early processing of interrupts

- Processing of late arriving higher priority interrupts

- Support for tail chaining

- Processor state automatically saved on interrupt entry, and restored on interrupt exit, with no instruction overhead

The NVIC hardware block provides flexible interrupt management features with minimal interrupt latency.

### 3.14.2 Extended interrupt/event controller (EXTI)

The extended interrupt/event controller consists of 37 edge detector lines used to generate interrupt/event requests and wake-up the system from Stop mode. Each external line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The internal lines are connected to peripherals with wakeup from Stop mode capability. The EXTI can detect an external line with a pulse width shorter than the internal clock period. Up to 83 GPIOs can be connected to the 16 external interrupt lines.

# 3.15 Analog to digital converter (ADC)

The device embeds a successive approximation analog-to-digital converter with the following features:

- 12-bit native resolution, with built-in calibration

- 5.33 Msps maximum conversion rate with full resolution

- Down to 18.75 ns sampling time

- Increased conversion rate for lower resolution (up to 8.88 Msps for 6-bit resolution)

- Up to 16 external channels.

- 4 internal channels: internal reference voltage, temperature sensor, VBAT/3 and DAC1\_OUT1.

- One external reference pin is available on some package, allowing the input voltage range to be independent from the power supply

- Single-ended and differential mode inputs

- Low-power design

- Capable of low-current operation at low conversion rate (consumption decreases linearly with speed)

- Dual clock domain architecture: ADC speed independent from CPU frequency

- Highly versatile digital interface

- Single-shot or continuous/discontinuous sequencer-based scan mode: 2 groups of analog signals conversions can be programmed to differentiate background and high-priority real-time conversions

- ADC supports multiple trigger inputs for synchronization with on-chip timers and external signals

- Results stored into data register or in RAM with DMA controller support

- Data pre-processing: left/right alignment and per channel offset compensation

- Built-in oversampling unit for enhanced SNR

- Channel-wise programmable sampling time

- Three analog watchdog for automatic voltage monitoring, generating interrupts and trigger for selected timers

- Hardware assistant to prepare the context of the injected channels to allow fast context switching

### 3.15.1 Temperature sensor

The temperature sensor (TS) generates a voltage  $V_{TS}$  that varies linearly with temperature.

The temperature sensor is internally connected to the ADC1\_IN17 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode.

|   |                              |      | -   |                           |             |     |                 |                         |             |                       |                       |      |

|---|------------------------------|------|-----|---------------------------|-------------|-----|-----------------|-------------------------|-------------|-----------------------|-----------------------|------|

|   | 1                            | 2    | 3   | 4                         | 5           | 6   | 7               | 8                       | 9           | 10                    | 11                    | 12   |

| A | PE3                          | PE1  | PB8 | PH3-BOOT0<br>(BOOT0)      | PD7         | PD5 | PB4<br>(NJTRST) | PB3 (JTDO/<br>TRACESWO) | PA15 (JTDI) | PA14 (JTCK/<br>SWCLK) | PA13 (JTMS/<br>SWDIO) | PA12 |

| В | PE4                          | PE2  | PB9 | PB7                       | PB6         | PD6 | PD4             | PD3                     | PD1         | PC12                  | PC10                  | PA11 |

| с | PC13                         | PE5  | PE0 | VDD                       | PB5 PD2 PD0 |     |                 |                         |             | PC11                  | VDDUSB                | PA10 |

| D | PC14-<br>OSC32_IN<br>(PC14)  | PE6  | VSS |                           |             | PA9 | PA8             | PC9                     |             |                       |                       |      |

| E | PC15-<br>OSC32_OUT<br>(PC15) | VBAT | vss |                           |             | PC7 | PC6             |                         |             |                       |                       |      |

| F | PH0-OSC_IN<br>(PH0)          | VSS  |     | -                         | l           |     | VSS             | VSS                     |             |                       |                       |      |

| G | PH1-<br>OSC_OUT<br>(PH1)     | VDD  |     | _                         |             |     | VDD             | VDD                     |             |                       |                       |      |

| н | PC0                          | NRST | VDD |                           |             |     |                 |                         |             | PD15                  | PD14                  | PD13 |

| J | VSSA                         | PC1  | PC2 |                           |             | _   |                 |                         |             | PD12                  | PD11                  | PD10 |

| к | VREF-                        | PC3  | PA2 | PA5                       | PC4         |     |                 | PD9                     | PD8         | PB15                  | PB14                  | PB13 |

| L | VREF+                        | PA0  | PA3 | PA6 PC5 PB2 PE8 PE10 PE12 |             |     |                 |                         |             | PB10                  | PB11                  | PB12 |

| м | VDDA                         | PA1  | PA4 | PA7                       | PB0         | PB1 | PE7             | PE9                     | PE11        | PE13                  | PE14                  | PE15 |

|   |                              |      |     |                           |             |     |                 |                         |             |                       |                       | MSv4 |

Figure 7. STM32L452Vx UFBGA100 ballout<sup>(1)</sup>

1. The above figure shows the package top view.

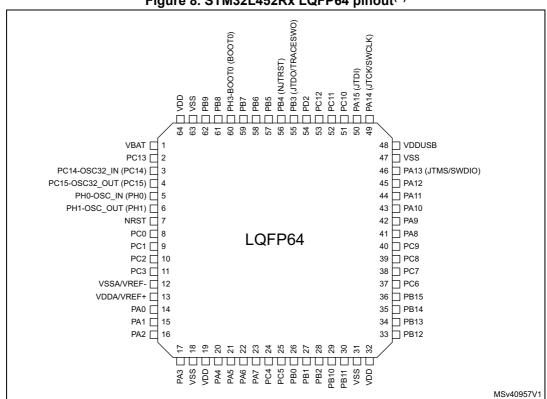

Figure 8. STM32L452Rx LQFP64 pinout<sup>(1)</sup>

1. The above figure shows the package top view.

|          |         | Pi     | n Nu        | ımbe    | r       |          |                                          |          | •             |       | Pin fund                                                                                 | ctions               |

|----------|---------|--------|-------------|---------|---------|----------|------------------------------------------|----------|---------------|-------|------------------------------------------------------------------------------------------|----------------------|

| UFQFPN48 | WLCSP64 | LQFP64 | LQFP64 SMPS | UFBGA64 | LQFP100 | UFBGA100 | Pin name<br>(function<br>after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                      | Additional functions |

| 20       | G4      | 28     | 27          | G6      | 37      | L6       | PB2                                      | I/O      | FT_a          | -     | RTC_OUT, LPTIM1_OUT,<br>I2C3_SMBA,<br>DFSDM1_CKIN0,<br>EVENTOUT                          | COMP1_INP            |

| -        | -       | -      | -           | -       | 38      | M7       | PE7                                      | I/O      | FT            | -     | TIM1_ETR,<br>DFSDM1_DATIN2,<br>SAI1_SD_B, EVENTOUT                                       | -                    |

| -        | -       | -      | -           | -       | 39      | L7       | PE8                                      | I/O      | FT            | -     | TIM1_CH1N,<br>DFSDM1_CKIN2,<br>SAI1_SCK_B,<br>EVENTOUT                                   | -                    |

| -        | -       | -      | -           | -       | 40      | M8       | PE9                                      | I/O      | FT            | -     | TIM1_CH1,<br>DFSDM1_CKOUT,<br>SAI1_FS_B, EVENTOUT                                        | -                    |

| -        | -       | -      | -           | -       | 41      | L8       | PE10                                     | I/O      | FT            | -     | TIM1_CH2N,<br>TSC_G5_IO1,<br>QUADSPI_CLK,<br>SAI1_MCLK_B,<br>EVENTOUT                    | -                    |

| -        | -       | -      | -           | -       | 42      | M9       | PE11                                     | I/O      | FT            | -     | TIM1_CH2,<br>TSC_G5_IO2,<br>QUADSPI_BK1_NCS,<br>EVENTOUT                                 | -                    |

| -        | -       | -      | -           | -       | 43      | L9       | PE12                                     | I/O      | FT            | I     | TIM1_CH3N, SPI1_NSS,<br>TSC_G5_IO3,<br>QUADSPI_BK1_IO0,<br>EVENTOUT                      | -                    |

| -        | -       | -      | -           | _       | 44      | M10      | PE13                                     | I/O      | FT            | I     | TIM1_CH3, SPI1_SCK,<br>TSC_G5_IO4,<br>QUADSPI_BK1_IO1,<br>EVENTOUT                       | -                    |

| -        | -       | -      | -           | -       | 45      | M11      | PE14                                     | I/O      | FT            | -     | TIM1_CH4, TIM1_BKIN2,<br>TIM1_BKIN2_COMP2,<br>SPI1_MISO,<br>QUADSPI_BK1_IO2,<br>EVENTOUT | -                    |

| -        | -       | -      | -           | -       | 46      | M12      | PE15                                     | I/O      | FT            | -     | TIM1_BKIN,<br>TIM1_BKIN_COMP1,<br>SPI1_MOSI,<br>QUADSPI_BK1_IO3,<br>EVENTOUT             | -                    |

Table 16. STM32L452xx pin definitions (continued)

|          |         | Pir    | n Nu        | ımbe    | r       |          |                                          |          |               |       | Pin fund                                                                                                       | ctions               |

|----------|---------|--------|-------------|---------|---------|----------|------------------------------------------|----------|---------------|-------|----------------------------------------------------------------------------------------------------------------|----------------------|

| UFQFPN48 | WLCSP64 | LQFP64 | LQFP64 SMPS | UFBGA64 | LQFP100 | UFBGA100 | Pin name<br>(function<br>after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                            | Additional functions |

| 42       | B5      | 58     | 57          | D3      | 92      | B5       | PB6                                      | I/O      | FT_fa         | -     | LPTIM1_ETR, I2C1_SCL,<br>I2C4_SCL, USART1_TX,<br>CAN1_TX, TSC_G2_IO3,<br>SAI1_FS_B,<br>TIM16_CH1N,<br>EVENTOUT | COMP2_INP            |

| 43       | A5      | 59     | 58          | C3      | 93      | B4       | PB7                                      | I/O      | FT_fa         | -     | LPTIM1_IN2, I2C1_SDA,<br>I2C4_SDA, USART1_RX,<br>UART4_CTS,<br>TSC_G2_IO4,<br>EVENTOUT                         | COMP2_INM, PVD_IN    |

| 44       | B6      | 60     | 59          | B4      | 94      | A4       | PH3-<br>BOOT0<br>(BOOT0)                 | I/O      | FT            | -     | EVENTOUT                                                                                                       | -                    |

| 45       | A6      | 61     | 60          | В3      | 95      | A3       | PB8                                      | I/O      | FT_f          | -     | I2C1_SCL, CAN1_RX,<br>SDMMC1_D4,<br>SAI1_MCLK_A,<br>TIM16_CH1, EVENTOUT                                        | -                    |

| 46       | C6      | 62     | 61          | A3      | 96      | В3       | PB9                                      | I/O      | FT_f          | -     | IR_OUT, I2C1_SDA,<br>SPI2_NSS, CAN1_TX,<br>SDMMC1_D5,<br>SAI1_FS_A, EVENTOUT                                   | -                    |

| -        | -       | -      | 62          | -       | -       | -        | VDD12                                    | S        | -             | -     | -                                                                                                              | -                    |

| -        | -       | -      | -           | -       | 97      | C3       | PE0                                      | I/O      | FT            | -     | TIM16_CH1, EVENTOUT                                                                                            | -                    |

| -        | -       | -      | -           | -       | 98      | A2       | PE1                                      | I/O      | FT            | -     | EVENTOUT                                                                                                       | -                    |

| 47       | A7      | 63     | 63          | D4      | 99      | D3       | VSS                                      | S        | -             | -     | -                                                                                                              | -                    |

| 48       | A8      | 64     | 64          | E4      | 100     | C4       | VDD                                      | S        | -             | -     | -                                                                                                              | -                    |

Table 16. STM32L452xx pin definitions (continued)

PC13, PC14 and PC15 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 in output mode is limited:

The speed should not exceed 2 MHz with a maximum load of 30 pF

These GPIOs must not be used as current sources (e.g. to drive an LED).

After a Backup domain power-up, PC13, PC14 and PC15 operate as GPIOs. Their function then depends on the content of the RTC registers which are not reset by the system reset. For details on how to manage these GPIOs, refer to the Backup domain and RTC register descriptions in the RM0394 reference manual.

3. After reset, these pins are configured as JTAG/SW debug alternate functions, and the internal pull-up on PA15, PA13, PB4 pins and the internal pull-down on PA14 pin are activated.

|        |      |                            | Table      | e 18. Alternate      | function AF8 | to AF15 <sup>(1)</sup> (conti | nued)     |                             |          |

|--------|------|----------------------------|------------|----------------------|--------------|-------------------------------|-----------|-----------------------------|----------|

|        |      | AF8                        | AF9        | AF10                 | AF11         | AF12                          | AF13      | AF14                        | AF15     |

| P      | ort  | UART4/<br>LPUART1/<br>CAN1 | CAN1/TSC   | CAN1/USB/<br>QUADSPI | -            | SDMMC1/<br>COMP1/<br>COMP2    | SAI1      | TIM2/TIM15/<br>TIM16/LPTIM2 | EVENTOUT |

|        | PC0  | LPUART1_RX                 | -          | -                    | -            | -                             | -         | LPTIM2_IN1                  | EVENTOUT |

|        | PC1  | LPUART1_TX                 | -          | -                    | -            | -                             | -         | -                           | EVENTOUT |

|        | PC2  | -                          | -          | -                    | -            | -                             | -         | -                           | EVENTOUT |

|        | PC3  | -                          | -          | -                    | -            | -                             | SAI1_SD_A | LPTIM2_ETR                  | EVENTOUT |

|        | PC4  | -                          | -          | -                    | -            | -                             | -         | -                           | EVENTOUT |

|        | PC5  | -                          | -          | -                    | -            | -                             | -         | -                           | EVENTOUT |

|        | PC6  | -                          | TSC_G4_IO1 | -                    | -            | SDMMC1_D6                     | -         | -                           | EVENTOUT |

| Dent   | PC7  | -                          | TSC_G4_IO2 | -                    | -            | SDMMC1_D7                     | -         | -                           | EVENTOUT |

| Port C | PC8  | -                          | TSC_G4_IO3 | -                    | -            | SDMMC1_D0                     | -         | -                           | EVENTOUT |

|        | PC9  | -                          | TSC_G4_IO4 | USBNOE               | -            | SDMMC1_D1                     | -         | -                           | EVENTOUT |

|        | PC10 | UART4_TX                   | TSC_G3_IO2 | -                    | -            | SDMMC1_D2                     | -         | -                           | EVENTOUT |

|        | PC11 | UART4_RX                   | TSC_G3_IO3 | -                    | -            | SDMMC1_D3                     | -         | -                           | EVENTOUT |

|        | PC12 | -                          | TSC_G3_IO4 | -                    | -            | SDMMC1_CK                     | -         | -                           | EVENTOUT |

|        | PC13 | -                          | -          | -                    | -            | -                             | -         | -                           | EVENTOUT |

|        | PC14 | -                          | -          | -                    | -            | -                             | -         | -                           | EVENTOUT |

|        | PC15 | -                          | -          | -                    | -            | -                             | -         | -                           | EVENTOUT |

DS11912 Rev 4

80/212

# (4)

| Symbol                                | Parameter                                         | Conditions <sup>(1)</sup> | Min  | Тур  | Max  | Unit |

|---------------------------------------|---------------------------------------------------|---------------------------|------|------|------|------|

| V                                     | V <sub>DDA</sub> peripheral voltage               | Rising edge               | 1.78 | 1.82 | 1.86 | V    |

| V <sub>PVM4</sub>                     | monitoring                                        | Falling edge              | 1.77 | 1.81 | 1.85 | v    |

| V <sub>hyst_PVM3</sub>                | PVM3 hysteresis                                   | -                         | -    | 10   | -    | mV   |

| V <sub>hyst_PVM4</sub>                | PVM4 hysteresis                                   | -                         | -    | 10   | -    | mV   |

| I <sub>DD</sub> (PVM1)<br>(2)         | PVM1 consumption from $V_{DD}$                    | -                         | -    | 0.2  | -    | μA   |

| I <sub>DD</sub><br>(PVM3/PVM4)<br>(2) | PVM3 and PVM4<br>consumption from V <sub>DD</sub> | -                         | -    | 2    | -    | μA   |

Table 25. Embedded reset and power control block characteristics (continued)

1. Continuous mode means Run/Sleep modes, or temperature sensor enable in Low-power run/Low-power sleep modes.

2. Guaranteed by design.

3. BOR0 is enabled in all modes (except shutdown) and its consumption is therefore included in the supply current characteristics tables.

|                                              |                         |                                                                   | Conditio                           | ons                         | ТҮР   |      | ТҮР   |        |            |    |    |      |      |    |        |        |      |             |           |      |  |     |  |

|----------------------------------------------|-------------------------|-------------------------------------------------------------------|------------------------------------|-----------------------------|-------|------|-------|--------|------------|----|----|------|------|----|--------|--------|------|-------------|-----------|------|--|-----|--|

| Symbol                                       | Parameter               | -                                                                 | Voltage<br>scaling                 | Code                        | 25 °C | Unit | 25 °C | Unit   |            |    |    |      |      |    |        |        |      |             |           |      |  |     |  |

|                                              |                         |                                                                   | Z                                  | Reduced code <sup>(1)</sup> | 2.35  |      | 90    |        |            |    |    |      |      |    |        |        |      |             |           |      |  |     |  |

|                                              |                         |                                                                   | Range 2<br><sub>:LK</sub> = 26 MHz | Coremark                    | 2.65  |      | 102   |        |            |    |    |      |      |    |        |        |      |             |           |      |  |     |  |

|                                              |                         | 6 - 6                                                             | ange<br>= 26                       | Dhrystone 2.1               | 2.75  | mA   | 106   | µA/MHz |            |    |    |      |      |    |        |        |      |             |           |      |  |     |  |

|                                              |                         | f <sub>HCLK</sub> = f <sub>HSE</sub> up<br>to 48 MHz              | Ra<br>fHCLK                        | Fibonacci                   | 2.60  |      | 100   |        |            |    |    |      |      |    |        |        |      |             |           |      |  |     |  |

| I <sub>DD_ALL</sub> Supply<br>(Run) Run mode |                         | included, bypass<br>mode PLL ON                                   | ι,Ξ                                | While(1)                    | 2.35  |      | 90    |        |            |    |    |      |      |    |        |        |      |             |           |      |  |     |  |

|                                              |                         | above 48 MHz<br>all peripherals<br>disable                        | N                                  | Reduced code <sup>(1)</sup> | 8.45  |      | 106   | µA/MHz |            |    |    |      |      |    |        |        |      |             |           |      |  |     |  |

|                                              |                         |                                                                   | 1<br>MHz                           | Coremark                    | 9.45  |      | 118   |        |            |    |    |      |      |    |        |        |      |             |           |      |  |     |  |

|                                              |                         |                                                                   | Range 1<br><sub>LK</sub> = 80 N    | Dhrystone 2.1               | 9.85  | mA   | 123   |        |            |    |    |      |      |    |        |        |      |             |           |      |  |     |  |

|                                              |                         |                                                                   | Ra<br>cLK                          | ICLK                        | Râ    | ICLK | ICLK  | Re     | CLK<br>CLK | Re | Re | ICLK | ICLK | Râ | ACLK R | ACLK R | HCLK | Ra<br>fнськ | Fibonacci | 9.25 |  | 116 |  |

|                                              |                         |                                                                   | Ę.                                 | While(1)                    | 8.45  |      | 106   |        |            |    |    |      |      |    |        |        |      |             |           |      |  |     |  |

|                                              |                         |                                                                   |                                    | Reduced code <sup>(1)</sup> | 225   |      | 113   |        |            |    |    |      |      |    |        |        |      |             |           |      |  |     |  |

|                                              | Supply                  |                                                                   |                                    | Coremark                    | 260   |      | 130   | µA/MHz |            |    |    |      |      |    |        |        |      |             |           |      |  |     |  |

| I <sub>DD_ALL</sub><br>(LPRun)               | current in<br>Low-power | f <sub>HCLK</sub> = f <sub>MSI</sub> = 2 M<br>all peripherals dis |                                    | Dhrystone 2.1               | 270   | μA   | 135   |        |            |    |    |      |      |    |        |        |      |             |           |      |  |     |  |

|                                              | run                     |                                                                   |                                    | Fibonacci                   | 245   |      | 123   |        |            |    |    |      |      |    |        |        |      |             |           |      |  |     |  |

|                                              |                         |                                                                   |                                    | While(1)                    | 285   |      | 143   |        |            |    |    |      |      |    |        |        |      |             |           |      |  |     |  |

# Table 33. Typical current consumption in Run and Low-power run modes, with different codesrunning from Flash, ART enable (Cache ON Prefetch OFF)

1. Reduced code used for characterization results provided in *Table 27*, *Table 29*, *Table 31*.

#### Table 34. Typical current consumption in Run, with different codes running from Flash, ART enable (Cache ON Prefetch OFF) and power supplied by external SMPS $(V_{DD12} = 1.10 \text{ V})$

|                     |                      | Co                                                                                                      | onditions <sup>(</sup> | 1)                          | ТҮР   |      | TYP   |        |

|---------------------|----------------------|---------------------------------------------------------------------------------------------------------|------------------------|-----------------------------|-------|------|-------|--------|

| Symbol              | Parameter            | -                                                                                                       | Voltage<br>scaling     | Code                        | 25 °C | Unit | 25 °C | Unit   |

|                     |                      |                                                                                                         | Ţ                      | Reduced code <sup>(2)</sup> | 1.01  |      | 39    |        |

|                     |                      | f <sub>HCLK</sub> = f <sub>HSE</sub> up to<br>48 MHz included,<br>bypass mode PLL<br>ON above<br>48 MHz | MF                     | Coremark                    | 1.14  |      | 44    |        |

|                     |                      |                                                                                                         | 80 MHz                 | Dhrystone 2.1               | 1.19  |      | 46    |        |

|                     |                      |                                                                                                         |                        | Fibonacci                   | 1.12  |      | 43    |        |

| I <sub>DD_ALL</sub> | Supply<br>current in |                                                                                                         |                        | While(1)                    | 1.01  | mA   | 39    | µA/MHz |

| (Rūn)               | Run mode             |                                                                                                         |                        | Reduced code <sup>(2)</sup> | 3.04  | -    | 38    |        |

|                     |                      | all peripherals                                                                                         |                        | Coremark                    | 3.40  |      | 42    |        |

|                     |                      | disable                                                                                                 | = 80                   | Dhrystone 2.1               | 3.54  |      | 44    |        |

|                     |                      |                                                                                                         | fHCLK =                | Fibonacci                   | 3.33  |      | 42    |        |

|                     |                      |                                                                                                         | fHo                    | While(1)                    | 3.04  |      | 38    |        |

DS11912 Rev 4

3. Wakeup with code execution from Flash. Average value given for a typical wakeup time as specified in *Table 52: Low-power mode wakeup timings*.

#### High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 4 to 48 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on design simulation results obtained with typical external components specified in *Table 57*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

|                                     | Symbol Parameter Conditions <sup>(2)</sup> Min Typ Max Unit |                                                           |     |      |     |      |  |  |  |  |  |  |  |

|-------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------|-----|------|-----|------|--|--|--|--|--|--|--|

| Symbol                              | Parameter                                                   | Conditions <sup>(2)</sup>                                 | Min | Тур  | Мах | Unit |  |  |  |  |  |  |  |

| f <sub>OSC_IN</sub>                 | Oscillator frequency                                        | -                                                         | 4   | 8    | 48  | MHz  |  |  |  |  |  |  |  |

| R <sub>F</sub>                      | Feedback resistor                                           | -                                                         | -   | 200  | -   | kΩ   |  |  |  |  |  |  |  |

|                                     |                                                             | During startup <sup>(3)</sup>                             | -   | -    | 5.5 |      |  |  |  |  |  |  |  |

|                                     |                                                             | V <sub>DD</sub> = 3 V,<br>Rm = 30 Ω,<br>CL = 10 pF@8 MHz  | -   | 0.44 | -   |      |  |  |  |  |  |  |  |

|                                     | HSE current consumption                                     | V <sub>DD</sub> = 3 V,<br>Rm = 45 Ω,<br>CL = 10 pF@8 MHz  | -   | 0.45 | -   |      |  |  |  |  |  |  |  |

| I <sub>DD(HSE)</sub>                |                                                             | V <sub>DD</sub> = 3 V,<br>Rm = 30 Ω,<br>CL = 5 pF@48 MHz  | -   | 0.68 | -   | mA   |  |  |  |  |  |  |  |

|                                     |                                                             | V <sub>DD</sub> = 3 V,<br>Rm = 30 Ω,<br>CL = 10 pF@48 MHz | -   | 0.94 | -   |      |  |  |  |  |  |  |  |

|                                     |                                                             | V <sub>DD</sub> = 3 V,<br>Rm = 30 Ω,<br>CL = 20 pF@48 MHz | -   | 1.77 | -   |      |  |  |  |  |  |  |  |

| G <sub>m</sub>                      | Maximum critical crystal transconductance                   | Startup                                                   | -   | -    | 1.5 | mA/V |  |  |  |  |  |  |  |

| t <sub>SU(HSE)</sub> <sup>(4)</sup> | Startup time                                                | V <sub>DD</sub> is stabilized                             | -   | 2    | -   | ms   |  |  |  |  |  |  |  |

| Table 57. HS | E oscillator | characteristics <sup>(1)</sup> |

|--------------|--------------|--------------------------------|

|--------------|--------------|--------------------------------|

1. Guaranteed by design.

2. Resonator characteristics given by the crystal/ceramic resonator manufacturer.

3. This consumption level occurs during the first 2/3 of the  $t_{SU(\text{HSE})}$  startup time

4. t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer

For C<sub>L1</sub> and C<sub>L2</sub>, it is recommended to use high-quality external ceramic capacitors in the 5 pF to 20 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 21*). C<sub>L1</sub> and C<sub>L2</sub> are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of C<sub>L1</sub> and C<sub>L2</sub>. PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing C<sub>L1</sub> and C<sub>L2</sub>.

# 6.3.10 Flash memory characteristics

| Symbol                 | Parameter                             | Conditions         | Тур           | Max   | Unit |  |  |  |  |  |  |  |  |

|------------------------|---------------------------------------|--------------------|---------------|-------|------|--|--|--|--|--|--|--|--|

| t <sub>prog</sub>      | 64-bit programming time               | -                  | 81.69         | 90.76 | μs   |  |  |  |  |  |  |  |  |

| +                      | one row (32 double                    | normal programming | 2.61          | 2.90  |      |  |  |  |  |  |  |  |  |

| <sup>t</sup> prog_row  | word) programming time                | fast programming   | 1.91          | 2.12  |      |  |  |  |  |  |  |  |  |

| +                      | one page (2 Kbyte)                    | normal programming | 20.91         | 23.24 | ms   |  |  |  |  |  |  |  |  |

| t <sub>prog_page</sub> | programming time                      | fast programming   | 15.29         | 16.98 |      |  |  |  |  |  |  |  |  |

| t <sub>ERASE</sub>     | Page (2 KB) erase time                | -                  | 22.02         | 24.47 |      |  |  |  |  |  |  |  |  |

| +                      | one bank (512 Kbyte)                  | normal programming | 5.35          | 5.95  | s    |  |  |  |  |  |  |  |  |

| t <sub>prog_bank</sub> | programming time                      | fast programming   | 3.91          | 4.35  | 5    |  |  |  |  |  |  |  |  |

| t <sub>ME</sub>        | Mass erase time<br>(one or two banks) | -                  | 22.13         | 24.59 | ms   |  |  |  |  |  |  |  |  |

|                        | Average consumption                   | Write mode         | 3.4           | -     |      |  |  |  |  |  |  |  |  |

|                        | from V <sub>DD</sub>                  | Erase mode         | 3.4           | -     | mA   |  |  |  |  |  |  |  |  |

| I <sub>DD</sub>        | Maximum aurrant (naak)                | Write mode         | 7 (for 2 µs)  | -     |      |  |  |  |  |  |  |  |  |

|                        | Maximum current (peak)                | Erase mode         | 7 (for 41 µs) | -     |      |  |  |  |  |  |  |  |  |

1. Guaranteed by design.

| Symbol           | Parameter      | Conditions                                           | Min <sup>(1)</sup> | Unit    |

|------------------|----------------|------------------------------------------------------|--------------------|---------|

| N <sub>END</sub> | Endurance      | T <sub>A</sub> = -40 to +105 °C                      | 10                 | kcycles |

|                  |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C    | 30                 |         |

|                  |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C   | 15                 |         |

| +                | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 125 °C   | 7                  | Years   |

| t <sub>RET</sub> | Data retention | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 55 °C  | 30                 | Tears   |

|                  |                | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 85 °C  | 15                 |         |

|                  |                | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 105 °C | 10                 |         |

### Table 65. Flash memory endurance and data retention

1. Guaranteed by characterization results.

2. Cycling performed over the whole temperature range.

## 6.3.18 Analog-to-Digital converter characteristics

Unless otherwise specified, the parameters given in *Table 77* are preliminary values derived from tests performed under ambient temperature,  $f_{PCLK}$  frequency and  $V_{DDA}$  supply voltage conditions summarized in *Table 23: General operating conditions*.

*Note:* It is recommended to perform a calibration after each power-up.

| Symbol                          | Parameter                          | Conditions                                        | Min                                                     | Тур                                           | Max                                                     | Unit                |

|---------------------------------|------------------------------------|---------------------------------------------------|---------------------------------------------------------|-----------------------------------------------|---------------------------------------------------------|---------------------|

| V <sub>DDA</sub>                | Analog supply voltage              | -                                                 | 1.62                                                    | -                                             | 3.6                                                     | V                   |

| N/                              |                                    | V <sub>DDA</sub> ≥ 2 V                            | 2                                                       | -                                             | V <sub>DDA</sub>                                        | V                   |

| V <sub>REF+</sub>               | Positive reference voltage         | V <sub>DDA</sub> < 2 V                            |                                                         | V <sub>DDA</sub>                              |                                                         | V                   |

| V <sub>REF-</sub>               | Negative reference voltage         | -                                                 |                                                         | V <sub>SSA</sub>                              |                                                         | V                   |

| f                               |                                    | Range 1                                           | 0.14                                                    | -                                             | 80                                                      | MHz                 |

| f <sub>ADC</sub>                | ADC clock frequency                | Range 2                                           | 0.14                                                    | -                                             | 26                                                      | WIHZ                |

|                                 |                                    | Resolution = 12 bits                              | -                                                       | -                                             | 5.33                                                    |                     |

|                                 | Sampling rate for FAST             | Resolution = 10 bits                              | -                                                       | -                                             | 6.15                                                    |                     |

|                                 | channels                           | Resolution = 8 bits                               | -                                                       | -                                             | 7.27                                                    |                     |

| £                               |                                    | Resolution = 6 bits                               | -                                                       | -                                             | 8.88                                                    | Mana                |

| f <sub>s</sub>                  | Sampling rate for SLOW channels    | Resolution = 12 bits                              | -                                                       | -                                             | 4.21                                                    | Msps                |

|                                 |                                    | Resolution = 10 bits                              | -                                                       | -                                             | 4.71                                                    |                     |

|                                 |                                    | Resolution = 8 bits                               | -                                                       | -                                             | 5.33                                                    |                     |

|                                 |                                    | Resolution = 6 bits                               | -                                                       | -                                             | 6.15                                                    |                     |

| f <sub>TRIG</sub>               | External trigger frequency         | f <sub>ADC</sub> = 80 MHz<br>Resolution = 12 bits | -                                                       | -                                             | 5.33                                                    | MHz                 |

|                                 |                                    | Resolution = 12 bits                              | -                                                       | -                                             | 15                                                      | 1/f <sub>ADC</sub>  |

| V <sub>CMIN</sub>               | Input common mode                  | Differential mode                                 | (V <sub>REF+</sub> +<br>V <sub>REF-</sub> )/2<br>- 0.18 | (V <sub>REF+</sub> +<br>V <sub>REF-</sub> )/2 | (V <sub>REF+</sub> +<br>V <sub>REF-</sub> )/2<br>+ 0.18 | V                   |

| V <sub>AIN</sub> <sup>(3)</sup> | Conversion voltage range(2)        | -                                                 | 0                                                       | -                                             | V <sub>REF+</sub>                                       | V                   |

| R <sub>AIN</sub>                | External input impedance           | -                                                 | -                                                       | -                                             | 50                                                      | kΩ                  |

| C <sub>ADC</sub>                | Internal sample and hold capacitor | -                                                 | -                                                       | 5                                             | -                                                       | pF                  |

| t <sub>STAB</sub>               | Power-up time                      | -                                                 |                                                         | 1                                             |                                                         | conversion<br>cycle |

| +                               | Calibration time                   | f <sub>ADC</sub> = 80 MHz                         |                                                         | 1.45                                          |                                                         | μs                  |

| t <sub>CAL</sub>                |                                    | -                                                 |                                                         | 116                                           |                                                         | 1/f <sub>ADC</sub>  |

| Table 77  |     | characteristics | (1) (2) |

|-----------|-----|-----------------|---------|

| Table 77. | ADC | characteristics | (1) (4) |

| Symbol | Parameter                         | Conditions                                           | Min | Тур  | Мах | Unit           |  |

|--------|-----------------------------------|------------------------------------------------------|-----|------|-----|----------------|--|

| SINAD  | Signal-to-noise<br>and distortion | DAC output buffer ON<br>CL ≤ 50 pF, RL ≥ 5 kΩ, 1 kHz | -   | 70.4 | -   | - dB<br>- bits |  |

|        | ratio                             | DAC output buffer OFF<br>CL ≤ 50 pF, no RL, 1 kHz    | -   | 71   | -   |                |  |

| ENOB   | Effective                         | DAC output buffer ON<br>CL ≤ 50 pF, RL ≥ 5 kΩ, 1 kHz | -   | 11.4 | -   | bito           |  |

|        | number of bits                    | DAC output buffer OFF<br>CL ≤ 50 pF, no RL, 1 kHz    | -   | 11.5 | -   | DILS           |  |

# Table 84. DAC accuracy<sup>(1)</sup> (continued)

1. Guaranteed by design.

2. Difference between two consecutive codes - 1 LSB.

3. Difference between measured value at Code i and the value at Code i on a line drawn between Code 0 and last Code 4095.

4. Difference between the value measured at Code (0x001) and the ideal value.

5. Difference between ideal slope of the transfer function and measured slope computed from code 0x000 and 0xFFF when buffer is OFF, and from code giving 0.2 V and ( $V_{REF+} - 0.2$ ) V when buffer is ON.

#### Voltage reference buffer characteristics 6.3.20

| Table 85. VREFBUF characteristics <sup>(1)</sup> |                                                                                                 |                                        |                                  |                            |       |                                                  |         |       |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------------|----------------------------|-------|--------------------------------------------------|---------|-------|

| Symbol                                           | Parameter                                                                                       | Conditio                               | ons                              | Min                        | Тур   | Max                                              | Unit    |       |

|                                                  |                                                                                                 |                                        | V <sub>RS</sub> = 0              | 2.4                        | -     | 3.6                                              |         |       |

| M                                                | Analog supply                                                                                   | Normal mode                            | V <sub>RS</sub> = 1              | 2.8                        | -     | 3.6                                              |         |       |

| V <sub>DDA</sub>                                 | voltage                                                                                         | Degraded mode <sup>(2)</sup>           | V <sub>RS</sub> = 0              | 1.65                       | -     | 2.4                                              |         |       |

|                                                  |                                                                                                 |                                        | V <sub>RS</sub> = 1              | 1.65                       | -     | 2.8                                              | V       |       |

|                                                  |                                                                                                 | Normal mode                            | V <sub>RS</sub> = 0              | 2.046 <sup>(3)</sup>       | 2.048 | 2.049 <sup>(3)</sup>                             | v       |       |

| V <sub>REFBUF</sub> _                            | Voltage<br>reference                                                                            | Normai mode                            | V <sub>RS</sub> = 1              | 2.498 <sup>(3)</sup>       | 2.5   | 2.502 <sup>(3)</sup>                             |         |       |

| OUT                                              | output                                                                                          | Degraded mode <sup>(2)</sup>           | V <sub>RS</sub> = 0              | $V_{DDA}$ -150 mV          | -     | V <sub>DDA</sub>                                 |         |       |

|                                                  |                                                                                                 |                                        | V <sub>RS</sub> = 1              | V <sub>DDA</sub> -150 mV   | -     | V <sub>DDA</sub>                                 |         |       |

| TRIM                                             | Trim step resolution                                                                            | -                                      | -                                | -                          | ±0.05 | ±0.1                                             | %       |       |

| CL                                               | Load capacitor                                                                                  | -                                      | -                                | 0.5                        | 1     | 1.5                                              | μF      |       |

| esr                                              | Equivalent<br>Serial Resistor<br>of Cload                                                       | -                                      | -                                | -                          | -     | 2                                                | Ω       |       |

| I <sub>load</sub>                                | Static load current                                                                             | -                                      | -                                | -                          | -     | 4                                                | mA      |       |

|                                                  |                                                                                                 |                                        | 2.8 V ≤ V <sub>DDA</sub> ≤ 3.6 V | I <sub>load</sub> = 500 μA | -     | 200                                              | 1000    | nnm// |

| I <sub>line_reg</sub>                            | Line regulation                                                                                 | $2.0 V \leq V_{\text{DDA}} \leq 3.0 V$ | I <sub>load</sub> = 4 mA         | -                          | 100   | 500                                              | ppm/V   |       |

| I <sub>load_reg</sub>                            | Load<br>regulation                                                                              | 500 µA ≤ I <sub>load</sub> ≤4 mA       | Normal mode                      | -                          | 50    | 500                                              | ppm/mA  |       |

| To r                                             | Temperature                                                                                     | -40 °C < T <sub>J</sub> < +125 °C      |                                  | -                          | -     | T <sub>coeff</sub><br>vrefint +<br>50            | ppm/ °C |       |

| T <sub>Coeff</sub>                               | coefficient                                                                                     | 0 °C < T <sub>J</sub> < +50 °C         |                                  | -                          | -     | T <sub>coeff</sub><br>vrefint <sup>+</sup><br>50 | ppm/ C  |       |

| PSRR                                             | Power supply                                                                                    | DC                                     |                                  | 40                         | 60    | -                                                | dB      |       |

| FORM                                             | rejection                                                                                       | 100 kHz                                |                                  | 25                         | 40    | -                                                | uв      |       |

|                                                  |                                                                                                 | $CL = 0.5 \ \mu F^{(4)}$               |                                  | -                          | 300   | 350                                              |         |       |

| t <sub>START</sub>                               | Start-up time                                                                                   | $CL = 1.1 \ \mu F^{(4)}$               |                                  | -                          | 500   | 650                                              | μs      |       |

|                                                  |                                                                                                 | CL = 1.5 µF <sup>(4)</sup>             |                                  | -                          | 650   | 800                                              |         |       |

| I <sub>INRUSH</sub>                              | Control of<br>maximum DC<br>current drive<br>on VREFBUF_<br>OUT during<br>start-up phase<br>(5) | -                                      | -                                | -                          | 8     | -                                                | mA      |       |

# (1)

| Symbol                         | Parameter             | Conditions                 | Min | Тур | Мах | Unit |  |  |

|--------------------------------|-----------------------|----------------------------|-----|-----|-----|------|--|--|

| I <sub>DDA</sub> (VREF<br>BUF) |                       | I <sub>load</sub> = 0 μA   | -   | 16  | 25  |      |  |  |

|                                | consumption           | I <sub>load</sub> = 500 μA | -   | 18  | 30  | μA   |  |  |

|                                | from V <sub>DDA</sub> | I <sub>load</sub> = 4 mA   | -   | 35  | 50  |      |  |  |

### Table 85. VREFBUF characteristics<sup>(1)</sup> (continued)

1. Guaranteed by design, unless otherwise specified.

2. In degraded mode, the voltage reference buffer can not maintain accurately the output voltage which will follow (V<sub>DDA</sub> - drop voltage).

3. Guaranteed by test in production.

4. The capacitive load must include a 100 nF capacitor in order to cut-off the high frequency noise.

5. To correctly control the VREFBUF inrush current during start-up phase and scaling change, the  $V_{DDA}$  voltage should be in the range [2.4 V to 3.6 V] and [2.8 V to 3.6 V] respectively for  $V_{RS}$  = 0 and  $V_{RS}$  = 1.

Г

Т

Т

### **SPI characteristics**

Unless otherwise specified, the parameters given in *Table 95* for SPI are derived from tests performed under the ambient temperature, f<sub>PCLKx</sub> frequency and supply voltage conditions summarized in *Table 23: General operating conditions*.

- Output speed is set to OSPEEDRy[1:0] = 11

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5 x V<sub>DD</sub>

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI).

Т

Т

Т

| Symbol                                       | Parameter                | Conditions                                                                              | Min                              | Тур               | Мах                  | Unit |

|----------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------|----------------------------------|-------------------|----------------------|------|

|                                              |                          | Master mode receiver/full duplex<br>2.7 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1    |                                  |                   | 40                   |      |

|                                              |                          | Master mode receiver/full duplex<br>1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1   |                                  |                   | 16                   |      |

|                                              |                          | Master mode transmitter<br>1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1            |                                  |                   | 40                   |      |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub>    | SPI clock frequency      | Slave mode receiver<br>1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1                | -                                | -                 | 40                   | MHz  |

|                                              |                          | Slave mode transmitter/full duplex<br>2.7 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1  |                                  |                   | 37 <sup>(2)</sup>    |      |

|                                              |                          | Slave mode transmitter/full duplex<br>1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1 |                                  |                   | 20 <sup>(2)</sup>    |      |

|                                              |                          | Voltage Range 2                                                                         |                                  |                   | 13                   |      |

| t <sub>su(NSS)</sub>                         | NSS setup time           | Slave mode, SPI prescaler = 2                                                           | 4 <sub>x</sub> T <sub>PCLK</sub> | -                 | -                    | ns   |

| t <sub>h(NSS)</sub>                          | NSS hold time            | Slave mode, SPI prescaler = 2                                                           | 2 <sub>x</sub> T <sub>PCLK</sub> | -                 | -                    | ns   |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time    | Master mode                                                                             | T <sub>PCLK</sub> -2             | T <sub>PCLK</sub> | T <sub>PCLK</sub> +2 | ns   |

| t <sub>su(MI)</sub>                          | Data input setup time    | Master mode                                                                             | 4                                | -                 | -                    | ns   |

| t <sub>su(SI)</sub>                          |                          | Slave mode                                                                              | 1.5                              | -                 | -                    | 115  |

| t <sub>h(MI)</sub>                           | Data input hold time     | Master mode                                                                             | 6.5                              | -                 | -                    | ns   |

| t <sub>h(SI)</sub>                           |                          | Slave mode                                                                              | 1.5                              | -                 | -                    | 115  |

| t <sub>a(SO)</sub>                           | Data output access time  | Slave mode                                                                              | 9                                | -                 | 36                   | ns   |

| t <sub>dis(SO)</sub>                         | Data output disable time | Slave mode                                                                              | 9                                | -                 | 16                   | ns   |

| Table 95. SP | characteristics <sup>(1)</sup> |

|--------------|--------------------------------|

|--------------|--------------------------------|

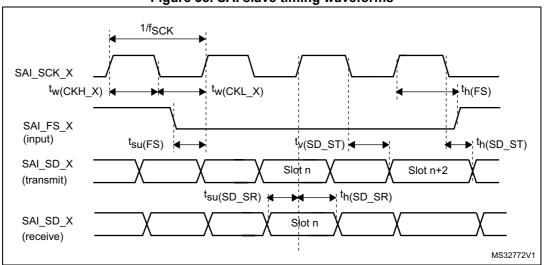

Figure 38. SAI slave timing waveforms

### **SDMMC** characteristics

Unless otherwise specified, the parameters given in *Table 99* for SDIO are derived from tests performed under the ambient temperature, f<sub>PCLKx</sub> frequency and V<sub>DD</sub> supply voltage conditions summarized in *Table 23: General operating conditions*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 11

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5 x V<sub>DD</sub>

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output characteristics.

| Symbol                                              | Parameter                             | Conditions               | Min | Тур | Max | Unit |  |

|-----------------------------------------------------|---------------------------------------|--------------------------|-----|-----|-----|------|--|

| f <sub>PP</sub>                                     | Clock frequency in data transfer mode | -                        | 0   | -   | 50  | MHz  |  |

| -                                                   | SDIO_CK/fPCLK2 frequency ratio        | -                        | -   | -   | 4/3 | -    |  |

| t <sub>W(CKL)</sub>                                 | Clock low time                        | f <sub>PP</sub> = 50 MHz | 8   | 10  | -   | ns   |  |

| t <sub>W(CKH)</sub>                                 | Clock high time                       | f <sub>PP</sub> = 50 MHz | 8   | 10  | -   | ns   |  |

| CMD, D inpu                                         | ts (referenced to CK) in MMC and SD H | S mode                   |     |     |     |      |  |

| t <sub>ISU</sub>                                    | Input setup time HS                   | f <sub>PP</sub> = 50 MHz | 3.5 | -   | -   | ns   |  |

| t <sub>IH</sub>                                     | Input hold time HS                    | f <sub>PP</sub> = 50 MHz | 2.5 | -   | -   | ns   |  |

| CMD, D outp                                         | uts (referenced to CK) in MMC and SD  | HS mode                  |     |     |     |      |  |

| t <sub>OV</sub>                                     | Output valid time HS                  | f <sub>PP</sub> = 50 MHz | -   | 12  | 13  | ns   |  |

| t <sub>ОН</sub>                                     | Output hold time HS                   | f <sub>PP</sub> = 50 MHz | 10  | -   | -   | ns   |  |

| CMD, D inputs (referenced to CK) in SD default mode |                                       |                          |     |     |     |      |  |

| t <sub>ISUD</sub>                                   | Input setup time SD                   | f <sub>PP</sub> = 50 MHz | 3.5 | -   | -   | ns   |  |

| t <sub>IHD</sub>                                    | Input hold time SD                    | f <sub>PP</sub> = 50 MHz | 3   | -   | -   | ns   |  |

Table 99. SD / MMC dynamic characteristics,  $V_{DD}$ =2.7 V to 3.6 V<sup>(1)</sup>

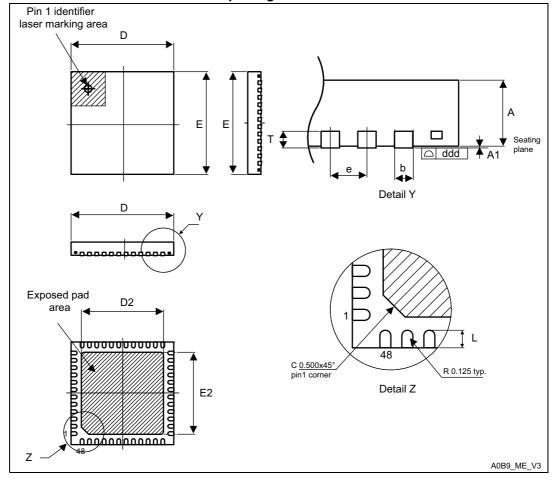

# 7.6 UFQFPN48 package information

Figure 56. UFQFPN48 - 48-lead, 7x7 mm, 0.5 mm pitch, ultra thin fine pitch quad flat package outline

1. Drawing is not to scale.

- 2. All leads/pads should also be soldered to the PCB to improve the lead/pad solder joint life.

- 3. There is an exposed die pad on the underside of the UFQFPN package. It is recommended to connect and solder this back-side pad to PCB ground.

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.