# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                 |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, PWM, WDT                                           |

| Number of I/O              | 83                                                                              |

| Program Memory Size        | 512KB (512K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 160K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                    |

| Data Converters            | A/D 16x12b; D/A 1x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-LQFP                                                                        |

| Supplier Device Package    | 100-LQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l452vet3           |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

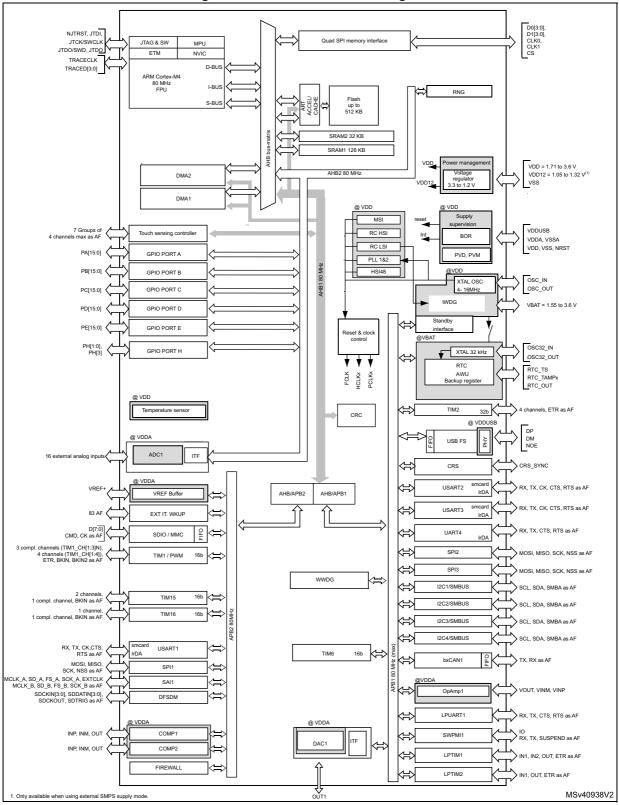

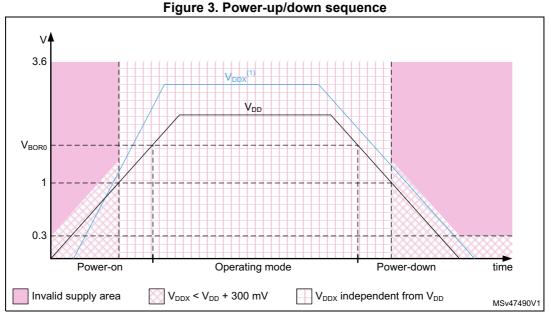

# 2 Description

The STM32L452xx devices are the ultra-low-power microcontrollers based on the highperformance Arm<sup>®</sup> Cortex<sup>®</sup>-M4 32-bit RISC core operating at a frequency of up to 80 MHz. The Cortex-M4 core features a Floating point unit (FPU) single precision which supports all Arm<sup>®</sup> single-precision data-processing instructions and data types. It also implements a full set of DSP instructions and a memory protection unit (MPU) which enhances application security.

The STM32L452xx devices embed high-speed memories (Flash memory up to 512 Kbyte, 160 Kbyte of SRAM), a Quad SPI flash memories interface (available on all packages) and an extensive range of enhanced I/Os and peripherals connected to two APB buses, two AHB buses and a 32-bit multi-AHB bus matrix.

The STM32L452xx devices embed several protection mechanisms for embedded Flash memory and SRAM: readout protection, write protection, proprietary code readout protection and Firewall.

The devices offer a fast 12-bit ADC (5 Msps), two comparators, one operational amplifier, one DAC channel, an internal voltage reference buffer, a low-power RTC, one general-purpose 32-bit timer, one 16-bit PWM timer dedicated to motor control, four general-purpose 16-bit timers, and two 16-bit low-power timers.

In addition, up to 21 capacitive sensing channels are available.

They also feature standard and advanced communication interfaces.

- Four I2Cs

- Three SPIs

- Three USARTs, one UART and one Low-Power UART.

- One SAI (Serial Audio Interfaces)

- One SDMMC

- One CAN

- One USB full-speed device crystal less

The STM32L452xx operates in the -40 to +85 °C (+105 °C junction) and -40 to +125 °C (+130 °C junction) temperature ranges from a 1.71 to 3.6 V V<sub>DD</sub> power supply when using internal LDO regulator and a 1.05 to 1.32V V<sub>DD12</sub> power supply when using external SMPS supply. A comprehensive set of power-saving modes allows the design of low-power applications.

Some independent power supplies are supported: analog independent supply input for ADC, DAC, OPAMP and comparators. A VBAT input allows to backup the RTC and backup registers. Dedicated  $V_{DD12}$  power supplies can be used to bypass the internal LDO regulator when connected to an external SMPS.

The STM32L452xx family offers six packages from 48 to 100-pin packages.

Figure 1. STM32L452xx block diagram

1.  $V_{DDX}$  refers to  $V_{DDA}$ .

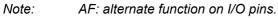

#### 3.9.2 Power supply supervisor

The device has an integrated ultra-low-power brown-out reset (BOR) active in all modes except Shutdown and ensuring proper operation after power-on and during power down. The device remains in reset mode when the monitored supply voltage  $V_{DD}$  is below a specified threshold, without the need for an external reset circuit.

The lowest BOR level is 1.71V at power on, and other higher thresholds can be selected through option bytes. The device features an embedded programmable voltage detector (PVD) that monitors the V<sub>DD</sub> power supply and compares it to the VPVD threshold. An interrupt can be generated when V<sub>DD</sub> drops below the VPVD threshold and/or when V<sub>DD</sub> is higher than the VPVD threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

In addition, the device embeds a Peripheral Voltage Monitor which compares the independent supply voltage  $V_{DDA}$  with a fixed threshold in order to ensure that the peripheral is in its functional supply range.

|                                                  |                  |                  | Ionantie             |                        |     | o 0/1             |     | p 2               | Stan             |                   | Shut | down              |      |

|--------------------------------------------------|------------------|------------------|----------------------|------------------------|-----|-------------------|-----|-------------------|------------------|-------------------|------|-------------------|------|

| Peripheral                                       | Run              | Sleep            | Low-<br>power<br>run | Low-<br>power<br>sleep | -   | Wakeup capability | -   | Wakeup capability | -                | Wakeup capability | -    | Wakeup capability | VBAT |

| CPU                                              | Y                | -                | Y                    | -                      | -   | -                 | -   | -                 | -                | -                 | -    | -                 | -    |

| Flash memory (up to 512 KB)                      | O <sup>(2)</sup> | O <sup>(2)</sup> | O <sup>(2)</sup>     | O <sup>(2)</sup>       | -   | -                 | -   | -                 | -                | -                 | -    | -                 | -    |

| SRAM1 (128 KB)                                   | Y                | Y <sup>(3)</sup> | Y                    | Y <sup>(3)</sup>       | Y   | -                 | Y   | -                 | -                | -                 | -    | -                 | -    |

| SRAM2 (32 KB)                                    | Y                | Y <sup>(3)</sup> | Y                    | Y <sup>(3)</sup>       | Y   | -                 | Y   | -                 | O <sup>(4)</sup> | -                 | -    | -                 | -    |

| Quad SPI                                         | 0                | 0                | 0                    | 0                      | -   | -                 | -   | -                 | -                | -                 | -    | -                 | -    |

| Backup Registers                                 | Y                | Y                | Y                    | Y                      | Y   | -                 | Y   | -                 | Y                | -                 | Y    | -                 | Y    |

| Brown-out reset<br>(BOR)                         | Y                | Y                | Y                    | Y                      | Y   | Y                 | Y   | Y                 | Y                | Y                 | -    | -                 | -    |

| Programmable<br>Voltage Detector<br>(PVD)        | 0                | 0                | 0                    | 0                      | 0   | 0                 | 0   | 0                 | -                | -                 | -    | -                 | -    |

| Peripheral Voltage<br>Monitor (PVMx;<br>x=1,3,4) | 0                | 0                | 0                    | 0                      | 0   | 0                 | 0   | 0                 | -                | -                 | -    | -                 | -    |

| DMA                                              | 0                | 0                | 0                    | 0                      | -   | -                 | -   | -                 | -                | -                 | -    | -                 | -    |

| High Speed Internal<br>(HSI16)                   | 0                | 0                | 0                    | 0                      | (5) | -                 | (5) | -                 | -                | -                 | -    | -                 | -    |

| Oscillator RC48                                  | 0                | 0                | -                    | -                      | -   | -                 | -   | -                 | -                | -                 | -    | -                 | -    |

| High Speed External<br>(HSE)                     | 0                | 0                | 0                    | 0                      | -   | -                 | -   | -                 | -                | -                 | -    | -                 | -    |

| Low Speed Internal<br>(LSI)                      | 0                | 0                | 0                    | 0                      | 0   | -                 | 0   | -                 | 0                | -                 | -    | -                 | -    |

| Low Speed External<br>(LSE)                      | 0                | 0                | 0                    | 0                      | 0   | -                 | 0   | -                 | 0                | -                 | 0    | -                 | 0    |

| Multi-Speed Internal<br>(MSI)                    | 0                | 0                | 0                    | 0                      | -   | -                 | -   | -                 | -                | -                 | -    | -                 | -    |

| Clock Security<br>System (CSS)                   | 0                | 0                | 0                    | 0                      | -   | -                 | -   | -                 | -                | -                 | -    | -                 | -    |

| Clock Security<br>System on LSE                  | 0                | 0                | 0                    | 0                      | 0   | 0                 | 0   | 0                 | 0                | 0                 | -    | -                 | -    |

| RTC / Auto wakeup                                | 0                | 0                | 0                    | 0                      | 0   | 0                 | 0   | 0                 | 0                | 0                 | 0    | 0                 | 0    |

| Number of RTC<br>Tamper pins                     | 3                | 3                | 3                    | 3                      | 3   | 0                 | 3   | 0                 | 3                | 0                 | 3    | 0                 | 3    |

Table 5. Functionalities depending on the working mode<sup>(1)</sup>

without having any impact on the timing of "injected" conversions

- "injected" conversions for precise timing and with high conversion priority

| DFSDM features            | DFSDM1 |

|---------------------------|--------|

| Number of channels        | 8      |

| Number of filters         | 4      |

| Input from internal ADC   | -      |

| Supported trigger sources | 10     |

| Pulses skipper            | -      |

| ID registers support      | -      |

### 3.22 Random number generator (RNG)

All devices embed an RNG that delivers 32-bit random numbers generated by an integrated analog circuit.

### 3.23 Timers and watchdogs

The STM32L452xx includes one advanced control timers, up to five general-purpose timers, two basic timers, two low-power timers, two watchdog timers and a SysTick timer. The table below compares the features of the advanced control, general purpose and basic timers.

| Timer type          | Timer | Counter resolution | Counter<br>type      | Prescaler<br>factor                   | request compare |   | Complementary<br>outputs |

|---------------------|-------|--------------------|----------------------|---------------------------------------|-----------------|---|--------------------------|

| Advanced control    | TIM1  | 16-bit             | Up, down,<br>Up/down | Any integer<br>between 1<br>and 65536 | Yes             | 4 | 3                        |

| General-<br>purpose | TIM2  | 32-bit             | Up, down,<br>Up/down | Any integer<br>between 1<br>and 65536 | Yes             | 4 | No                       |

| General-<br>purpose | TIM3  | 16-bit             | Up, down,<br>Up/down | Any integer<br>between 1<br>and 65536 | Yes             | 4 | No                       |

| General-<br>purpose | TIM15 | 16-bit             | Up                   | Any integer<br>between 1<br>and 65536 | Yes             | 2 | 1                        |

| General-<br>purpose | TIM16 | 16-bit             | Up                   | Any integer<br>between 1<br>and 65536 | Yes             | 1 | 1                        |

| Basic               | TIM6  | 16-bit             | Up                   | Any integer<br>between 1<br>and 65536 | Yes             | 0 | No                       |

| Table 11. | Timer | feature | comparison |

|-----------|-------|---------|------------|

|-----------|-------|---------|------------|

| SAI features                                           | Support <sup>(1)</sup> |

|--------------------------------------------------------|------------------------|

| I2S, LSB or MSB-justified, PCM/DSP, TDM, AC'97         | Х                      |

| Mute mode                                              | Х                      |

| Stereo/Mono audio frame capability.                    | Х                      |

| 16 slots                                               | Х                      |

| Data size configurable: 8-, 10-, 16-, 20-, 24-, 32-bit | Х                      |

| FIFO Size                                              | X (8 Word)             |

| SPDIF                                                  | Х                      |

Table 14. SAI implementation

1. X: supported

### 3.30 Controller area network (CAN)

The CAN is compliant with specifications 2.0A and B (active) with a bit rate up to 1 Mbit/s. It can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers. It has three transmit mailboxes, two receive FIFOs with 3 stages and 14 scalable filter banks.

The CAN peripheral supports:

- Supports CAN protocol version 2.0 A, B Active

- Bit rates up to 1 Mbit/s

- Transmission

- Three transmit mailboxes

- Configurable transmit priority

- Reception

- Two receive FIFOs with three stages

- 14 Scalable filter banks

- Identifier list feature

- Configurable FIFO overrun

- Time-triggered communication option

- Disable automatic retransmission mode

- 16-bit free running timer

- Time Stamp sent in last two data bytes

- Management

- Maskable interrupts

- Software-efficient mailbox mapping at a unique address space

# 3.31 Secure digital input/output and MultiMediaCards Interface (SDMMC)

The card host interface (SDMMC) provides an interface between the APB peripheral bus and MultiMediaCards (MMCs), SD memory cards and SDIO cards.

DS11912 Rev 4

The Quad SPI interface supports:

- Three functional modes: indirect, status-polling, and memory-mapped

- Dual-flash mode, where 8 bits can be sent/received simultaneously by accessing two flash memories in parallel.

- SDR and DDR support

- Fully programmable opcode for both indirect and memory mapped mode

- Fully programmable frame format for both indirect and memory mapped mode

- Each of the 5 following phases can be configured independently (enable, length, single/dual/quad communication)

- Instruction phase

- Address phase

- Alternate bytes phase

- Dummy cycles phase

- Data phase

- Integrated FIFO for reception and transmission

- 8, 16, and 32-bit data accesses are allowed

- DMA channel for indirect mode operations

- Programmable masking for external flash flag management

- Timeout management

- Interrupt generation on FIFO threshold, timeout, status match, operation complete, and access error

|        |      | AF8                        | AF9        | AF10                 | AF11 | AF12           | AF13      | AF14                        | AF15     |

|--------|------|----------------------------|------------|----------------------|------|----------------|-----------|-----------------------------|----------|

| Po     | ort  | UART4/<br>LPUART1/<br>CAN1 | CAN1/TSC   | CAN1/USB/<br>QUADSPI |      |                | SAI1      | TIM2/TIM15/<br>TIM16/LPTIM2 | EVENTOUT |

|        | PD0  | -                          | CAN1_RX    | -                    | -    | -              | -         | -                           | EVENTOUT |

|        | PD1  | -                          | CAN1_TX    | -                    | -    | -              | -         | -                           | EVENTOUT |

|        | PD2  | -                          | TSC_SYNC   | -                    | -    | SDMMC1_<br>CMD | -         | -                           | EVENTOUT |

|        | PD3  | -                          | -          | QUADSPI_<br>BK2_NCS  | -    | -              | -         | -                           | EVENTOUT |

|        | PD4  | -                          | -          | QUADSPI_<br>BK2_IO0  | -    | -              | -         | -                           | EVENTOUT |

|        | PD5  | -                          | -          | QUADSPI_<br>BK2_IO1  | -    | -              | -         | -                           | EVENTOUT |

| Port D | PD6  | -                          | -          | QUADSPI_<br>BK2_IO2  | -    | -              | SAI1_SD_A | -                           | EVENTOUT |

|        | PD7  | -                          | -          | QUADSPI_<br>BK2_IO3  | -    | -              | -         | -                           | EVENTOUT |

|        | PD8  | -                          | -          | -                    | -    | -              | -         | -                           | EVENTOUT |

|        | PD9  | -                          | -          | -                    | -    | -              | -         | -                           | EVENTOUT |

|        | PD10 | -                          | TSC_G6_IO1 | -                    | -    | -              | -         | -                           | EVENTOUT |

|        | PD11 | -                          | TSC_G6_IO2 | -                    | -    | -              | -         | LPTIM2_ETR                  | EVENTOUT |

|        | PD12 | -                          | TSC_G6_IO3 | -                    | -    | -              | -         | LPTIM2_IN1                  | EVENTOUT |

|        | PD13 | -                          | TSC_G6_IO4 | -                    | -    | -              | -         | LPTIM2_OUT                  | EVENTOUT |

|        | PD14 | -                          | -          | -                    | -    | -              | -         | -                           | EVENTOUT |

|        | PD15 | -                          | -          | -                    | -    | -              | -         | -                           | EVENTOU  |

STM32L452xx

DS11912 Rev 4

577

81/212

Pinouts and pin description

| (continued) |                           |             |            |  |  |  |  |  |

|-------------|---------------------------|-------------|------------|--|--|--|--|--|

| Bus         | Boundary address          | Size(bytes) | Peripheral |  |  |  |  |  |

|             | 0x4001 2C00 - 0x4001 2FFF | 1 KB        | TIM1       |  |  |  |  |  |

|             | 0x4001 2800 - 0x4001 2BFF | 1 KB        | SDMMC1     |  |  |  |  |  |

|             | 0x4001 2000 - 0x4001 27FF | 2 KB        | Reserved   |  |  |  |  |  |

|             | 0x4001 1C00 - 0x4001 1FFF | 1 KB        | FIREWALL   |  |  |  |  |  |

| APB2        | 0x4001 0800- 0x4001 1BFF  | 5 KB        | Reserved   |  |  |  |  |  |

|             | 0x4001 0400 - 0x4001 07FF | 1 KB        | EXTI       |  |  |  |  |  |

|             | 0x4001 0200 - 0x4001 03FF |             | COMP       |  |  |  |  |  |

|             | 0x4001 0030 - 0x4001 01FF | 1 KB        | VREFBUF    |  |  |  |  |  |

|             | 0x4001 0000 - 0x4001 002F |             | SYSCFG     |  |  |  |  |  |

|             | 0x4000 9800 - 0x4000 FFFF | 26 KB       | Reserved   |  |  |  |  |  |

|             | 0x4000 9400 - 0x4000 97FF | 1 KB        | LPTIM2     |  |  |  |  |  |

|             | 0x4000 8800 - 0x4000 93FF | 3 KB        | Reserved   |  |  |  |  |  |

|             | 0x4000 8400 - 0x4000 87FF | 1 KB        | 12C4       |  |  |  |  |  |

|             | 0x4000 8000 - 0x4000 83FF | 1 KB        | LPUART1    |  |  |  |  |  |

|             | 0x4000 7C00 - 0x4000 7FFF | 1 KB        | LPTIM1     |  |  |  |  |  |

|             | 0x4000 7800 - 0x4000 7BFF | 1 KB        | OPAMP      |  |  |  |  |  |

|             | 0x4000 7400 - 0x4000 77FF | 1 KB        | DAC1       |  |  |  |  |  |

|             | 0x4000 7000 - 0x4000 73FF | 1 KB        | PWR        |  |  |  |  |  |

|             | 0x4000 6C00 - 0x4000 6FFF | 1 KB        | USB SRAM   |  |  |  |  |  |

|             | 0x4000 6800 - 0x4000 6BFF | 1 KB        | USB FS     |  |  |  |  |  |

| APB1        | 0x4000 6400 - 0x4000 67FF | 1 KB        | CAN1       |  |  |  |  |  |

| APDI        | 0x4000 6000 - 0x4000 63FF | 1 KB        | CRS        |  |  |  |  |  |

|             | 0x4000 5C00- 0x4000 5FFF  | 1 KB        | I2C3       |  |  |  |  |  |

|             | 0x4000 5800 - 0x4000 5BFF | 1 KB        | I2C2       |  |  |  |  |  |

|             | 0x4000 5400 - 0x4000 57FF | 1 KB        | I2C1       |  |  |  |  |  |

|             | 0x4000 5000 - 0x4000 53FF | 1 KB        | Reserved   |  |  |  |  |  |

|             | 0x4000 4C00 - 0x4000 4FFF | 1 KB        | UART4      |  |  |  |  |  |

|             | 0x4000 4800 - 0x4000 4BFF | 1 KB        | USART3     |  |  |  |  |  |

|             | 0x4000 4400 - 0x4000 47FF | 1 KB        | USART2     |  |  |  |  |  |

|             | 0x4000 4000 - 0x4000 43FF | 1 KB        | Reserved   |  |  |  |  |  |

|             | 0x4000 3C00 - 0x4000 3FFF | 1 KB        | SPI3       |  |  |  |  |  |

|             | 0x4000 3800 - 0x4000 3BFF | 1 KB        | SPI2       |  |  |  |  |  |

|             | 0x4000 3400 - 0x4000 37FF | 1 KB        | Reserved   |  |  |  |  |  |

Table 19. STM32L452xx memory map and peripheral register boundary addresses<sup>(1)</sup>(continued)

|                                |                         |                                                                                         | <u> </u>                          |                             | TYP              |             | TVD       |        |  |    |  |

|--------------------------------|-------------------------|-----------------------------------------------------------------------------------------|-----------------------------------|-----------------------------|------------------|-------------|-----------|--------|--|----|--|

|                                |                         |                                                                                         | Conditions                        |                             |                  |             | TYP       |        |  |    |  |

| Symbol                         | Parameter               | -                                                                                       | Voltage<br>scaling                | Code                        | le 25 °C         |             | 25 °C     | Unit   |  |    |  |

|                                |                         |                                                                                         | Ηz                                | Reduced code <sup>(1)</sup> | 2.75             |             | 106       |        |  |    |  |

|                                |                         |                                                                                         | Range 2<br><sub>LK</sub> = 26 MHz | Coremark                    | 2.50             |             | 96        |        |  |    |  |

|                                |                         | f <sub>HCLK</sub> = f <sub>HSE</sub> up to                                              | ange<br>= 2(                      | Dhrystone 2.1               | 2.50             | mA          | 96        | µA/MHz |  |    |  |

|                                |                         | 48 MHz included,<br>bypass mode<br>PLL ON above<br>48 MHz<br>all peripherals<br>disable | 48 MHz included,                  | 48 MHz included,            | 48 MHz included, | Ra<br>fнськ | Fibonacci | 2.30   |  | 88 |  |

| I <sub>DD_ALL</sub>            | Supply<br>current in    |                                                                                         | fHo                               | While(1)                    | 2.20             |             | 84.6      |        |  |    |  |

| (Run)                          | (Rūn) Run mode          |                                                                                         | 러                                 | Reduced code <sup>(1)</sup> | 8.85             |             | 111       | µA/MHz |  |    |  |

|                                |                         |                                                                                         | inge 1<br>= 80 MHz                | Coremark                    | 8.15             |             | 102       |        |  |    |  |

|                                |                         |                                                                                         | Range<br>f <sub>HCLK</sub> = 80   | Dhrystone 2.1               | 8.15             | mA          | 102       |        |  |    |  |

|                                |                         |                                                                                         |                                   | Fibonacci                   | 7.55             |             | 94        |        |  |    |  |

|                                |                         |                                                                                         |                                   | While(1)                    | 7.95             |             | 99        |        |  |    |  |

|                                |                         |                                                                                         |                                   | Reduced code <sup>(1)</sup> | 340              |             | 170       |        |  |    |  |

| 1                              | Supply                  |                                                                                         |                                   | Coremark                    | 380              |             | 190       |        |  |    |  |

| I <sub>DD_ALL</sub><br>(LPRun) | current in<br>Low-power | f <sub>HCLK</sub> = f <sub>MSI</sub> = 2 MI<br>all peripherals disa                     |                                   | Dhrystone 2.1               | 355              | μA          | 178       | µA/MHz |  |    |  |

| ()                             | run                     |                                                                                         |                                   | Fibonacci                   | 355              |             | 178       |        |  |    |  |

|                                |                         |                                                                                         |                                   | While(1)                    | 405              |             | 203       |        |  |    |  |

# Table 36. Typical current consumption in Run and Low-power run modes, with different codesrunning from Flash, ART disable

1. Reduced code used for characterization results provided in *Table 27, Table 29, Table 31*.

| Table 37. Typical current consumption in Run modes, with different codes running from |  |

|---------------------------------------------------------------------------------------|--|

| Flash, ART disable and power supplied by external SMPS (V <sub>DD12</sub> = 1.10 V)   |  |

|                     |                      | C                                                                                                                                     | onditions <sup>(</sup>    | 1)                          | ΤΥΡ    |          | ΤΥΡ   |                             |      |    |    |            |

|---------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----------------------------|--------|----------|-------|-----------------------------|------|----|----|------------|

| Symbol              | Parameter            | -                                                                                                                                     | Voltage<br>scaling        | Code                        | 25 °C  | Unit     | 25 °C | Unit                        |      |    |    |            |

|                     |                      |                                                                                                                                       | Р<br>Н                    | Reduced code <sup>(2)</sup> | 1.19   |          | 46    |                             |      |    |    |            |

|                     |                      |                                                                                                                                       | 26 MHz                    | Coremark                    | 1.08   | -        | 41    | μA/MHz                      |      |    |    |            |

|                     |                      | f <sub>HCLK</sub> = f <sub>HSE</sub> up to<br>48 MHz included,<br>bypass mode<br>PLL ON above<br>48 MHz<br>all peripherals<br>disable | f <sub>HCLK</sub> = 26    | Dhrystone 2.1               | 1.08   |          | 41    |                             |      |    |    |            |

|                     |                      |                                                                                                                                       |                           | Fibonacci                   | 0.99   |          | 38    |                             |      |    |    |            |

| I <sub>DD_ALL</sub> | Supply<br>current in |                                                                                                                                       |                           | While(1)                    | 0.95   | mA       | 37    |                             |      |    |    |            |

| (Rūn)               | Run mode             |                                                                                                                                       | 48 MHz<br>all peripherals | 48 MHz<br>all peripherals   |        |          | ٦٢    | Reduced code <sup>(2)</sup> | 3.18 | ШA | 40 | μΑντιντίτε |

|                     |                      |                                                                                                                                       |                           |                             | 80 MHz | Coremark | 2.93  |                             | 37   |    |    |            |

|                     |                      |                                                                                                                                       | = 8(                      | Dhrystone 2.1               | 2.93   |          | 37    |                             |      |    |    |            |

|                     |                      |                                                                                                                                       | - роск                    | Fibonacci                   | 2.71   |          | 34    | 1                           |      |    |    |            |

|                     |                      |                                                                                                                                       | fHc                       | While(1)                    | 2.86   |          | 36    |                             |      |    |    |            |

All values are obtained by calculation based on measurements done without SMPS and using following parameters: SMPS input = 3.3 V, SMPS efficiency = 85%, V<sub>DD12</sub> = 1.10 V

2. Reduced code used for characterization results provided in *Table 27*, *Table 29*, *Table 31*.

- 1. Guaranteed by design.

- 2. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

- 3. t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and it can vary significantly with the crystal manufacturer

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

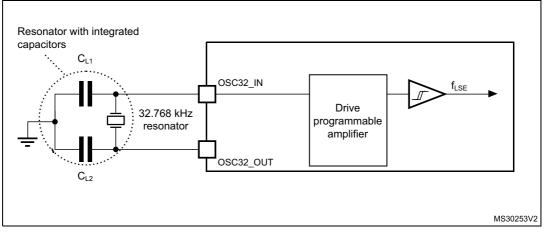

Figure 22. Typical application with a 32.768 kHz crystal

*Note:* An external resistor is not required between OSC32\_IN and OSC32\_OUT and it is forbidden to add one.

#### 6.3.8 Internal clock source characteristics

The parameters given in *Table 59* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 23: General operating conditions*. The provided curves are characterization results, not tested in production.

#### High-speed internal (HSI16) RC oscillator

| Symbol                                   | Parameter                                             | Conditions                                    | Min   | Тур | Мах   | Unit |

|------------------------------------------|-------------------------------------------------------|-----------------------------------------------|-------|-----|-------|------|

| f <sub>HSI16</sub>                       | HSI16 Frequency                                       | V <sub>DD</sub> =3.0 V, T <sub>A</sub> =30 °C | 15.88 | -   | 16.08 | MHz  |

|                                          | HSI16 user trimming step                              | Trimming code is not a multiple of 64         | 0.2   | 0.3 | 0.4   | %    |

| TRIM                                     | HSI to user trimming step                             | Trimming code is a multiple of 64             | -4    | -6  | -8    | %    |

| DuCy(HSI16) <sup>(2)</sup>               | Duty Cycle                                            | -                                             | 45    | -   | 55    | %    |

| A (USI16)                                | HSI16 oscillator frequency drift over temperature     | T <sub>A</sub> = 0 to 85 °C                   | -1    | -   | 1     | %    |

| ∆ <sub>Temp</sub> (HSI16)                |                                                       | T <sub>A</sub> = -40 to 125 °C                | -2    | -   | 1.5   | %    |

| ∆ <sub>VDD</sub> (HSI16)                 | HSI16 oscillator frequency drift over V <sub>DD</sub> | V <sub>DD</sub> =1.62 V to 3.6 V              | -0.1  | -   | 0.05  | %    |

| t <sub>su</sub> (HSI16) <sup>(2)</sup>   | HSI16 oscillator start-up time                        | -                                             | -     | 0.8 | 1.2   | μs   |

| t <sub>stab</sub> (HSI16) <sup>(2)</sup> | HSI16 oscillator<br>stabilization time                | -                                             | -     | 3   | 5     | μs   |

| I <sub>DD</sub> (HSI16) <sup>(2)</sup>   | HSI16 oscillator power<br>consumption                 | -                                             | -     | 155 | 190   | μA   |

#### Table 59. HSI16 oscillator characteristics<sup>(1)</sup>

1. Guaranteed by characterization results.

2. Guaranteed by design.

| Speed | Symbol                         | Parameter                                  | Conditions                                 | Min | Max                | Unit  |

|-------|--------------------------------|--------------------------------------------|--------------------------------------------|-----|--------------------|-------|

|       |                                |                                            | C=50 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 50                 |       |

|       |                                |                                            | C=50 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 25                 |       |

|       | Fmax                           |                                            | C=50 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 5                  | MHz   |

|       | Fillax                         | Maximum frequency                          | C=10 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 100 <sup>(3)</sup> | IVINZ |

|       |                                |                                            | C=10 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 37.5               |       |

| 10    |                                |                                            | C=10 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 5                  |       |

| 10    |                                |                                            | C=50 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 5.8                |       |

|       |                                |                                            | C=50 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 11                 | ns    |

|       | T=/Tf                          | Tr/Tf Output rise and fall time            | C=50 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 28                 |       |

|       | 11/11                          |                                            | C=10 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 2.5                |       |

|       |                                |                                            | C=10 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 5                  |       |

|       |                                |                                            | C=10 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 12                 |       |

|       |                                |                                            | C=30 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 120 <sup>(3)</sup> | MHz   |

|       |                                |                                            | C=30 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 50                 |       |

|       | Emay                           |                                            | C=30 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 10                 |       |

|       | Fmax                           | Maximum frequency                          | C=10 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 180 <sup>(3)</sup> |       |

| 11    |                                |                                            | C=10 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 75                 |       |

|       |                                | C=10 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -                                          | 10  |                    |       |

|       |                                |                                            | C=30 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 3.3                |       |

| Tr/Tf | r/Tf Output rise and fall time | C=30 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -                                          | 6   | ns                 |       |

|       |                                |                                            | C=30 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 16                 |       |

| [m]   | Fmax                           | Maximum frequency                          |                                            | -   | 1                  | MHz   |

| Fm+   | Tf                             | Output fall time <sup>(4)</sup>            | C=50 pF, 1.6 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 5                  | ns    |

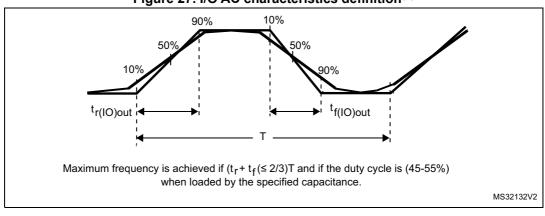

The I/O speed is configured using the OSPEEDRy[1:0] bits. The Fm+ mode is configured in the SYSCFG\_CFGR1 register. Refer to the RM0394 reference manual for a description of GPIO Port configuration register.

2. Guaranteed by design.

3. This value represents the I/O capability but the maximum system frequency is limited to 80 MHz.

4. The fall time is defined between 70% and 30% of the output waveform accordingly to I<sup>2</sup>C specification.

1. Refer to Table 73: I/O AC characteristics.

#### 6.3.15 NRST pin characteristics

The NRST pin input driver uses the CMOS technology. It is connected to a permanent pull-up resistor,  $\mathsf{R}_{\mathsf{PU}}.$

Unless otherwise specified, the parameters given in the table below are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 23: General operating conditions*.

| Symbol                 | Parameter                                          | Conditions                        | Min                                 | Тур | Мах                                 | Unit |

|------------------------|----------------------------------------------------|-----------------------------------|-------------------------------------|-----|-------------------------------------|------|

| V <sub>IL(NRST)</sub>  | NRST input low level voltage                       | -                                 | -                                   | -   | 0.3 <sub>x</sub> V <sub>DDIOx</sub> | v    |

| V <sub>IH(NRST)</sub>  | NRST input high level voltage                      | -                                 | 0.7 <sub>x</sub> V <sub>DDIOx</sub> | -   | -                                   | v    |

| V <sub>hys(NRST)</sub> | NRST Schmitt trigger voltage hysteresis            | -                                 | -                                   | 200 | -                                   | mV   |

| R <sub>PU</sub>        | Weak pull-up<br>equivalent resistor <sup>(2)</sup> | V <sub>IN</sub> = V <sub>SS</sub> | 25                                  | 40  | 55                                  | kΩ   |

| V <sub>F(NRST)</sub>   | NRST input filtered<br>pulse                       | -                                 | -                                   | -   | 70                                  | ns   |

| V <sub>NF(NRST)</sub>  | NRST input not filtered pulse                      | 1.71 V ≤ V <sub>DD</sub> ≤ 3.6 V  | 350                                 | -   | -                                   | ns   |

Table 74. NRST pin characteristics<sup>(1)</sup>

1. Guaranteed by design.

2. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is minimal (~10% order).

#### 6.3.18 Analog-to-Digital converter characteristics

Unless otherwise specified, the parameters given in *Table 77* are preliminary values derived from tests performed under ambient temperature,  $f_{PCLK}$  frequency and  $V_{DDA}$  supply voltage conditions summarized in *Table 23: General operating conditions*.

*Note:* It is recommended to perform a calibration after each power-up.

| Symbol                          | Parameter                          | Conditions                                        | Min                                                     | Тур                                           | Max                                                     | Unit                |

|---------------------------------|------------------------------------|---------------------------------------------------|---------------------------------------------------------|-----------------------------------------------|---------------------------------------------------------|---------------------|

| V <sub>DDA</sub>                | Analog supply voltage              | -                                                 | 1.62                                                    | -                                             | 3.6                                                     | V                   |

|                                 |                                    | V <sub>DDA</sub> ≥ 2 V                            | 2                                                       | -                                             | V <sub>DDA</sub>                                        | V                   |

| V <sub>REF+</sub>               | Positive reference voltage         | V <sub>DDA</sub> < 2 V                            |                                                         | V <sub>DDA</sub>                              | •                                                       | V                   |

| V <sub>REF-</sub>               | Negative reference voltage         | -                                                 |                                                         | $V_{SSA}$                                     |                                                         | V                   |

| f                               |                                    | Range 1                                           | 0.14                                                    | -                                             | 80                                                      | MHz                 |

| f <sub>ADC</sub>                | ADC clock frequency                | Range 2                                           | 0.14                                                    | -                                             | 26                                                      | WIHZ                |

|                                 |                                    | Resolution = 12 bits                              | -                                                       | -                                             | 5.33                                                    |                     |

|                                 | Sampling rate for FAST             | Resolution = 10 bits                              | -                                                       | -                                             | 6.15                                                    |                     |

|                                 | channels                           | Resolution = 8 bits                               | -                                                       | -                                             | 7.27                                                    |                     |

| £                               |                                    | Resolution = 6 bits                               | -                                                       | -                                             | 8.88                                                    | Maria               |

| f <sub>s</sub>                  | Sampling rate for SLOW channels    | Resolution = 12 bits                              | -                                                       | -                                             | 4.21                                                    | Msps                |

|                                 |                                    | Resolution = 10 bits                              | -                                                       | -                                             | 4.71                                                    |                     |

|                                 |                                    | Resolution = 8 bits                               | -                                                       | -                                             | 5.33                                                    |                     |

|                                 |                                    | Resolution = 6 bits                               | -                                                       | -                                             | 6.15                                                    |                     |

| f <sub>TRIG</sub>               | External trigger frequency         | f <sub>ADC</sub> = 80 MHz<br>Resolution = 12 bits | -                                                       | -                                             | 5.33                                                    | MHz                 |

|                                 |                                    | Resolution = 12 bits                              | -                                                       | -                                             | 15                                                      | 1/f <sub>ADC</sub>  |

| V <sub>CMIN</sub>               | Input common mode                  | Differential mode                                 | (V <sub>REF+</sub> +<br>V <sub>REF-</sub> )/2<br>- 0.18 | (V <sub>REF+</sub> +<br>V <sub>REF-</sub> )/2 | (V <sub>REF+</sub> +<br>V <sub>REF-</sub> )/2<br>+ 0.18 | V                   |

| V <sub>AIN</sub> <sup>(3)</sup> | Conversion voltage range(2)        | -                                                 | 0                                                       | -                                             | V <sub>REF+</sub>                                       | V                   |

| R <sub>AIN</sub>                | External input impedance           | -                                                 | -                                                       | -                                             | 50                                                      | kΩ                  |

| C <sub>ADC</sub>                | Internal sample and hold capacitor | -                                                 | -                                                       | 5                                             | -                                                       | pF                  |

| t <sub>STAB</sub>               | Power-up time                      | -                                                 |                                                         | 1                                             |                                                         | conversion<br>cycle |

| +                               | Calibration time                   | f <sub>ADC</sub> = 80 MHz                         |                                                         | 1.45                                          |                                                         | μs                  |

| t <sub>CAL</sub>                |                                    | -                                                 |                                                         | 116                                           |                                                         |                     |

| Table 77  |     | characteristics | (1) (2) |

|-----------|-----|-----------------|---------|

| Table 77. | ADC | characteristics | (1) (4) |

| Prescaler divider | PR[2:0] bits | Min timeout RL[11:0]=<br>0x000 | Max timeout RL[11:0]=<br>0xFFF | Unit |  |  |

|-------------------|--------------|--------------------------------|--------------------------------|------|--|--|

| /4                | 0            | 0.125                          | 512                            |      |  |  |

| /8                | 1            | 0.250                          | 1024                           |      |  |  |

| /16               | 2            | 0.500                          | 2048                           |      |  |  |

| /32               | 3            | 1.0                            | 4096                           | ms   |  |  |

| /64               | 4            | 2.0                            | 8192                           |      |  |  |

| /128              | 5            | 4.0                            | 16384                          |      |  |  |

| /256              | 6 or 7       | 8.0                            | 32768                          |      |  |  |

Table 92. IWDG min/max timeout period at 32 kHz (LSI)<sup>(1)</sup>

1. The exact timings still depend on the phasing of the APB interface clock versus the LSI clock so that there is always a full RC period of uncertainty.

| Prescaler | WDGTB | Min timeout value | Max timeout value | Unit       |

|-----------|-------|-------------------|-------------------|------------|

| 1         | 0     | 0.0512            | 3.2768            |            |

| 2         | 1     | 0.1024            | 6.5536            | <b>m</b> 0 |

| 4         | 2     | 0.2048            | 13.1072           | ms         |

| 8         | 3     | 0.4096            | 26.2144           |            |

#### 6.3.26 Communication interfaces characteristics

#### I<sup>2</sup>C interface characteristics

The I2C interface meets the timings requirements of the  $I^2$ C-bus specification and user manual rev. 03 for:

- Standard-mode (Sm): with a bit rate up to 100 kbit/s

- Fast-mode (Fm): with a bit rate up to 400 kbit/s

- Fast-mode Plus (Fm+): with a bit rate up to 1 Mbit/s.

The I2C timings requirements are guaranteed by design when the I2C peripheral is properly configured (refer to RM0394 reference manual).

The SDA and SCL I/O requirements are met with the following restrictions: the SDA and SCL I/O pins are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and  $V_{DDIOx}$  is disabled, but is still present. Only FT\_f I/O pins support Fm+ low level output current maximum requirement. Refer to Section 6.3.14: I/O port characteristics for the I2C I/Os characteristics.

All I2C SDA and SCL I/Os embed an analog filter. Refer to the table below for the analog filter characteristics:

#### **SAI characteristics**

Unless otherwise specified, the parameters given in *Table 98* for SAI are derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 23: General operating conditions*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels:  $0.5 \times V_{DD}$

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (CK,SD,FS).

| Symbol                   | Parameter                          | Conditions                                                            |                                   | Мах  | Unit |  |

|--------------------------|------------------------------------|-----------------------------------------------------------------------|-----------------------------------|------|------|--|

| f <sub>MCLK</sub>        | SAI Main clock output              | -                                                                     | -                                 | 50   | MHz  |  |

|                          |                                    | Master transmitter<br>2.7 ≤ V <sub>DD</sub> ≤ 3.6<br>Voltage Range 1  | -                                 | 18.5 |      |  |

|                          |                                    | Master transmitter<br>1.71 ≤ V <sub>DD</sub> ≤ 3.6<br>Voltage Range 1 | -                                 | 12.5 |      |  |

|                          |                                    | Master receiver<br>Voltage Range 1                                    | -                                 | 25   |      |  |

| f <sub>CK</sub>          | SAI clock frequency <sup>(2)</sup> | Slave transmitter<br>2.7 ≤ V <sub>DD</sub> ≤ 3.6<br>Voltage Range 1   | -                                 | 22.5 | MHz  |  |

|                          |                                    | Slave transmitter<br>1.71 ≤ V <sub>DD</sub> ≤ 3.6<br>Voltage Range 1  | -                                 | 14.5 |      |  |

|                          |                                    |                                                                       | Slave receiver<br>Voltage Range 1 | -    | 25   |  |

|                          |                                    | Voltage Range 2                                                       | -                                 | 12.5 |      |  |

| +                        | FS valid time                      | Master mode<br>2.7 $\leq$ V <sub>DD</sub> $\leq$ 3.6                  | -                                 | 22   | 20   |  |

| t <sub>v(FS)</sub>       |                                    | Master mode<br>$1.71 \le V_{DD} \le 3.6$                              | -                                 | 40   | ns   |  |

| t <sub>h(FS)</sub>       | FS hold time                       | Master mode                                                           | 10                                | -    | ns   |  |

| t <sub>su(FS)</sub>      | FS setup time                      | Slave mode                                                            | 1                                 | -    | ns   |  |

| t <sub>h(FS)</sub>       | FS hold time                       | Slave mode                                                            | 2                                 | -    | ns   |  |

| t <sub>su(SD_A_MR)</sub> | Data input setup time              | Master receiver                                                       | 2                                 | -    | 200  |  |

| t <sub>su(SD_B_SR)</sub> |                                    | Slave receiver                                                        | 1.5                               | -    | ns   |  |

| t <sub>h(SD_A_MR)</sub>  | Data input hold time               | Master receiver                                                       | 5                                 | -    | ns   |  |

| $t_{h(SD\_B\_SR)}$       |                                    | Slave receiver                                                        | 2.5                               | -    | 113  |  |

#### Table 98. SAI characteristics<sup>(1)</sup>

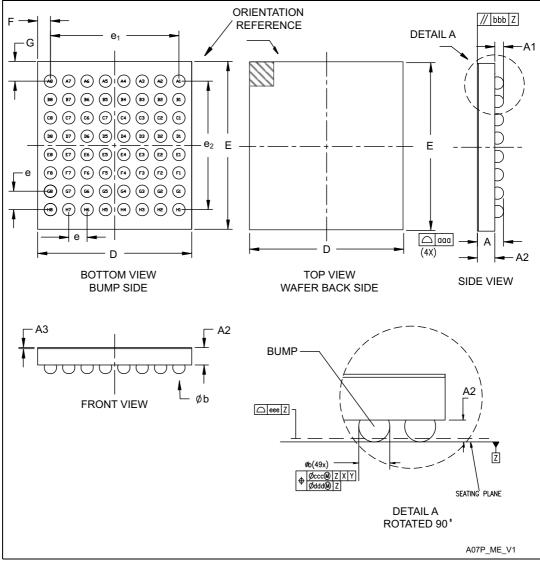

## 7.5 WLCSP64 package information

1. Dimensions are expressed in millimeters.

| Date Revision |                  | Changes                                                                                                                                                                                                                                        |

|---------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21-May-2018   | 4<br>(continued) | Updated Table 51: Peripheral current consumption.<br>Added Section 6.3.16: Extended interrupt and event<br>controller input (EXTI) characteristics.<br>Updated Table 71: I/O static characteristics.<br>Updated Table 83: DAC characteristics. |

#### Table 113. Document revision history (continued)