#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                        |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | TriCore™                                                                        |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 100MHz                                                                          |

| Connectivity               | EBI/EMI, FIFO, I <sup>2</sup> C, IrDA, SPI, UART/USART                          |

| Peripherals                | DMA, POR, PWM, WDT                                                              |

| Number of I/O              | 72                                                                              |

| Program Memory Size        | -                                                                               |

| Program Memory Type        | ROMIess                                                                         |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 144K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.43V ~ 1.58V                                                                   |

| Data Converters            | -                                                                               |

| Oscillator Type            | External                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 208-LBGA                                                                        |

| Supplier Device Package    | P-LBGA-208-2                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-tc1100-l100eb-bb |

|                            |                                                                                 |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                  | ata Sheet<br>Information<br>History: | 2005-02                            | V1.0 |

|------------------|--------------------------------------|------------------------------------|------|

| Previous \       | /ersion:                             | none                               |      |

| Page Subjects (m |                                      | major changes since last revision) |      |

|                  |                                      |                                    |      |

|                  |                                      |                                    |      |

Controller Area Network (CAN): License of Robert Bosch GmbH

#### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to: mcdocu.comments@infineon.com

#### **General Device Information**

# Table 2-1Pin Definitions and Functions (cont'd)

| Symbol  | Pin   | In<br>Out | PU/<br>PD <sup>1)</sup> | Functions                       |                                          |  |  |

|---------|-------|-----------|-------------------------|---------------------------------|------------------------------------------|--|--|

| P1      |       | I/O       |                         | Port 1                          |                                          |  |  |

|         |       |           |                         | Port 1 serves                   | as 16-bit bi-directional general purpose |  |  |

|         |       |           |                         | I/O port whicl                  | h can be used for input/output for OCDS  |  |  |

|         |       |           |                         | L2, SSC0/1,                     | EBU and SCU.                             |  |  |

| P1.0    | D11   | 1         | PUC                     | SWCFG0                          | Software configuration 0                 |  |  |

|         |       | 0         |                         | OCDSA_0                         | OCDS L2 Debug Line A0                    |  |  |

| P1.1    | C12   | I         | PUC                     | SWCFG1                          | Software configuration 1                 |  |  |

|         |       | 0         |                         | OCDSA_1                         | OCDS L2 Debug Line A1                    |  |  |

| P1.2    | D12   | I         | PUC                     | SWCFG2                          | Software configuration 2                 |  |  |

|         |       | 0         |                         | OCDSA_2                         | OCDS L2 Debug Line A2                    |  |  |

| P1.3    | B12   | 1         | PUC                     | SWCFG3                          | Software configuration 3                 |  |  |

|         |       | 0         |                         | OCDSA_3                         | OCDS L2 Debug Line A3                    |  |  |

| P1.4    | C11   | I         | PUC                     | SWCFG4                          | Software configuration 4                 |  |  |

|         |       | 0         |                         | OCDSA_4                         | OCDS L2 Debug Line A4                    |  |  |

| P1.5    | C13   | I         | PUC                     | SWCFG5                          | Software configuration 5                 |  |  |

|         |       | 0         |                         | OCDSA_5                         | OCDS L2 Debug Line A5                    |  |  |

| P1.6    | A12   | I         | PUC                     | SWCFG6                          | Software configuration 6                 |  |  |

|         |       | 0         |                         | OCDSA_6                         | OCDS L2 Debug Line A6                    |  |  |

| P1.7    | B13   | I         | PUC                     | SWCFG7                          | Software configuration 7                 |  |  |

|         |       | 0         |                         | OCDSA_7                         | OCDS L2 Debug Line A7                    |  |  |

| P1.8    | A13   |           | PUC                     | SWCFG8                          | Software configuration 8                 |  |  |

| - / -   |       | 0         |                         | OCDSA_8 OCDS L2 Debug Line A8   |                                          |  |  |

| P1.9    | A14   |           | PUC                     | SWCFG9 Software configuration 9 |                                          |  |  |

| - / / - |       | 0         |                         | OCDSA_9                         | OCDS L2 Debug Line A9                    |  |  |

| P1.10   | B14   |           | PUC                     | SWCFG10                         | Software configuration 10                |  |  |

|         |       | 0         |                         | OCDSA_10                        | OCDS L2 Debug Line A10                   |  |  |

| P1.11   | C14   |           | PUC                     | SWCFG11                         | Software configuration 11                |  |  |

|         |       | 0         |                         | OCDSA_11                        | OCDS L2 Debug Line A1                    |  |  |

| 54.40   | = 10  | 0         | 5.1.0                   | SLSO0_1                         | SSC0 Slave Select output 1               |  |  |

| P1.12   | F13   |           | PUC                     | SWCFG12                         | Software configuration 12                |  |  |

|         |       | 0         |                         | OCDSA_12                        | OCDS L2 Debug Line A12                   |  |  |

| D4 40   | - 4 4 | 0         | DUO                     | SLSO1_1                         | SSC1 Slave Select output 1               |  |  |

| P1.13   | E14   |           | PUC                     | SWCFG13                         | Software configuration 13                |  |  |

|         |       | 0         |                         | OCDSA_13                        | OCDS L2 Debug Line A13                   |  |  |

|         |       | 0         |                         | SLSO0_2                         | SSC0 Slave Select output 2               |  |  |

| P1.14   | D14   | 0         | PUC                     | SLSO1_2                         | SSC1 Slave Select output 2               |  |  |

|         |       |           |                         | SWCFG14                         | Software configuration 14                |  |  |

|         |       | 0         |                         | OCDSA_14                        | OCDS L2 Debug Line A14                   |  |  |

#### **General Device Information**

# Table 2-1Pin Definitions and Functions (cont'd)

| Symbol | Pin | In<br>Out | PU/<br>PD <sup>1)</sup> | Functions       |                                                                                               |  |  |

|--------|-----|-----------|-------------------------|-----------------|-----------------------------------------------------------------------------------------------|--|--|

| P1.15  | F14 | I         | PUC                     | SLSI0           | SSC0 Slave Select Input                                                                       |  |  |

|        |     | 0         |                         | RMW             | EBU Read Modify Write                                                                         |  |  |

|        |     | I         |                         | SWCFG15         | Software configuration 15                                                                     |  |  |

|        |     | 0         |                         | OCDSA_15        | OCDS L2 Debug Line A15                                                                        |  |  |

| P2     |     | I/O       |                         | Port 2          |                                                                                               |  |  |

|        |     |           |                         |                 | bit bi-directional general purpose I/O port<br>alternatively used for ASC0/1, SSC0/1,<br>SCU. |  |  |

| P2.0   | P12 | I/O       | PUC                     | RXD0            | ASC0 receiver input/output line                                                               |  |  |

|        |     | 0         |                         | CSEMU           | EBU Chip Select Output for Emulator                                                           |  |  |

|        |     |           |                         |                 | Region                                                                                        |  |  |

| P2.1   | P11 | 0         | PUC                     | TXD0            | ASC0 transmitter output line                                                                  |  |  |

|        |     | 1         |                         | TESTMODE        | Test Mode Select Input                                                                        |  |  |

| P2.2   | P13 | I/O       | PUC                     | MRST0           | SSC0 master receive/slave transmit                                                            |  |  |

|        |     |           |                         |                 | input/output                                                                                  |  |  |

| P2.3   | P14 | I/O       | PUC                     | MTSR0           | SSC0 master transmit/slave receive                                                            |  |  |

|        |     |           |                         |                 | input/output                                                                                  |  |  |

| P2.4   | N15 | I/O       | PUC                     | SCLK0           | SSC0 clock input/output line                                                                  |  |  |

| P2.5   | N14 | I/O       | PUC                     | MRST1A          | SSC1 master receive/slave transmit                                                            |  |  |

|        |     |           |                         |                 | input/output A                                                                                |  |  |

| P2.6   | N12 | I/O       | PUC                     | MTSR1A          |                                                                                               |  |  |

|        |     |           |                         |                 | receive input/output A                                                                        |  |  |

| P2.7   | K16 | I/O       | PUC                     | SCLK1A          | SSC1 clock input/output line A                                                                |  |  |

| P2.8   | J16 | I/O       | PUC                     | RXD1A           | ASC1 receiver input/output line A                                                             |  |  |

| P2.9   | H16 | 0         | PUC                     | TXD1A           | ASC1 transmitter output line A                                                                |  |  |

| P2.10  | L13 | —         | PUC                     |                 |                                                                                               |  |  |

| P2.11  | G16 |           | PUC                     |                 | 110 Carial Data line 0                                                                        |  |  |

| P2.12  | K15 | I/O       | —                       | SDA0            | IIC Serial Data line 0                                                                        |  |  |

|        |     | 0         |                         | SLSO0_3         | SSC0 Slave Select output 3                                                                    |  |  |

| P2.13  | K14 | 1/0       |                         | SCL0            | IIC clock line 0                                                                              |  |  |

|        | E16 | 0         |                         | SLSO1_3         | SSC1 Slave Select output 3                                                                    |  |  |

| P2.14  | F16 | 1/0       | —                       | SDA1            | IIC Serial Data line 1                                                                        |  |  |

| D2 15  | E16 | 0         |                         | SLSO0_4<br>SCL1 | SSC0 Slave Select output 4<br>IIC clock line 1                                                |  |  |

| P2.15  |     | 1/O<br>O  |                         | SLSO1 4         | SSC1 Slave Select output 4                                                                    |  |  |

|        |     | 0         |                         | JLJUI_4         |                                                                                               |  |  |

#### **General Device Information**

#### Table 2-1Pin Definitions and Functions (cont'd)

| Symbol | Pin | In<br>Out | PU/<br>PD <sup>1)</sup> | Functions                                                                                      |  |  |

|--------|-----|-----------|-------------------------|------------------------------------------------------------------------------------------------|--|--|

| BFCLKI | D1  | I         |                         | Burst Flash Clock Input (Clock Feedback)                                                       |  |  |

| BFCLKO | E1  | 0         |                         | Burst Flash Clock Output<br>Accesses to Burst Flash devices are synchronized to<br>this clock. |  |  |

| RD     | P2  | 0         | PUC                     | EBU Read Control Line                                                                          |  |  |

|        |     |           |                         | Output in master mode<br>Input in slave mode                                                   |  |  |

| RD/WR  | Т3  | 0         | PUC                     | <b>EBU Write Control Line</b><br>Output in master mode<br>Input in slave mode                  |  |  |

| WAIT   | B9  | 1         | PUC                     | EBU Wait Control Line                                                                          |  |  |

| ALE    | R3  | 0         | PDC                     | EBU Address Latch Enable Output                                                                |  |  |

| MR/W   | P3  | 0         | PUC                     | EBU Motorola-style Read/Write Output                                                           |  |  |

| BAA    | A11 | 0         | PUC                     | <b>EBU Burst Address Advance Output</b><br>For advancing address in a Burst Flash access       |  |  |

| ADV    | B11 | 0         | PUC                     | EBU Burst Flash Address Valid Output                                                           |  |  |

#### **General Device Information**

| Table 2-1 | Pin Definitions and Functions | (conťd) |

|-----------|-------------------------------|---------|

|-----------|-------------------------------|---------|

| Symbol              | Pin        | In<br>Out | PU/<br>PD <sup>1)</sup> | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------|------------|-----------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     |            |           |                         | EBU Address Bus Input/Output Lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| A0                  | K1         | 0         | PUC                     | EBU Address Bus Line 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A1                  | L1         | 0         | PUC                     | EBU Address Bus Line 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A2                  | M1         | 0         | PUC                     | EBU Address Bus Line 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A3                  | N1         | 0         | PUC                     | EBU Address Bus Line 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A4                  | P1         | 0         | PUC                     | EBU Address Bus Line 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A5                  | J2         | 0         | PUC                     | EBU Address Bus Line 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A6                  | K2         | 0         | PUC                     | EBU Address Bus Line 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A7                  | L2         | 0         | PUC                     | EBU Address Bus Line 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A8                  | M2         | 0         | PUC                     | EBU Address Bus Line 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A9                  | N2         | 0         | PUC                     | EBU Address Bus Line 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A10                 | J3         | 0         | PUC                     | EBU Address Bus Line 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A11                 | K3         | 0         | PUC                     | EBU Address Bus Line 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A12                 | L3         | 0         | PUC                     | EBU Address Bus Line 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A13                 | M3         | 0         | PUC                     | EBU Address Bus Line 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A14                 | K4         | 0         | PUC                     | EBU Address Bus Line 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A15                 | A8         | 0         | PUC                     | EBU Address Bus Line 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A16                 | A9         | 0         | PUC                     | EBU Address Bus Line 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A17                 | A10        | 0         | PUC                     | EBU Address Bus Line 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A18                 | B10        | 0         | PUC                     | EBU Address Bus Line 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A19                 | C10        | 0         | PUC                     | EBU Address Bus Line 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A20                 | D10        | 0         | PUC                     | EBU Address Bus Line 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A21                 | T4         | 0         | PUC                     | EBU Address Bus Line 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A22                 | R4         | 0         | PUC                     | EBU Address Bus Line 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A23                 | P4         | 0         | PUC                     | EBU Address Bus Line 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| XTAL1<br>XTAL2      | M16<br>N16 | I<br>O    |                         | <b>Oscillator/PLL/Clock Generator Input/Output Pins</b><br>XTAL1 is the input to the main oscillator amplifier and<br>input to the internal clock generator. XTAL2 is the<br>output of the main oscillator amplifier circuit. For<br>clocking of the device from an external source, XTAL1<br>is driven with the clock signal while XTAL2 is left<br>unconnected. For crystal oscillator operation, XTAL1<br>and XTAL2 are connected to the crystal with the<br>appropriate recommended oscillator circuitry. |

| V <sub>DDOSC3</sub> | P16        | <u> </u>  |                         | Main Oscillator Power Supply (3.3 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| V <sub>SSOSC3</sub> | R16        |           |                         | Main Oscillator Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| V <sub>DDOSC</sub>  | L16        |           |                         | Main Oscillator Power Supply (1.5 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

## TC1100

#### Advance Information

#### **Functional Description**

#### Table 3-1 TC1100 Block Address Map (cont'd)

| Seg-<br>ment | Address<br>Range                                   | •       |                                                                                                                                                                       | DMI<br>Acc.                          | PMI<br>Acc.                          |            |  |  |  |

|--------------|----------------------------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------|------------|--|--|--|

|              | D000 0000 <sub>H</sub> –<br>D000 6FFF <sub>H</sub> | 28 KB   | DMI Local Data RAM<br>(LDRAM)                                                                                                                                         | DMI<br>local                         | via<br>LMB                           |            |  |  |  |

|              | D000 7000 <sub>H</sub> –<br>D3FF FFFF <sub>H</sub> | ~ 64 MB | Reserved                                                                                                                                                              |                                      |                                      |            |  |  |  |

| 13           | D400 0000 <sub>H</sub> –<br>D400 7FFF <sub>H</sub> | 32 KB   | PMI Local Code Scratch Pad<br>RAM (SPRAM)                                                                                                                             | via<br>LMB                           | PMI<br>local                         |            |  |  |  |

|              | D400 8000 <sub>H</sub> –<br>D7FF FFFF <sub>H</sub> | ~64 MB  | Reserved                                                                                                                                                              |                                      |                                      |            |  |  |  |

|              | D800 0000 <sub>H</sub> –<br>DDFF FFFF <sub>H</sub> | 96 MB   | External Memory Space                                                                                                                                                 | via                                  | via                                  |            |  |  |  |

|              | DE00 0000 <sub>H</sub> –<br>DEFF FFFF <sub>H</sub> | 16 MB   | Emulator Memory Space                                                                                                                                                 | LMB                                  | LMB                                  |            |  |  |  |

|              | DF00 0000 <sub>H</sub> –<br>DFFF BFFF <sub>H</sub> | ~16 MB  | Reserved                                                                                                                                                              | _                                    | _                                    |            |  |  |  |

|              | DFFF C000 <sub>H</sub> –<br>DFFF FFFF <sub>H</sub> | 16 KB   | Boot ROM Space                                                                                                                                                        | via FPI                              | via<br>FPI                           | led        |  |  |  |

|              | E000 0000 <sub>H</sub> –<br>E7FF FFFF <sub>H</sub> | 128 MB  | External Memory Space                                                                                                                                                 | via<br>LMB                           | via<br>LMB                           | non-cached |  |  |  |

| 14           | E800 0000 <sub>H</sub> –<br>E83F FFFF <sub>H</sub> | 4 MB    | MB Reserved for mapped space<br>for lower 4 Mbytes of Local<br>Memory in Segment 12<br>(Transformed by LFI bridge to                                                  |                                      | access<br>only<br>from<br>FPI        |            |  |  |  |

|              |                                                    |         | C000 0000 <sub>H</sub> – C03F FFF <sub>H</sub> )                                                                                                                      | bus<br>side of<br>LFI                | bus<br>side of<br>LFI                |            |  |  |  |

|              | E840 0000 <sub>H</sub> –<br>E84F FFFF <sub>H</sub> | 1 MB    | Reserved for mapped space<br>for lower 1 Mbyte of Local<br>Memory in Segment 13<br>(Transformed by LFI bridge to<br>D000 0000 <sub>H</sub> – D00F FFFF <sub>H</sub> ) | access<br>only<br>from<br>FPI<br>bus | access<br>only<br>from<br>FPI<br>bus |            |  |  |  |

|              | E850 0000 <sub>H</sub> –<br>E85F FFFF <sub>H</sub> | 1 MB    | Reserved for mapped space<br>for 1 Mbyte of Local Memory in<br>Segment 13<br>(Transformed by LFI bridge to<br>D400 0000 <sub>H</sub> – D40F FFFF <sub>H</sub> )       | side of<br>LFI                       | side of<br>LFI                       |            |  |  |  |

## TC1100

#### **Advance Information**

#### **Functional Description**

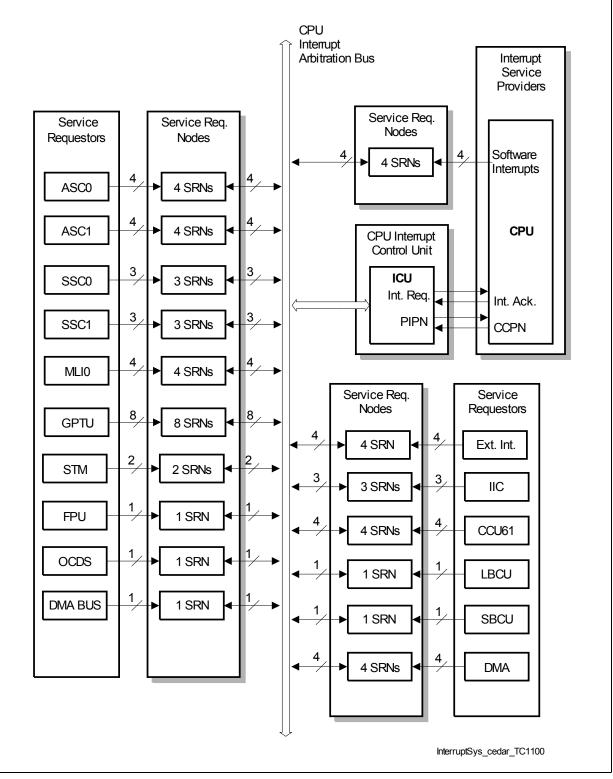

Figure 3-3 Block Diagram of the TC1100 Interrupt System

#### **Functional Description**

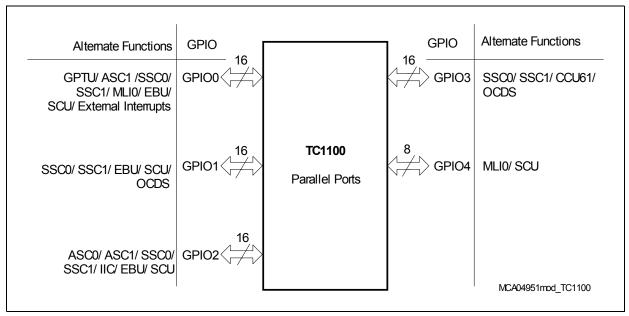

#### 3.8 Parallel Ports

The TC1100 has 72 digital input/output port lines, which are organized into four parallel 16-bit ports and one parallel 8-bit port, Port P0 to Port P4 with 3.3 V nominal voltage.

The digital parallel ports can be used as general purpose I/O lines or they can perform input/output functions for the on-chip peripheral units. An overview on the port-to-peripheral unit assignment is shown in **Figure 3-4**.

Figure 3-4 Parallel Ports of the TC1100

## **Functional Description**

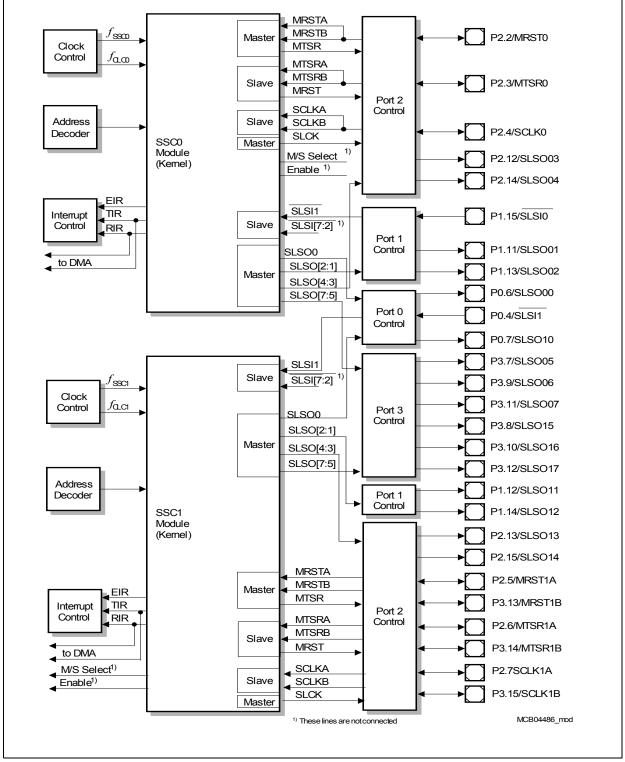

Figure 3-6 General Block Diagram of the SSC Interfaces

#### **Functional Description**

- Evaluation of the device address in slave mode

- · Bus access arbitration in multimaster mode

#### Features:

- · Extended buffer allows up to 4 send/receive data bytes to be stored

- Selectable baud rate generation

- Support of standard 100 kBaud and extended 400 kBaud data rates

- Operation in 7-bit addressing mode or 10-bit addressing mode

- · Flexible control via interrupt service routines or by polling

- Dynamic access to up to 2 physical IIC buses

#### 3.15 System Timer

The STM within the TC1100 is designed for global system timing applications requiring both high precision and long range. The STM provides the following features:

- Free-running 56-bit counter

- All 56 bits can be read synchronously

- Different 32-bit portions of the 56-bit counter can be read synchronously

- Flexible interrupt generation on partial STM content compare match

- Driven by clock  $f_{STM}$  after reset (default after reset is  $f_{STM} = f_{SYS} = 150 \text{ MHz}$ )

- Counting starts automatically after a reset operation

- STM is reset under following reset causes:

- Wake-up reset (PMG\_CON.DSRW must be set)

- Software reset (RST\_REQ.RRSTM must be set)

- Power-on reset

- <u>STM</u> (and the clock divider) is not reset at watchdog reset and hardware reset (HDRST = 0)

The STM is an upward counter, running with the system clock frequency  $f_{SYS}$  (after reset  $f_{STM} = f_{SYS}$ ). It is enabled per default after reset, and immediately starts counting up. Other than via reset, it is not possible to affect the contents of the timer during normal operation of the application; it can only be read, but not written to. Depending on the implementation of the clock control of the STM, the timer can optionally be disabled or suspended for power-saving and debugging purposes via a clock control register.

The maximum clock period is  $2^{56}/f_{STM}$ . At  $f_{STM}$  = 150 MHz (maximum), for example, the STM counts 15.2 years before overflowing. Thus, it is capable of continuously timing the entire expected product lifetime of a system without overflowing.

# TC1100

#### **Functional Description**

#### 3.19 Power Management System

The TC1100 power management system allows software to configure the various processing units to adjust automatically in order to draw the minimum necessary power for the application.

There are four power management modes:

- Run Mode

- Idle Mode

- Sleep Mode

- Deep Sleep Mode

Table 3-4 describes the features of the power management modes.

#### Table 3-4 Power Management Mode Summary

| Mode       | Description                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Run        | The system is fully operational. All clocks and peripherals are enabled, as determined by software.                                                                                                                                                                                                                                                                                                                                  |

| Idle       | The CPU clock is disabled, waiting for a condition to return it to run mode.<br>Idle mode can be entered by software when the processor has no active<br>tasks to perform. All peripherals remain powered and clocked. Processor<br>memory is accessible to peripherals. A reset, Watchdog Timer event, a<br>falling edge on the NMI pin, or any enabled interrupt event will return the<br>system to run mode.                      |

| Sleep      | The system clock continues to be distributed only to those peripherals programmed to operate in sleep mode. The other peripheral modules will be shut down by the suspend signal. Interrupts from operating peripherals, the Watchdog Timer, a falling edge on the NMI pin, or a reset event will return the system to run mode. Entering this state requires an orderly shut-down controlled by the Power Management State Machine. |

| Deep Sleep | The system clock is shut off; only an external signal will restart the system. Entering this state requires an orderly shut-down controlled by the Power Management State Machine (PMSM).                                                                                                                                                                                                                                            |

Besides these explicit software-controlled power-saving modes, special attention has been paid in the TC1100 to automatic power-saving in operating units that are currently not required or idle. In this case, they are shut off automatically until their operation is required again.

TC1100

#### Advance Information

#### **Functional Description**

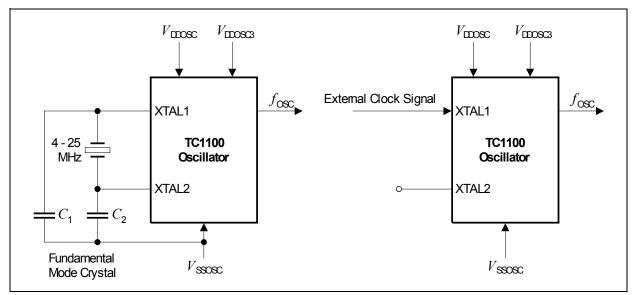

The oscillator circuit, which is designed to work with an external crystal oscillator or an external stable clock source, consists of an inverting amplifier with XTAL1 as input and XTAL2 as output.

**Figure 3-14** shows the recommended external oscillator circuitries for both operating modes, i.e. external crystal mode and external input clock mode.

#### Figure 3-14 Oscillator Circuitries

When using an external clock signal, it must be connected to XTAL1 and XTAL2 is left open (unconnected). When supplying the clock signal directly, not using a crystal and the oscillator, the input frequency can be in the range of 0 - 40 MHz if the PLL is not used, 4 - 40 MHz in case the PLL is used.

When using a crystal, its frequency can be within the range of 4 MHz to 25 MHz. An external oscillator load circuitry must be used, connected to both pins, XTAL1 and XTAL2. It consists normally of the two load capacitances, C1 and C2. For some crystals, a series damp resistor may be necessary. The exact values and related operating range are dependent on the crystal and have to be determined and optimized together with the crystal vendor using the negative resistance method. As starting point for the evaluation and for non-productive systems, the following load capacitor values might be used.

| Fundamental Mode Crystal Frequency<br>(approx., MHz) | Load Capacitors<br>C1, C2 (pF) |

|------------------------------------------------------|--------------------------------|

| 4                                                    | 33                             |

| 8                                                    | 18                             |

| 12                                                   | 12                             |

| 16                                                   | 10                             |

#### Table 3-5 Load Capacitors Select

#### **Functional Description**

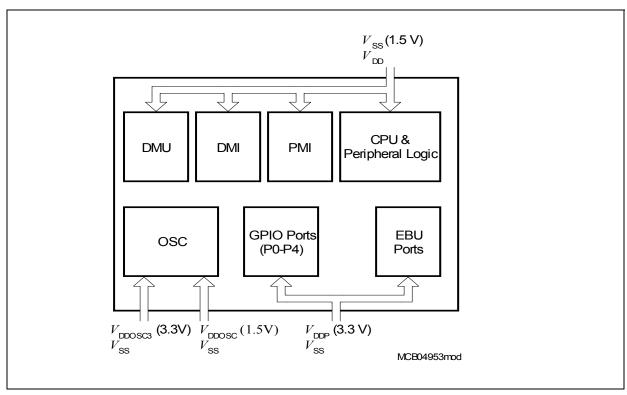

#### 3.22 Power Supply

The TC1100 provides an ingenious power supply concept in order to improve the EMI behavior as well as to minimize the crosstalk within on-chip modules.

**Figure 3-15** shows the TC1100's power supply concept, where certain logic modules are individually supplied with power. This concept improves the EMI behavior by reduction of the noise cross coupling.

Figure 3-15 TC1100 Power Supply Concept

#### **Electrical Parameters**

# 4 Electrical Parameters

## 4.1 General Parameters

#### 4.1.1 **Parameter Interpretation**

The parameters listed in this section represent partly the characteristics of the TC1100 and partly its requirements on the system. To aid interpreting the parameters easily when evaluating them for design purposes, they are indicated by the abbreviations in the "Symbol" column:

• cc

These parameters indicate **C**ontroller **C**haracteristics, which are distinctive features of the TC1100 and must be considered for system design.

• SR

These parameters indicate **S**ystem **R**equirements, which must be provided by the microcontroller system in which the TC1100 is included.

TC1100

#### **Electrical Parameters**

#### 4.1.3 **Operating Condition**

The following operating conditions must be complied with in order to ensure correct operation of the TC1100. All parameters specified in the following table refer to these operating conditions, unless otherwise indicated.

| Parameter                                               | Symbol              | Limi      | it Values | Unit | Notes                     |  |

|---------------------------------------------------------|---------------------|-----------|-----------|------|---------------------------|--|

|                                                         |                     | min. max. |           |      | Conditions                |  |

| Digital supply voltage                                  | $V_{DD}$            | 1.43      | 1.58      | V    | -                         |  |

|                                                         | $V_{DDP}$           | 3.14      | 3.47      | V    | -                         |  |

| Digital ground voltage                                  | V <sub>SS</sub>     |           | 0         | V    | -                         |  |

| Digital core supply current                             | I <sub>DD</sub>     | _         | 525       | mA   | -                         |  |

| Ambient temperature under bias                          | T <sub>A</sub>      | -40       | +85       | °C   | -                         |  |

| CPU clock                                               | fsys                | _1)       | 150       | MHz  | -                         |  |

| Overload current                                        | I <sub>OV</sub>     | -1        | 1         | mA   | 2)3)                      |  |

|                                                         |                     | -3        | 3         |      | duty cycle $\leq 25\%$    |  |

| Short circuit current                                   | I <sub>SC</sub>     | -1        | 1         | mA   | 4)                        |  |

|                                                         |                     | -3        | 3         |      | duty cycle $\leq 25\%$    |  |

| Absolute sum of overload +                              | $\Sigma  I_{OV}  +$ | -         | 50        | mA   | 3)                        |  |

| short circuit currents                                  | I <sub>SC</sub>     |           | 100       |      | duty cycle $\leq 25\%$    |  |

| Inactive device pin current<br>$(V_{DD} = V_{DDP} = 0)$ | I <sub>ID</sub>     | -1        | 1         | mA   | -                         |  |

| External load capacitance                               | CL                  | -         | 50        | pF   | -                         |  |

| ESD strength                                            | -                   | 2000      | -         | V    | Human Body<br>Model (HBM) |  |

<sup>1)</sup> The TC1100 uses a static design, so the minimum operation frequency is 0 MHz. However, due to test time restriction no lower frequency boundary is tested.

<sup>2)</sup> Overload conditions occur if the standard operating conditions are exceeded, i.e. the voltage on any pin exceeds the specified range (i.e.  $V_{OV} > V_{DDP} + 0.5 \text{ V}$  or  $V_{OV} < V_{SS}$  - 0.5 V). The absolute sum of input overload currents on all digital I/O pins may not exceed **50 mA**. The supply voltage must remain within the specified limits.

<sup>3)</sup> Not subject to production test, verified by design/characterization.

<sup>4)</sup> Applicable for digital inputs.

#### **Electrical Parameters**

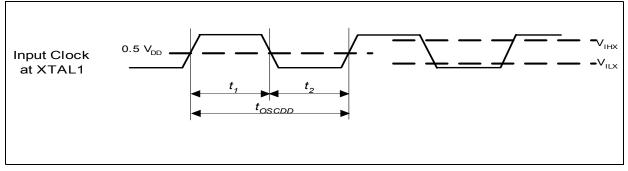

#### 4.3.4 Input Clock Timing

(Operating Conditions apply)

| Parameter                              | Symbol   | Limits       |     | Unit |     |

|----------------------------------------|----------|--------------|-----|------|-----|

|                                        |          |              | min | max  |     |

| Oscillator clock frequency             | with PLL | $f_{OSC}$ SR | 4   | 25   | MHz |

| Input clock frequency driving at XTAL1 | with PLL | foscdd<br>SR | -   | 40   | MHz |

| Input Clock Duty Cycle $(t_1 / t_2)$   | SR       | 45           | 55  | %    |     |

Figure 4-4 Input Clock Timing

#### **Electrical Parameters**

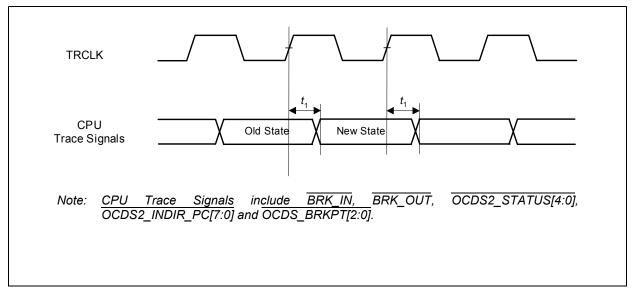

## 4.3.7 Timing for OCDS Trace and Breakpoint Signals

(Operating Conditions apply;  $C_{L}$ (TRCLK) = 25 pF,  $C_{L}$  = 50 pF)

| Parameter                              | Syr                   | nbol | Limits |     | Unit |

|----------------------------------------|-----------------------|------|--------|-----|------|

|                                        |                       |      | min    | max | -    |

| BRK_OUT valid from TRCLK _             | <i>t</i> <sub>1</sub> | CC   | _      | 5.2 | ns   |

| OCDS2_STATUS[4:0] valid from TRCLK _   | <i>t</i> <sub>1</sub> | CC   | 0      | 5   | ns   |

| OCDS2_INDIR_PC[7:0] valid from TRCLK _ | <i>t</i> <sub>1</sub> | CC   | 0      | 5   | ns   |

| OCDS2_BRKPT[2:0] valid from TRCLK _    | <i>t</i> <sub>1</sub> | CC   | 0      | 5   | ns   |

Figure 4-8 OCDS Trace Signals Timing

#### **Electrical Parameters**

#### 4.3.8.6 Timing for Multiplexed Access Signals

(Operating Conditions apply;  $C_{\rm L} = 50 \text{ pF})^{1)}$

| Parameter                                                                                                                                                   |                        | nbol | Limits |     | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|--------|-----|------|

|                                                                                                                                                             |                        |      | min    | max |      |

| ALE, $\overline{CSx}$ , RD/ $\overline{WR}$ , $\overline{RD}$ , MR/ $\overline{W}$ , $\overline{BC(3:0)}$ output valid time from output clock $\mathcal{A}$ | <i>t</i> <sub>1</sub>  | CC   | -      | 9   | ns   |

| ALE, $\overline{CSx}$ , RD/ $\overline{WR}$ , $\overline{RD}$ , MR/ $\overline{W}$ , $\overline{BC(3:0)}$ output hold time from output clock $\mathcal{A}$  | <i>t</i> <sub>2</sub>  | CC   | 0.0    | -   | ns   |

| AD(31:0) output valid time from output clock _                                                                                                              | t <sub>3</sub>         | CC   | _      | 9   | ns   |

| AD(31:0) output hold time from output clock _                                                                                                               | <i>t</i> <sub>4</sub>  | CC   | 0.0    | -   | ns   |

| AD(31:0) input setup time to output clock _                                                                                                                 | $t_5$                  | SR   | 1.4    | -   | ns   |

| AD(31:0) input hold time from output clock _                                                                                                                | <i>t</i> <sub>6</sub>  | SR   | 3      | -   | ns   |

| WAIT input setup time to output clock 🦨                                                                                                                     | t <sub>9</sub>         | SR   | 12     | _   | ns   |

| WAIT input hold time from output clock _                                                                                                                    | <i>t</i> <sub>10</sub> | SR   | 3      | _   | ns   |

| RMW output valid time from output clock 🦨                                                                                                                   | <i>t</i> <sub>11</sub> | CC   | -      | 8   | ns   |

| RMW output hold time from output clock 🖌                                                                                                                    | <i>t</i> <sub>12</sub> | CC   | 1.3    | _   | ns   |

| ALE width                                                                                                                                                   | <i>t</i> <sub>13</sub> | CC   | 8.5    | -   | ns   |

| AD(31:0) output hold time from RD/WR                                                                                                                        | t <sub>14</sub>        | CC   | 0      | _   | ns   |

The purpose for characterization of Asynchronous access is to provide the performance of all of the signals to user. User can decide whether an extra cycle is needed or not based on above parameters to generate signals with correct timing sequence. It is user's responsibility to program the correct phase length according to the memory/peripheral device specification and EBU Specification.

## TC1100

#### **Advance Information**

#### **Electrical Parameters**

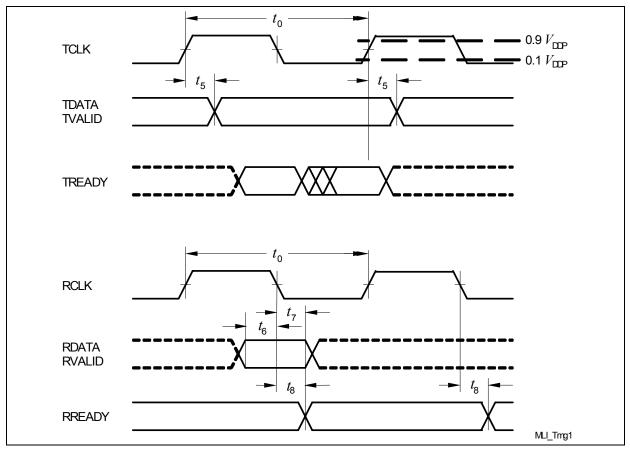

#### 4.3.9.2 MLI Interface Timing

(Operating Conditions apply;  $C_{L} = 50 \text{ pF}$ )

| Parameter                       | Symbol                |     | Limit                            | Unit |    |

|---------------------------------|-----------------------|-----|----------------------------------|------|----|

|                                 |                       |     | min.                             | max. |    |

| TCLK/RCLK clock period          |                       | /SR | 2*T <sub>MLI</sub> <sup>1)</sup> | -    | ns |

| MLI outputs delay from TCLK 🦨   | <i>t</i> <sub>5</sub> | CC  | 0                                | 8    | ns |

| MLI inputs setup to RCLK 飞      | t <sub>6</sub>        | SR  | 4                                | _    | ns |

| MLI inputs hold to RCLK -       | <i>t</i> <sub>7</sub> | SR  | 4                                | -    | ns |

| RREADY output delay from TCLK ٦ | <i>t</i> <sub>8</sub> | CC  | 0                                | 8    | ns |

<sup>1)</sup>  $T_{MLImin} = T_{SYS} = 1/f_{SYS}$ . When  $f_{SYS} = 120MHz$ ,  $t_0 = 16.7ns$

Figure 4-15 MLI Interface Timing

Note: The generation of RREADY is in the input clock domain of the receiver. The reception of TREADY is asynchronous to TCLK.