Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | TriCore™                                                                          |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 150MHz                                                                            |

| Connectivity               | EBI/EMI, FIFO, I <sup>2</sup> C, IrDA, SPI, UART/USART                            |

| Peripherals                | DMA, POR, PWM, WDT                                                                |

| Number of I/O              | 72                                                                                |

| Program Memory Size        | -                                                                                 |

| Program Memory Type        | ROMIess                                                                           |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 144K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.43V ~ 1.58V                                                                     |

| Data Converters            | -                                                                                 |

| Oscillator Type            | External                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 208-LBGA                                                                          |

| Supplier Device Package    | P-LBGA-208-2                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-tc1100-l150eb-g-bb |

#### **Edition 2005-02**

Published by Infineon Technologies AG, St.-Martin-Strasse 53, 81669 München, Germany

© Infineon Technologies AG 2005.

All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as a guarantee of characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

#### **Warnings**

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

|            | Oata Sheet<br>Information<br>History: | 2005-02                            | V1.0 |

|------------|---------------------------------------|------------------------------------|------|

| Previous \ | Version:                              | none                               |      |

| Page       | Subjects (                            | major changes since last revision) |      |

|            |                                       |                                    |      |

|            |                                       |                                    |      |

Controller Area Network (CAN): License of Robert Bosch GmbH

### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

| Table of                                                                                                                                                                                                                                                                                                                                       | Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Page                                                                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                                                                                                                                                                                                                                                                                                                              | Summary of Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                                                                                                                                                                                                            |

| 2<br>2.1<br>2.2<br>2.3<br>2.4                                                                                                                                                                                                                                                                                                                  | General Device Information  Block Diagram  Logic Symbol  Pin Configuration  Pin Definitions and Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3<br>4<br>5                                                                                                                                                                                                  |

| 3<br>3.1<br>3.2<br>3.3<br>3.3.1<br>3.3.2<br>3.3.3<br>3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11<br>3.12<br>3.13<br>3.14<br>3.15<br>3.16<br>3.17<br>3.18<br>3.19<br>3.10<br>3.11<br>3.12<br>3.13<br>3.14<br>3.15<br>3.16<br>3.17<br>3.18<br>3.19<br>3.19<br>3.19<br>3.19<br>3.19<br>3.19<br>3.19<br>3.19 | Functional Description On-Chip Memories Address Map Memory Protection System Protection for Direct translation Protection for PTE based translation Memory Checker On-Chip Bus System Local Memory Bus (LMB) Flexible Peripheral Interconnect Bus (FPI) LFI LMB External Bus Unit Direct Memory Access (DMA) Interrupt System Parallel Ports Asynchronous/Synchronous Serial Interface (ASC) High-Speed Synchronous Serial Interface (SSC) Inter IC Serial Interface (IIC) Micro Link Serial Bus Interface (MLI) General Purpose Timer Unit (GPTU) Capture/Compare Unit 6 (CCU6) System Timer Watchdog Timer System Control Unit Boot Options Power Management System On-Chip Debug Support Clock Generation Unit Power Supply Power Sequencing Identification Register Values | . 16<br>. 17<br>. 24<br>. 25<br>. 25<br>. 26<br>. 26<br>. 26<br>. 27<br>. 28<br>. 30<br>. 32<br>. 34<br>. 35<br>. 40<br>. 42<br>. 44<br>. 46<br>. 50<br>. 52<br>. 53<br>. 54<br>. 55<br>. 57<br>. 60<br>. 61 |

| <b>4</b><br>4.1<br>4.1.1<br>4.1.2                                                                                                                                                                                                                                                                                                              | Electrical Parameters  General Parameters  Parameter Interpretation  Absolute Maximum Rating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 63<br>. 63                                                                                                                                                                                                 |

| Table of | Contents                                     | Page |

|----------|----------------------------------------------|------|

| 4.1.3    | Operating Condition                          | 65   |

| 4.2      | DC Parameters                                | 66   |

| 4.2.1    | Input/Output Characteristics                 | 66   |

| 4.2.2    | Oscillator Characteristics                   | 67   |

| 4.2.3    | IIC Characteristics                          | 68   |

| 4.2.4    | Power Supply Current                         | 69   |

| 4.3      | AC Parameters                                | 70   |

| 4.3.1    | Power, Pad and Reset Timing                  | 70   |

| 4.3.2    | PLL Parameters                               | 72   |

| 4.3.3    | AC Characteristics                           | 74   |

| 4.3.4    | Input Clock Timing                           | 75   |

| 4.3.5    | Port Timing                                  | 76   |

| 4.3.6    | Timing for JTAG Signals                      | 77   |

| 4.3.7    | Timing for OCDS Trace and Breakpoint Signals | 79   |

| 4.3.8    | EBU Timings                                  | 80   |

| 4.3.8.1  | SDCLKO Output Clock Timing                   |      |

| 4.3.8.2  | BFCLKO Output Clock Timing                   | 80   |

| 4.3.8.3  | Timing for SDRAM Access Signals              | 81   |

| 4.3.8.4  | Timing for Burst Flash Access Signals        |      |

| 4.3.8.5  | Timing for Demultiplexed Access Signals      | 85   |

| 4.3.8.6  | Timing for Multiplexed Access Signals        | 87   |

| 4.3.9    | Peripheral Timings                           | 89   |

| 4.3.9.1  | SSC Master Mode Timing                       | 89   |

| 4.3.9.2  | MLI Interface Timing                         | 90   |

| 5        | Package Outline                              | 91   |

### **General Device Information**

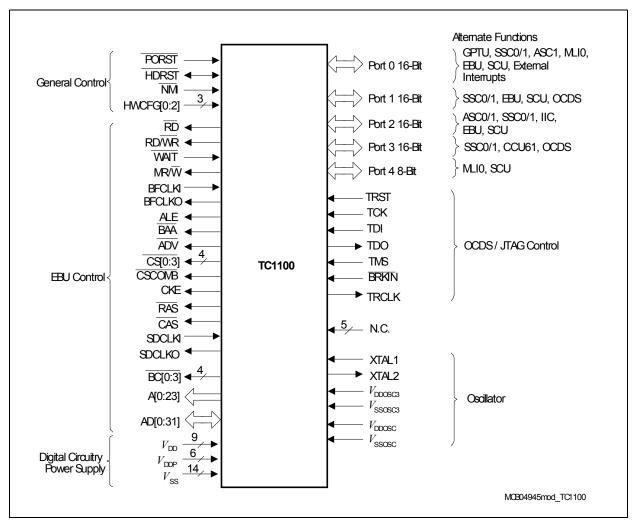

# 2.2 Logic Symbol

Figure 2-2 TC1100 Logic Symbol

# **Functional Description**

Table 3-1 TC1100 Block Address Map (cont'd)

| Seg-<br>ment | Address<br>Range                                   | Size    | Description                                                                                                                                                            | DMI<br>Acc.                                            | PMI<br>Acc.                                            |            |

|--------------|----------------------------------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|------------|

|              | D000 0000 <sub>H</sub> –<br>D000 6FFF <sub>H</sub> | 28 KB   | DMI Local Data RAM<br>(LDRAM)                                                                                                                                          | DMI<br>local                                           | via<br>LMB                                             |            |

|              | D000 7000 <sub>H</sub> –<br>D3FF FFFF <sub>H</sub> | ~ 64 MB | Reserved                                                                                                                                                               |                                                        |                                                        |            |

|              | D400 0000 <sub>H</sub> –<br>D400 7FFF <sub>H</sub> | 32 KB   | PMI Local Code Scratch Pad RAM (SPRAM)                                                                                                                                 | via<br>LMB                                             | PMI<br>local                                           |            |

| 13           | D400 8000 <sub>H</sub> –<br>D7FF FFFF <sub>H</sub> | ~64 MB  | Reserved                                                                                                                                                               |                                                        |                                                        |            |

|              | D800 0000 <sub>H</sub> –<br>DDFF FFFF <sub>H</sub> | 96 MB   | External Memory Space                                                                                                                                                  | via                                                    | via                                                    |            |

|              | DE00 0000 <sub>H</sub> –<br>DEFF FFFF <sub>H</sub> | 16 MB   | Emulator Memory Space                                                                                                                                                  | LMB                                                    | LMB                                                    |            |

|              | DF00 0000 <sub>H</sub> –<br>DFFF BFFF <sub>H</sub> | ~16 MB  | Reserved                                                                                                                                                               | _                                                      | _                                                      |            |

|              | DFFF C000 <sub>H</sub> –<br>DFFF FFFF <sub>H</sub> | 16 KB   | Boot ROM Space                                                                                                                                                         | via FPI                                                | via<br>FPI                                             | ped        |

|              | E000 0000 <sub>H</sub> –<br>E7FF FFFF <sub>H</sub> | 128 MB  | External Memory Space                                                                                                                                                  | via<br>LMB                                             | via<br>LMB                                             | non-cached |

|              | E800 0000 <sub>H</sub> –<br>E83F FFFF <sub>H</sub> | 4 MB    | Reserved for mapped space<br>for lower 4 Mbytes of Local<br>Memory in Segment 12<br>(Transformed by LFI bridge to<br>C000 0000 <sub>H</sub> – C03F FFFF <sub>H</sub> ) | access<br>only<br>from<br>FPI<br>bus<br>side of<br>LFI | access<br>only<br>from<br>FPI<br>bus<br>side of<br>LFI | lou        |

| 14           | E840 0000 <sub>H</sub> –<br>E84F FFFF <sub>H</sub> | 1 MB    | Reserved for mapped space<br>for lower 1 Mbyte of Local<br>Memory in Segment 13<br>(Transformed by LFI bridge to<br>D000 0000 <sub>H</sub> – D00F FFFF <sub>H</sub> )  | access<br>only<br>from<br>FPI<br>bus                   | access<br>only<br>from<br>FPI<br>bus                   |            |

|              | E850 0000 <sub>H</sub> –<br>E85F FFFF <sub>H</sub> | 1 MB    | Reserved for mapped space<br>for 1 Mbyte of Local Memory in<br>Segment 13<br>(Transformed by LFI bridge to<br>D400 0000 <sub>H</sub> – D40F FFFF <sub>H</sub> )        | side of<br>LFI                                         | side of<br>LFI                                         |            |

### **Functional Description**

# 3.6 Direct Memory Access (DMA)

The Direct Memory Access Controller executes DMA transactions from a source address location to a destination address location, without intervention of the CPU. One DMA transaction is controlled by one DMA channel. Each DMA channel has assigned its own channel register set. The total of 8 channels are provided by one DMA sub-block.

The DMA module is connected to 3 bus interfaces in TC1100, the Flexible Peripheral Interconnect Bus (FPI), the DMA Bus and the Micro Link Bus. It can do transfers on each of the buses as well as between the buses.

In addition, it bridges accesses from the Flexible Peripheral Interconnect Bus to the peripherals on the DMA Bus, allowing easy access to these peripherals by CPU. Clock control, address decoding, DMA request wiring, and DMA interrupt service request control are implementation specific and managed outside the DMA controller kernel.

#### Features:

- 8 independent DMA channels

- Up to 8 selectable request inputs per DMA channel

- Programmable priority of DMA channels within a DMA sub-block (2 levels)

- Software and hardware DMA request generation

- Hardware requests by selected peripherals and external inputs

- · Programmable priority of the DMA sub-block on the bus interfaces

- Buffer capability for move actions on the buses (min. 1 move per bus is buffered)

- Individually programmable operation modes for each DMA channel

- Single mode: stops and disables DMA channel after a predefined number of DMA transfers

- Continuous mode: DMA channel remains enabled after a predefined number of DMA transfers; DMA transaction can be repeated

- Programmable address modification

- Full 32-bit addressing capability of each DMA channel

- 4-Gbyte address range

- Support of circular buffer addressing mode

- Programmable data width of a DMA transaction: 8-bit, 16-bit, or 32-bit

- Micro Link supported

- Register set for each DMA channel

- Source and destination address register

- Channel control and status register

- Transfer count register

- Flexible interrupt generation (the service request node logic for the MLI channels is also implemented in the DMA module)

- All buses/interfaces connected to the DMA module must work at the same frequency.

- Read/write requests of the FPI Bus Side to the Remote Peripherals are bridged to the DMA Bus (only the DMA is master on the DMA bus)

### **Functional Description**

# 3.9 Asynchronous/Synchronous Serial Interface (ASC)

**Figure 3-5** shows a global view of the functional blocks of two Asynchronous/ Synchronous Serial interfaces (ASC0 and ASC1).

Each ASC module (ASC0/ASC1) communicates with the external world via one pair of I/O lines. The RXD line is the receive data input signal (in synchronous mode also output). TXD is the transmit output signal. Clock control, address decoding, and interrupt service request control are managed outside the ASC module kernel.

The Asynchronous/Synchronous Serial interfaces provide serial communication between the TC1100 and other microcontrollers, microprocessors or external peripherals.

Each ASC supports full-duplex asynchronous communication and half-duplex synchronous communication. In synchronous mode, data is transmitted or received synchronous to a shift clock which is generated by the ASC internally. In asynchronous mode, 8-bit or 9-bit data transfer, parity generation, and the number of stop bits can be selected. Parity, framing, and overrun error detection are provided to increase the reliability of data transfers. Transmission and reception of data is double-buffered. For multiprocessor communication, a mechanism is included to distinguish address bytes from data bytes. Testing is supported by a loop-back option. A 13-bit baud-rate generator provides the ASC with a separate serial clock signal that can be accurately adjusted by a prescaler implemented as a fractional divider.

### **Functional Description**

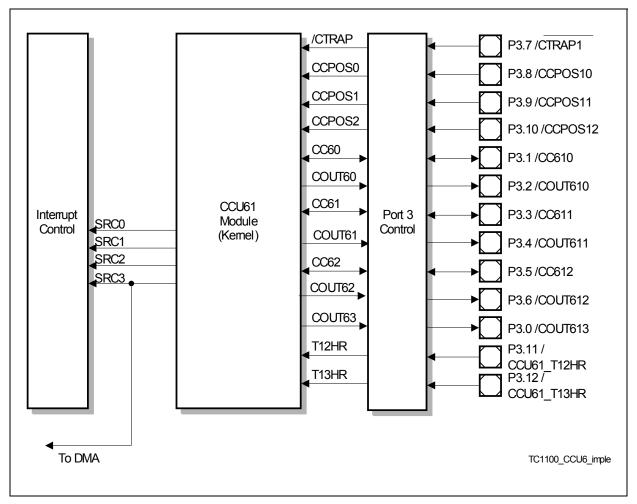

Figure 3-10 General Block Diagram of the CCU6 Interface

### **Functional Description**

# 3.16 Watchdog Timer

The Watchdog Timer (WDT) provides a highly reliable and secure way to detect and recover from software or hardware failure. The WDT helps to abort an accidental malfunction of the TC1100 in a user-specified time period. When enabled, the WDT will cause the TC1100 system to be reset if the WDT is not serviced within a user-programmable time period. The CPU must service the WDT within this time interval to prevent the WDT from causing a TC1100 system reset. Hence, routine service of the WDT confirms that the system is functioning properly.

In addition to this standard "Watchdog" function, the WDT incorporates the ENDINIT feature and monitors its modifications. A system-wide line is connected to the ENDINIT bit implemented in a WDT control register, serving as an additional write-protection for critical registers (besides supervisor mode protection). Registers protected via this line can be modified only when supervisor mode is active and bit ENDINIT = 0.

A further enhancement in the TC1100's Watchdog Timer is its reset prewarning operation. Instead of immediately resetting the device upon detection of an error, the WDT first issues a Non-Maskable Interrupt (NMI) to the CPU before finally resetting the device at a specified time period later. This gives the CPU a chance to save system state to memory for later examination of the cause of the malfunction, thus providing an important aid in debugging.

#### Features:

- 16-bit Watchdog counter

- Selectable input frequency:  $f_{SYS}/256$  or  $f_{SYS}/16384$

- 16-bit user-definable reload value for normal Watchdog operation, fixed reload value for time-out and prewarning modes

- Incorporation of the ENDINIT bit and monitoring of its modifications

- Sophisticated password access mechanism with fixed and user-definable password fields

- Proper access always requires two write accesses. The time between the two accesses is monitored by the WDT.

- Access Error Detection: Invalid password (during first access) or invalid guard bits (during second access) trigger the Watchdog reset generation

- Overflow Error Detection: An overflow of the counter triggers the Watchdog reset generation

- Watchdog function can be disabled; access protection and ENDINIT monitor function remain enabled

- Double Reset Detection: If a Watchdog induced reset occurs twice without a proper access to its control register in between, a severe system malfunction is assumed and the TC1100 is held in reset until a power-on reset. This prevents the device from being periodically reset if, for instance, connection to the external memory has been lost such that even system initialization could not be performed.

# **Functional Description**

Important debugging support is provided through the reset prewarning operation by first issuing an NMI to the CPU before finally resetting the device after a certain period of time.

Data Sheet 51 V1.0, 2005-02

### **Functional Description**

# 3.17 System Control Unit

The System Control Unit (SCU) of the TC1100 handles the system control tasks. All of these system functions are tightly coupled; thus, they are conveniently handled by one unit, the SCU. The system tasks of the SCU are:

- Clock Control

- Clock generation

- Oscillator and PLL control

- Reset and Boot Control

- Generation of all internal reset signals

- Generation of external hardware and software reset signal

- Power Management Control

- Enabling of several power management modes

- · Configuration input sampling

- · FPU interrupts

- External Request Unit

- Parity Error Control

- Fault SRAM Fuse Box

- CSCOMB Control

- · EBU Pull-Up Control

- NMI Control and Status

- DMA Request Signal Selection

#### **Electrical Parameters**

# 4.1.2 Absolute Maximum Rating

| Parameter                                                            | Symbol          | Limit | Values Unit |     | Notes      |  |

|----------------------------------------------------------------------|-----------------|-------|-------------|-----|------------|--|

|                                                                      |                 | min.  | max.        |     |            |  |

| Ambient temperature                                                  | $T_{A}$         | -40   | 85          | °C  | under bias |  |

| Storage temperature                                                  | $T_{ST}$        | -65   | 150         | °C  | _          |  |

| Junction temperature                                                 | $T_{J}$         | -40   | 125         | °C  | under bias |  |

| Voltage at 1.5 V power supply pins with respect to $V_{\rm SS}^{1)}$ | $V_{DD}$        | -0.5  | 1.7         | V   | -          |  |

| Voltage at 3.3 V power supply pins with respect to $V_{\rm SS}^{2)}$ | $V_{DDP}$       | -0.5  | 4.0         | V   | -          |  |

| Voltage on any pin with respect to $V_{\rm SS}^{(2)}$                | $V_{IN}$        | -0.5  | 4.0         | V   | _          |  |

| Input current on any pin during overload condition                   | $I_{IN}$        | -10   | 10          | mA  | _          |  |

| Absolute sum of all input currents during overload condition         | $\Sigma I_{IN}$ | _     | 100         | mA  | _          |  |

| CPU & LMB Bus Frequency                                              | $f_{\sf SYS}$   | _     | 150         | MHz | _          |  |

| FPI Bus Frequency                                                    | $f_{FPI}$       | _     | 100         | MHz | _          |  |

<sup>&</sup>lt;sup>1)</sup> Applicable for  $V_{\rm DD}$  and  $V_{\rm DDOSC}$ .

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. During absolute maximum rating overload conditions ( $V_{IN} > V_{DD}$  or  $V_{IN} < V_{SS}$ ) the voltage on  $V_{DD}$  pins with respect to ground ( $V_{SS}$ ) must not exceed the values defined by the absolute maximum ratings.

Applicable for  $V_{\rm DDP}$  and  $V_{\rm DDOSC3}$ . The maximum voltage difference must not exceed 4.0 V in any case (i.e. Supply Voltage = 4.0 V and Input Voltage = -0.5 V is not allowed).

#### **Electrical Parameters**

# 4.1.3 Operating Condition

The following operating conditions must be complied with in order to ensure correct operation of the TC1100. All parameters specified in the following table refer to these operating conditions, unless otherwise indicated.

| Parameter                                                            | Symbol              | Limit Values |       | Unit | Notes                     |  |

|----------------------------------------------------------------------|---------------------|--------------|-------|------|---------------------------|--|

|                                                                      |                     | min.         | max.  |      | Conditions                |  |

| Digital supply voltage                                               | $V_{DD}$            | 1.43         | 1.58  | V    | _                         |  |

|                                                                      | $V_{DDP}$           | 3.14         | 3.47  | V    | _                         |  |

| Digital ground voltage                                               | $V_{SS}$            |              | 0     | V    | _                         |  |

| Digital core supply current                                          | $I_{DD}$            | <u> </u>     | 525   | mA   | _                         |  |

| Ambient temperature under bias                                       | $T_{A}$             | -40          | +85   | °C   | -                         |  |

| CPU clock                                                            | $f_{\sf SYS}$       | _1)          | 150   | MHz  | _                         |  |

| Overload current                                                     | $I_{OV}$            | -1           | 1     | mA   | 2)3)                      |  |

|                                                                      |                     | -3           | 3     |      | duty cycle ≤ 25%          |  |

| Short circuit current                                                | $I_{SC}$            | -1           | 1     | mA   | 4)                        |  |

|                                                                      |                     | -3           | 3     |      | duty cycle ≤ 25%          |  |

| Absolute sum of overload +                                           | $\Sigma  I_{OV} $ + | _            | [50]  | mA   | 3)                        |  |

| short circuit currents                                               | $ I_{SC} $          |              | [100] |      | duty cycle ≤ 25%          |  |

| Inactive device pin current (V <sub>DD</sub> = V <sub>DDP</sub> = 0) | $I_{ m ID}$         | -1           | 1     | mA   | _                         |  |

| External load capacitance                                            | $C_{L}$             | _            | 50    | pF   | _                         |  |

| ESD strength                                                         | _                   | 2000         | _     | V    | Human Body<br>Model (HBM) |  |

<sup>1)</sup> The TC1100 uses a static design, so the minimum operation frequency is 0 MHz. However, due to test time restriction no lower frequency boundary is tested.

Overload conditions occur if the standard operating conditions are exceeded, i.e. the voltage on any pin exceeds the specified range (i.e.  $V_{\rm OV} > V_{\rm DDP} + 0.5 \, \text{V}$  or  $V_{\rm OV} < V_{\rm SS}$  - 0.5 V). The absolute sum of input overload currents on all digital I/O pins may not exceed **50 mA**. The supply voltage must remain within the specified limits.

<sup>3)</sup> Not subject to production test, verified by design/characterization.

<sup>4)</sup> Applicable for digital inputs.

## **Electrical Parameters**

## 4.2.2 Oscillator Characteristics

$V_{SS} = 0 \text{ V}; T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$

| Parameter                                                  | Symbol                | Limit | Values                  | Unit | <b>Test Condition</b> |

|------------------------------------------------------------|-----------------------|-------|-------------------------|------|-----------------------|

|                                                            |                       | min.  | max.                    |      |                       |

| Oscillator Pins                                            |                       |       |                         | •    |                       |

| Input low voltage at XTAL1                                 | $V_{ILX}$ SR          | -0.3  | _                       | V    | 1)                    |

| Input high voltage at XTAL1                                | $V_{IHX}$ SR          | _     | 3                       | V    | 1)                    |

| Quartz oscillation peak-peak amplitude at oscillator Input | V <sub>PPOSC</sub> SR | 0.6   | _                       | V    | 1)                    |

| Input low voltage at XTAL1                                 | $V_{ILX}$ SR          | -0.3  | 0.1                     | V    | 2)                    |

| Input high voltage at XTAL1                                | $V_{IHX}$ SR          | 1.4   | V <sub>DDC</sub> + 0.3V | V    | 2)                    |

| Oscillator input current                                   | $I_{OSCIN}$           | _     | 25                      | μΑ   |                       |

<sup>1)</sup> Quartz mode: using a quartz crystal

<sup>&</sup>lt;sup>2)</sup> Bypass mode: using an external clock

### **Electrical Parameters**

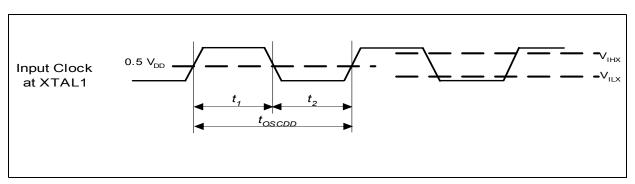

# 4.3.4 Input Clock Timing

(Operating Conditions apply)

| Parameter                                                | Symbol   | Limits           |     | Unit |     |

|----------------------------------------------------------|----------|------------------|-----|------|-----|

|                                                          |          |                  | min | max  |     |

| Oscillator clock frequency                               | with PLL | $f_{\rm OSC}$ SR | 4   | 25   | MHz |

| Input clock frequency driving at XTAL1                   | with PLL | foscod SR        | -   | 40   | MHz |

| Input Clock Duty Cycle (t <sub>1</sub> /t <sub>2</sub> ) |          | SR               | 45  | 55   | %   |

Figure 4-4 Input Clock Timing

#### **Electrical Parameters**

# 4.3.8 EBU Timings

# 4.3.8.1 SDCLKO Output Clock Timing

(Operating Conditions apply; CL = 50 pF)

| Parameter        | Symbol            | Limits <sup>1)</sup> |     | Limits <sup>2)</sup> |     | Unit |

|------------------|-------------------|----------------------|-----|----------------------|-----|------|

|                  |                   | min                  | max | min                  | max |      |

| SDCLKO period    | t <sub>1</sub> CC | 10                   | _   | 8.3                  | _   | ns   |

| SDCLKO high time | t <sub>2</sub> CC | 3                    | _   | 2.5                  | _   | ns   |

| SDCLKO low time  | t <sub>3</sub> CC | 3                    | _   | 2.5                  | _   | ns   |

| SDCLKO rise time | t <sub>4</sub> CC | _                    | 2.5 | _                    | 2.5 | ns   |

| SDCLKO fall time | t <sub>5</sub> CC | _                    | 2.5 | _                    | 2.5 | ns   |

<sup>1)</sup> The parameters are applicable for PC100 SDRAM access and the maximum SDCLKO is up to 100 MHz.

# 4.3.8.2 BFCLKO Output Clock Timing

(Operating Conditions apply;  $C_{l} = 50 \text{ pF}$ )

| Parameter        | Sy             | Symbol |     | Limit 1) |      | Limit <sup>2)</sup> |    |

|------------------|----------------|--------|-----|----------|------|---------------------|----|

|                  |                |        | min | max      | min  | max                 |    |

| Clock period     | t <sub>1</sub> | CC     | 20  | _        | 16.7 | _                   | ns |

| BFCLKO high time | $t_2$          | CC     | 6.6 | _        | 7.5  | _                   | ns |

| BFCLKO low time  | $t_3$          | CC     | 6.6 | _        | 7.5  | _                   | ns |

| BFCLKO rise time | $t_4$          | CC     | _   | 3.5      | _    | 3.5                 | ns |

| BFCLKO fall time | t <sub>5</sub> | CC     | _   | 2.5      | _    | 2.5                 | ns |

<sup>1)</sup> The CPU runs at 150 MHz and the Burst Flash runs at divided by 3 clock.

<sup>2)</sup> The parameters are applicable for PC133 SDRAM access and the maximum SDCLKO is up to 120 MHz.

<sup>2)</sup> The CPU runs at 120 MHz and the Burst Flash runs at divided by 2 clock.

### **Electrical Parameters**

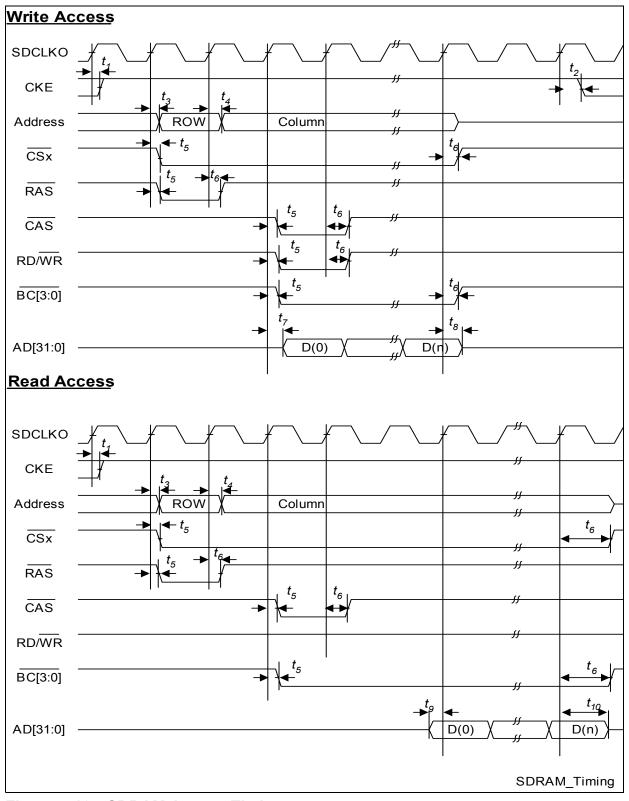

Figure 4-10 SDRAM Access Timing

#### **Electrical Parameters**

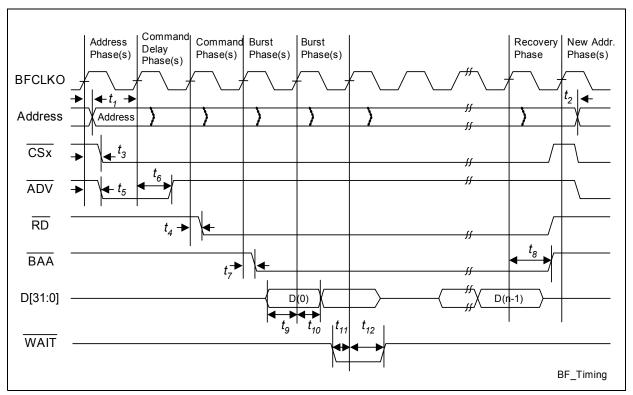

Figure 4-11 Burst Flash Access Timing

Note: Output delays are always referenced to BFCLKO. The reference clock for input characteristics depends on bit BFCON.FDBKEN.

BFCON.FDBKEN = 0: BFCLKO is the input reference clock.

BFCON.FDBKEN = 1: BFCLKI is the input reference clock (EBULMB clock feedback enabled).

### **Electrical Parameters**

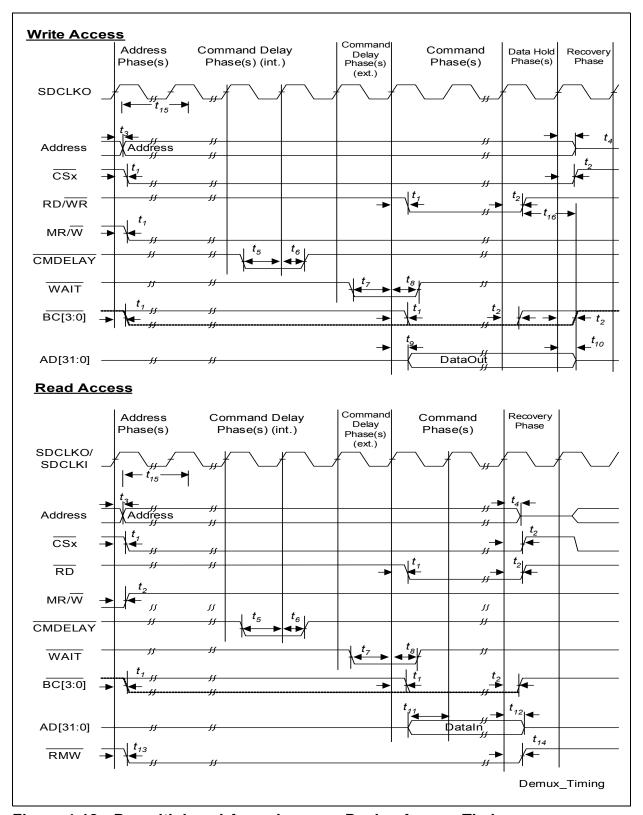

Figure 4-12 Demultiplexed Asynchronous Device Access Timing