Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB OTG                                     |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 51                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-VFQFN Exposed Pad                                                           |

| Supplier Device Package    | 64-VQFN (9x9)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128gb106-i-mr |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

Microchip's Worldwide Web site; http://www.microchip.com

Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### Customer Notification System

Register on our web site at www.microchip.com to receive the most current information on all of our products.

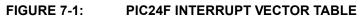

| I                                 | Reset – GOTO Instruction    | 000000h |                                                        |

|-----------------------------------|-----------------------------|---------|--------------------------------------------------------|

|                                   | Reset – GOTO Address        | 000002h |                                                        |

|                                   | Reserved                    | 000004h |                                                        |

|                                   | Oscillator Fail Trap Vector |         |                                                        |

|                                   | Address Error Trap Vector   | -       |                                                        |

|                                   | Stack Error Trap Vector     |         |                                                        |

|                                   | Math Error Trap Vector      |         |                                                        |

|                                   | Reserved                    |         |                                                        |

|                                   | Reserved                    |         |                                                        |

|                                   | Reserved                    |         |                                                        |

|                                   | Interrupt Vector 0          | 000014h | ]                                                      |

|                                   | Interrupt Vector 1          |         |                                                        |

|                                   |                             |         |                                                        |

|                                   |                             |         |                                                        |

|                                   |                             |         |                                                        |

|                                   | Interrupt Vector 52         | 00007Ch |                                                        |

| ority                             | Interrupt Vector 53         | 00007Eh | Interrupt Vector Table (IVT) <sup>(1)</sup>            |

| Dric                              | Interrupt Vector 54         | 000080h |                                                        |

| r<br>F                            |                             |         |                                                        |

| rde                               | _                           |         |                                                        |

| <u>0</u>                          |                             |         |                                                        |

| rra                               | Interrupt Vector 116        | 0000FCh |                                                        |

| lati                              | Interrupt Vector 117        | 0000FEh |                                                        |

| 2                                 | Reserved                    | 000100h |                                                        |

| sin                               | Reserved                    | 000102h |                                                        |

| ea                                | Reserved                    |         |                                                        |

| Decreasing Natural Order Priority | Oscillator Fail Trap Vector |         |                                                        |

| Ō                                 | Address Error Trap Vector   |         |                                                        |

|                                   | Stack Error Trap Vector     |         |                                                        |

|                                   | Math Error Trap Vector      |         |                                                        |

|                                   | Reserved                    |         |                                                        |

|                                   | Reserved                    |         | 7                                                      |

|                                   | Reserved                    |         |                                                        |

|                                   | Interrupt Vector 0          | 000114h |                                                        |

|                                   | Interrupt Vector 1          |         |                                                        |

|                                   |                             |         |                                                        |

|                                   |                             |         | (1)                                                    |

|                                   | _                           |         | Alternate Interrupt Vector Table (AIVT) <sup>(1)</sup> |

|                                   | Interrupt Vector 52         | 00017Ch |                                                        |

|                                   | Interrupt Vector 53         | 00017Eh |                                                        |

|                                   | Interrupt Vector 54         | 000180h |                                                        |

|                                   | —                           |         |                                                        |

|                                   | —                           | 4       |                                                        |

|                                   | —                           |         | <u> </u>                                               |

| Ļ                                 | Interrupt Vector 116        |         |                                                        |

| V                                 | Interrupt Vector 117        | 0001FEh |                                                        |

|                                   | Start of Code               | 000200h |                                                        |

#### TABLE 7-1: TRAP VECTOR DETAILS

| Vector Number | IVT Address | AIVT Address | Trap Source        |

|---------------|-------------|--------------|--------------------|

| 0             | 000004h     | 000104h      | Reserved           |

| 1             | 000006h     | 000106h      | Oscillator Failure |

| 2             | 000008h     | 000108h      | Address Error      |

| 3             | 00000Ah     | 00010Ah      | Stack Error        |

| 4             | 00000Ch     | 00010Ch      | Math Error         |

| 5             | 00000Eh     | 00010Eh      | Reserved           |

| 6             | 000010h     | 000110h      | Reserved           |

| 7             | 000012h     | 000112h      | Reserved           |

## 9.2.2 IDLE MODE

Idle mode has these features:

- The CPU will stop executing instructions.

- The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 9.4 "Selective Peripheral Module Control").

- If the WDT or FSCM is enabled, the LPRC will also remain active.

The device will wake from Idle mode on any of these events:

- Any interrupt that is individually enabled.

- · Any device Reset.

- A WDT time-out.

On wake-up from Idle, the clock is reapplied to the CPU and instruction execution begins immediately, starting with the instruction following the PWRSAV instruction or the first instruction in the ISR.

#### 9.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction will be held off until entry into Sleep or Idle mode has completed. The device will then wake-up from Sleep or Idle mode.

## 9.3 Doze Mode

Generally, changing clock speed and invoking one of the power-saving modes are the preferred strategies for reducing power consumption. There may be circumstances, however, where this is not practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed may introduce communication errors, while using a power-saving mode may stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate.

Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:256, with 1:1 being the default.

It is also possible to use Doze mode to selectively reduce power consumption in event driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU Idles, waiting for something to invoke an interrupt routine. Enabling the automatic return to full-speed CPU operation on interrupts is enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

### 9.4 Selective Peripheral Module Control

Idle and Doze modes allow users to substantially reduce power consumption by slowing or stopping the CPU clock. Even so, peripheral modules still remain clocked, and thus, consume power. There may be cases where the application needs what these modes do not provide: the allocation of power resources to CPU processing with minimal power consumption from the peripherals.

PIC24F devices address this requirement by allowing peripheral modules to be selectively disabled, reducing or eliminating their power consumption. This can be done with two control bits:

- The Peripheral Enable bit, generically named, "XXXEN", located in the module's main control SFR.

- The Peripheral Module Disable (PMD) bit, generically named, "XXXMD", located in one of the PMD Control registers.

Both bits have similar functions in enabling or disabling their associated module. Setting the PMD bit for a module disables all clock sources to that module, reducing its power consumption to an absolute minimum. In this state, the control and status registers associated with the peripheral will also be disabled, so writes to those registers will have no effect and read values will be invalid. Many peripheral modules have a corresponding PMD bit.

In contrast, disabling a module by clearing its XXXEN bit disables its functionality, but leaves its registers available to be read and written to. This reduces power consumption, but not by as much as setting the PMD bit does. Most peripheral modules have an enable bit; exceptions include input capture, output compare and RTCC.

To achieve more selective power savings, peripheral modules can also be selectively disabled when the device enters Idle mode. This is done through the control bit of the generic name format, "XXXIDL". By default, all modules that can operate during Idle mode will do so. Using the disable on Idle feature allows further reduction of power consumption during Idle mode, enhancing power savings for extremely critical power applications.

NOTES:

## 17.1 UART Baud Rate Generator (BRG)

The UART module includes a dedicated 16-bit Baud Rate Generator. The UxBRG register controls the period of a free-running, 16-bit timer. Equation 17-1 shows the formula for computation of the baud rate with BRGH = 0.

## EQUATION 17-1: UART BAUD RATE WITH BRGH = $0^{(1,2)}$

Baud Rate =  $\frac{FCY}{16 \cdot (UxBRG + 1)}$ UxBRG =  $\frac{FCY}{16 \cdot Baud Rate} - 1$

**Note 1:** FCY denotes the instruction cycle clock

- frequency (Fosc/2).

- **2:** Based on FCY = FOSC/2, Doze mode and PLL are disabled.

Example 17-1 shows the calculation of the baud rate error for the following conditions:

- Fcy = 4 MHz

- Desired Baud Rate = 9600

The maximum baud rate (BRGH = 0) possible is FCY/16 (for UxBRG = 0) and the minimum baud rate possible is FCY/(16 \* 65536).

Equation 17-2 shows the formula for computation of the baud rate with BRGH = 1.

#### EQUATION 17-2: UART BAUD RATE WITH BRGH = $1^{(1,2)}$

|      |    | Baud Rate = $\frac{FCY}{4 \cdot (UxBRG + 1)}$         |

|------|----|-------------------------------------------------------|

|      |    | $UxBRG = \frac{FCY}{4 \cdot Baud Rate} - 1$           |

| Note | 1: | Fcy denotes the instruction cycle clock<br>frequency. |

|      | э. | Deced on Fox - Foco/2 Deze made                       |

2: Based on FCY = FOSC/2, Doze mode and PLL are disabled.

The maximum baud rate (BRGH = 1) possible is FcY/4 (for UxBRG = 0) and the minimum baud rate possible is FcY/(4 \* 65536).

Writing a new value to the UxBRG register causes the BRG timer to be reset (cleared). This ensures the BRG does not wait for a timer overflow before generating the new baud rate.

## EXAMPLE 17-1: BAUD RATE ERROR CALCULATION (BRGH = 0)<sup>(1)</sup>

Desired Baud Rate = FCY/(16 (UxBRG + 1))Solving for UxBRG value: UxBRG = ((FCY/Desired Baud Rate)/16) - 1UxBRG = ((400000/9600)/16) - 1UxBRG = 2.5 Calculated Baud Rate= 4000000/(16 (25 + 1)) 9615 = Error (Calculated Baud Rate - Desired Baud Rate) = Desired Baud Rate = (9615 - 9600)/9600= 0.16%**Note 1:** Based on FCY = FOSC/2, Doze mode and PLL are disabled.

#### REGISTER 17-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 4   | RXINV: Receive Polarity Inversion bit<br>1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                             |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                               |

|         | <ul><li>1 = High-Speed mode (baud clock generated from FcY/4)</li><li>0 = Standard mode (baud clock generated from FcY/16)</li></ul>                          |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                    |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul> |

| bit 0   | STSEL: Stop Bit Selection bit                                                                                                                                 |

|         | 1 = Two Stop bits<br>0 = One Stop bit                                                                                                                         |

- **Note 1:** If UARTEN = 1, the peripheral inputs and outputs must be configured to an available RPn pin. See **Section 10.4 "Peripheral Pin Select"** for more information.

- **2:** This feature is only available for the 16x BRG mode (BRGH = 0).

## REGISTER 18-1: BDnSTAT: BUFFER DESCRIPTOR n STATUS REGISTER PROTOTYPE, USB MODE (BD0STAT THROUGH BD63STAT)

| R/W-x        | R/W-x                                                              | R/W-x                                                          | R/W-x                               | R/W-x                                                  | R/W-x            | R/W-x           | R/W-x |

|--------------|--------------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------|--------------------------------------------------------|------------------|-----------------|-------|

| UOWN         | DTS                                                                | PID3                                                           | PID2                                | PID1                                                   | PID0             | BC9             | BC8   |

| bit 15       |                                                                    |                                                                |                                     | •                                                      | •                |                 | bit 8 |

| R/W-x        | R/W-x                                                              | R/W-x                                                          | R/W-x                               | R/W-x                                                  | R/W-x            | R/W-x           | R/W-x |

| BC7          | BC6                                                                | BC5                                                            | BC4                                 | BC3                                                    | BC2              | BC1             | BC0   |

| bit 7        |                                                                    |                                                                |                                     | 1                                                      |                  |                 | bit ( |

| Legend:      |                                                                    |                                                                |                                     |                                                        |                  |                 |       |

| R = Readab   | le bit                                                             | W = Writable                                                   | bit                                 | U = Unimpler                                           | nented bit, read | d as '0'        |       |

| -n = Value a | t POR                                                              | '1' = Bit is set                                               |                                     | '0' = Bit is clea                                      |                  | x = Bit is unkr | nown  |

| bit 14       | the buffe<br><b>DTS:</b> Data To<br>1 = Data 1 pa<br>0 = Data 0 pa | oggle Packet bi<br>acket                                       | t                                   |                                                        |                  |                 |       |

| bit 13-10    | PID<3:0>: Pa<br>In Device mo<br>Represents th<br>In Host mode      | acket Identifier<br><u>de:</u><br>ne PID of the re<br><u>:</u> | eceived token o                     | the USB modu<br>during the last tr<br>nsfer status ind | ransfer.         |                 |       |

| bit 9-0      | BC<9:0>: By<br>This represer<br>during a tran                      | te Count<br>its the number                                     | of bytes to be t<br>npletion, the b | transmitted or the optic count is up                   | ne maximum n     |                 |       |

#### 18.7.2 USB INTERRUPT REGISTERS

#### REGISTER 18-14: U1OTGIR: USB OTG INTERRUPT STATUS REGISTER (HOST MODE ONLY)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     | •   |     | •   |     | bit 8 |

| bit 15 |     |     |     |     |     |     |       |

| R/K-0, HS | U-0 | R/K-0, HS |

|-----------|-----------|-----------|-----------|-----------|-----------|-----|-----------|

| IDIF      | T1MSECIF  | LSTATEIF  | ACTVIF    | SESVDIF   | SESENDIF  | _   | VBUSVDIF  |

| bit 7     |           |           |           |           |           |     | bit 0     |

| Legend:           | U = Unimplemented bit, read as '0' |                            |                    |  |  |  |

|-------------------|------------------------------------|----------------------------|--------------------|--|--|--|

| R = Readable bit  | K = Write '1' to clear bit         | HS = Hardware Settable bit |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                   | '0' = Bit is cleared       | x = Bit is unknown |  |  |  |

| bit 15-8 | Unimplemented: Read as '0'                                                                                                                         |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | IDIF: ID State Change Indicator bit                                                                                                                |

|          | 1 = Change in ID state detected                                                                                                                    |

|          | 0 = No ID state change                                                                                                                             |

| bit 6    | T1MSECIF: 1 Millisecond Timer bit                                                                                                                  |

|          | 1 = The 1 millisecond timer has expired                                                                                                            |

|          | 0 = The 1 millisecond timer has not expired                                                                                                        |

| bit 5    | LSTATEIF: Line State Stable Indicator bit                                                                                                          |

|          | 1 = USB line state (as defined by the SE0 and JSTATE bits) has been stable for 1 ms, but different from<br>last time                               |

|          | 0 = USB line state has not been stable for 1 ms                                                                                                    |

| bit 4    | ACTVIF: Bus Activity Indicator bit                                                                                                                 |

|          | 1 = Activity on the D+/D- lines or VBUS detected                                                                                                   |

|          | 0 = No activity on the D+/D- lines or VBUS detected                                                                                                |

| bit 3    | SESVDIF: Session Valid Change Indicator bit                                                                                                        |

|          | 1 = VBUS has crossed VA_SESS_END (as defined in the USB OTG Specification) <sup>(1)</sup>                                                          |

|          | 0 = VBUS has not crossed VA_SESS_END                                                                                                               |

| bit 2    | SESENDIF: B-Device VBUS Change Indicator bit                                                                                                       |

|          | <ul> <li>1 = VBUS change on B-device detected; VBUS has crossed VB_SESS_END (as defined in the USB OTG<br/>Specification)<sup>(1)</sup></li> </ul> |

|          | 0 = VBUS has not crossed VA_SESS_END                                                                                                               |

| bit 1    | Unimplemented: Read as '0'                                                                                                                         |

| bit 0    | VBUSVDIF A-Device VBUS Change Indicator bit                                                                                                        |

|          | 1 = VBUS change on A-device detected; VBUS has crossed VA_VBUS_VLD (as defined in the USB OTG<br>Specification) <sup>(1)</sup>                     |

|          | 0 = No VBUS change on A-device detected                                                                                                            |

| Note 1:  | VBUS threshold crossings may be either rising or falling.                                                                                          |

**Note:** Individual bits can only be cleared by writing a '1' to the bit position as part of a word write operation on the entire register. Using Boolean instructions or bitwise operations to write to a single bit position will cause all set bits at the moment of the write to become cleared.

#### 18.7.4 USB VBUS POWER CONTROL REGISTER

#### REGISTER 18-22: U1PWMCON: USB VBUS PWM GENERATOR CONTROL REGISTER

| R/W-0         | U-0         | U-0                | U-0             | U-0                                     | U-0              | R/W-0    | R/W-0 |

|---------------|-------------|--------------------|-----------------|-----------------------------------------|------------------|----------|-------|

| PWMEN         | _           |                    |                 |                                         | —                | PWMPOL   | CNTEN |

| bit 15        |             |                    |                 |                                         |                  |          | bit 8 |

|               |             |                    |                 |                                         |                  |          |       |

| U-0           | U-0         | U-0                | U-0             | U-0                                     | U-0              | U-0      | U-0   |

| —             | _           |                    | _               | _                                       | —                | —        | —     |

| bit 7         |             |                    |                 |                                         |                  |          | bit 0 |

|               |             |                    |                 |                                         |                  |          |       |

| Legend:       |             |                    |                 |                                         |                  |          |       |

| R = Readabl   | le bit      | W = Writable b     | it              | U = Unimplem                            | nented bit, read | d as '0' |       |

| -n = Value at | t POR       | '1' = Bit is set   |                 | '0' = Bit is cleared x = Bit is unknown |                  |          | own   |

|               |             |                    |                 |                                         |                  |          |       |

| bit 15        | PWMEN: PW   | M Enable bit       |                 |                                         |                  |          |       |

|               |             | nerator is enable  |                 |                                         |                  |          |       |

|               | 0 = PWM gei | nerator is disable | ed; output is h | neld in Reset sta                       | ate specified b  | Y PWMPOL |       |

| bit 14-10     | Unimplemen  | ted: Read as '0'   | •               |                                         |                  |          |       |

| bit 9         | PWMPOL: P   | WM Polarity bit    |                 |                                         |                  |          |       |

|               | 1 = PWM out | put is active-low  | and resets h    | igh                                     |                  |          |       |

|               |             | hout is potivo his | h and reacte    | low                                     |                  |          |       |

0 = PWM output is active-high and resets low

bit 8 CNTEN: PWM Counter Enable bit

- 1 = Counter is enabled

- 0 = Counter is disabled

- bit 7-0 Unimplemented: Read as '0'

#### REGISTER 19-6: PADCFG1: PAD CONFIGURATION CONTROL REGISTER

| U-0             | U-0                                                                  | U-0              | U-0 | U-0                                     | U-0 | U-0                     | U-0    |

|-----------------|----------------------------------------------------------------------|------------------|-----|-----------------------------------------|-----|-------------------------|--------|

|                 | —                                                                    | —                | —   | _                                       |     | —                       | _      |

| bit 15          |                                                                      |                  |     |                                         |     |                         | bit 8  |

|                 |                                                                      |                  |     |                                         |     |                         |        |

| U-0             | U-0                                                                  | U-0              | U-0 | U-0                                     | U-0 | R/W-0                   | R/W-0  |

| _               | —                                                                    | —                |     | —                                       |     | RTSECSEL <sup>(1)</sup> | PMPTTL |

| bit 7           | •                                                                    | · · · · · ·      |     |                                         |     |                         | bit 0  |

|                 |                                                                      |                  |     |                                         |     |                         |        |

| Legend:         |                                                                      |                  |     |                                         |     |                         |        |

| R = Readable    | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |     |                                         |     |                         |        |

| -n = Value at I | POR                                                                  | '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknown |     |                         | own    |

|                 |                                                                      |                  |     |                                         |     |                         |        |

bit 15-2 Unimplemented: Read as '0'

bit 1 RTSECSEL: RTCC Seconds Clock Output Select bit<sup>(1)</sup> 1 = RTCC seconds clock is selected for the RTCC pin 0 = RTCC alarm pulse is selected for the RTCC pin

bit 0 **PMPTTL:** PMP Module TTL Input Buffer Select bit

1 = PMP module inputs (PMDx, PMCS1) use TTL input buffers

0 = PMP module inputs use Schmitt Trigger input buffers

**Note 1:** To enable the actual RTCC output, the RTCOE (RCFGCAL<10>)) bit must also be set.

## REGISTER 20-1: RCFGCAL: RTCC CALIBRATION AND CONFIGURATION REGISTER<sup>(1)</sup> (CONTINUED)

bit 7-0 CAL<7:0>: RTC Drift Calibration bits

...

01111111 = Maximum positive adjustment; adds 508 RTC clock pulses every one minute

... 00000001 = Minimum positive adjustment; adds 4 RTC clock pulses every one minute 00000000 = No adjustment

111111111 = Minimum negative adjustment; subtracts 4 RTC clock pulses every one minute

10000000 = Maximum negative adjustment; subtracts 512 RTC clock pulses every one minute

- **Note 1:** The RCFGCAL register is only affected by a POR.

- **2:** A write to the RTCEN bit is only allowed when RTCWREN = 1.

- 3: This bit is read-only. It is cleared to '0' on a write to the lower half of the MINSEC register.

#### REGISTER 20-2: PADCFG1: PAD CONFIGURATION CONTROL REGISTER

| U-0                                | U-0 | U-0 | U-0                                     | U-0                                | U-0 | U-0                     | U-0    |

|------------------------------------|-----|-----|-----------------------------------------|------------------------------------|-----|-------------------------|--------|

| —                                  | _   | —   | —                                       | —                                  | —   | —                       | _      |

| bit 15                             |     |     |                                         |                                    |     |                         | bit 8  |

|                                    |     |     |                                         |                                    |     |                         |        |

| U-0                                | U-0 | U-0 | U-0                                     | U-0                                | U-0 | R/W-0                   | R/W-0  |

| —                                  | —   | —   | —                                       | —                                  | —   | RTSECSEL <sup>(1)</sup> | PMPTTL |

| bit 7                              |     | ·   |                                         |                                    |     | ·                       | bit 0  |

|                                    |     |     |                                         |                                    |     |                         |        |

| Legend:                            |     |     |                                         |                                    |     |                         |        |

| R = Readable bit W = Writable bit  |     |     | oit                                     | U = Unimplemented bit, read as '0' |     |                         |        |

| -n = Value at POR '1' = Bit is set |     |     | '0' = Bit is cleared x = Bit is unknown |                                    |     | own                     |        |

| L                                  |     |     |                                         |                                    |     |                         |        |

| Unimplemented: Read as '0'                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------|

| RTSECSEL: RTCC Seconds Clock Output Select bit <sup>(1)</sup>                                                                               |

| <ul> <li>1 = RTCC seconds clock is selected for the RTCC pin</li> <li>0 = RTCC alarm pulse is selected for the RTCC pin</li> </ul>          |

| PMPTTL: PMP Module TTL Input Buffer Select bit                                                                                              |

| <ul><li>1 = PMP module inputs (PMDx, PMCS1) use TTL input buffers</li><li>0 = PMP module inputs use Schmitt Trigger input buffers</li></ul> |

|                                                                                                                                             |

Note 1: To enable the actual RTCC output, the RTCOE (RCFGCAL<10>)) bit must also be set.

## 21.3 Registers

There are four registers used to control programmable CRC operation:

- CRCCON

- CRCXOR

- CRCDAT

- CRCWDAT

#### REGISTER 21-1: CRCCON: CRC CONTROL REGISTER

| U-0    | U-0 | R/W-0 | R-0    | R-0    | R-0    | R-0    | R-0    |

|--------|-----|-------|--------|--------|--------|--------|--------|

| —      | —   | CSIDL | VWORD4 | VWORD3 | VWORD2 | VWORD1 | VWORD0 |

| bit 15 |     |       |        |        |        |        | bit 8  |

| R-0    | R-1    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|--------|-----|-------|-------|-------|-------|-------|

| CRCFUL | CRCMPT | —   | CRCGO | PLEN3 | PLEN2 | PLEN1 | PLEN0 |

| bit 7  |        |     |       |       |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                         |

|-----------|------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | CSIDL: CRC Stop in Idle Mode bit                                                                                                   |

|           | <ul><li>1 = Discontinue module operation when device enters Idle mode</li><li>0 = Continue module operation in Idle mode</li></ul> |

| bit 12-8  | VWORD<4:0>: Pointer Value bits                                                                                                     |

|           | Indicates the number of valid words in the FIFO. Has a maximum value of 8 when PLEN<3:0> > 7, or 16 when PLEN<3:0> $\leq$ 7.       |

| bit 7     | CRCFUL: FIFO Full bit                                                                                                              |

|           | 1 = FIFO is full                                                                                                                   |

|           | 0 = FIFO is not full                                                                                                               |

| bit 6     | CRCMPT: FIFO Empty Bit                                                                                                             |

|           | 1 = FIFO is empty                                                                                                                  |

|           | 0 = FIFO is not empty                                                                                                              |

| bit 5     | Unimplemented: Read as '0'                                                                                                         |

| bit 4     | CRCGO: Start CRC bit                                                                                                               |

|           | 1 = Start CRC serial shifter                                                                                                       |

|           | 0 = CRC serial shifter turned off                                                                                                  |

| bit 3-0   | PLEN<3:0>: Polynomial Length bits                                                                                                  |

|           | Denotes the length of the polynomial to be generated minus 1.                                                                      |

|           |                                                                                                                                    |

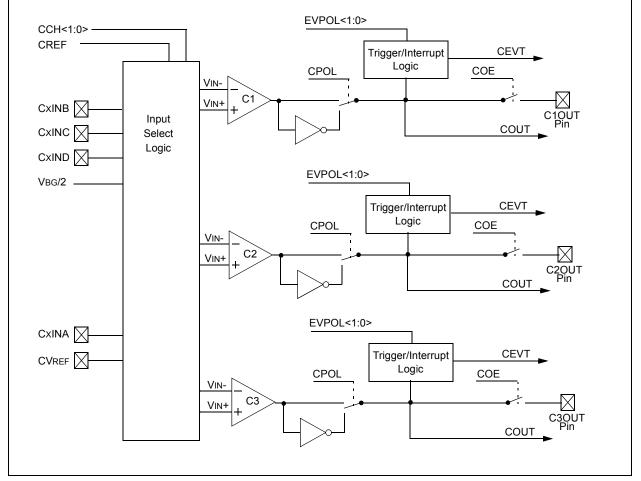

## 23.0 TRIPLE COMPARATOR MODULE

| Note: | This data sheet summarizes the features    |

|-------|--------------------------------------------|

|       | of this group of PIC24F devices. It is not |

|       | intended to be a comprehensive reference   |

|       | source. For more information, refer to the |

|       | associated "PIC24F Family Reference        |

|       | Manual" chapter.                           |

The triple comparator module provides three dual input comparators. The inputs to the comparator can be configured to use any one of four external analog inputs as well, as a voltage reference input from either the internal band gap reference divided by two (VBG/2) or the comparator voltage reference generator.

The comparator outputs may be directly connected to the CxOUT pins. When the respective COE equals '1', the I/O pad logic makes the unsynchronized output of the comparator available on the pin.

A simplified block diagram of the module in shown in Figure 23-1. Diagrams of the possible individual comparator configurations are shown in Figure 23-2.

Each comparator has its own control register, CMxCON (Register 23-1), for enabling and configuring its operation. The output and event status of all three comparators is provided in the CMSTAT register (Register 23-2).

## FIGURE 23-1: TRIPLE COMPARATOR MODULE BLOCK DIAGRAM

#### REGISTER 26-1: CW1: FLASH CONFIGURATION WORD 1 (CONTINUED)

bit 3-0 **WDTPS<3:0>:** Watchdog Timer Postscaler Select bits

1111 = 1:32,768 1110 = 1:16,384 1101 = 1:8,192 1100 = 1:4,096 1011 = 1:2,048 1010 = 1:1,024 1001 = 1:512 1000 = 1:256 0111 = 1:128 0110 = 1:64 0101 = 1:32 0100 = 1:16 0011 = 1:8 0010 = 1:4 0001 = 1:2 0000 = 1:1

**Note 1:** The JTAGEN bit can only be modified using In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>). It cannot be modified while programming the device through the JTAG interface.

#### TABLE 29-6: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

| DC CHARACTERISTICS |                             |      |       |                  |                                                                   | V to 3.6V (unless otherwise stated)<br>5 +85°C for Industrial |  |  |

|--------------------|-----------------------------|------|-------|------------------|-------------------------------------------------------------------|---------------------------------------------------------------|--|--|

| Parameter<br>No.   | Typical <sup>(1)</sup>      | Мах  | Units | Inits Conditions |                                                                   |                                                               |  |  |

| Power-Down         | Current (IPD) <sup>(;</sup> | 2)   | •     |                  |                                                                   |                                                               |  |  |

| DC60               | 0.1                         | 1    | μA    | -40°C            |                                                                   |                                                               |  |  |

| DC60a              | 0.15                        | 1    | μΑ    | +25°C            | 2.0∨ <sup>(3)</sup><br>2.5∨ <sup>(3)</sup><br>3.3∨ <sup>(4)</sup> |                                                               |  |  |

| DC60m              | 2.25                        | 11   | μA    | +60°C            |                                                                   |                                                               |  |  |

| DC60b              | 3.7                         | 18   | μΑ    | +85°C            |                                                                   |                                                               |  |  |

| DC60c              | 0.2                         | 1.4  | μΑ    | -40°C            |                                                                   | 7                                                             |  |  |

| DC60d              | 0.25                        | 1.4  | μΑ    | +25°C            |                                                                   | Base Power-Down Current <sup>(5)</sup>                        |  |  |

| DC60n              | 2.6                         | 16.5 | μΑ    | +60°C            |                                                                   | Base Power-Down Current(*)                                    |  |  |

| DC60e              | 4.2                         | 27   | μΑ    | +85°C            |                                                                   |                                                               |  |  |

| DC60f              | 3.6                         | 10   | μA    | -40°C            |                                                                   |                                                               |  |  |

| DC60g              | 4.0                         | 10   | μΑ    | +25°C            |                                                                   |                                                               |  |  |

| DC60p              | 8.1                         | 25.2 | μΑ    | +60°C            |                                                                   |                                                               |  |  |

| DC60h              | 11.0                        | 36   | μΑ    | +85°C            |                                                                   |                                                               |  |  |

| DC61               | 1.75                        | 3    | μA    | -40°C            |                                                                   |                                                               |  |  |

| DC61a              | 1.75                        | 3    | μA    | +25°C            | 2.0V <sup>(3)</sup>                                               |                                                               |  |  |

| DC61m              | 1.75                        | 3    | μA    | +60°C            | 2.000                                                             |                                                               |  |  |

| DC61b              | 1.75                        | 3    | μA    | +85°C            |                                                                   |                                                               |  |  |

| DC61c              | 2.4                         | 4    | μA    | -40°C            |                                                                   |                                                               |  |  |

| DC61d              | 2.4                         | 4    | μA    | +25°C            | 2.5V <sup>(3)</sup>                                               | Watchdog Timer Current: ∆lwDT <sup>(5)</sup>                  |  |  |

| DC61n              | 2.4                         | 4    | μA    | +60°C            | 2.50.7                                                            |                                                               |  |  |

| DC61e              | 2.4                         | 4    | μA    | +85°C            | ]                                                                 |                                                               |  |  |

| DC61f              | 2.8                         | 5    | μA    | -40°C            |                                                                   |                                                               |  |  |

| DC61g              | 2.8                         | 5    | μA    | +25°C            | 3.3∨ <sup>(4)</sup>                                               |                                                               |  |  |

| DC61p              | 2.8                         | 5    | μA    | +60°C            | 3.30                                                              |                                                               |  |  |

| DC61b              | 2.8                         | 5    | μA    | +85°C            |                                                                   |                                                               |  |  |

**Note 1:** Data in the Typical column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: Base IPD is measured with all peripherals and clocks shut down. All I/Os are configured as inputs and pulled high. WDT, etc., are all switched off, PMSLP bit is clear, and the Peripheral Module Disable (PMD) bits for all unused peripherals are set.

3: On-chip voltage regulator disabled (ENVREG tied to Vss).

4: On-chip voltage regulator enabled (ENVREG tied to VDD). Low-Voltage Detect (LVD) and Brown-out Detect (BOD) are enabled.

**5:** The  $\Delta$  current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

| DC CHARACI       | FERISTICS                   |     | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |       |                     |                                                                  |  |

|------------------|-----------------------------|-----|-------------------------------------------------------|-------|---------------------|------------------------------------------------------------------|--|

| Parameter<br>No. | Typical <sup>(1)</sup>      | Мах | Units Conditions                                      |       |                     |                                                                  |  |

| Power-Down       | Current (IPD) <sup>(2</sup> | 2)  |                                                       |       |                     |                                                                  |  |

| DC62             | 2.5                         | 7   | μΑ                                                    | -40°C |                     |                                                                  |  |

| DC62a            | 2.5                         | 7   | μA                                                    | +25°C | 2.0V <sup>(3)</sup> | RTCC + Timer1 w/32 kHz Crystal:<br>∆RTCC + ∆I⊺i32 <sup>(5)</sup> |  |

| DC62m            | 3.0                         | 7   | μA                                                    | +60°C |                     |                                                                  |  |

| DC62b            | 3.0                         | 7   | μA                                                    | +85°C |                     |                                                                  |  |

| DC62c            | 2.8                         | 7   | μA                                                    | -40°C |                     |                                                                  |  |

| DC62d            | 3.0                         | 7   | μA                                                    | +25°C | 2.5∨ <sup>(3)</sup> |                                                                  |  |

| DC62n            | 3.0                         | 7   | μA                                                    | +60°C | 2.50(1)             |                                                                  |  |

| DC62e            | 3.0                         | 7   | μA                                                    | +85°C |                     |                                                                  |  |

| DC62f            | 3.5                         | 10  | μΑ                                                    | -40°C |                     |                                                                  |  |

| DC62g            | 3.5                         | 10  | μA                                                    | +25°C | 3.3∨ <sup>(4)</sup> |                                                                  |  |

| DC62p            | 4.0                         | 10  | μA                                                    | +60°C |                     |                                                                  |  |

| DC62h            | 4.0                         | 10  | μA                                                    | +85°C |                     |                                                                  |  |

#### TABLE 29-6: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD) (CONTINUED)

**Note 1:** Data in the Typical column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: Base IPD is measured with all peripherals and clocks shut down. All I/Os are configured as inputs and pulled high. WDT, etc., are all switched off, PMSLP bit is clear, and the Peripheral Module Disable (PMD) bits for all unused peripherals are set.

3: On-chip voltage regulator disabled (ENVREG tied to Vss).

4: On-chip voltage regulator enabled (ENVREG tied to VDD). Low-Voltage Detect (LVD) and Brown-out Detect (BOD) are enabled.

5: The  $\Delta$  current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

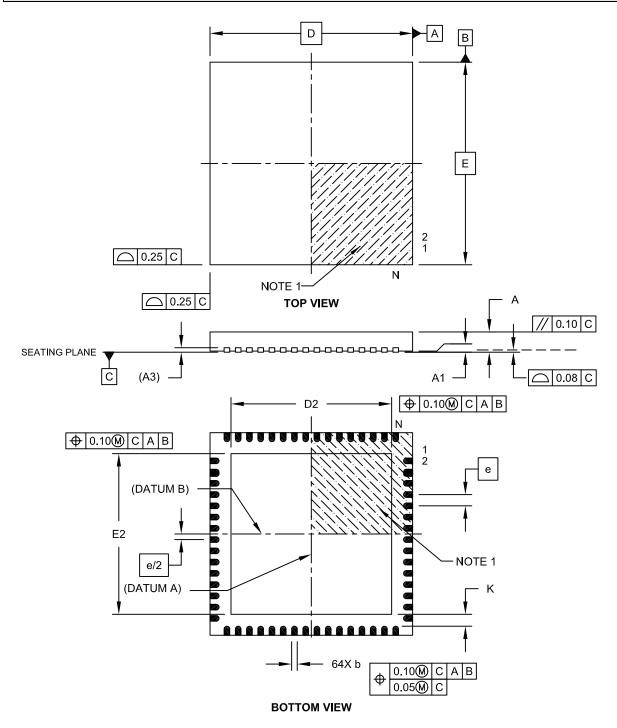

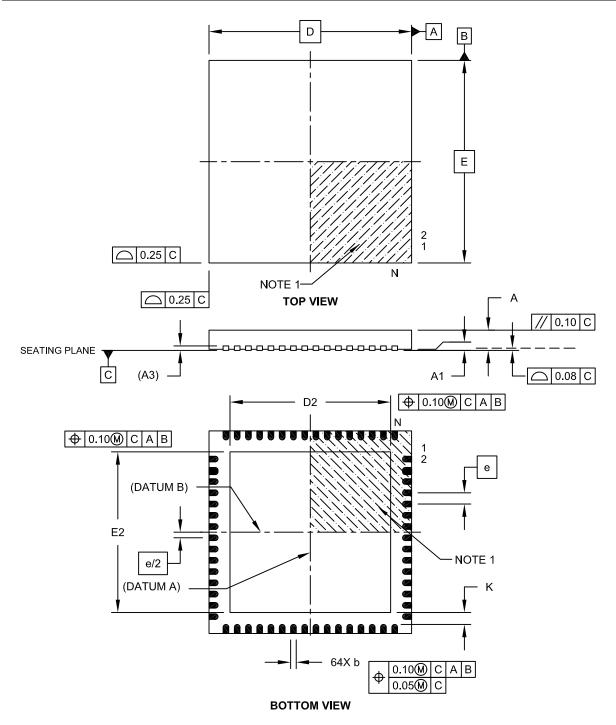

#### 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-149B Sheet 1 of 2

## 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-149B Sheet 1 of 2

NOTES:

| Peripheral Pin Select (PPS)         |

|-------------------------------------|

| Available Peripherals and Pins136   |

| Configuration Control 139           |

| Considerations for Use140           |

| Input Mapping136                    |

| Mapping Exceptions                  |

| Output Mapping                      |

| Peripheral Priority                 |

| Registers141–159                    |

| Pinout Descriptions                 |

| PMSLP Bit                           |

| and Wake-up Time                    |

| POR                                 |

| and On-Chip Voltage Regulator       |

| Power-Saving Features               |

| Clock Frequency and Clock Switching |

| Instruction-Based Modes             |

| Idle                                |

| Sleep                               |

| Power-up Requirements               |

| Product Identification System       |

| Program Memory                      |

| Access Using Table Instructions     |

| Address Construction                |

| Address Space                       |

| Flash Configuration Words           |

| Memory Maps                         |

| Organization                        |

| Program Space Visibility            |

| Program Space Visibility (PSV)      |

| Pulse-Width Modulation (PWM) Mode   |

| Pulse-Width Modulation, See PWM.    |

| PWM                                 |

| Duty Cycle and Period               |

## R

| Reader Response            |     |

|----------------------------|-----|

| Reference Clock Output     | 129 |

| Register Maps              |     |

| A/D Converter              | 53  |

| Comparators                | 56  |

| CPU Core                   |     |

| CRC                        | 56  |

| CTMU                       | 53  |

| I <sup>2</sup> C           |     |

| ICN                        |     |

| Input Capture              | 47  |

| Interrupt Controller       | 45  |

| NVM                        | 58  |

| Output Compare             |     |

| Pad Configuration          | 52  |

| Parallel Master/Slave Port | 55  |

| Peripheral Pin Select      | 57  |

| PMD                        | 58  |

| PORTA                      | 51  |

| PORTB                      | 51  |

| PORTC                      | 51  |

| PORTD                      | 51  |

| PORTE                      | 52  |

| PORTF                      | 52  |

| PORTG                      | 52  |

| RTCC                       |     |

| SPI                        | 50  |

| System                     |     |

| Timers                     |     |

| UART                       |     |

| USB OTG                    | 54  |

|                            |     |

| Registers                                                                      |                         |

|--------------------------------------------------------------------------------|-------------------------|

| AD1CHS (A/D Input Select)                                                      |                         |

| AD1CON1 (A/D Control 1)                                                        |                         |

| AD1CON2 (A/D Control 2)                                                        |                         |

| AD1CON3 (A/D Control 3)                                                        |                         |

| AD1CSSL (A/D Input Scan Select, Low)                                           |                         |

| AD1PCFGH (A/D Port Configuration, High)                                        |                         |

| AD1PCFGL (A/D Port Configuration, Low)                                         |                         |

| ALCFGRPT (Alarm Configuration)                                                 |                         |

| ALMINSEC (Alarm Minutes and Seconds Value)                                     |                         |

| ALMTHDY (Alarm Month and Day Value)                                            |                         |

| ALWDHR (Alarm Weekday and Hours Value)                                         | 259                     |

| BDnSTAT Prototype (Buffer Descriptor n                                         |                         |

| Status, CPU Mode)                                                              | 215                     |

| BDnSTAT Prototype (Buffer Descriptor n                                         |                         |

| Status, USB Mode)                                                              |                         |

| CLKDIV (Clock Divider)                                                         |                         |

| CMSTAT (Comparator Status)                                                     |                         |

| CMxCON (Comparator x Control)                                                  |                         |

| CORCON (CPU Control)                                                           |                         |

| CORCON (CPU Core Control)                                                      |                         |

| CRCCON (CRC Control)                                                           |                         |

| CRCXOR (CRC XOR Polynomial)                                                    |                         |

| CTMUCON (CTMU Control)                                                         |                         |

| CTMUICON (CTMU Current Control)                                                | 286                     |

| CVRCON (Comparator Voltage                                                     |                         |

| Reference Control)                                                             |                         |

| CW1 (Flash Configuration Word 1)                                               |                         |

| CW2 (Flash Configuration Word 2)                                               |                         |

| CW3 (Flash Configuration Word 3)                                               |                         |

| DEVID (Device ID)                                                              |                         |

| DEVREV (Device Revision)                                                       |                         |

| I2CxCON (I2Cx Control)                                                         |                         |

| I2CxMSK (I2Cx Slave Mode Address Mask)                                         |                         |

| I2CxSTAT (I2Cx Status)                                                         |                         |

| ICxCON1 (Input Capture x Control 1)                                            |                         |

| ICxCON2 (Input Capture x Control 2)                                            |                         |

| IEC0 (Interrupt Enable Control 0)                                              |                         |

| IEC1 (Interrupt Enable Control 1)                                              |                         |

| IEC2 (Interrupt Enable Control 2)                                              |                         |

| IEC3 (Interrupt Enable Control 3)                                              |                         |

| IEC4 (Interrupt Enable Control 4)                                              |                         |

| IEC5 (Interrupt Enable Control 5)                                              |                         |

| IFS0 (Interrupt Flag Status 0)<br>IFS1 (Interrupt Flag Status 1)               |                         |

| IFS1 (Interrupt Flag Status 2)                                                 |                         |

| IFS2 (Interrupt Flag Status 2)                                                 |                         |

| IFS4 (Interrupt Flag Status 4)                                                 |                         |

| IFS5 (Interrupt Flag Status 5)                                                 |                         |

| INTCON1 (Interrupt Control 1)                                                  |                         |

| INTCON2 (Interrupt Control 2)                                                  |                         |

| INTTREG (Interrupt Control and Status)                                         |                         |

| IPC0 (Interrupt Priority Control 0)                                            |                         |

| IPC1 (Interrupt Priority Control 1)                                            |                         |

| IPC10 (Interrupt Priority Control 10)                                          |                         |

| IPC10 (Interrupt Priority Control 10)                                          |                         |

| IPC12 (Interrupt Priority Control 12)                                          |                         |

| IPC13 (Interrupt Priority Control 13)                                          |                         |

| IPC15 (Interrupt Priority Control 15)                                          |                         |

| IPC16 (Interrupt Priority Control 16)                                          |                         |

| IPC18 (Interrupt Priority Control 18)                                          |                         |

| IPC19 (Interrupt Priority Control 19)                                          |                         |

| IPC2 (Interrupt Priority Control 2)                                            |                         |

|                                                                                |                         |

| IPC20 (Interrupt Priority Control 20)                                          | . 99                    |

| IPC20 (Interrupt Priority Control 20)<br>IPC21 (Interrupt Priority Control 21) | . 99<br>114             |

| IPC21 (Interrupt Priority Control 21)                                          | . 99<br>114<br>115      |

|                                                                                | 99<br>114<br>115<br>116 |