Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB OTG                                      |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                      |

| Number of I/O              | 51                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128gb106t-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.4 Voltage Regulator Pins (ENVREG/DISVREG and VCAP/VDDCORE)

| Note: | This secti | on applies   | only | to | PIC24FJ |

|-------|------------|--------------|------|----|---------|

|       |            | th an on-chi |      |    |         |

The on-chip voltage regulator enable/disable pin (ENVREG or DISVREG, depending on the device family) must always be connected directly to either a supply voltage or to ground. The particular connection is determined by whether or not the regulator is to be used:

- For ENVREG, tie to VDD to enable the regulator, or to ground to disable the regulator

- For DISVREG, tie to ground to enable the regulator or to VDD to disable the regulator

Refer to **Section 26.2** "**On-Chip Voltage Regulator**" for details on connecting and using the on-chip regulator.

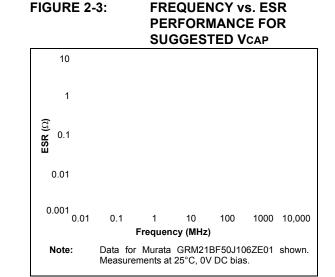

When the regulator is enabled, a low-ESR (<5 $\Omega$ ) capacitor is required on the VCAP/VDDCORE pin to stabilize the voltage regulator output voltage. The VCAP/VDDCORE pin must not be connected to VDD, and must use a capacitor of 10  $\mu$ F connected to ground. The type can be ceramic or tantalum. A suitable example is the Murata GRM21BF50J106ZE01 (10  $\mu$ F, 6.3V) or equivalent. Designers may use Figure 2-3 to evaluate ESR equivalence of candidate devices.

The placement of this capacitor should be close to VCAP/VDDCORE. It is recommended that the trace length not exceed 0.25 inch (6 mm). Refer to **Section 29.0 "Electrical Characteristics"** for additional information.

When the regulator is disabled, the VCAP/VDDCORE pin must be tied to a voltage supply at the VDDCORE level. Refer to **Section 29.0 "Electrical Characteristics"** for information on VDD and VDDCORE.

## 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming (ICSP) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of ohms, not to exceed  $100\Omega$ .

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

For device emulation, ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to the Microchip debugger/emulator tool.

For more information on available Microchip development tools connection requirements, refer to **Section 27.0 "Development Support"**.

#### TABLE 4-3: CPU CORE REGISTERS MAP

| IABLE        | 4-J. | CFUC   |                              |        | R2 MAP |        |        |        |             |              |           |            |                |              |              |       |       |               |

|--------------|------|--------|------------------------------|--------|--------|--------|--------|--------|-------------|--------------|-----------|------------|----------------|--------------|--------------|-------|-------|---------------|

| File<br>Name | Addr | Bit 15 | Bit 14                       | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8       | Bit 7        | Bit 6     | Bit 5      | Bit 4          | Bit 3        | Bit 2        | Bit 1 | Bit 0 | All<br>Resets |

| WREG0        | 0000 |        |                              |        |        |        |        |        | Working F   | Register 0   |           |            |                |              |              |       |       | 0000          |

| WREG1        | 0002 |        |                              |        |        |        |        |        | Working F   | Register 1   |           |            |                |              |              |       |       | 0000          |

| WREG2        | 0004 |        | Working Register 2           |        |        |        |        |        |             |              |           |            | 0000           |              |              |       |       |               |

| WREG3        | 0006 |        |                              |        |        |        |        |        | Working F   | Register 3   |           |            |                |              |              |       |       | 0000          |

| WREG4        | 0008 |        |                              |        |        |        |        |        | Working F   | Register 4   |           |            |                |              |              |       |       | 0000          |

| WREG5        | 000A |        |                              |        |        |        |        |        | Working F   | Register 5   |           |            |                |              |              |       |       | 0000          |

| WREG6        | 000C |        |                              |        |        |        |        |        | Working F   | Register 6   |           |            |                |              |              |       |       | 0000          |

| WREG7        | 000E |        |                              |        |        |        |        |        | Working F   | Register 7   |           |            |                |              |              |       |       | 0000          |

| WREG8        | 0010 |        |                              |        |        |        |        |        | Working F   | Register 8   |           |            |                |              |              |       |       | 0000          |

| WREG9        | 0012 |        |                              |        |        |        |        |        | Working F   | Register 9   |           |            |                |              |              |       |       | 0000          |

| WREG10       | 0014 |        |                              |        |        |        |        |        | Working R   | Register 10  |           |            |                |              |              |       |       | 0000          |

| WREG11       | 0016 |        |                              |        |        |        |        |        | Working F   | Register 11  |           |            |                |              |              |       |       | 0000          |

| WREG12       | 0018 |        |                              |        |        |        |        |        | Working R   | Register 12  |           |            |                |              |              |       |       | 0000          |

| WREG13       | 001A |        |                              |        |        |        |        |        | Working R   | Register 13  |           |            |                |              |              |       |       | 0000          |

| WREG14       | 001C |        |                              |        |        |        |        |        | Working R   | Register 14  |           |            |                |              |              |       |       | 0000          |

| WREG15       | 001E |        |                              |        |        |        |        |        | Working R   | Register 15  |           |            |                |              |              |       |       | 0800          |

| SPLIM        | 0020 |        |                              |        |        |        |        | Stack  | Pointer Lin | nit Value Re | egister   |            |                |              |              |       |       | xxxx          |

| PCL          | 002E |        |                              |        |        |        |        | Progra | m Counter I | Low Word F   | Register  |            |                |              |              |       |       | 0000          |

| PCH          | 0030 |        |                              |        | _      | —      |        | —      | —           |              |           | Progra     | m Counter      | Register Hig | gh Byte      |       |       | 0000          |

| TBLPAG       | 0032 |        |                              |        | _      | —      |        | —      | —           |              |           | Table N    | lemory Pag     | e Address I  | Register     |       |       | 0000          |

| PSVPAG       | 0034 | _      | _                            | _      | _      | _      | _      | _      | _           |              | P         | rogram Spa | ace Visibility | / Page Add   | ress Registe | er    |       | 0000          |

| RCOUNT       | 0036 |        | Repeat Loop Counter Register |        |        |        |        |        |             |              |           | xxxx       |                |              |              |       |       |               |

| SR           | 0042 | -      | _                            | _      | —      |        | _      | _      | DC          | IPL2         | IPL1      | IPL0       | RA             | Ν            | OV           | Z     | С     | 0000          |

| CORCON       | 0044 | _      | IPL3 PSV 000                 |        |        |        |        |        |             |              |           | 0000       |                |              |              |       |       |               |

| DISICNT      | 0052 | _      | -                            |        |        |        |        |        | Disabl      | e Interrupts | Counter R | egister    |                |              |              |       |       | xxxx          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-7: INPUT CAPTURE REGISTER MAP 1

| 0          |

|------------|

| 2009       |

| Microchip  |

| Technology |

| Inc.       |

| File<br>Name | Addr | Bit 15 | Bit 14                                | Bit 13 | Bit 12  | Bit 11  | Bit 10  | Bit 9 | Bit 8      | Bit 7        | Bit 6       | Bit 5 | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|--------------|------|--------|---------------------------------------|--------|---------|---------|---------|-------|------------|--------------|-------------|-------|----------|----------|----------|----------|----------|---------------|

| IC1CON1      | 0140 |        | —                                     | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | —     | —          | —            | ICI1        | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC1CON2      | 0142 | _      | _                                     | _      |         | _       | _       | _     | IC32       | ICTRIG       | TRIGSTAT    | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC1BUF       | 0144 |        |                                       |        |         |         |         |       | Input Cap  | ture 1 Buffe | er Register |       | •        |          |          | •        | •        | 0000          |

| IC1TMR       | 0146 |        |                                       |        |         |         |         |       | Timer      | Value 1 Re   | egister     |       |          |          |          |          |          | xxxx          |

| IC2CON1      | 0148 | _      | —                                     | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | _     | _          | _            | ICI1        | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC2CON2      | 014A | _      | _                                     | _      | —       | _       | _       | _     | IC32       | ICTRIG       | TRIGSTAT    | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC2BUF       | 014C |        |                                       |        |         |         |         |       | Input Cap  | ture 2 Buffe | er Register |       |          |          |          |          |          | 0000          |

| IC2TMR       | 014E |        | , , , , , , , , , , , , , , , , , , , |        |         |         |         |       |            |              |             |       |          | xxxx     |          |          |          |               |

| IC3CON1      | 0150 | _      | —                                     | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | _     | _          | _            | ICI1        | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC3CON2      | 0152 | _      | _                                     | _      |         | _       | _       | _     | IC32       | ICTRIG       | TRIGSTAT    | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC3BUF       | 0154 |        |                                       |        |         |         |         |       | Input Capt | ture 3 Buffe | er Register |       |          |          |          |          |          | 0000          |

| IC3TMR       | 0156 |        |                                       |        |         |         |         |       | Timer      | Value 3 Re   | egister     |       |          |          |          |          |          | xxxx          |

| IC4CON1      | 0158 | _      | _                                     | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | _     | _          | _            | ICI1        | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC4CON2      | 015A | -      | —                                     | _      | _       | _       | —       | _     | IC32       | ICTRIG       | TRIGSTAT    | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC4BUF       | 015C |        |                                       |        |         |         |         |       | Input Cap  | ture 4 Buffe | er Register |       |          |          |          |          |          | 0000          |

| IC4TMR       | 015E |        |                                       |        |         |         |         |       | Timer      | Value 4 Re   | egister     |       |          |          |          |          |          | xxxx          |

| IC5CON1      | 0160 | _      | —                                     | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | _     | _          | —            | ICI1        | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC5CON2      | 0162 |        | _                                     | _      | _       | _       | —       | _     | IC32       | ICTRIG       | TRIGSTAT    | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC5BUF       | 0164 |        |                                       |        |         |         |         |       | Input Cap  | ture 5 Buffe | er Register |       |          |          |          |          |          | 0000          |

| IC5TMR       | 0166 |        |                                       |        |         |         |         |       | Timer      | Value 5 Re   | egister     |       |          |          |          |          |          | xxxx          |

| IC6CON1      | 0168 | _      |                                       | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | —     | —          |              | ICI1        | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC6CON2      | 016A | _      |                                       |        | _       | —       | _       | —     | IC32       | ICTRIG       | TRIGSTAT    | —     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC6BUF       | 016C |        |                                       |        |         |         |         |       | Input Capt | ture 6 Buffe | er Register |       |          |          |          |          |          | 0000          |

| IC6TMR       | 016E |        |                                       |        |         |         |         |       | Timer      | Value 6 Re   | egister     |       |          |          |          |          |          | xxxx          |

| IC7CON1      | 0170 | _      |                                       | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | _     | _          | -            | ICI1        | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC7CON2      | 0172 | —      | _                                     | _      |         | —       | —       | —     | IC32       | ICTRIG       | TRIGSTAT    | —     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC7BUF       | 0174 |        |                                       |        |         |         |         |       | Input Capt | ture 7 Buffe | er Register |       |          |          |          |          |          | 0000          |

| IC7TMR       | 0176 |        |                                       |        |         |         |         |       | Timer      | Value 7 Re   | egister     |       |          |          |          |          |          | xxxx          |

| IC8CON1      | 0178 | —      | _                                     | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | —     | —          | _            | ICI1        | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC8CON2      | 017A | —      | —                                     | —      | _       | —       | —       | _     | IC32       | ICTRIG       | TRIGSTAT    | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC8BUF       | 017C |        |                                       |        |         |         |         |       | Input Cap  | ture 8 Buffe | er Register |       |          |          |          |          |          | 0000          |

| IC8TMR       | 017E |        |                                       |        |         |         |         |       | Timer      | Value 8 Re   | egister     |       |          |          |          |          |          | xxxx          |

| IC9CON1      | 0180 | _      | _                                     | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | —     | —          | _            | ICI1        | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC9CON2      | 0182 | _      | _                                     | _      |         | _       | _       |       | IC32       | ICTRIG       | TRIGSTAT    | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC9BUF       | 0184 |        |                                       |        |         |         |         |       | Input Cap  | ture 9 Buffe | er Register |       |          |          |          |          |          | 0000          |

| IC9TMR       | 0186 |        |                                       |        |         |         |         |       | Timer      | Value 9 Re   | egister     |       |          |          |          |          |          | xxxx          |

DS39897C-page 47

## 5.2 RTSP Operation

The PIC24F Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user to erase blocks of eight rows (512 instructions) at a time and to program one row at a time. It is also possible to program single words.

The 8-row erase blocks and single row write blocks are edge-aligned, from the beginning of program memory, on boundaries of 1536 bytes and 192 bytes, respectively.

When data is written to program memory using TBLWT instructions, the data is not written directly to memory. Instead, data written using table writes is stored in holding latches until the programming sequence is executed.

Any number of TBLWT instructions can be executed and a write will be successfully performed. However, 64 TBLWT instructions are required to write the full row of memory.

To ensure that no data is corrupted during a write, any unused addresses should be programmed with FFFFFFh. This is because the holding latches reset to an unknown state, so if the addresses are left in the Reset state, they may overwrite the locations on rows which were not rewritten.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register.

Data can be loaded in any order and the holding registers can be written to multiple times before performing a write operation. Subsequent writes, however, will wipe out any previous writes.

**Note:** Writing to a location multiple times without erasing is *not* recommended.

All of the table write operations are single-word writes (2 instruction cycles), because only the buffers are written. A programming cycle is required for programming each row.

### 5.3 JTAG Operation

The PIC24F family supports JTAG boundary scan. Boundary scan can improve the manufacturing process by verifying pin-to-PCB connectivity.

### 5.4 Enhanced In-Circuit Serial Programming

Enhanced In-Circuit Serial Programming uses an on-board bootloader, known as the program executive, to manage the programming process. Using an SPI data frame format, the program executive can erase, program and verify program memory. For more information on Enhanced ICSP, see the device programming specification.

#### 5.5 Control Registers

There are two SFRs used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls which blocks are to be erased, which memory type is to be programmed and when the programming cycle starts.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user must consecutively write 55h and AAh to the NVMKEY register. Refer to **Section 5.6 "Programming Operations"** for further details.

### 5.6 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. During a programming or erase operation, the processor stalls (waits) until the operation is finished. Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

#### REGISTER 7-1: SR: ALU STATUS REGISTER (IN CPU)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R-0               |

|--------|-----|-----|-----|-----|-----|-----|-------------------|

|        | —   | —   | —   | _   | —   | —   | DC <sup>(1)</sup> |

| bit 15 |     |     |     |     |     |     | bit 8             |

| R/W-0                 | R/W-0                 | R/W-0                 | R-0               | R/W-0            | R/W-0             | R/W-0            | R/W-0            |

|-----------------------|-----------------------|-----------------------|-------------------|------------------|-------------------|------------------|------------------|

| IPL2 <sup>(2,3)</sup> | IPL1 <sup>(2,3)</sup> | IPL0 <sup>(2,3)</sup> | RA <sup>(1)</sup> | N <sup>(1)</sup> | 0V <sup>(1)</sup> | Z <sup>(1)</sup> | C <sup>(1)</sup> |

| bit 7                 |                       |                       |                   |                  |                   |                  | bit 0            |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup>     |

|---------|-------------------------------------------------------------------------|

|         | 111 = CPU interrupt priority level is 7 (15). User interrupts disabled. |

|         | 110 = CPU interrupt priority level is 6 (14)                            |

|         | 101 = CPU interrupt priority level is 5 (13)                            |

|         | 100 = CPU interrupt priority level is 4 (12)                            |

|         | 011 = CPU interrupt priority level is 3 (11)                            |

|         | 010 = CPU interrupt priority level is 2 (10)                            |

|         | 001 = CPU interrupt priority level is 1 (9)                             |

|         | 000 = CPU interrupt priority level is 0 (8)                             |

- **Note 1:** See Register 3-1 for the description of the remaining bit(s) that are not dedicated to interrupt control functions.

- **2:** The IPL bits are concatenated with the IPL3 bit (CORCON<3>) to form the CPU interrupt priority level. The value in parentheses indicates the interrupt priority level if IPL3 = 1.

- 3: The IPL Status bits are read-only when NSTDIS (INTCON1<15>) = 1.

#### REGISTER 7-2: CORCON: CPU CONTROL REGISTER

| U-0             | U-0 | U-0              | U-0 | U-0                                     | U-0                | U-0    | U-0   |  |

|-----------------|-----|------------------|-----|-----------------------------------------|--------------------|--------|-------|--|

| —               | —   | —                | —   | —                                       | —                  | —      | —     |  |

| bit 15          |     |                  |     |                                         |                    |        | bit 8 |  |

|                 |     |                  |     |                                         |                    |        |       |  |

| U-0             | U-0 | U-0              | U-0 | R/C-0                                   | R/W-0              | U-0    | U-0   |  |

| —               | _   | —                |     | IPL3 <sup>(2)</sup>                     | PSV <sup>(1)</sup> | —      | —     |  |

| bit 7           |     |                  |     |                                         |                    |        | bit 0 |  |

|                 |     |                  |     |                                         |                    |        |       |  |

| Legend:         |     | C = Clearable    | bit |                                         |                    |        |       |  |

| R = Readable b  | oit | W = Writable I   | bit | U = Unimpler                            | nented bit, read   | as '0' |       |  |

| -n = Value at P | OR  | '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknowr |                    |        |       |  |

|                 |     |                  |     |                                         |                    |        |       |  |

bit 3 IPL3: CPU Interrupt Priority Level Status bit<sup>(2)</sup> 1 = CPU interrupt priority level is greater than 7 0 = CPU interrupt priority level is 7 or less

- **Note 1:** See Register 3-2 for the description of the remaining bit(s) that are not dedicated to interrupt control functions.

- 2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU interrupt priority level.

| U-0                | R/W-1                                                                 | R/W-0                                                                                                                    | R/W-0                       | U-0               | R/W-1            | R/W-0           | R/W-0  |

|--------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------------|------------------|-----------------|--------|

| _                  | T2IP2                                                                 | T2IP1                                                                                                                    | T2IP0                       | _                 | OC2IP2           | OC2IP1          | OC2IP0 |

| bit 15             |                                                                       |                                                                                                                          |                             |                   |                  |                 | bit    |

| U-0                | R/W-1                                                                 | R/W-0                                                                                                                    | R/W-0                       | U-0               | U-0              | U-0             | U-0    |

| _                  | IC2IP2                                                                | IC2IP1                                                                                                                   | IC2IP0                      | —                 | _                | _               | _      |

| bit 7              |                                                                       |                                                                                                                          |                             |                   |                  |                 | bit    |

| Legend:            |                                                                       |                                                                                                                          |                             |                   |                  |                 |        |

| R = Readab         | le bit                                                                | W = Writable                                                                                                             | bit                         | U = Unimplei      | mented bit, read | l as '0'        |        |

| -n = Value a       | t POR                                                                 | '1' = Bit is set                                                                                                         |                             | '0' = Bit is cle  | ared             | x = Bit is unkr | nown   |

| bit 11<br>bit 10-8 | •<br>•<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>OC2IP<2:0>: | pt is priority 7 (I<br>pt is priority 1<br>pt source is dis<br>ated: Read as '(<br>c Output Compa<br>pt is priority 7 (I | abled<br>)'<br>re Channel 2 | Interrupt Priorit | ty bits          |                 |        |

| bit 7<br>bit 6-4   | Unimplemen<br>IC2IP<2:0>:                                             | pt source is dis<br>ited: Read as '(<br>Input Capture C<br>pt is priority 7 (I                                           | )'<br>Shannel 2 Inte        |                   | S                |                 |        |

| bit 3-0            | 000 = Interru                                                         | pt is priority i<br>pt source is dis<br>ited: Read as '(                                                                 |                             |                   |                  |                 |        |

#### REGISTER 7-18: IPC1: INTERRUPT PRIORITY CONTROL REGISTER 1

### REGISTER 7-29: IPC12: INTERRUPT PRIORITY CONTROL REGISTER 12

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-1   | R/W-0   | R/W-0   |

|--------|-----|-----|-----|-----|---------|---------|---------|

| —      | _   |     |     | —   | MI2C2P2 | MI2C2P1 | MI2C2P0 |

| bit 15 |     |     |     |     |         |         | bit 8   |

|        |     |     |     |     |         |         |         |

| U-0   | R/W-1       | R/W-0   | R/W-0   | U-0 | U-0 | U-0 | U-0 |  |  |  |

|-------|-------------|---------|---------|-----|-----|-----|-----|--|--|--|

| —     | SI2C2P2     | SI2C2P1 | SI2C2P0 | —   |     |     | _   |  |  |  |

| bit 7 | bit 7 bit 0 |         |         |     |     |     |     |  |  |  |

| Legend:          |                                                                          |                                                                 |                       |                    |  |  |  |  |

|------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------|--------------------|--|--|--|--|

| R = Readable bit |                                                                          | W = Writable bit                                                | U = Unimplemented bit | , read as '0'      |  |  |  |  |

| -n = Value a     | at POR                                                                   | '1' = Bit is set                                                | '0' = Bit is cleared  | x = Bit is unknown |  |  |  |  |

| bit 15-11        | Unimpler                                                                 | nented: Read as '0'                                             |                       |                    |  |  |  |  |

| bit 10-8         | •                                                                        |                                                                 |                       |                    |  |  |  |  |

|                  | •<br>001 = Interrupt is priority 1<br>000 = Interrupt source is disabled |                                                                 |                       |                    |  |  |  |  |

| bit 7            | Unimpler                                                                 | nented: Read as '0'                                             |                       |                    |  |  |  |  |

| bit 6-4          |                                                                          | 2:0>: Slave I2C2 Event Inter<br>errupt is priority 7 (highest p | 1 2                   |                    |  |  |  |  |

- 111 = Interrupt is priority 7 (highest priority interrup

- 001 = Interrupt is priority 1 000 = Interrupt source is disabled

- bit 3-0 Unimplemented: Read as '0'

### 10.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORT, LAT and TRIS registers for data control, each port pin can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V) on any desired digital only pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

### 10.2 Configuring Analog Port Pins

The AD1PCFGL and TRIS registers control the operation of the A/D port pins. Setting a port pin as an analog input also requires that the corresponding TRIS bit be set. If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

When reading the PORT register, all pins configured as analog input channels will read as cleared (a low level).

Pins configured as digital inputs will not convert an analog input. Analog levels on any pin that is defined as a digital input (including the ANx pins) may cause the input buffer to consume current that exceeds the device specifications.

#### 10.2.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP.

# 10.2.2 ANALOG INPUT PINS AND VOLTAGE CONSIDERATIONS

The voltage tolerance of pins used as device inputs is dependent on the pin's input function. Pins that are used as digital only inputs are able to handle DC voltages up to 5.5V, a level typical for digital logic circuits. In contrast, pins that also have analog input functions of any kind can only tolerate voltages up to VDD. Voltage excursions beyond VDD on these pins are always to be avoided. Table 10-1 summarizes the input capabilities. Refer to **Section 29.1 "DC Characteristics"** for more details.

**Note:** For easy identification, the pin diagrams at the beginning of the data sheet also indicate 5.5V tolerant pins with dark grey shading.

#### TABLE 10-1: INPUT VOLTAGE LEVELS<sup>(1)</sup>

| Port or Pin                              | Tolerated<br>Input | Description                     |

|------------------------------------------|--------------------|---------------------------------|

| PORTA<10:9>                              | Vdd                | Only VDD input                  |

| PORTB<15:0>                              |                    | levels tolerated.               |

| PORTC<15:12>                             |                    |                                 |

| PORTD<7:6>                               |                    |                                 |

| PORTF<0>                                 |                    |                                 |

| PORTG<9:6>,<br>PORTG<3:2>                |                    |                                 |

| PORTA<15:14>,<br>PORTA<7:0>              | 5.5V               | Tolerates input<br>levels above |

| PORTC<4:1>                               |                    | VDD, useful for                 |

| PORTD<15:8>,<br>PORTD<5:0>               |                    | most standard<br>logic.         |

| PORTE<9:0>                               |                    |                                 |

| PORTF<13:12>,<br>PORTF<8>,<br>PORTF<5:1> |                    |                                 |

| PORTG<15:12>,<br>PORTG<1:0>              |                    |                                 |

Note 1: Not all port pins shown here are implemented on 64-pin and 80-pin devices. Refer to Section 1.0 "Device Overview" to confirm which ports are available in specific devices.

#### EXAMPLE 10-1: PORT WRITE/READ EXAMPLE

MOV 0xFF00, W0 MOV W0, TRISBB NOP BTSS PORTB, #13 ; Configure PORTB<15:8> as inputs

; and PORTB<7:0> as outputs

- ; Delay 1 cycle

- ; Next Instruction

For 32-bit cascaded operation, these steps are also necessary:

- Set the OC32 bits for both registers (OCyCON2<8> and (OCxCON2<8>). Enable the even numbered module first to ensure the modules will start functioning in unison.

- Clear the OCTRIG bit of the even module (OCyCON2), so the module will run in Synchronous mode.

- 3. Configure the desired output and Fault settings for OCy.

- 4. Force the output pin for OCx to the output state by clearing the OCTRIS bit.

- If Trigger mode operation is required, configure the trigger options in OCx by using the OCTRIG (OCxCON2<7>), TRIGSTAT (OCxCON2<6>), and SYNCSEL (OCxCON2<4:0>) bits.

- Configure the desired compare or PWM mode of operation (OCM<2:0>) for OCy first, then for OCx.

Depending on the output mode selected, the module holds the OCx pin in its default state, and forces a transition to the opposite state when OCxR matches the timer. In Double Compare modes, OCx is forced back to its default state when a match with OCxRS occurs. The OCxIF interrupt flag is set after an OCxR match in Single Compare modes, and after each OCxRS match in Double Compare modes.

Single-shot pulse events only occur once, but may be repeated by simply rewriting the value of the OCxCON1 register. Continuous pulse events continue indefinitely until terminated.

#### 14.3 Pulse-Width Modulation (PWM) Mode

In PWM mode, the output compare module can be configured for edge-aligned or center-aligned pulse waveform generation. All PWM operations are double-buffered (buffer registers are internal to the module and are not mapped into SFR space).

To configure the output compare module for PWM operation:

- 1. Configure the OCx output for one of the available Peripheral Pin Select pins.

- 2. Calculate the desired duty cycles and load them into the OCxR register.

- 3. Calculate the desired period and load it into the OCxRS register.

- Select the current OCx as the sync source by writing 0x1F to SYNCSEL<4:0> (OCxCON2<4:0>), and clearing OCTRIG (OCxCON2<7>).

- 5. Select a clock source by writing the OCTSEL<2:0> (OCxCON<12:10>) bits.

- 6. Enable interrupts, if required, for the timer and output compare modules. The output compare interrupt is required for PWM Fault pin utilization.

- 7. Select the desired PWM mode in the OCM<2:0> (OCxCON1<2:0>) bits.

- If a timer is selected as a clock source, set the TMRy prescale value and enable the time base by setting the TON (TxCON<15>) bit.

- Note: This peripheral contains input and output functions that may need to be configured by the Peripheral Pin Select. See Section 10.4 "Peripheral Pin Select" for more information.

#### REGISTER 15-1: SPIx STATUS AND CONTROL REGISTER (CONTINUED)

- bit 1 SPITBF: SPIx Transmit Buffer Full Status bit 1 = Transmit not yet started, SPIxTXB is full 0 = Transmit started, SPIxTXB is empty In Standard Buffer mode: Automatically set in hardware when CPU writes SPIxBUF location, loading SPIxTXB. Automatically cleared in hardware when SPIx module transfers data from SPIxTXB to SPIxSR. In Enhanced Buffer mode: Automatically set in hardware when CPU writes SPIxBUF location, loading the last available buffer location. Automatically cleared in hardware when a buffer location is available for a CPU write. bit 0 SPIRBF: SPIx Receive Buffer Full Status bit 1 = Receive complete, SPIxRXB is full 0 = Receive is not complete, SPIxRXB is empty In Standard Buffer mode: Automatically set in hardware when SPIx transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when core reads SPIxBUF location, reading SPIxRXB. In Enhanced Buffer mode: Automatically set in hardware when SPIx transfers data from SPIxSR to buffer, filling the last unread buffer location. Automatically cleared in hardware when a buffer location is available for a transfer from SPIxSR.

- **Note 1:** If SPIEN = 1, these functions must be assigned to available RPn pins before use. See **Section 10.4** "**Peripheral Pin Select**" for more information.

# REGISTER 18-1: BDnSTAT: BUFFER DESCRIPTOR n STATUS REGISTER PROTOTYPE, USB MODE (BD0STAT THROUGH BD63STAT)

| R/W-x        | R/W-x                                                                                                                                                                                                                                                                                                                     | R/W-x                      | R/W-x                               | R/W-x                                | R/W-x            | R/W-x              | R/W-x |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------------------------|--------------------------------------|------------------|--------------------|-------|--|

| UOWN         | DTS                                                                                                                                                                                                                                                                                                                       | PID3                       | PID2                                | PID1                                 | PID0             | BC9                | BC8   |  |

| bit 15       |                                                                                                                                                                                                                                                                                                                           | •                          |                                     | •                                    | •                |                    | bit 8 |  |

| R/W-x        | R/W-x                                                                                                                                                                                                                                                                                                                     | R/W-x                      | R/W-x                               | R/W-x                                | R/W-x            | R/W-x              | R/W-x |  |

| BC7          | BC6                                                                                                                                                                                                                                                                                                                       | BC5                        | BC4                                 | BC3                                  | BC2              | BC1                | BC0   |  |

| bit 7        |                                                                                                                                                                                                                                                                                                                           |                            |                                     | 1                                    |                  |                    | bit ( |  |

| Legend:      |                                                                                                                                                                                                                                                                                                                           |                            |                                     |                                      |                  |                    |       |  |

| R = Readab   | le bit                                                                                                                                                                                                                                                                                                                    | W = Writable               | bit                                 | U = Unimpler                         | nented bit, read | d as '0'           |       |  |

| -n = Value a | t POR                                                                                                                                                                                                                                                                                                                     | '1' = Bit is set           |                                     | '0' = Bit is cleared                 |                  | x = Bit is unknown |       |  |

| bit 14       | 1 = Data 1 p                                                                                                                                                                                                                                                                                                              | oggle Packet bi<br>acket   | t                                   |                                      |                  |                    |       |  |

| bit 13-10    | <ul> <li>0 = Data 0 packet</li> <li>PID&lt;3:0&gt;: Packet Identifier bits (written by the USB module)</li> <li>In Device mode:</li> <li>Represents the PID of the received token during the last transfer.</li> <li>In Host mode:</li> <li>Represents the last returned PID or the transfer status indicator.</li> </ul> |                            |                                     |                                      |                  |                    |       |  |

| bit 9-0      | BC<9:0>: By<br>This represer<br>during a tran                                                                                                                                                                                                                                                                             | te Count<br>its the number | of bytes to be t<br>npletion, the b | transmitted or the optic count is up | ne maximum n     |                    |       |  |

#### 18.7.2 USB INTERRUPT REGISTERS

#### REGISTER 18-14: U1OTGIR: USB OTG INTERRUPT STATUS REGISTER (HOST MODE ONLY)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _ /    | —   | —   | —   | _   | —   | _   | _     |

| bit 15 | -   | •   |     |     | •   |     | bit 8 |

| DIL 15 |     |     |     |     |     |     | Ľ     |

| R/K-0, HS | U-0 | R/K-0, HS |

|-----------|-----------|-----------|-----------|-----------|-----------|-----|-----------|

| IDIF      | T1MSECIF  | LSTATEIF  | ACTVIF    | SESVDIF   | SESENDIF  | _   | VBUSVDIF  |

| bit 7     |           |           |           |           |           |     | bit 0     |

| Legend:           | U = Unimplemented bit, read as '0' |                            |                    |  |  |  |

|-------------------|------------------------------------|----------------------------|--------------------|--|--|--|

| R = Readable bit  | K = Write '1' to clear bit         | HS = Hardware Settable bit |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                   | '0' = Bit is cleared       | x = Bit is unknown |  |  |  |

| bit 15-8 | Unimplemented: Read as '0'                                                                                                     |

|----------|--------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | IDIF: ID State Change Indicator bit                                                                                            |

|          | 1 = Change in ID state detected                                                                                                |

|          | 0 = No ID state change                                                                                                         |

| bit 6    | T1MSECIF: 1 Millisecond Timer bit                                                                                              |

|          | 1 = The 1 millisecond timer has expired                                                                                        |

|          | 0 = The 1 millisecond timer has not expired                                                                                    |

| bit 5    | LSTATEIF: Line State Stable Indicator bit                                                                                      |

|          | 1 = USB line state (as defined by the SE0 and JSTATE bits) has been stable for 1 ms, but different from<br>last time           |

|          | 0 = USB line state has not been stable for 1 ms                                                                                |

| bit 4    | ACTVIF: Bus Activity Indicator bit                                                                                             |

|          | 1 = Activity on the D+/D- lines or VBUS detected                                                                               |

|          | 0 = No activity on the D+/D- lines or VBUS detected                                                                            |

| bit 3    | SESVDIF: Session Valid Change Indicator bit                                                                                    |

|          | 1 = VBUS has crossed VA_SESS_END (as defined in the USB OTG Specification) <sup>(1)</sup>                                      |

|          | 0 = VBUS has not crossed VA_SESS_END                                                                                           |

| bit 2    | SESENDIF: B-Device VBUS Change Indicator bit                                                                                   |

|          | 1 = VBUS change on B-device detected; VBUS has crossed VB_SESS_END (as defined in the USB OTG<br>Specification) <sup>(1)</sup> |

|          | 0 = VBUS has not crossed VA_SESS_END                                                                                           |

| bit 1    | Unimplemented: Read as '0'                                                                                                     |

| bit 0    | VBUSVDIF A-Device VBUS Change Indicator bit                                                                                    |

|          | 1 = VBUS change on A-device detected; VBUS has crossed VA_VBUS_VLD (as defined in the USB OTG<br>Specification) <sup>(1)</sup> |

|          | 0 = No VBUS change on A-device detected                                                                                        |

| Note 1:  | VBUS threshold crossings may be either rising or falling.                                                                      |

**Note:** Individual bits can only be cleared by writing a '1' to the bit position as part of a word write operation on the entire register. Using Boolean instructions or bitwise operations to write to a single bit position will cause all set bits at the moment of the write to become cleared.

# 23.0 TRIPLE COMPARATOR MODULE

| Note: | This data sheet summarizes the features    |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|

|       | of this group of PIC24F devices. It is not |  |  |  |  |  |  |

|       | intended to be a comprehensive reference   |  |  |  |  |  |  |

|       | source. For more information, refer to the |  |  |  |  |  |  |

|       | associated "PIC24F Family Reference        |  |  |  |  |  |  |

|       | Manual" chapter.                           |  |  |  |  |  |  |

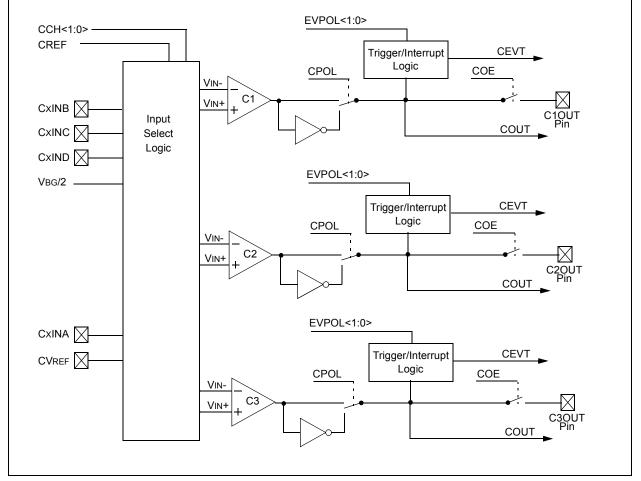

The triple comparator module provides three dual input comparators. The inputs to the comparator can be configured to use any one of four external analog inputs as well, as a voltage reference input from either the internal band gap reference divided by two (VBG/2) or the comparator voltage reference generator.

The comparator outputs may be directly connected to the CxOUT pins. When the respective COE equals '1', the I/O pad logic makes the unsynchronized output of the comparator available on the pin.

A simplified block diagram of the module in shown in Figure 23-1. Diagrams of the possible individual comparator configurations are shown in Figure 23-2.

Each comparator has its own control register, CMxCON (Register 23-1), for enabling and configuring its operation. The output and event status of all three comparators is provided in the CMSTAT register (Register 23-2).

# FIGURE 23-1: TRIPLE COMPARATOR MODULE BLOCK DIAGRAM

| R/W-0         | U-0                                                             | R/W-0             | R/W-0                  | R/W-0            | R/W-0            | R/W-0           | R/W-0    |  |  |  |

|---------------|-----------------------------------------------------------------|-------------------|------------------------|------------------|------------------|-----------------|----------|--|--|--|

| CTMUEN        |                                                                 | CTMUSIDL          | TGEN                   | EDGEN            | EDGSEQEN         | IDISSEN         | CTTRIG   |  |  |  |

| bit 15        |                                                                 |                   |                        |                  |                  |                 | bit 8    |  |  |  |

|               |                                                                 |                   |                        |                  |                  |                 |          |  |  |  |

| R/W-0         | R/W-0                                                           | R/W-0             | R/W-0                  | R/W-0            | R/W-0            | R/W-0           | R/W-0    |  |  |  |

| EDG2POL       | EDG2SEL1                                                        | EDG2SEL0          | EDG1POL                | EDG1SEL1         | EDG1SEL0         | EDG2STAT        | EDG1STAT |  |  |  |

| bit 7         |                                                                 |                   |                        |                  |                  |                 | bit C    |  |  |  |

|               |                                                                 |                   |                        |                  |                  |                 |          |  |  |  |

| Legend:       |                                                                 |                   |                        |                  |                  |                 |          |  |  |  |

| R = Readable  |                                                                 | W = Writable I    | oit                    | •                | nented bit, read | l as '0'        |          |  |  |  |

| -n = Value at | POR                                                             | '1' = Bit is set  |                        | '0' = Bit is cle | ared             | x = Bit is unkn | own      |  |  |  |

|               |                                                                 |                   |                        |                  |                  |                 |          |  |  |  |

| bit 15        |                                                                 | FMU Enable bit    |                        |                  |                  |                 |          |  |  |  |

|               | 1 = Module is<br>0 = Module is                                  |                   |                        |                  |                  |                 |          |  |  |  |

| bit 14        |                                                                 | ited: Read as '0  | )'                     |                  |                  |                 |          |  |  |  |

| bit 13        | -                                                               | Stop in Idle Mod  |                        |                  |                  |                 |          |  |  |  |

|               |                                                                 | nue module ope    |                        | evice enters Idl | e mode           |                 |          |  |  |  |

|               |                                                                 | module operat     |                        |                  | 0                |                 |          |  |  |  |

| bit 12        | TGEN: Time                                                      | Generation Ena    | ble bit <sup>(1)</sup> |                  |                  |                 |          |  |  |  |

|               | 1 = Enables edge delay generation                               |                   |                        |                  |                  |                 |          |  |  |  |

|               | 0 = Disables edge delay generation                              |                   |                        |                  |                  |                 |          |  |  |  |

| bit 10        | EDGEN: Edg                                                      |                   |                        |                  |                  |                 |          |  |  |  |

|               | 1 = Edges are not blocked<br>0 = Edges are blocked              |                   |                        |                  |                  |                 |          |  |  |  |

| bit 10        | •                                                               | Edge Sequence     | e Enable hit           |                  |                  |                 |          |  |  |  |

|               |                                                                 | vent must occu    |                        | 2 event can or   | cur              |                 |          |  |  |  |

|               |                                                                 | sequence is ne    |                        |                  |                  |                 |          |  |  |  |

| bit 9         | IDISSEN: An                                                     | alog Current Sc   | ource Control b        | oit              |                  |                 |          |  |  |  |

|               | 1 = Analog current source output is grounded                    |                   |                        |                  |                  |                 |          |  |  |  |

|               |                                                                 | urrent source o   | utput is not gro       | bunded           |                  |                 |          |  |  |  |

| bit 8         | -                                                               | ger Control bit   |                        |                  |                  |                 |          |  |  |  |

|               | 1 = Trigger output is enabled<br>0 = Trigger output is disabled |                   |                        |                  |                  |                 |          |  |  |  |

| bit 7         |                                                                 | Edge 2 Polarity S |                        |                  |                  |                 |          |  |  |  |

|               |                                                                 | rogrammed for     |                        | e response       |                  |                 |          |  |  |  |

|               |                                                                 | rogrammed for     |                        |                  |                  |                 |          |  |  |  |

| bit 6-5       | EDG2SEL<1                                                       | :0>: Edge 2 So    | urce Select bit        | s                |                  |                 |          |  |  |  |

|               | 11 = CTED1                                                      |                   |                        |                  |                  |                 |          |  |  |  |

|               | 10 = CTED2                                                      | •                 |                        |                  |                  |                 |          |  |  |  |

|               | 01 = OC1 mo<br>00 = Timer1 r                                    |                   |                        |                  |                  |                 |          |  |  |  |

| bit 4         |                                                                 | dge 1 Polarity S  | Select bit             |                  |                  |                 |          |  |  |  |

|               |                                                                 | rogrammed for     |                        | e response       |                  |                 |          |  |  |  |

|               |                                                                 | rogrammed for     |                        |                  |                  |                 |          |  |  |  |

| Note 1: If ]  | CEN - 1 that                                                    | CTEDGx inputs     | and CTDI S a           | utoute must be   | assigned to av   | ailabla PDn nin |          |  |  |  |

See Section 10.4 "Peripheral Pin Select" for more information.

#### REGISTER 25-1: CTMUCON: CTMU CONTROL REGISTER

© 2009 Microchip Technology Inc.

| Assembly<br>Mnemonic | Assembly Syntax |             | Description                  | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|----------------------|-----------------|-------------|------------------------------|---------------|----------------|--------------------------|

| TBLRDH               | TBLRDH          | Ws,Wd       | Read Prog<23:16> to Wd<7:0>  | 1             | 2              | None                     |

| TBLRDL               | TBLRDL          | Ws,Wd       | Read Prog<15:0> to Wd        | 1             | 2              | None                     |

| TBLWTH               | TBLWTH          | Ws,Wd       | Write Ws<7:0> to Prog<23:16> | 1             | 2              | None                     |

| TBLWTL               | TBLWTL          | Ws,Wd       | Write Ws to Prog<15:0>       | 1             | 2              | None                     |

| ULNK                 | ULNK            |             | Unlink Frame Pointer         | 1             | 1              | None                     |

| XOR                  | XOR             | f           | f = f .XOR. WREG             | 1             | 1              | N, Z                     |

|                      | XOR             | f,WREG      | WREG = f .XOR. WREG          | 1             | 1              | N, Z                     |

|                      | XOR             | #lit10,Wn   | Wd = lit10 .XOR. Wd          | 1             | 1              | N, Z                     |

|                      | XOR             | Wb,Ws,Wd    | Wd = Wb .XOR. Ws             | 1             | 1              | N, Z                     |

|                      | XOR             | Wb,#lit5,Wd | Wd = Wb .XOR. lit5           | 1             | 1              | N, Z                     |

| ZE                   | ZE              | Ws,Wnd      | Wnd = Zero-Extend Ws         | 1             | 1              | C, Z, N                  |

#### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

#### TABLE 29-10: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS

| Operati      | <b>Operating Conditions:</b> -40°C < TA < +125°C (unless otherwise stated) |                                     |     |     |     |       |                                                             |  |  |

|--------------|----------------------------------------------------------------------------|-------------------------------------|-----|-----|-----|-------|-------------------------------------------------------------|--|--|

| Param<br>No. | Symbol                                                                     | Characteristics                     | Min | Тур | Max | Units | Comments                                                    |  |  |

|              | Vrgout                                                                     | Regulator Output Voltage            | _   | 2.5 | _   | V     |                                                             |  |  |

|              | Vbg                                                                        | Internal Band Gap Reference         | _   | 1.2 | _   | V     |                                                             |  |  |

|              | CEFC                                                                       | External Filter Capacitor Value     | 4.7 | 10  |     | μF    | Series resistance < 3 Ohm<br>recommended; < 5 Ohm required. |  |  |

|              | TVREG                                                                      | Regulator Start-up Time             |     |     |     |       |                                                             |  |  |

|              |                                                                            |                                     | —   | 10  | —   | μS    | PMSLP = 1, or any POR or BOR                                |  |  |

|              |                                                                            |                                     | _   | 190 | _   | μS    | Wake for sleep when PMSLP = 0                               |  |  |

|              | Твg                                                                        | Band Gap Reference Start-up<br>Time |     | _   | 1   | ms    |                                                             |  |  |

### 29.2 AC Characteristics and Timing Parameters

The information contained in this section defines the PIC24FJ256GB110 family AC characteristics and timing parameters.

#### TABLE 29-11: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 2.0V to 3.6V (unless otherwise stated)          |  |  |  |

|--------------------|--------------------------------------------------------------------------------|--|--|--|

| AC CHARACTERISTICS | Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial    |  |  |  |

|                    | Operating voltage VDD range as described in Section 29.1 "DC Characteristics". |  |  |  |

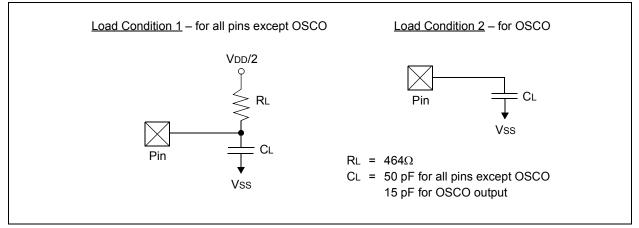

#### FIGURE 29-2: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

#### TABLE 29-12: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min | Typ <sup>(1)</sup> | Max | Units | Conditions                                                          |

|--------------|--------|-----------------------|-----|--------------------|-----|-------|---------------------------------------------------------------------|

| DO50         | Cosc2  | OSCO/CLKO pin         | _   | —                  | 15  |       | In XT and HS modes when<br>external clock is used to drive<br>OSCI. |

| DO56         | Сю     | All I/O pins and OSCO | —   | —                  | 50  | pF    | EC mode.                                                            |

| DO58         | Св     | SCLx, SDAx            |     | —                  | 400 | pF    | In I <sup>2</sup> C™ mode.                                          |

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

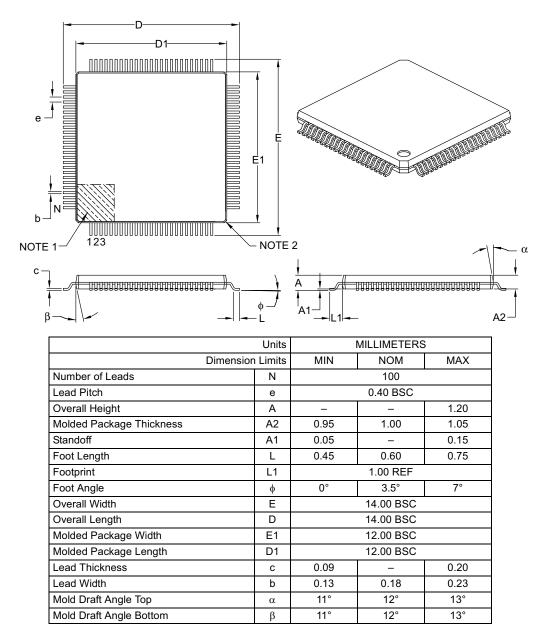

### 100-Lead Plastic Thin Quad Flatpack (PT) – 12x12x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

- 3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-100B

#### D

| Data Memory                   |     |

|-------------------------------|-----|

| Address Space                 | 41  |

| Memory Map                    | 41  |

| Near Data Space               |     |

| SFR Space                     |     |

| Software Stack                | 59  |

| Space Organization            |     |

| DC Characteristics            |     |

| I/O Pin Input Specifications  | 318 |

| I/O Pin Output Specifications | 319 |

| Idle Current                  | 315 |

| Operating Current             | 314 |

| Power-Down Current            | 316 |

| Program Memory Specifications | 319 |

| Development Support           | 299 |

| Device Features (Summary)     |     |

| 100-Pin                       | 15  |

| 64-Pin                        |     |

| 80-Pin                        | 14  |

| Doze Mode                     | 132 |

#### Е

| Electrical Characteristics                |  |

|-------------------------------------------|--|

| A/D Specifications                        |  |

| Absolute Maximum Ratings                  |  |

| External Clock                            |  |

| Internal Voltage Regulator Specifications |  |

| Load Conditions and Requirements for      |  |

| Specifications                            |  |

| PLL Clock Specifications                  |  |

| Temperature and Voltage Specifications    |  |

| Thermal Conditions                        |  |

| V/F Graph                                 |  |

| ENVREG Pin                                |  |

| Equations                                 |  |

| A/D Conversion Clock Period274            |  |

| Baud Rate Reload Calculation 193          |  |

| Calculating the PWM Period176             |  |

| Calculation for Maximum PWM Resolution    |  |

| Estimating USB Transceiver Current        |  |

| Consumption211                            |  |

| Relationship Between Device and SPI       |  |

| Clock Speed190                            |  |

| RTCC Calibration                          |  |

| UART Baud Rate with BRGH = 0              |  |

| UART Baud Rate with BRGH = 1              |  |

| Errata 9                                  |  |

### F

| 40, 287–291 |

|-------------|

| 63          |

| 63          |

| 64          |

| 64          |

|             |

| 64          |

| 69          |

|             |

# I

| I/O Ports                      |  |

|--------------------------------|--|

| Analog Port Pins Configuration |  |

| Input Change Notification      |  |

| Open-Drain Configuration       |  |

| Parallel (PIO)                 |  |

| Peripheral Pi                         | n Select                      | 135 |

|---------------------------------------|-------------------------------|-----|

| Pull-ups and                          | Pull-downs                    |     |