Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

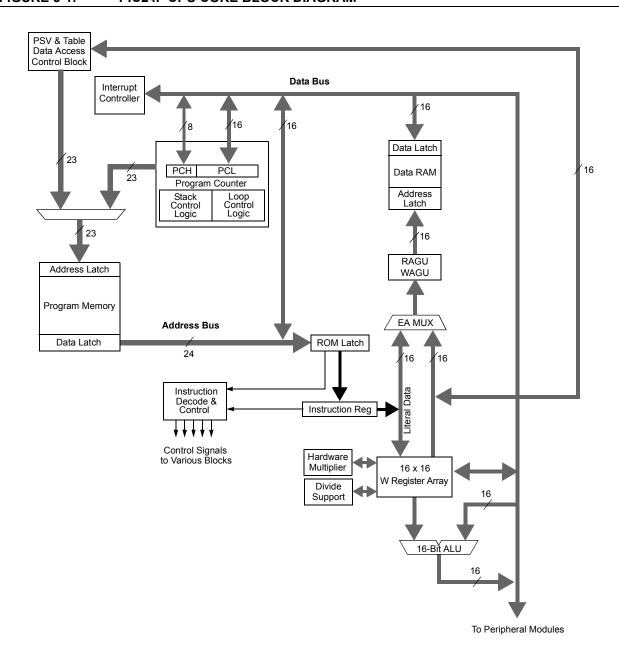

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB OTG                                     |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 65                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 80-TQFP                                                                        |

| Supplier Device Package    | 80-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128gb108-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### EXAMPLE 5-4: LOADING THE WRITE BUFFERS (C LANGUAGE CODE)

```

// C example using MPLAB C30

#define NUM_INSTRUCTION_PER_ROW 64

unsigned int offset;

unsigned int i;

unsigned long progAddr = 0xXXXXXX;

// Address of row to write

unsigned int progData[2*NUM_INSTRUCTION_PER_ROW]; // Buffer of data to write

//Set up NVMCON for row programming

NVMCON = 0 \times 4001;

// Initialize NVMCON

//Set up pointer to the first memory location to be written

// Initialize PM Page Boundary SFR

TBLPAG = progAddr>>16;

offset = progAddr & 0xFFFF;

// Initialize lower word of address

//Perform TBLWT instructions to write necessary number of latches

for(i=0; i < 2*NUM_INSTRUCTION_PER_ROW; i++)</pre>

{

__builtin_tblwtl(offset, progData[i++]); // Write to address low word

__builtin_tblwth(offset, progData[i]); // Write to upper byte

// Increment address

offset = offset + 2;

}

```

| DISI | #5          | ; | Block all interrupts with priority <7 |

|------|-------------|---|---------------------------------------|

|      |             | ; | for next 5 instructions               |

| MOV  | #0x55, W0   |   |                                       |

| MOV  | W0, NVMKEY  | ; | Write the 55 key                      |

| MOV  | #0xAA, W1   | ; |                                       |

| MOV  | W1, NVMKEY  | ; | Write the AA key                      |

| BSET | NVMCON, #WR | ; | Start the erase sequence              |

| NOP  |             | ; |                                       |

| NOP  |             | ; |                                       |

| BTSC | NVMCON, #15 | ; | and wait for it to be                 |

| BRA  | \$-2        | ; | completed                             |

|      |             |   |                                       |

#### EXAMPLE 5-6: INITIATING A PROGRAMMING SEQUENCE (C LANGUAGE CODE)

| // C example using MPLAB C | 30 |                                                                   |

|----------------------------|----|-------------------------------------------------------------------|

| · · · ·                    |    | Block all interrupts with priority < 7<br>for next 5 instructions |

| builtin_write_NVM();       | // | Perform unlock sequence and set WR                                |

NOTES:

| REGISTER     | 7-6: IFS1:                            | INTERRUPT                                                | FLAG STAT                | US REGISTE        | ER 1            |                 |         |

|--------------|---------------------------------------|----------------------------------------------------------|--------------------------|-------------------|-----------------|-----------------|---------|

| R/W-0        | R/W-0                                 | R/W-0                                                    | R/W-0                    | R/W-0             | R/W-0           | R/W-0           | U-0     |

| U2TXIF       | U2RXIF                                | INT2IF                                                   | T5IF                     | T4IF              | OC4IF           | OC3IF           |         |

| bit 15       |                                       |                                                          |                          |                   |                 |                 | bit 8   |

| R/W-0        | R/W-0                                 | U-0                                                      | R/W-0                    | R/W-0             | R/W-0           | R/W-0           | R/W-0   |

| IC8IF        | IC7IF                                 | _                                                        | INT1IF                   | CNIF              | CMIF            | MI2C1IF         | SI2C1IF |

| bit 7        |                                       |                                                          |                          |                   |                 |                 | bit 0   |

| Legend:      |                                       |                                                          |                          |                   |                 |                 |         |

| R = Readab   | le bit                                | W = Writable I                                           | oit                      | U = Unimplen      | nented bit, rea | d as '0'        |         |

| -n = Value a | t POR                                 | '1' = Bit is set                                         |                          | '0' = Bit is clea | ared            | x = Bit is unkr | nown    |

| bit 15       | 1 = Interrupt                         | RT2 Transmitter<br>request has occ<br>request has not    | urred                    | Status bit        |                 |                 |         |

| bit 14       | 1 = Interrupt                         | RT2 Receiver In<br>request has occ<br>request has not    | urred                    | tatus bit         |                 |                 |         |

| bit 13       | 1 = Interrupt                         | rnal Interrupt 2 F<br>request has occ<br>request has not | urred                    |                   |                 |                 |         |

| bit 12       | 1 = Interrupt                         | Interrupt Flag S<br>request has occ<br>request has not   | urred                    |                   |                 |                 |         |

| bit 11       | 1 = Interrupt                         | Interrupt Flag S<br>request has occ<br>request has not   | urred                    |                   |                 |                 |         |

| bit 10       | 1 = Interrupt                         | ut Compare Cha<br>request has occ<br>request has not     | urred                    | pt Flag Status I  | bit             |                 |         |

| bit 9        | 1 = Interrupt                         | ut Compare Cha<br>request has occ<br>request has not     | urred                    | pt Flag Status I  | bit             |                 |         |

| bit 8        | Unimplemen                            | ted: Read as '0                                          | )'                       |                   |                 |                 |         |

| bit 7        | 1 = Interrupt                         | Capture Channe<br>request has occ<br>request has not     | urred                    | lag Status bit    |                 |                 |         |

| bit 6        | 1 = Interrupt                         | Capture Channe<br>request has occ<br>request has not     | urred                    | lag Status bit    |                 |                 |         |

| bit 5        | Unimplemen                            | ted: Read as 'o                                          | )'                       |                   |                 |                 |         |

| bit 4        | 1 = Interrupt                         | nal Interrupt 1 F<br>request has occ<br>request has not  | urred                    |                   |                 |                 |         |

| bit 3        | <b>CNIF:</b> Input C<br>1 = Interrupt | Change Notificat<br>request has occ<br>request has not   | ion Interrupt F<br>urred | lag Status bit    |                 |                 |         |

| bit 2        | 1 = Interrupt                         | arator Interrupt<br>request has occ<br>request has not   | urred                    |                   |                 |                 |         |

| bit 1        | 1 = Interrupt                         | ster I2C1 Event<br>request has occ<br>request has not    | urred                    | Status bit        |                 |                 |         |

| bit 0        | 1 = Interrupt                         | ve I2C1 Event In<br>request has occ<br>request has not   | urred                    | Status bit        |                 |                 |         |

#### REGISTER 7-17: IPC0: INTERRUPT PRIORITY CONTROL REGISTER 0

| U-0                                   | R/W-1                                                                                                                                                                                                         | R/W-0                                                                                                                                                                                                                                        | R/W-0                                                                                                                                     | U-0                                                        | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |  |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|------------------|-----------------|---------|--|--|--|--|--|

| _                                     | T1IP2                                                                                                                                                                                                         | T1IP1                                                                                                                                                                                                                                        | T1IP0                                                                                                                                     | _                                                          | OC1IP2           | OC1IP1          | OC1IP0  |  |  |  |  |  |

| bit 15                                |                                                                                                                                                                                                               |                                                                                                                                                                                                                                              |                                                                                                                                           |                                                            |                  |                 | bit 8   |  |  |  |  |  |

|                                       |                                                                                                                                                                                                               |                                                                                                                                                                                                                                              |                                                                                                                                           |                                                            |                  |                 |         |  |  |  |  |  |

| U-0                                   | R/W-1                                                                                                                                                                                                         | R/W-0                                                                                                                                                                                                                                        | R/W-0                                                                                                                                     | U-0                                                        | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |  |

| _                                     | IC1IP2                                                                                                                                                                                                        | IC1IP1                                                                                                                                                                                                                                       | IC1IP0                                                                                                                                    |                                                            | INT0IP2          | INT0IP1         | INT0IP0 |  |  |  |  |  |

| bit 7                                 |                                                                                                                                                                                                               |                                                                                                                                                                                                                                              |                                                                                                                                           |                                                            |                  |                 | bit (   |  |  |  |  |  |

| Legend:                               |                                                                                                                                                                                                               |                                                                                                                                                                                                                                              |                                                                                                                                           |                                                            |                  |                 |         |  |  |  |  |  |

| R = Readab                            | le bit                                                                                                                                                                                                        | W = Writable I                                                                                                                                                                                                                               | oit                                                                                                                                       | U = Unimpler                                               | nented bit, read | d as '0'        |         |  |  |  |  |  |

| -n = Value a                          | t POR                                                                                                                                                                                                         | '1' = Bit is set                                                                                                                                                                                                                             |                                                                                                                                           | '0' = Bit is cle                                           | ared             | x = Bit is unkr | nown    |  |  |  |  |  |

| bit 15                                | Unimplemen                                                                                                                                                                                                    | nted: Read as '0                                                                                                                                                                                                                             | )'                                                                                                                                        |                                                            |                  |                 |         |  |  |  |  |  |

| bit 14-12                             | -                                                                                                                                                                                                             | imer1 Interrupt                                                                                                                                                                                                                              |                                                                                                                                           |                                                            |                  |                 |         |  |  |  |  |  |

|                                       |                                                                                                                                                                                                               | -                                                                                                                                                                                                                                            | -                                                                                                                                         | y interrupt)                                               |                  |                 |         |  |  |  |  |  |

|                                       | •                                                                                                                                                                                                             | <ul><li>111 = Interrupt is priority 7 (highest priority interrupt)</li><li></li></ul>                                                                                                                                                        |                                                                                                                                           |                                                            |                  |                 |         |  |  |  |  |  |

|                                       | •                                                                                                                                                                                                             |                                                                                                                                                                                                                                              |                                                                                                                                           |                                                            |                  |                 |         |  |  |  |  |  |

|                                       | •<br>001 = Interrupt is priority 1                                                                                                                                                                            |                                                                                                                                                                                                                                              |                                                                                                                                           |                                                            |                  |                 |         |  |  |  |  |  |

|                                       |                                                                                                                                                                                                               | pt source is disa                                                                                                                                                                                                                            | abled                                                                                                                                     |                                                            |                  |                 |         |  |  |  |  |  |

| it 11 Unimplemented: Read as '0'      |                                                                                                                                                                                                               |                                                                                                                                                                                                                                              |                                                                                                                                           |                                                            |                  |                 |         |  |  |  |  |  |

| -                                     | -                                                                                                                                                                                                             |                                                                                                                                                                                                                                              |                                                                                                                                           |                                                            |                  |                 |         |  |  |  |  |  |

|                                       | -                                                                                                                                                                                                             |                                                                                                                                                                                                                                              |                                                                                                                                           | Interrupt Priorit                                          | y bits           |                 |         |  |  |  |  |  |

|                                       | OC1IP<2:0>:                                                                                                                                                                                                   |                                                                                                                                                                                                                                              | re Channel 1                                                                                                                              |                                                            | y bits           |                 |         |  |  |  |  |  |

|                                       | OC1IP<2:0>:                                                                                                                                                                                                   | : Output Compa                                                                                                                                                                                                                               | re Channel 1                                                                                                                              |                                                            | y bits           |                 |         |  |  |  |  |  |

| bit 10-8                              | OC1IP<2:0>:                                                                                                                                                                                                   | : Output Compa                                                                                                                                                                                                                               | re Channel 1                                                                                                                              |                                                            | y bits           |                 |         |  |  |  |  |  |

|                                       | OC1IP<2:0>:<br>111 = Interru                                                                                                                                                                                  | : Output Compa                                                                                                                                                                                                                               | re Channel 1                                                                                                                              |                                                            | y bits           |                 |         |  |  |  |  |  |

|                                       | OC1IP<2:0>:<br>111 = Interru<br>001 = Interru                                                                                                                                                                 | : Output Compa<br>pt is priority 7 (h                                                                                                                                                                                                        | re Channel 1<br>highest priority                                                                                                          |                                                            | y bits           |                 |         |  |  |  |  |  |

| bit 10-8                              | OC1IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru                                                                                                                                                | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1                                                                                                                                                                                    | re Channel 1<br>highest priority<br>abled                                                                                                 |                                                            | y bits           |                 |         |  |  |  |  |  |

| bit 10-8<br>bit 7                     | OC1IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>IC1IP<2:0>:                                                                                                                   | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>nted:</b> Read as '0<br>Input Capture C                                                                                                                 | re Channel 1<br>highest priority<br>abled<br>''<br>hannel 1 Inte                                                                          | y interrupt)<br>rrupt Priority bit                         |                  |                 |         |  |  |  |  |  |

| bit 10-8<br>bit 7                     | OC1IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>IC1IP<2:0>:                                                                                                                   | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>nted:</b> Read as '0                                                                                                                                    | re Channel 1<br>highest priority<br>abled<br>''<br>hannel 1 Inte                                                                          | y interrupt)<br>rrupt Priority bit                         |                  |                 |         |  |  |  |  |  |

| bit 10-8<br>bit 7                     | OC1IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>IC1IP<2:0>:                                                                                                                   | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>nted:</b> Read as 'o<br>Input Capture C                                                                                                                 | re Channel 1<br>highest priority<br>abled<br>''<br>hannel 1 Inte                                                                          | y interrupt)<br>rrupt Priority bit                         |                  |                 |         |  |  |  |  |  |

| bit 10-8<br>bit 7                     | OC1IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>IC1IP<2:0>:                                                                                                                   | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>nted:</b> Read as 'o<br>Input Capture C                                                                                                                 | re Channel 1<br>highest priority<br>abled<br>''<br>hannel 1 Inte                                                                          | y interrupt)<br>rrupt Priority bit                         |                  |                 |         |  |  |  |  |  |

| bit 10-8<br>bit 7                     | OC1IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>IC1IP<2:0>:<br>111 = Interru                                                                                                  | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>nted:</b> Read as 'o<br>Input Capture C                                                                                                                 | re Channel 1<br>highest priority<br>abled<br>''<br>hannel 1 Inte                                                                          | y interrupt)<br>rrupt Priority bit                         |                  |                 |         |  |  |  |  |  |

| bit 10-8<br>bit 7                     | OC1IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>IC1IP<2:0>:<br>111 = Interru<br>001 = Interru                                                                                 | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br>nted: Read as 'c<br>Input Capture C<br>pt is priority 7 (h                                                                                                 | re Channel 1<br>highest priority<br>abled<br>,,<br>hannel 1 Inte<br>highest priority                                                      | y interrupt)<br>rrupt Priority bit                         |                  |                 |         |  |  |  |  |  |

| bit 10-8<br>bit 7<br>bit 6-4          | OC1IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>IC1IP<2:0>:<br>111 = Interru<br>001 = Interru<br>001 = Interru                                                                | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>ited:</b> Read as '0<br>Input Capture C<br>pt is priority 7 (h                                                                                          | re Channel 1<br>highest priority<br>abled<br>,'<br>hannel 1 Inte<br>highest priority                                                      | y interrupt)<br>rrupt Priority bit                         |                  |                 |         |  |  |  |  |  |

| bit 10-8<br>bit 7<br>bit 6-4<br>bit 3 | OC1IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>IC1IP<2:0>:<br>111 = Interru<br>001 = Interru<br>001 = Interru<br>Unimplemen<br>INT0IP<2:0>                                   | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>ited:</b> Read as '0<br>Input Capture C<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>ited:</b> Read as '0<br>: External Intern | re Channel 1<br>highest priority<br>abled<br>hannel 1 Inte<br>highest priority<br>abled                                                   | y interrupt)<br>rrupt Priority bit<br>y interrupt)<br>bits |                  |                 |         |  |  |  |  |  |

| bit 10-8<br>bit 7<br>bit 6-4<br>bit 3 | OC1IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>IC1IP<2:0>:<br>111 = Interru<br>001 = Interru<br>001 = Interru<br>Unimplemen<br>INT0IP<2:0>                                   | Output Compa<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>nted:</b> Read as '0<br>Input Capture C<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>nted:</b> Read as '0                        | re Channel 1<br>highest priority<br>abled<br>hannel 1 Inte<br>highest priority<br>abled                                                   | y interrupt)<br>rrupt Priority bit<br>y interrupt)<br>bits |                  |                 |         |  |  |  |  |  |

| bit 10-8<br>bit 7<br>bit 6-4<br>bit 3 | OC1IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>IC1IP<2:0>:<br>111 = Interru<br>001 = Interru<br>001 = Interru<br>Unimplemen<br>INT0IP<2:0>                                   | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>ited:</b> Read as '0<br>Input Capture C<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>ited:</b> Read as '0<br>: External Intern | re Channel 1<br>highest priority<br>abled<br>hannel 1 Inte<br>highest priority<br>abled                                                   | y interrupt)<br>rrupt Priority bit<br>y interrupt)<br>bits |                  |                 |         |  |  |  |  |  |

|                                       | OC1IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>IC1IP<2:0>:<br>111 = Interru<br>001 = Interru<br>001 = Interru<br>Unimplemen<br>INT0IP<2:0>                                   | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>ited:</b> Read as '0<br>Input Capture C<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>ited:</b> Read as '0<br>: External Intern | re Channel 1<br>highest priority<br>abled<br>hannel 1 Inte<br>highest priority<br>abled                                                   | y interrupt)<br>rrupt Priority bit<br>y interrupt)<br>bits |                  |                 |         |  |  |  |  |  |

| bit 10-8<br>bit 7<br>bit 6-4<br>bit 3 | OC1IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>IC1IP<2:0>:<br>111 = Interru<br>001 = Interru<br>001 = Interru<br>Unimplemen<br>INT0IP<2:0><br>111 = Interru<br>001 = Interru | : Output Compa<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>ited:</b> Read as '0<br>Input Capture C<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>ited:</b> Read as '0<br>: External Intern | re Channel 1<br>highest priority<br>abled<br>,<br>hannel 1 Inte<br>highest priority<br>abled<br>,<br>upt 0 Priority I<br>highest priority | y interrupt)<br>rrupt Priority bit<br>y interrupt)<br>bits |                  |                 |         |  |  |  |  |  |

| U-0          | R/W-1                                                                 | R/W-0                                     | R/W-0             | U-0              | R/W-1           | R/W-0           | R/W-0   |  |  |  |  |  |

|--------------|-----------------------------------------------------------------------|-------------------------------------------|-------------------|------------------|-----------------|-----------------|---------|--|--|--|--|--|

| _            | U1RXIP2                                                               | U1RXIP1                                   | U1RXIP0           |                  | SPI1IP2         | SPI1IP1         | SPI1IP0 |  |  |  |  |  |

| oit 15       |                                                                       |                                           | 1                 |                  |                 |                 | bit     |  |  |  |  |  |

|              |                                                                       |                                           |                   |                  |                 |                 |         |  |  |  |  |  |

| U-0          | R/W-1                                                                 | R/W-0                                     | R/W-0             | U-0              | R/W-1           | R/W-0           | R/W-0   |  |  |  |  |  |

| —            | SPF1IP2                                                               | SPF1IP1                                   | SPF1IP0           |                  | T3IP2           | T3IP1           | T3IP0   |  |  |  |  |  |

| bit 7        |                                                                       |                                           |                   |                  |                 |                 | bit     |  |  |  |  |  |

| Legend:      |                                                                       |                                           |                   |                  |                 |                 |         |  |  |  |  |  |

| R = Readab   | le bit                                                                | W = Writable                              | bit               | U = Unimplei     | mented bit, rea | d as '0'        |         |  |  |  |  |  |

| -n = Value a | It POR                                                                | '1' = Bit is set                          |                   | '0' = Bit is cle |                 | x = Bit is unkr | nown    |  |  |  |  |  |

|              |                                                                       |                                           |                   |                  |                 |                 |         |  |  |  |  |  |

| bit 15       | Unimplemen                                                            | ted: Read as '                            | )'                |                  |                 |                 |         |  |  |  |  |  |

| bit 14-12    | U1RXIP<2:0>                                                           | >: UART1 Rece                             | eiver Interrupt I | Priority bits    |                 |                 |         |  |  |  |  |  |

|              | 111 = Interru                                                         | pt is priority 7 (l                       | nighest priority  | interrupt)       |                 |                 |         |  |  |  |  |  |

|              | •                                                                     |                                           |                   |                  |                 |                 |         |  |  |  |  |  |

|              | •                                                                     |                                           |                   |                  |                 |                 |         |  |  |  |  |  |

|              | 001 = Interrupt is priority 1                                         |                                           |                   |                  |                 |                 |         |  |  |  |  |  |

|              | 000 = Interru                                                         | pt source is dis                          | abled             |                  |                 |                 |         |  |  |  |  |  |

| bit 11       | Unimplemen                                                            | ted: Read as '                            | כי                |                  |                 |                 |         |  |  |  |  |  |

| bit 10-8     | SPI1IP<2:0>:                                                          | SPI1 Event In                             | terrupt Priority  | bits             |                 |                 |         |  |  |  |  |  |

|              | 111 = Interrupt is priority 7 (highest priority interrupt)            |                                           |                   |                  |                 |                 |         |  |  |  |  |  |

|              |                                                                       |                                           |                   |                  |                 |                 |         |  |  |  |  |  |

|              | •                                                                     |                                           |                   |                  |                 |                 |         |  |  |  |  |  |

|              | 001 = Interrupt is priority 1                                         |                                           |                   |                  |                 |                 |         |  |  |  |  |  |

|              | 000 = Interru                                                         | pt source is dis                          | abled             |                  |                 |                 |         |  |  |  |  |  |

| bit 7        | Unimplemen                                                            | ted: Read as '                            | כי                |                  |                 |                 |         |  |  |  |  |  |

| bit 6-4      | SPF1IP<2:0>                                                           | SPI1 Fault In                             | terrupt Priority  | bits             |                 |                 |         |  |  |  |  |  |

|              | <pre>111 = Interrupt is priority 7 (highest priority interrupt)</pre> |                                           |                   |                  |                 |                 |         |  |  |  |  |  |

|              | •                                                                     |                                           |                   |                  |                 |                 |         |  |  |  |  |  |

|              | •                                                                     |                                           |                   |                  |                 |                 |         |  |  |  |  |  |

|              | 001 = Interru                                                         | pt is priority 1                          |                   |                  |                 |                 |         |  |  |  |  |  |

|              | 000 = Interru                                                         | pt source is dis                          | abled             |                  |                 |                 |         |  |  |  |  |  |

| bit 3        | Unimplemen                                                            | ted: Read as '                            | כ'                |                  |                 |                 |         |  |  |  |  |  |

| bit 2-0      |                                                                       | T3IP<2:0>: Timer3 Interrupt Priority bits |                   |                  |                 |                 |         |  |  |  |  |  |

|              | 111 = Interru                                                         | pt is priority 7 (I                       | nighest priority  | interrupt)       |                 |                 |         |  |  |  |  |  |

|              | •                                                                     |                                           |                   |                  |                 |                 |         |  |  |  |  |  |

|              | •                                                                     |                                           |                   |                  |                 |                 |         |  |  |  |  |  |

|              |                                                                       |                                           |                   |                  |                 |                 |         |  |  |  |  |  |

|              | 001 = Interru                                                         | pt is priority 1<br>pt source is dis      |                   |                  |                 |                 |         |  |  |  |  |  |

| U-0              | R/W-1                                                                                       | R/W-0                                                                                                                                                                           | R/W-0                                                                     | U-0                          | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------|------------------|-----------------|---------|--|--|--|--|--|

| _                | CNIP2                                                                                       | CNIP1                                                                                                                                                                           | CNIP0                                                                     |                              | CMIP2            | CMIP1           | CMIP0   |  |  |  |  |  |

| bit 15           | ·                                                                                           |                                                                                                                                                                                 |                                                                           |                              |                  |                 | bit 8   |  |  |  |  |  |

| U-0              | R/W-1                                                                                       | R/W-0                                                                                                                                                                           | R/W-0                                                                     | U-0                          | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |  |

|                  | MI2C1P2                                                                                     | MI2C1P1                                                                                                                                                                         | MI2C1P0                                                                   |                              | SI2C1P2          | SI2C1P1         | SI2C1P0 |  |  |  |  |  |

| bit 7            |                                                                                             |                                                                                                                                                                                 |                                                                           |                              | 0.2011 2         |                 | bit     |  |  |  |  |  |

| Legend:          |                                                                                             |                                                                                                                                                                                 |                                                                           |                              |                  |                 |         |  |  |  |  |  |

| R = Readat       | ole bit                                                                                     | W = Writable                                                                                                                                                                    | bit                                                                       | U = Unimpler                 | mented bit, read | d as '0'        |         |  |  |  |  |  |

| -n = Value a     |                                                                                             | '1' = Bit is set                                                                                                                                                                |                                                                           | '0' = Bit is cle             |                  | x = Bit is unkr | nown    |  |  |  |  |  |

|                  |                                                                                             |                                                                                                                                                                                 |                                                                           |                              |                  |                 |         |  |  |  |  |  |

| bit 15           | -                                                                                           | ited: Read as '                                                                                                                                                                 |                                                                           |                              |                  |                 |         |  |  |  |  |  |

| bit 14-12        |                                                                                             | nput Change N<br>pt is priority 7 (                                                                                                                                             |                                                                           |                              | ts               |                 |         |  |  |  |  |  |

|                  | •                                                                                           | pr is priority 7 (                                                                                                                                                              | ingriest priority                                                         | mienupi)                     |                  |                 |         |  |  |  |  |  |

|                  | •                                                                                           |                                                                                                                                                                                 |                                                                           |                              |                  |                 |         |  |  |  |  |  |

|                  | •                                                                                           |                                                                                                                                                                                 |                                                                           |                              |                  |                 |         |  |  |  |  |  |

|                  | 001 = Interru                                                                               | pt is priority 1<br>pt source is dis                                                                                                                                            | abled                                                                     |                              |                  |                 |         |  |  |  |  |  |

| bit 11           |                                                                                             | ited: Read as '                                                                                                                                                                 |                                                                           |                              |                  |                 |         |  |  |  |  |  |

| bit 10-8         | CMIP<2:0>: Comparator Interrupt Priority bits                                               |                                                                                                                                                                                 |                                                                           |                              |                  |                 |         |  |  |  |  |  |

|                  | 111 = Interrupt is priority 7 (highest priority interrupt)                                  |                                                                                                                                                                                 |                                                                           |                              |                  |                 |         |  |  |  |  |  |

|                  | •                                                                                           |                                                                                                                                                                                 | 0, ,                                                                      | . ,                          |                  |                 |         |  |  |  |  |  |

|                  | •                                                                                           |                                                                                                                                                                                 |                                                                           |                              |                  |                 |         |  |  |  |  |  |

|                  | •<br>001 = Interru                                                                          | pt is priority 1                                                                                                                                                                |                                                                           |                              |                  |                 |         |  |  |  |  |  |

|                  |                                                                                             |                                                                                                                                                                                 |                                                                           |                              |                  |                 |         |  |  |  |  |  |

|                  |                                                                                             | pt source is dis                                                                                                                                                                | abled                                                                     |                              |                  |                 |         |  |  |  |  |  |

| bit 7            | Unimplemen                                                                                  |                                                                                                                                                                                 |                                                                           |                              |                  |                 |         |  |  |  |  |  |

| bit 7<br>bit 6-4 | -                                                                                           | pt source is dis                                                                                                                                                                | כ'                                                                        | t Priority bits              |                  |                 |         |  |  |  |  |  |

|                  | MI2C1P<2:0                                                                                  | pt source is dis<br>ited: Read as '                                                                                                                                             | o'<br>Event Interrup                                                      | -                            |                  |                 |         |  |  |  |  |  |

|                  | MI2C1P<2:0                                                                                  | pt source is dis<br>ited: Read as '<br>>: Master I2C1                                                                                                                           | o'<br>Event Interrup                                                      | -                            |                  |                 |         |  |  |  |  |  |

|                  | MI2C1P<2:0                                                                                  | pt source is dis<br>ited: Read as '<br>>: Master I2C1                                                                                                                           | o'<br>Event Interrup                                                      | -                            |                  |                 |         |  |  |  |  |  |

|                  | MI2C1P<2:0:<br>111 = Interru                                                                | pt source is dis<br>ited: Read as '<br>>: Master I2C1<br>pt is priority 7 (<br>pt is priority 1                                                                                 | <sub>D</sub> '<br>Event Interrup<br>highest priority                      | -                            |                  |                 |         |  |  |  |  |  |

|                  | MI2C1P<2:0:<br>111 = Interru<br>001 = Interru<br>000 = Interru                              | pt source is dis<br><b>ited:</b> Read as '<br>>: Master I2C1<br>pt is priority 7 (                                                                                              | <sub>D</sub> '<br>Event Interrup<br>highest priority<br>abled             | -                            |                  |                 |         |  |  |  |  |  |

| bit 6-4          | MI2C1P<2:0<br>111 = Interru                                                                 | pt source is dis<br><b>ited:</b> Read as '<br>>: Master I2C1<br>pt is priority 7 (<br>pt is priority 1<br>pt source is dis<br><b>ited:</b> Read as '                            | <sub>D</sub> ,<br>Event Interrup<br>highest priority<br>abled             | r interrupt)                 |                  |                 |         |  |  |  |  |  |

| bit 6-4<br>bit 3 | MI2C1P<2:0:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>SI2C1P<2:0> | pt source is dis<br><b>ited:</b> Read as '<br>>: Master I2C1<br>pt is priority 7 (<br>pt is priority 1<br>pt source is dis                                                      | D'<br>Event Interrup<br>highest priority<br>abled<br>D'<br>vent Interrupt | rinterrupt)<br>Priority bits |                  |                 |         |  |  |  |  |  |

| bit 6-4<br>bit 3 | MI2C1P<2:0:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>SI2C1P<2:0> | pt source is dis<br>ited: Read as '<br>>: Master I2C1<br>pt is priority 7 (<br>pt is priority 1<br>pt source is dis<br>ited: Read as '<br>:: Slave I2C1 E                       | D'<br>Event Interrup<br>highest priority<br>abled<br>D'<br>vent Interrupt | rinterrupt)<br>Priority bits |                  |                 |         |  |  |  |  |  |

| bit 6-4<br>bit 3 | MI2C1P<2:0:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>SI2C1P<2:0> | pt source is dis<br>ited: Read as '<br>>: Master I2C1<br>pt is priority 7 (<br>pt is priority 1<br>pt source is dis<br>ited: Read as '<br>:: Slave I2C1 E                       | D'<br>Event Interrup<br>highest priority<br>abled<br>D'<br>vent Interrupt | rinterrupt)<br>Priority bits |                  |                 |         |  |  |  |  |  |

| bit 6-4<br>bit 3 | MI2C1P<2:0:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>SI2C1P<2:0> | pt source is dis<br>ited: Read as '<br>>: Master I2C1<br>pt is priority 7 (<br>pt is priority 1<br>pt source is dis<br>ited: Read as '<br>>: Slave I2C1 E<br>pt is priority 7 ( | D'<br>Event Interrup<br>highest priority<br>abled<br>D'<br>vent Interrupt | rinterrupt)<br>Priority bits |                  |                 |         |  |  |  |  |  |

### REGISTER 7-21: IPC4: INTERRUPT PRIORITY CONTROL REGISTER 4

#### REGISTER 10-9: RPINR10: PERIPHERAL PIN SELECT INPUT REGISTER 10

| U-0 | R/W-1            | R/W-1                                                                                          | R/W-1                                                                                                                                                  | R/W-1                                                                                                                                                                                                       | R/W-1                                                                                                                                                                                                                                                       | R/W-1                                                                                                                                                                                                                                                                                                                                                                      |  |

|-----|------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|     | IC8R5            | IC8R4                                                                                          | IC8R3                                                                                                                                                  | IC8R2                                                                                                                                                                                                       | IC8R1                                                                                                                                                                                                                                                       | IC8R0                                                                                                                                                                                                                                                                                                                                                                      |  |

|     |                  |                                                                                                |                                                                                                                                                        |                                                                                                                                                                                                             |                                                                                                                                                                                                                                                             | bit 8                                                                                                                                                                                                                                                                                                                                                                      |  |

|     |                  |                                                                                                |                                                                                                                                                        |                                                                                                                                                                                                             |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                            |  |

| U-0 | R/W-1            | R/W-1                                                                                          | R/W-1                                                                                                                                                  | R/W-1                                                                                                                                                                                                       | R/W-1                                                                                                                                                                                                                                                       | R/W-1                                                                                                                                                                                                                                                                                                                                                                      |  |

|     | IC7R5            | IC7R4                                                                                          | IC7R3                                                                                                                                                  | IC7R2                                                                                                                                                                                                       | IC7R1                                                                                                                                                                                                                                                       | IC7R0                                                                                                                                                                                                                                                                                                                                                                      |  |

|     |                  |                                                                                                |                                                                                                                                                        | •                                                                                                                                                                                                           |                                                                                                                                                                                                                                                             | bit 0                                                                                                                                                                                                                                                                                                                                                                      |  |

|     |                  |                                                                                                |                                                                                                                                                        |                                                                                                                                                                                                             |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                            |  |

|     |                  |                                                                                                |                                                                                                                                                        |                                                                                                                                                                                                             |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                            |  |