Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB OTG                                     |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 83                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (12x12)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128gb110-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Octopus, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, PIC<sup>32</sup> logo, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2009, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

### QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

|          |                     | Pin Number     |                 |     |                 |                                                |

|----------|---------------------|----------------|-----------------|-----|-----------------|------------------------------------------------|

| Function | 64-Pin<br>TQFP, QFN | 80-Pin<br>TQFP | 100-Pin<br>TQFP | I/O | Input<br>Buffer | Description                                    |

| RC1      | _                   | 4              | 6               | I/O | ST              | PORTC Digital I/O.                             |

| RC2      | _                   |                | 7               | I/O | ST              |                                                |

| RC3      | _                   | 5              | 8               | I/O | ST              |                                                |

| RC4      | _                   | _              | 9               | I/O | ST              |                                                |

| RC12     | 39                  | 49             | 63              | I/O | ST              |                                                |

| RC13     | 47                  | 59             | 73              | I/O | ST              |                                                |

| RC14     | 48                  | 60             | 74              | I/O | ST              |                                                |

| RC15     | 40                  | 50             | 64              | I/O | ST              |                                                |

| RCV      | 18                  | 22             | 27              | I   | ST              | USB Receive Input (from external transceiver). |

| RD0      | 46                  | 58             | 72              | I/O | ST              | PORTD Digital I/O.                             |

| RD1      | 49                  | 61             | 76              | I/O | ST              |                                                |

| RD2      | 50                  | 62             | 77              | I/O | ST              |                                                |

| RD3      | 51                  | 63             | 78              | I/O | ST              |                                                |

| RD4      | 52                  | 66             | 81              | I/O | ST              |                                                |

| RD5      | 53                  | 67             | 82              | I/O | ST              |                                                |

| RD6      | 54                  | 68             | 83              | I/O | ST              |                                                |

| RD7      | 55                  | 69             | 84              | I/O | ST              |                                                |

| RD8      | 42                  | 54             | 68              | I/O | ST              |                                                |

| RD9      | 43                  | 55             | 69              | I/O | ST              |                                                |

| RD10     | 44                  | 56             | 70              | I/O | ST              |                                                |

| RD11     | 45                  | 57             | 71              | I/O | ST              |                                                |

| RD12     | _                   | 64             | 79              | I/O | ST              |                                                |

| RD13     | _                   | 65             | 80              | I/O | ST              |                                                |

| RD14     | _                   | 37             | 47              | I/O | ST              |                                                |

| RD15     | _                   | 38             | 48              | I/O | ST              |                                                |

| RE0      | 60                  | 76             | 93              | I/O | ST              | PORTE Digital I/O.                             |

| RE1      | 61                  | 77             | 94              | I/O | ST              | 1                                              |

| RE2      | 62                  | 78             | 98              | I/O | ST              | 1                                              |

| RE3      | 63                  | 79             | 99              | I/O | ST              | 1                                              |

| RE4      | 64                  | 80             | 100             | I/O | ST              | 1                                              |

| RE5      | 1                   | 1              | 3               | I/O | ST              | 1                                              |

| RE6      | 2                   | 2              | 4               | I/O | ST              | 1                                              |

| RE7      | 3                   | 3              | 5               | I/O | ST              | 1                                              |

| RE8      | _                   | 13             | 18              | I/O | ST              | 1                                              |

| RE9      | _                   | 14             | 19              | I/O | ST              | 1                                              |

| REFO     | 30                  | 36             | 44              | 0   | —               | Reference Clock Output.                        |

| Legend:  | TTL = TTL in        | put buffer     |                 |     | ST = 5          | Schmitt Trigger input buffer                   |

#### **TABLE 1-4:** PIC24FJ256GB110 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Legend: TTL = TTL input buffer ANA = Analog level input/output ST = Schmitt Trigger input buffer

$I^2C^{TM} = I^2C/SMBus$  input buffer

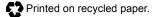

### 2.6 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration**" for details).

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-4. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins and other signals in close proximity to the oscillator are benign (i.e., free of high frequencies, short rise and fall times and other similar noise).

For additional information and design guidance on oscillator circuits, please refer to these Microchip Application Notes, available at the corporate web site (www.microchip.com):

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC™ and PICmicro<sup>®</sup> Devices"

- AN849, "Basic PICmicro<sup>®</sup> Oscillator Design"

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

### FIGURE 2-4: SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

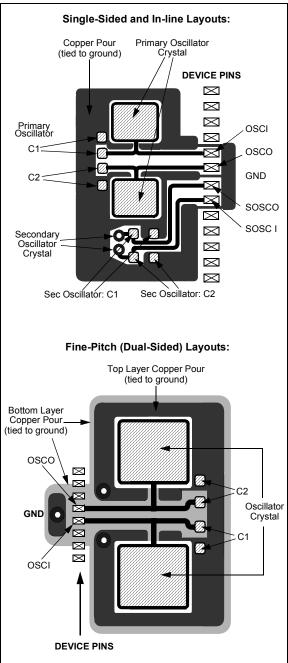

| Register(s) Name | Description                                    |

|------------------|------------------------------------------------|

| W0 through W15   | Working Register Array                         |

| PC               | 23-Bit Program Counter                         |

| SR               | ALU STATUS Register                            |

| SPLIM            | Stack Pointer Limit Value Register             |

| TBLPAG           | Table Memory Page Address Register             |

| PSVPAG           | Program Space Visibility Page Address Register |

| RCOUNT           | Repeat Loop Counter Register                   |

| CORCON           | CPU Control Register                           |

### FIGURE 3-2: PROGRAMMER'S MODEL

### 3.3.2 DIVIDER

The divide block supports signed and unsigned integer divide operations with the following data sizes:

- 1. 32-bit signed/16-bit signed divide

- 2. 32-bit unsigned/16-bit unsigned divide

- 3. 16-bit signed/16-bit signed divide

- 4. 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. Sixteen-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn), and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

### 3.3.3 MULTI-BIT SHIFT SUPPORT

The PIC24F ALU supports both single bit and single-cycle, multi-bit arithmetic and logic shifts. Multi-bit shifts are implemented using a shifter block, capable of performing up to a 15-bit arithmetic right shift, or up to a 15-bit left shift, in a single cycle. All multi-bit shift instructions only support Register Direct Addressing for both the operand source and result destination.

A full summary of instructions that use the shift operation is provided below in Table 3-2.

### TABLE 3-2: INSTRUCTIONS THAT USE THE SINGLE AND MULTI-BIT SHIFT OPERATION

| Instruction | Description                                                 |

|-------------|-------------------------------------------------------------|

| ASR         | Arithmetic shift right source register by one or more bits. |

| SL          | Shift left source register by one or more bits.             |

| LSR         | Logical shift right source register by one or more bits.    |

### TABLE 4-12: PORTA REGISTER MAP<sup>(1)</sup>

| File<br>Name | Addr | Bit 15  | Bit 14  | Bit 13 | Bit 12 | Bit 11 | Bit 10  | Bit 9  | Bit 8 | Bit 7 <sup>(2)</sup> | Bit 6 <sup>(2)</sup> | Bit 5 <sup>(2)</sup> | Bit 4 <sup>(2)</sup> | Bit 3 <sup>(2)</sup> | Bit2 <sup>(2)</sup> | Bit 1 <sup>(2)</sup> | Bit 0 <sup>(2)</sup> | All<br>Resets |

|--------------|------|---------|---------|--------|--------|--------|---------|--------|-------|----------------------|----------------------|----------------------|----------------------|----------------------|---------------------|----------------------|----------------------|---------------|

| TRISA        | 02C0 | TRISA15 | TRISA14 | _      | _      | _      | TRISA10 | TRISA9 | _     | TRISA7               | TRISA6               | TRISA5               | TRISA4               | TRISA3               | TRISA2              | TRISA1               | TRISA0               | 36FF          |

| PORTA        | 02C2 | RA15    | RA14    | -      | _      | —      | RA10    | RA9    | —     | RA7                  | RA6                  | RA5                  | RA4                  | RA3                  | RA2                 | RA1                  | RA0                  | xxxx          |

| LATA         | 02C4 | LATA15  | LATA14  |        | _      | —      | LATA10  | LATA9  | —     | LATA7                | LATA6                | LATA5                | LATA4                | LATA3                | LATA2               | LATA1                | LATA0                | xxxx          |

| ODCA         | 02C6 | ODA15   | ODA14   | _      | _      | _      | ODA10   | ODA9   | _     | ODA7                 | ODA6                 | ODA5                 | ODA4                 | ODA3                 | ODA2                | ODA1                 | ODA0                 | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Reset values shown are for 100-pin devices.

Note 1: PORTA and all associated bits are unimplemented on 64-pin devices and read as '0'. Bits are available on 80-pin and 100-pin devices only, unless otherwise noted.

**2:** Bits are implemented on 100-pin devices only; otherwise read as '0'.

### TABLE 4-13: PORTB REGISTER MAP

| File<br>Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 02C8 | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 02CA | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 02CC | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 02CE | ODB15   | ODB14   | ODB13   | ODB12   | ODB11   | ODB10   | ODB9   | ODB8   | ODB7   | ODB6   | ODB5   | ODB4   | ODB3   | ODB2   | ODB1   | ODB0   | 0000          |

Legend: Reset values are shown in hexadecimal.

#### TABLE 4-14: PORTC REGISTER MAP

| File<br>Name | Addr | Bit 15                | Bit 14  | Bit 13  | Bit 12              | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 <sup>(1)</sup> | Bit 3 <sup>(2)</sup> | Bit 2 <sup>(1)</sup> | Bit 1 <sup>(2)</sup> | Bit 0 | All<br>Resets |

|--------------|------|-----------------------|---------|---------|---------------------|--------|--------|-------|-------|-------|-------|-------|----------------------|----------------------|----------------------|----------------------|-------|---------------|

| TRISC        | 02D0 | TRISC15               | TRISC14 | TRISC13 | TRISC12             | —      | _      | -     | _     | _     | —     | -     | TRISC4               | TRISC3               | TRISC2               | TRISC1               | _     | F01E          |

| PORTC        | 02D2 | RC15 <sup>(3,4)</sup> | RC14    | RC13    | RC12 <sup>(3)</sup> | _      |        | _     | _     | _     | _     | _     | RC4                  | RC3                  | RC2                  | RC1                  | _     | xxxx          |

| LATC         | 02D4 | LATC15                | LATC14  | LATC13  | LATC12              | _      | _      |       | _     | _     | _     |       | LATC4                | LATC3                | LATC2                | LATC1                |       | xxxx          |

| ODCC         | 02D6 | ODC15                 | ODC14   | ODC13   | ODC12               | _      | _      | _     | _     | _     | _     | _     | ODC4                 | ODC3                 | ODC2                 | ODC1                 |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Reset values shown are for 100-pin devices.

Note 1: Bits are unimplemented on 64-pin and 80-pin devices; read as '0'.

2: Bits are unimplemented on 64-pin devices; read as '0'.

3: RC12 and RC15 are only available when the Primary Oscillator is disabled or when EC mode is selected (POSCMD<1:0> Configuration bits = 11 or 00); otherwise read as '0'.

4: RC15 is only available when the POSCMD<1:0> Configuration bits = 11 or 00 and the OSCIOFN Configuration bit = 1.

### TABLE 4-15:PORTD REGISTER MAP

| File<br>Name | Addr | Bit 15 <sup>(1)</sup> | Bit 14 <sup>(1)</sup> | Bit 13 <sup>(1)</sup> | Bit 12 <sup>(1)</sup> | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|------|-----------------------|-----------------------|-----------------------|-----------------------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISD        | 02D8 | TRISD15               | TRISD14               | TRISD13               | TRISD12               | TRISD11 | TRISD10 | TRISD9 | TRISD8 | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 | FFFF          |

| PORTD        | 02DA | RD15                  | RD14                  | RD13                  | RD12                  | RD11    | RD10    | RD9    | RD8    | RD7    | RD6    | RD5    | RD4    | RD3    | RD2    | RD1    | RD0    | xxxx          |

| LATD         | 02DC | LATD15                | LATD14                | LATD13                | LATD12                | LATD11  | LATD10  | LATD9  | LATD8  | LATD7  | LATD6  | LATD5  | LATD4  | LATD3  | LATD2  | LATD1  | LATD0  | xxxx          |

| ODCD         | 02DE | ODD15                 | ODD14                 | ODD13                 | ODD12                 | ODD11   | ODD10   | ODD9   | ODD8   | ODD7   | ODD6   | ODD5   | ODD4   | ODD3   | ODD2   | ODD1   | ODD0   | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Reset values shown are for 100-pin devices.

Note 1: Bits are unimplemented on 64-pin devices; read as '0'.

DS39897C-page 51

|                   | Vector |             | AIVT    | Inte     | errupt Bit Locat | ions         |

|-------------------|--------|-------------|---------|----------|------------------|--------------|

| Interrupt Source  | Number | IVT Address | Address | Flag     | Enable           | Priority     |

| Timer1            | 3      | 00001Ah     | 00011Ah | IFS0<3>  | IEC0<3>          | IPC0<14:12>  |

| Timer2            | 7      | 000022h     | 000122h | IFS0<7>  | IEC0<7>          | IPC1<14:12>  |

| Timer3            | 8      | 000024h     | 000124h | IFS0<8>  | IEC0<8>          | IPC2<2:0>    |

| Timer4            | 27     | 00004Ah     | 00014Ah | IFS1<11> | IEC1<11>         | IPC6<14:12>  |

| Timer5            | 28     | 00004Ch     | 00014Ch | IFS1<12> | IEC1<12>         | IPC7<2:0>    |

| UART1 Error       | 65     | 000096h     | 000196h | IFS4<1>  | IEC4<1>          | IPC16<6:4>   |

| UART1 Receiver    | 11     | 00002Ah     | 00012Ah | IFS0<11> | IEC0<11>         | IPC2<14:12>  |

| UART1 Transmitter | 12     | 00002Ch     | 00012Ch | IFS0<12> | IEC0<12>         | IPC3<2:0>    |

| UART2 Error       | 66     | 000098h     | 000198h | IFS4<2>  | IEC4<2>          | IPC16<10:8>  |

| UART2 Receiver    | 30     | 000050h     | 000150h | IFS1<14> | IEC1<14>         | IPC7<10:8>   |

| UART2 Transmitter | 31     | 000052h     | 000152h | IFS1<15> | IEC1<15>         | IPC7<14:12>  |

| UART3 Error       | 81     | 0000B6h     | 0001B6h | IFS5<1>  | IEC5<1>          | IPC20<6:4>   |

| UART3 Receiver    | 82     | 0000B8h     | 0001B8h | IFS5<2>  | IEC5<2>          | IPC20<10:8>  |

| UART3 Transmitter | 83     | 0000BAh     | 0001BAh | IFS5<3>  | IEC5<3>          | IPC20<14:12> |

| UART4 Error       | 87     | 0000C2h     | 0001C2h | IFS5<7>  | IEC5<7>          | IPC21<14:12> |

| UART4 Receiver    | 88     | 0000C4h     | 0001C4h | IFS5<8>  | IEC5<8>          | IPC22<2:0>   |

| UART4 Transmitter | 89     | 0000C6h     | 0001C6h | IFS5<9>  | IEC5<9>          | IPC22<6:4>   |

| USB Interrupt     | 86     | 0000C0h     | 0001C0h | IFS5<6>  | IEC5<6>          | IPC21<10:8>  |

### TABLE 7-2: IMPLEMENTED INTERRUPT VECTORS (CONTINUED)

### 7.3 Interrupt Control and Status Registers

The PIC24FJ256GB110 family of devices implements a total of 37 registers for the interrupt controller:

- INTCON1

- INTCON2

- IFS0 through IFS5

- IEC0 through IEC5

- IPC0 through IPC23 (except IPC14 and IPC17)

- INTTREG

Global interrupt control functions are controlled from INTCON1 and INTCON2. INTCON1 contains the Interrupt Nesting Disable (NSTDIS) bit, as well as the control and status flags for the processor trap sources. The INTCON2 register controls the external interrupt request signal behavior and the use of the Alternate Interrupt Vector Table.

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit which is set by the respective peripherals, or an external signal, and is cleared via software.

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

The IPCx registers are used to set the interrupt priority level for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels. The INTTREG register contains the associated interrupt vector number and the new CPU interrupt priority level, which are latched into the Vector Number (VECNUM<6:0>) and the Interrupt Level (ILR<3:0>) bit fields in the INTTREG register. The new interrupt priority level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the order of their vector numbers, as shown in Table 7-2. For example, the INT0 (External Interrupt 0) is shown as having a vector number and a natural order priority of 0. Thus, the INT0IF status bit is found in IFS0<0>, the INT0IE enable bit in IEC0<0> and the INT0IP<2:0> priority bits in the first position of IPC0 (IPC0<2:0>).

Although they are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. The ALU STATUS register (SR) contains the IPL<2:0> bits (SR<7:5>). These indicate the current CPU interrupt priority level. The user may change the current CPU priority level by writing to the IPL bits.

The CORCON register contains the IPL3 bit, which together with IPL<2:0>, indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All interrupt registers are described in Register 7-1 through Register 7-39, in the following pages.

| U-0          | U-0                                    | R/W-0                                                                   | R/W-0                  | R/W-0             | R/W-0            | R/W-0           | R/W-0  |

|--------------|----------------------------------------|-------------------------------------------------------------------------|------------------------|-------------------|------------------|-----------------|--------|

|              | —                                      | AD1IE                                                                   | U1TXIE                 | U1RXIE            | SPI1IE           | SPF1IE          | T3IE   |

| bit 15       |                                        |                                                                         |                        |                   |                  |                 | bit 8  |

| R/W-0        | R/W-0                                  | R/W-0                                                                   | U-0                    | R/W-0             | R/W-0            | R/W-0           | R/W-0  |

| T2IE         | OC2IE                                  | IC2IE                                                                   | —                      | T1IE              | OC1IE            | IC1IE           | INT0IE |

| bit 7        |                                        |                                                                         |                        |                   |                  |                 | bit (  |

| Legend:      |                                        |                                                                         |                        |                   |                  |                 |        |

| R = Readab   | le bit                                 | W = Writable                                                            | bit                    | U = Unimplen      | nented bit, read | d as '0'        |        |

| -n = Value a | t POR                                  | '1' = Bit is set                                                        |                        | '0' = Bit is clea | ared             | x = Bit is unkn | own    |

| bit 15-14    | Unimplemen                             | ted: Read as '                                                          | )'                     |                   |                  |                 |        |

| bit 13       | AD1IE: A/D C<br>1 = Interrupt r        | Conversion Con<br>request enable                                        | nplete Interrup<br>d   | t Enable bit      |                  |                 |        |

| bit 12       | <b>U1TXIE:</b> UAF<br>1 = Interrupt r  | request not ena<br>RT1 Transmitter<br>request enable<br>request not ena | · Interrupt Enal       | ble bit           |                  |                 |        |

| bit 11       | <b>U1RXIE:</b> UAF<br>1 = Interrupt r  | RT1 Receiver Ir<br>equest enable<br>equest not ena                      | nterrupt Enable<br>d   | e bit             |                  |                 |        |

| bit 10       | <b>SPI1IE:</b> SPI1<br>1 = Interrupt r | Transfer Comp<br>request enabled<br>request not ena                     | blete Interrupt I<br>d | Enable bit        |                  |                 |        |

| bit 9        | SPF1IE: SPI1<br>1 = Interrupt r        | Fault Interrup<br>equest enable<br>equest not ena                       | t Enable bit<br>d      |                   |                  |                 |        |

| bit 8        | <b>T3IE:</b> Timer3<br>1 = Interrupt r | Interrupt Enable<br>equest enable<br>equest not ena                     | e bit<br>d             |                   |                  |                 |        |

| bit 7        | <b>T2IE:</b> Timer2<br>1 = Interrupt r | Interrupt Enable<br>request enable<br>request not ena                   | e bit<br>d             |                   |                  |                 |        |

| bit 6        | <b>OC2IE:</b> Outpu<br>1 = Interrupt r | ut Compare Ch<br>equest enable<br>equest not ena                        | annel 2 Interru<br>ป   | ipt Enable bit    |                  |                 |        |

| bit 5        | IC2IE: Input C<br>1 = Interrupt r      | Capture Channe<br>request enable<br>request not ena                     | el 2 Interrupt E<br>d  | nable bit         |                  |                 |        |

| bit 4        | -                                      | ted: Read as '                                                          |                        |                   |                  |                 |        |

| bit 3        | <b>T1IE:</b> Timer1<br>1 = Interrupt r | Interrupt Enable<br>request enable<br>request not ena                   | e bit<br>d             |                   |                  |                 |        |

| bit 2        | 1 = Interrupt r                        | ut Compare Ch<br>equest enabled<br>equest not ena                       | b                      | ipt Enable bit    |                  |                 |        |

| bit 1        | 1 = Interrupt r                        | Capture Channe<br>request enable<br>request not ena                     | d .                    | nable bit         |                  |                 |        |

| bit 0        | 1 = Interrupt r                        | nal Interrupt 0<br>equest enable<br>equest not ena                      | b                      |                   |                  |                 |        |

### REGISTER 7-15: IEC4: INTERRUPT ENABLE CONTROL REGISTER 4

| U-0           | U-0           | R/W-0                               | U-0            | U-0               | U-0              | U-0             | R/W-0 |

|---------------|---------------|-------------------------------------|----------------|-------------------|------------------|-----------------|-------|

| _             | —             | CTMUIE                              | _              | —                 | —                | —               | LVDIE |

| bit 15        |               |                                     |                |                   |                  |                 | bit 8 |

|               |               |                                     |                |                   |                  |                 |       |

| U-0           | U-0           | U-0                                 | U-0            | R/W-0             | R/W-0            | R/W-0           | U-0   |

|               |               | —                                   | —              | CRCIE             | U2ERIE           | U1ERIE          |       |

| bit 7         |               |                                     |                |                   |                  |                 | bit C |

|               |               |                                     |                |                   |                  |                 |       |

| Legend:       |               |                                     |                |                   |                  |                 |       |

| R = Readabl   |               | W = Writable b                      | bit            |                   | nented bit, read | d as '0'        |       |

| -n = Value at | t POR         | '1' = Bit is set                    |                | '0' = Bit is clea | ared             | x = Bit is unkn | own   |

|               |               |                                     |                |                   |                  |                 |       |

| bit 15-14     | -             | ted: Read as '0                     |                |                   |                  |                 |       |

| bit 13        |               | MU Interrupt En                     |                |                   |                  |                 |       |

|               |               | request enabled<br>request not enal |                |                   |                  |                 |       |

| bit 12-9      | Unimplemen    | ted: Read as '0                     | ,              |                   |                  |                 |       |

| bit 8         | LVDIE: Low-   | Voltage Detect I                    | nterrupt Enab  | le bit            |                  |                 |       |

|               |               | request enabled<br>request not enal |                |                   |                  |                 |       |

| bit 7-4       |               | ted: Read as '0                     |                |                   |                  |                 |       |

| bit 3         | CRCIE: CRC    | Generator Inter                     | rupt Enable b  | pit               |                  |                 |       |

|               |               | request enabled<br>request not enal |                |                   |                  |                 |       |

| bit 2         | •             | RT2 Error Interru                   |                |                   |                  |                 |       |

|               |               | request enabled                     | •              |                   |                  |                 |       |

|               |               | request not enal                    |                |                   |                  |                 |       |

|               | •             |                                     | unt Enchla hit |                   |                  |                 |       |

| bit 1         | U1ERIE: UA    | RI1 Error Interru                   | ומנ בהמסופ סוו |                   |                  |                 |       |

| bit 1         | 1 = Interrupt | request enabled                     |                |                   |                  |                 |       |

| bit 1         | 1 = Interrupt |                                     |                |                   |                  |                 |       |

| U-0                                | U-0 | R/W-0  | R/W-0                                  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|------------------------------------|-----|--------|----------------------------------------|--------|--------|--------|--------|

| _                                  | —   | RP27R5 | RP27R4                                 | RP27R3 | RP27R2 | RP27R1 | RP27R0 |

| bit 15                             |     |        |                                        |        |        |        | bit 8  |

|                                    |     |        |                                        |        |        |        |        |

| U-0                                | U-0 | R/W-0  | R/W-0                                  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| —                                  | —   | RP26R5 | RP26R4                                 | RP26R3 | RP26R2 | RP26R1 | RP26R0 |

| bit 7                              |     |        |                                        |        |        |        | bit 0  |

|                                    |     |        |                                        |        |        |        |        |

| Legend:                            |     |        |                                        |        |        |        |        |

| R = Readable bit W = Writable bit  |     |        | U = Unimplemented bit, read as '0'     |        |        |        |        |

| -n = Value at POR '1' = Bit is set |     |        | '0' = Bit is cleared x = Bit is unknow |        |        | iown   |        |

### REGISTER 10-35: RPOR13: PERIPHERAL PIN SELECT OUTPUT REGISTER 13

bit 15-14 Unimplemented: Read as '0'

- bit 13-8

RP27R<5:0>: RP27 Output Pin Mapping bits

Peripheral output number n is assigned to pin, RP27 (see Table 10-3 for peripheral function numbers)

bit 7-6

Unimplemented: Read as '0'

- bit 5-0 **RP26R<5:0>:** RP26 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP26 (see Table 10-3 for peripheral function numbers)

### REGISTER 10-36: RPOR14: PERIPHERAL PIN SELECT OUTPUT REGISTER 14

| U-0                               | U-0 | R/W-0  | R/W-0                              | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-----------------------------------|-----|--------|------------------------------------|--------|--------|--------|--------|

| _                                 | _   | RP29R5 | RP29R4                             | RP29R3 | RP29R2 | RP29R1 | RP29R0 |

| bit 15                            |     |        |                                    |        |        |        | bit 8  |

|                                   |     |        |                                    |        |        |        |        |

| U-0                               | U-0 | R/W-0  | R/W-0                              | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| —                                 | _   | RP28R5 | RP28R4                             | RP28R3 | RP28R2 | RP28R1 | RP28R0 |

| bit 7                             |     |        |                                    |        |        |        | bit 0  |

|                                   |     |        |                                    |        |        |        |        |

| Legend:                           |     |        |                                    |        |        |        |        |

| R = Readable bit W = Writable bit |     |        | U = Unimplemented bit, read as '0' |        |        |        |        |

|                                   |     |        |                                    |        |        |        |        |

'0' = Bit is cleared

bit 15-14 Unimplemented: Read as '0'

'1' = Bit is set

bit 13-8 **RP29R<5:0>:** RP29 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP29 (see Table 10-3 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP28R<5:0>:** RP28 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP28 (see Table 10-3 for peripheral function numbers)

-n = Value at POR

x = Bit is unknown

For 32-bit cascaded operation, these steps are also necessary:

- Set the OC32 bits for both registers (OCyCON2<8> and (OCxCON2<8>). Enable the even numbered module first to ensure the modules will start functioning in unison.

- Clear the OCTRIG bit of the even module (OCyCON2), so the module will run in Synchronous mode.

- 3. Configure the desired output and Fault settings for OCy.

- 4. Force the output pin for OCx to the output state by clearing the OCTRIS bit.

- If Trigger mode operation is required, configure the trigger options in OCx by using the OCTRIG (OCxCON2<7>), TRIGSTAT (OCxCON2<6>), and SYNCSEL (OCxCON2<4:0>) bits.

- Configure the desired compare or PWM mode of operation (OCM<2:0>) for OCy first, then for OCx.

Depending on the output mode selected, the module holds the OCx pin in its default state, and forces a transition to the opposite state when OCxR matches the timer. In Double Compare modes, OCx is forced back to its default state when a match with OCxRS occurs. The OCxIF interrupt flag is set after an OCxR match in Single Compare modes, and after each OCxRS match in Double Compare modes.

Single-shot pulse events only occur once, but may be repeated by simply rewriting the value of the OCxCON1 register. Continuous pulse events continue indefinitely until terminated.

### 14.3 Pulse-Width Modulation (PWM) Mode

In PWM mode, the output compare module can be configured for edge-aligned or center-aligned pulse waveform generation. All PWM operations are double-buffered (buffer registers are internal to the module and are not mapped into SFR space).

To configure the output compare module for PWM operation:

- 1. Configure the OCx output for one of the available Peripheral Pin Select pins.

- 2. Calculate the desired duty cycles and load them into the OCxR register.

- 3. Calculate the desired period and load it into the OCxRS register.

- Select the current OCx as the sync source by writing 0x1F to SYNCSEL<4:0> (OCxCON2<4:0>), and clearing OCTRIG (OCxCON2<7>).

- 5. Select a clock source by writing the OCTSEL<2:0> (OCxCON<12:10>) bits.

- 6. Enable interrupts, if required, for the timer and output compare modules. The output compare interrupt is required for PWM Fault pin utilization.

- 7. Select the desired PWM mode in the OCM<2:0> (OCxCON1<2:0>) bits.

- If a timer is selected as a clock source, set the TMRy prescale value and enable the time base by setting the TON (TxCON<15>) bit.

- Note: This peripheral contains input and output functions that may need to be configured by the Peripheral Pin Select. See Section 10.4 "Peripheral Pin Select" for more information.

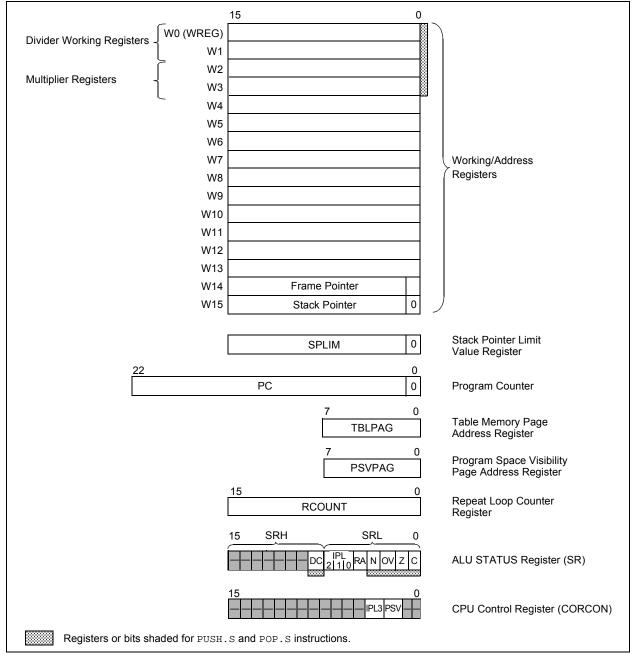

### 16.2 Setting Baud Rate When Operating as a Bus Master

To compute the Baud Rate Generator reload value, use Equation 16-1.

### EQUATION 16-1: COMPUTING BAUD RATE RELOAD VALUE<sup>(1,2)</sup>

- **Note 1:** Based on Fcy = Fosc/2; Doze mode and PLL are disabled.

- 2: These clock rate values are for guidance only. The actual clock rate can be affected by various system level parameters. The actual clock rate should be measured in its intended application.

### TABLE 16-1: I<sup>2</sup>C<sup>™</sup> CLOCK RATES<sup>(1,2)</sup>

### 16.3 Slave Address Masking

The I2CxMSK register (Register 16-3) designates address bit positions as "don't care" for both 7-Bit and 10-Bit Addressing modes. Setting a particular bit location (= 1) in the I2CxMSK register causes the slave module to respond whether the corresponding address bit value is a '0' or a '1'. For example, when I2CxMSK is set to '00100000', the slave module will detect both addresses, '0000000' and '0100000'.

To enable address masking, the IPMI (Intelligent Peripheral Management Interface) must be disabled by clearing the IPMIEN bit (I2CxCON<11>).

Note: As a result of changes in the I<sup>2</sup>C<sup>™</sup> protocol, the addresses in Table 16-2 are reserved and will not be Acknowledged in Slave mode. This includes any address mask settings that include any of these addresses.

| Demained Queters Fact | Fair   | I2CxB     |               |             |

|-----------------------|--------|-----------|---------------|-------------|

| Required System FscL  | Fcy    | (Decimal) | (Hexadecimal) | Actual FSCL |

| 100 kHz               | 16 MHz | 157       | 9D            | 100 kHz     |

| 100 kHz               | 8 MHz  | 78        | 4E            | 100 kHz     |

| 100 kHz               | 4 MHz  | 39        | 27            | 99 kHz      |

| 400 kHz               | 16 MHz | 37        | 25            | 404 kHz     |

| 400 kHz               | 8 MHz  | 18        | 12            | 404 kHz     |

| 400 kHz               | 4 MHz  | 9         | 9             | 385 kHz     |

| 400 kHz               | 2 MHz  | 4         | 4             | 385 kHz     |

| 1 MHz                 | 16 MHz | 13        | D             | 1.026 MHz   |

| 1 MHz                 | 8 MHz  | 6         | 6             | 1.026 MHz   |

| 1 MHz                 | 4 MHz  | 3         | 3             | 0.909 MHz   |

Note 1: Based on FCY = FOSC/2, Doze mode and PLL are disabled.

2: These clock rate values are for guidance only. The actual clock rate can be affected by various system level parameters. The actual clock rate should be measured in its intended application.

TABLE 16-2: I<sup>2</sup>C<sup>™</sup> RESERVED ADDRESSES<sup>(1)</sup>

| Slave Address | R/W Bit | Description                            |

|---------------|---------|----------------------------------------|

| 0000 0000     | 0       | General Call Address <sup>(2)</sup>    |

| 0000 0000     | 1       | Start Byte                             |

| 0000 001      | x       | Cbus Address                           |

| 0000 010      | х       | Reserved                               |

| 0000 011      | х       | Reserved                               |

| 0000 1xx      | x       | HS Mode Master Code                    |

| 1111 1xx      | х       | Reserved                               |

| 1111 Oxx      | x       | 10-Bit Slave Upper Byte <sup>(3)</sup> |

Note 1: The address bits listed here will never cause an address match, independent of address mask settings.

- 2: Address will be Acknowledged only if GCEN = 1.

- 3: Match on this address can only occur on the upper byte in 10-Bit Addressing mode.

### REGISTER 17-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 4   | RXINV: Receive Polarity Inversion bit<br>1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                             |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                               |

|         | <ul><li>1 = High-Speed mode (baud clock generated from FcY/4)</li><li>0 = Standard mode (baud clock generated from FcY/16)</li></ul>                          |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                    |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul> |

| bit 0   | STSEL: Stop Bit Selection bit                                                                                                                                 |

|         | 1 = Two Stop bits<br>0 = One Stop bit                                                                                                                         |

- **Note 1:** If UARTEN = 1, the peripheral inputs and outputs must be configured to an available RPn pin. See **Section 10.4 "Peripheral Pin Select"** for more information.

- **2:** This feature is only available for the 16x BRG mode (BRGH = 0).

| U-0          | U-0                                                                                                                                              | U-0                                                                                                                                    | U-0             | U-0                 | U-0             | U-0             | U-0      |  |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------|-----------------|-----------------|----------|--|--|--|--|

| —            | —                                                                                                                                                | —                                                                                                                                      | —               | —                   | —               | —               |          |  |  |  |  |

| bit 15       |                                                                                                                                                  |                                                                                                                                        |                 |                     |                 |                 | bit      |  |  |  |  |

| R-x, HSC     | R-x, HSC                                                                                                                                         | R/W-0                                                                                                                                  | R/W-0           | R/W-0               | R/W-0           | R/W-0           | R/W-0    |  |  |  |  |

| JSTATE       | SE0                                                                                                                                              | TOKBUSY                                                                                                                                | USBRST          | HOSTEN              | RESUME          | PPBRST          | SOFEN    |  |  |  |  |

| bit 7        | 320                                                                                                                                              | TURBUST                                                                                                                                | USDROI          | HUSTEN              | RESUME          | FFDROI          | bit      |  |  |  |  |

|              |                                                                                                                                                  |                                                                                                                                        |                 |                     |                 |                 |          |  |  |  |  |

| Legend:      |                                                                                                                                                  | U = Unimplem                                                                                                                           | ented bit, read | d as '0'            |                 |                 |          |  |  |  |  |

| R = Readab   | ole bit                                                                                                                                          | W = Writable t                                                                                                                         | bit             | HSC = Hardw         | are Settable/C  | learable bit    |          |  |  |  |  |

| -n = Value a | it POR                                                                                                                                           | '1' = Bit is set                                                                                                                       |                 | '0' = Bit is clea   | ared            | x = Bit is unkn | iown     |  |  |  |  |

|              |                                                                                                                                                  |                                                                                                                                        |                 |                     |                 |                 |          |  |  |  |  |

| bit 15-8     | -                                                                                                                                                | ited: Read as '0                                                                                                                       |                 |                     |                 |                 |          |  |  |  |  |

| bit 7        |                                                                                                                                                  | e Differential Re                                                                                                                      |                 | •                   |                 |                 | <b>D</b> |  |  |  |  |

|              | 1 = J state (0<br>0 = No J stat                                                                                                                  | differential '0' in te detected                                                                                                        | low speed, dif  | terential '1' in fi | ull speed) dete | cted on the US  | В        |  |  |  |  |

| oit 6        | SE0: Live Single-Ended Zero Flag bit                                                                                                             |                                                                                                                                        |                 |                     |                 |                 |          |  |  |  |  |

|              | 1 = Single-ended zero active on the USB bus                                                                                                      |                                                                                                                                        |                 |                     |                 |                 |          |  |  |  |  |

|              | 0 = No single-ended zero detected                                                                                                                |                                                                                                                                        |                 |                     |                 |                 |          |  |  |  |  |

| bit 5        |                                                                                                                                                  | TOKBUSY: Token Busy Status bit                                                                                                         |                 |                     |                 |                 |          |  |  |  |  |

|              | <ul> <li>1 = Token being executed by the USB module in On-The-Go state</li> <li>0 = No token being executed</li> </ul>                           |                                                                                                                                        |                 |                     |                 |                 |          |  |  |  |  |

| bit 4        |                                                                                                                                                  | •                                                                                                                                      | •               |                     |                 |                 |          |  |  |  |  |

|              |                                                                                                                                                  | <b>USBRST:</b> Module Reset bit<br>1 = USB Reset has been generated; for software Reset, application must set this bit for 50 ms, then |                 |                     |                 |                 |          |  |  |  |  |

|              | clear it                                                                                                                                         |                                                                                                                                        |                 |                     |                 |                 |          |  |  |  |  |

|              | 0 = USB Reset terminated                                                                                                                         |                                                                                                                                        |                 |                     |                 |                 |          |  |  |  |  |

| bit 3        |                                                                                                                                                  | HOSTEN: Host Mode Enable bit                                                                                                           |                 |                     |                 |                 |          |  |  |  |  |

|              | <ul> <li>1 = USB host capability enabled; pull-downs on D+ and D- are activated in hardware</li> <li>0 = USB host capability disabled</li> </ul> |                                                                                                                                        |                 |                     |                 |                 |          |  |  |  |  |

| bit 2        |                                                                                                                                                  | RESUME: Resume Signaling Enable bit                                                                                                    |                 |                     |                 |                 |          |  |  |  |  |

|              |                                                                                                                                                  | 1 = Resume signaling activated; software must set bit for 10 ms and then clear to enable remote wake-up                                |                 |                     |                 |                 |          |  |  |  |  |

|              | 0 = Resume signaling disabled                                                                                                                    |                                                                                                                                        |                 |                     |                 |                 |          |  |  |  |  |

| bit 1        |                                                                                                                                                  | PPBRST: Ping-Pong Buffers Reset bit                                                                                                    |                 |                     |                 |                 |          |  |  |  |  |

|              |                                                                                                                                                  | Il Ping-Pong But<br>ng Buffer Pointe                                                                                                   |                 | the EVEN BD         | banks           |                 |          |  |  |  |  |

|              |                                                                                                                                                  |                                                                                                                                        |                 |                     |                 |                 |          |  |  |  |  |

| bit 0        |                                                                                                                                                  |                                                                                                                                        |                 |                     |                 |                 |          |  |  |  |  |

| bit 0        | SOFEN: Star                                                                                                                                      | t-Of-Frame Ena<br>Frame token se                                                                                                       | ble bit         | millisecond         |                 |                 |          |  |  |  |  |

| U-0                   | U-0                                                                                                                                                                         | U-0                 | U-0     | U-0               | U-0            | U-0             | U-0   |  |  |  |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------|-------------------|----------------|-----------------|-------|--|--|--|

| _                     | —                                                                                                                                                                           | _                   | —       | —                 | _              | —               | —     |  |  |  |

| bit 15                |                                                                                                                                                                             |                     |         |                   |                |                 | bit 8 |  |  |  |

|                       |                                                                                                                                                                             |                     |         |                   |                |                 |       |  |  |  |

| R/W-0                 | R/W-0                                                                                                                                                                       | R/W-0               | R/W-0   | R/W-0             | R/W-0          | R/W-0           | R/W-0 |  |  |  |

| CVREN                 | CVROE                                                                                                                                                                       | CVRR                | CVRSS   | CVR3              | CVR2           | CVR1            | CVR0  |  |  |  |

| bit 7                 |                                                                                                                                                                             |                     |         |                   |                |                 | bit ( |  |  |  |

|                       |                                                                                                                                                                             |                     |         |                   |                |                 |       |  |  |  |

| Legend:<br>R = Readab | lo hit                                                                                                                                                                      | W = Writable        | hit     | II – Unimplom     | onted hit read | d ac 'O'        |       |  |  |  |

|                       |                                                                                                                                                                             |                     |         | U = Unimplem      |                |                 |       |  |  |  |

| -n = Value a          | IT POR                                                                                                                                                                      | '1' = Bit is set    |         | '0' = Bit is clea | ared           | x = Bit is unkn | IOWN  |  |  |  |

| bit 15-8              | Unimplemen                                                                                                                                                                  | ted: Read as '      | 0'      |                   |                |                 |       |  |  |  |

| bit 7                 | CVREN: Comparator Voltage Reference Enable bit                                                                                                                              |                     |         |                   |                |                 |       |  |  |  |

|                       | 1 = CVREF circuit powered on                                                                                                                                                |                     |         |                   |                |                 |       |  |  |  |

|                       | 0 = CVREF circuit powered down                                                                                                                                              |                     |         |                   |                |                 |       |  |  |  |

| bit 6                 | CVROE: Comparator VREF Output Enable bit                                                                                                                                    |                     |         |                   |                |                 |       |  |  |  |

|                       | 1 = CVREF voltage level is output on CVREF pin                                                                                                                              |                     |         |                   |                |                 |       |  |  |  |

|                       | 0 = CVREF voltage level is disconnected from CVREF pin                                                                                                                      |                     |         |                   |                |                 |       |  |  |  |

| bit 5                 | CVRR: Comparator VREF Range Selection bit                                                                                                                                   |                     |         |                   |                |                 |       |  |  |  |

|                       | <ul> <li>1 = CVRSRC range should be 0 to 0.625 CVRSRC with CVRSRC/24 step size</li> <li>0 = CVRSRC range should be 0.25 to 0.719 CVRSRC with CVRSRC/32 step size</li> </ul> |                     |         |                   |                |                 |       |  |  |  |

|                       |                                                                                                                                                                             | •                   |         |                   | JVRSRC/32 ste  | p size          |       |  |  |  |

| bit 4                 | CVRSS: Comparator VREF Source Selection bit                                                                                                                                 |                     |         |                   |                |                 |       |  |  |  |

|                       | <ul> <li>1 = Comparator reference source CVRSRC = VREF+ – VREF-</li> <li>0 = Comparator reference source CVRSRC = AVDD – AVSS</li> </ul>                                    |                     |         |                   |                |                 |       |  |  |  |

| bit 3-0               | <b>CVR&lt;3:0&gt;:</b> Comparator VREF Value Selection $0 \le \text{CVR3:CVR0} \le 15$ bits                                                                                 |                     |         |                   |                |                 |       |  |  |  |

|                       | When $CVRR = 1$ :                                                                                                                                                           |                     |         |                   |                |                 |       |  |  |  |

|                       |                                                                                                                                                                             | <br>R<3:0>/24) ● (0 | CVRSRC) |                   |                |                 |       |  |  |  |

|                       | When CVRR                                                                                                                                                                   |                     | -       |                   |                |                 |       |  |  |  |

|                       | CVREF = 1/4                                                                                                                                                                 |                     |         |                   |                |                 |       |  |  |  |

### REGISTER 24-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

### REGISTER 26-2: CW2: FLASH CONFIGURATION WORD 2 (CONTINUED)

- bit 4 **IOL1WAY:** IOLOCK One-Way Set Enable bit

- 1 = The IOLOCK bit (OSCCON<6>)can be set once, provided the unlock sequence has been completed. Once set, the Peripheral Pin Select registers cannot be written to a second time.

- 0 = The IOLOCK bit can be set and cleared as needed, provided the unlock sequence has been completed

bit 3 DISUVREG: Internal USB 3.3V Regulator Disable bit

- 1 = Regulator is disabled

- 0 = Regulator is enabled

- bit 2 Reserved: Always maintain as '1'

- bit 1-0 **POSCMD<1:0>:** Primary Oscillator Configuration bits

- 11 = Primary Oscillator disabled

- 10 = HS Oscillator mode selected

- 01 = XT Oscillator mode selected

- 00 = EC Oscillator mode selected

### REGISTER 26-3: CW3: FLASH CONFIGURATION WORD 3

| U-1            | U-1                             | U-1                     | U-1                       | U-1                                | U-1                     | U-1                     | U-1           |  |  |  |

|----------------|---------------------------------|-------------------------|---------------------------|------------------------------------|-------------------------|-------------------------|---------------|--|--|--|

| —              | —                               | —                       | —                         | —                                  | —                       | —                       | —             |  |  |  |

| bit 23         |                                 |                         |                           |                                    |                         |                         | bit 16        |  |  |  |

|                |                                 |                         |                           |                                    |                         |                         |               |  |  |  |

| R/PO-1         | R/PO-1                          | R/PO-1                  | U-1                       | U-1                                | U-1                     | U-1                     | U-1           |  |  |  |

| WPEND          | WPCFG                           | WPCFG WPDIS             |                           |                                    |                         |                         |               |  |  |  |

| bit 15         |                                 |                         |                           |                                    |                         |                         | bit 8         |  |  |  |

|                | D (D 0 4                        | <b>D</b> / <b>D</b> 0_1 | <b>D</b> ( <b>D</b> 0, 4) | <b>D</b> / <b>D</b> 0_4            | <b>D</b> / <b>D</b> 0_4 | <b>D</b> / <b>D</b> 0_1 |               |  |  |  |

| R/PO-1         | R/PO-1                          | R/PO-1                  | R/PO-1                    | R/PO-1                             | R/PO-1                  | R/PO-1                  | R/PO-1        |  |  |  |