Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB OTG                                      |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                      |

| Number of I/O              | 51                                                                              |

| Program Memory Size        | 192KB (65.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

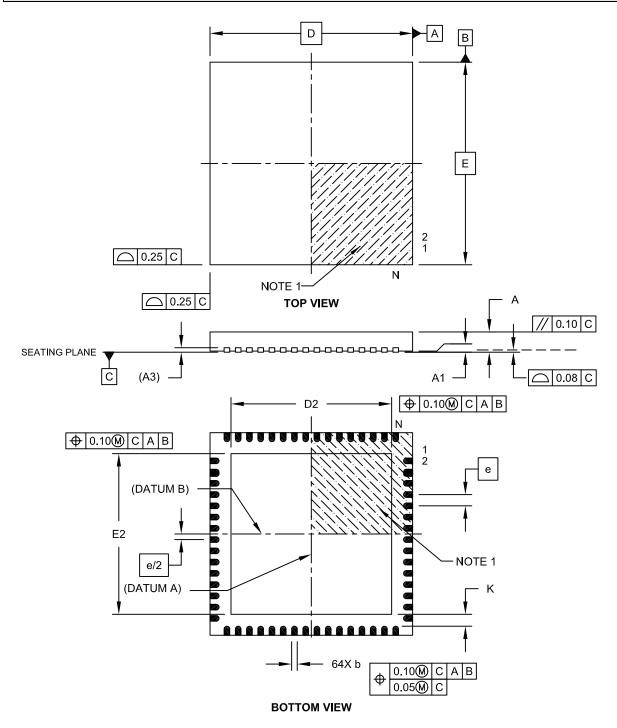

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj192gb106t-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.2 USB On-The-Go

With the PIC24FJ256GB110 family of devices, Microchip introduces USB On-The-Go functionality on a single chip to its product line. This new module provides on-chip functionality as a target device compatible with the USB 2.0 standard, as well as limited stand-alone functionality as a USB embedded host. By implementing USB Host Negotiation Protocol (HNP), the module can also dynamically switch between device and host operation, allowing for a much wider range of versatile USB-enabled applications on a microcontroller platform.

In addition to USB host functionality, PIC24FJ256GB110 family devices provide a true single-chip USB solution, including an on-chip transceiver and voltage regulator, and a voltage boost generator for sourcing bus power during host operations.

### 1.3 Other Special Features

- Peripheral Pin Select: The Peripheral Pin Select (PPS) feature allows most digital peripherals to be mapped over a fixed set of digital I/O pins. Users may independently map the input and/or output of any one of the many digital peripherals to any one of the I/O pins.

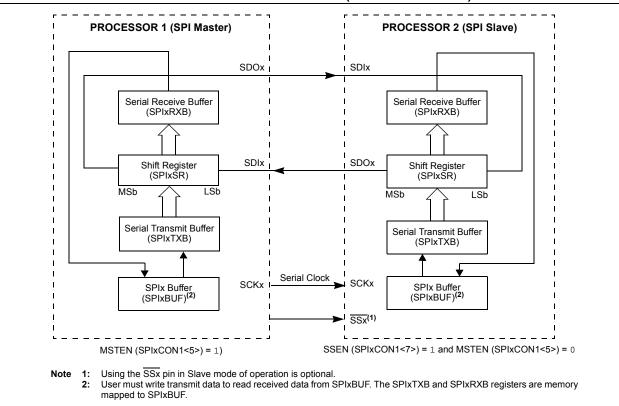

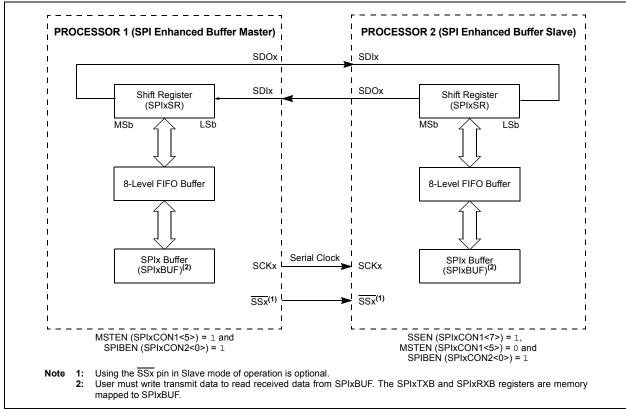

- **Communications:** The PIC24FJ256GB110 family incorporates a range of serial communication peripherals to handle a range of application requirements. There are three independent I<sup>2</sup>C modules that support both Master and Slave modes of operation. Devices also have, through the Peripheral Pin Select feature, four independent UARTs with built-in IrDA encoder/decoders and three SPI modules.

- Analog Features: All members of the PIC24FJ256GB110 family include a 10-bit A/D Converter module and a triple comparator module. The A/D module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period, as well as faster sampling speeds. The comparator module includes three analog comparators that are configurable for a wide range of operations.

- **CTMU Interface:** In addition to their other analog features, members of the PIC24FJ256GB110 family include the brand new CTMU interface module. This provides a convenient method for precision time measurement and pulse generation, and can serve as an interface for capacitive sensors.

- Parallel Master/Enhanced Parallel Slave Port: One of the general purpose I/O ports can be reconfigured for enhanced parallel data communications. In this mode, the port can be configured for both master and slave operations, and supports 8-bit and 16-bit data transfers with up to 16 external address lines in Master modes.

- Real-Time Clock/Calendar: This module implements a full-featured clock and calendar with alarm functions in hardware, freeing up timer resources and program memory space for use of the core application.

### 1.4 Details on Individual Family Members

Devices in the PIC24FJ256GB110 family are available in 64-pin, 80-pin and 100-pin packages. The general block diagram for all devices is shown in Figure 1-1.

The devices are differentiated from each other in four ways:

- Flash program memory (64 Kbytes for PIC24FJ64GB1 devices, 128 Kbytes for PIC24FJ128GB1 devices, 192 Kbytes for PIC24FJ192GB1 devices and 256 Kbytes for PIC24FJ256GB1 devices).

- Available I/O pins and ports (51 pins on 6 ports for 64-pin devices, 65 pins on 7 ports for 80-pin devices and 83 pins on 7 ports for 100-pin devices).

- 3. Available Interrupt-on-Change Notification (ICN) inputs (49 on 64-pin devices, 63 on 80-pin devices and 81 on 100-pin devices).

- 4. Available remappable pins (29 pins on 64-pin devices, 40 pins on 80-pin devices and 44 pins on 100-pin devices)

All other features for devices in this family are identical. These are summarized in Table 1-1.

A list of the pin features available on the PIC24FJ256GB110 family devices, sorted by function, is shown in Table 1-4. Note that this table shows the pin location of individual peripheral features and not how they are multiplexed on the same pin. This information is provided in the pinout diagrams in the beginning of the data sheet. Multiplexed features are sorted by the priority given to a feature, with the highest priority peripheral being listed first.

|          |                     | Pin Number     |                 | I/O |                 |                                                                                            |

|----------|---------------------|----------------|-----------------|-----|-----------------|--------------------------------------------------------------------------------------------|

| Function | 64-Pin<br>TQFP, QFN | 80-Pin<br>TQFP | 100-Pin<br>TQFP | I/O | Input<br>Buffer | Description                                                                                |

| D+       | 37                  | 47             | 57              | I/O | —               | USB Differential Plus line (internal transceiver).                                         |

| D-       | 36                  | 46             | 56              | I/O | _               | USB Differential Minus line (internal transceiver).                                        |

| DMH      | 46                  | 58             | 72              | 0   | _               | D- External Pull-up Control Output.                                                        |

| DMLN     | 42                  | 54             | 68              | 0   | _               | D- External Pull-down Control Output.                                                      |

| DPH      | 50                  | 62             | 77              | 0   | _               | D+ External Pull-up Control Output.                                                        |

| DPLN     | 43                  | 55             | 69              | 0   | _               | D+ External Pull-down Control Output.                                                      |

| ENVREG   | 57                  | 71             | 86              | I   | ST              | Voltage Regulator Enable.                                                                  |

| INT0     | 46                  | 58             | 72              | I   | ST              | External Interrupt Input.                                                                  |

| MCLR     | 7                   | 9              | 13              | I   | ST              | Master Clear (device Reset) Input. This line is brought low to cause a Reset.              |

| OSCI     | 39                  | 49             | 63              | I   | ANA             | Main Oscillator Input Connection.                                                          |

| OSCO     | 40                  | 50             | 64              | 0   | ANA             | Main Oscillator Output Connection.                                                         |

| PGEC1    | 15                  | 19             | 24              | I/O | ST              | In-Circuit Debugger/Emulator/ICSP™ Programming Clock.                                      |

| PGED1    | 16                  | 20             | 25              | I/O | ST              | In-Circuit Debugger/Emulator/ICSP Programming Data.                                        |

| PGEC2    | 17                  | 21             | 26              | I/O | ST              | In-Circuit Debugger/Emulator/ICSP Programming Clock.                                       |

| PGED2    | 18                  | 22             | 27              | I/O | ST              | In-Circuit Debugger/Emulator/ICSP Programming Data.                                        |

| PGEC3    | 11                  | 15             | 20              | I/O | ST              | In-Circuit Debugger/Emulator/ICSP Programming Clock.                                       |

| PGED3    | 12                  | 16             | 21              | I/O | ST              | In-Circuit Debugger/Emulator/ICSP Programming Data.                                        |

| PMA0     | 30                  | 36             | 44              | I/O | ST              | Parallel Master Port Address Bit 0 Input (Buffered Slave modes) and Output (Master modes). |

| PMA1     | 29                  | 35             | 43              | I/O | ST              | Parallel Master Port Address Bit 1 Input (Buffered Slave modes) and Output (Master modes). |

| PMA2     | 8                   | 10             | 14              | 0   | —               | Parallel Master Port Address (Demultiplexed Master                                         |

| PMA3     | 6                   | 8              | 12              | 0   | —               | modes).                                                                                    |

| PMA4     | 5                   | 7              | 11              | 0   | —               |                                                                                            |

| PMA5     | 4                   | 6              | 10              | 0   | —               |                                                                                            |

| PMA6     | 16                  | 24             | 29              | 0   | —               |                                                                                            |

| PMA7     | 22                  | 23             | 28              | 0   | —               |                                                                                            |

| PMA8     | 32                  | 40             | 50              | 0   | —               |                                                                                            |

| PMA9     | 31                  | 39             | 49              | 0   | —               |                                                                                            |

| PMA10    | 28                  | 34             | 42              | 0   | —               |                                                                                            |

| PMA11    | 27                  | 33             | 41              | 0   | —               |                                                                                            |

| PMA12    | 24                  | 30             | 35              | 0   | —               |                                                                                            |

| PMA13    | 23                  | 29             | 34              | 0   | - 1             |                                                                                            |

| PMCS1    | 45                  | 57             | 71              | I/O | ST/TTL          | Parallel Master Port Chip Select 1 Strobe/Address Bit 15.                                  |

| PMCS2    | 44                  | 56             | 70              | 0   | ST              | Parallel Master Port Chip Select 2 Strobe/Address Bit 14.                                  |

| PMBE     | 51                  | 63             | 78              | 0   | —               | Parallel Master Port Byte Enable Strobe.                                                   |

| Leaend:  | TTL = TTL in        | and handfam    |                 |     |                 | Schmitt Trigger input buffer                                                               |

### TABLE 1-4: PIC24FJ256GB110 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Legend: TTL = TTL input buffer ANA = Analog level input/output ST = Schmitt Trigger input buffer  $I^2C^{TM} = I^2C/SMBus$  input buffer

NOTES:

| TABLE 4-20: ADC REGISTER MAP |

|------------------------------|

|------------------------------|

|           | -0.      |            |                      |                |              |               |             |           | 1          |            |       |       |        |        |        |        |        | r             |

|-----------|----------|------------|----------------------|----------------|--------------|---------------|-------------|-----------|------------|------------|-------|-------|--------|--------|--------|--------|--------|---------------|

| File Name | Addr     | Bit 15     | Bit 14               | Bit 13         | Bit 12       | Bit 11        | Bit 10      | Bit 9     | Bit 8      | Bit 7      | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| ADC1BUF0  | 0300     |            |                      |                |              |               |             |           | ADC Dat    | a Buffer 0 |       |       |        |        |        |        |        | xxxx          |

| ADC1BUF1  | 0302     |            |                      |                |              |               |             |           | ADC Dat    | a Buffer 1 |       |       |        |        |        |        |        | xxxx          |

| ADC1BUF2  | 0304     |            |                      |                |              |               |             |           | ADC Dat    | a Buffer 2 |       |       |        |        |        |        |        | xxxx          |

| ADC1BUF3  | 0306     |            |                      |                |              |               |             |           | ADC Dat    | a Buffer 3 |       |       |        |        |        |        |        | xxxx          |

| ADC1BUF4  | 0308     |            |                      |                |              |               |             |           | ADC Dat    | a Buffer 4 |       |       |        |        |        |        |        | xxxx          |

| ADC1BUF5  | 030A     |            |                      |                |              |               |             |           | ADC Dat    | a Buffer 5 |       |       |        |        |        |        |        | xxxx          |

| ADC1BUF6  | 030C     |            |                      |                |              |               |             |           |            |            |       |       |        |        | xxxx   |        |        |               |

| ADC1BUF7  | 030E     |            | ADC Data Buffer 7 xx |                |              |               |             |           |            |            |       |       |        |        | xxxx   |        |        |               |

| ADC1BUF8  | 0310     |            | ADC Data Buffer 8 x  |                |              |               |             |           |            |            |       |       |        | xxxx   |        |        |        |               |

| ADC1BUF9  | 0312     |            | ADC Data Buffer 9    |                |              |               |             |           |            |            |       |       |        | xxxx   |        |        |        |               |

| ADC1BUFA  | 0314     |            | ADC Data Buffer 10   |                |              |               |             |           |            |            |       |       |        | xxxx   |        |        |        |               |

| ADC1BUFB  | 0316     |            |                      |                |              |               |             |           | ADC Data   | Buffer 11  |       |       |        |        |        |        |        | xxxx          |

| ADC1BUFC  | 0318     |            |                      |                |              |               |             |           | ADC Data   | Buffer 12  |       |       |        |        |        |        |        | xxxx          |

| ADC1BUFD  | 031A     |            |                      |                |              |               |             |           | ADC Data   | Buffer 13  |       |       |        |        |        |        |        | xxxx          |

| ADC1BUFE  | 031C     |            |                      |                |              |               |             |           | ADC Data   | Buffer 14  |       |       |        |        |        |        |        | xxxx          |

| ADC1BUFF  | 031E     |            |                      |                |              |               |             |           | ADC Data   | Buffer 15  |       |       |        |        |        |        |        | xxxx          |

| AD1CON1   | 0320     | ADON       | _                    | ADSIDL         | _            | —             | _           | FORM1     | FORM0      | SSRC2      | SSRC1 | SSRC0 | —      | —      | ASAM   | SAMP   | DONE   | 0000          |

| AD1CON2   | 0322     | VCFG2      | VCFG1                | VCFG0          | r            | —             | CSCNA       | —         | —          | BUFS       | _     | SMPI3 | SMPI2  | SMPI1  | SMPI0  | BUFM   | ALTS   | 0000          |

| AD1CON3   | 0324     | ADRC       | r                    | r              | SAMC4        | SAMC3         | SAMC2       | SAMC1     | SAMC0      | ADCS7      | ADCS6 | ADCS5 | ADCS4  | ADCS3  | ADCS2  | ADCS1  | ADCS0  | 0000          |

| AD1CHS    | 0328     | CH0NB      | _                    | —              | CH0SB4       | CH0SB3        | CH0SB2      | CH0SB1    | CH0SB0     | CH0NA      | _     | _     | CH0SA4 | CH0SA3 | CH0SA2 | CH0SA1 | CH0SA0 | 0000          |

| AD1PCFGH  | 032A     | —          | _                    | —              | —            | —             | —           | —         | —          | —          | _     | _     | —      | —      | —      | PCFG17 | PCFG16 | 0000          |

| AD1PCFGL  | 032C     | PCFG15     | PCFG14               | PCFG13         | PCFG12       | PCFG11        | PCFG10      | PCFG9     | PCFG8      | PCFG7      | PCFG6 | PCFG5 | PCFG4  | PCFG3  | PCFG2  | PCFG1  | PCFG0  | 0000          |

| AD1CSSL   | 0330     | CSSL15     | CSSL14               | CSSL13         | CSSL12       | CSSL11        | CSSL10      | CSSL9     | CSSL8      | CSSL7      | CSSL6 | CSSL5 | CSSL4  | CSSL3  | CSSL2  | CSSL1  | CSSL0  | 0000          |

| Legend:   | — = unii | mplemented | l, read as 'o        | )', r = reserv | ved, maintai | in as '0'. Re | eset values | are shown | in hexadec | mal.       |       |       |        |        |        |        |        |               |

### TABLE 4-21: CTMU REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10   | Bit 9   | Bit 8  | Bit 7   | Bit 6    | Bit 5    | Bit 4   | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-----------|------|--------|--------|----------|--------|--------|----------|---------|--------|---------|----------|----------|---------|----------|----------|----------|----------|---------------|

| CTMUCON   | 033C | CTMUEN | _      | CTMUSIDL | TGEN   | EDGEN  | EDGSEQEN | IDISSEN | CTTRIG | EDG2POL | EDG2SEL1 | EDG2SEL0 | EDG1POL | EDG1SEL1 | EDG1SEL0 | EDG2STAT | EDG1STAT | 0000          |

| CTMUICON  | 033E | ITRIM5 | ITRIM4 | ITRIM3   | ITRIM2 | ITRIM1 | ITRIM0   | IRNG1   | IRNG0  |         | -        | _        | -       |          |          | —        | _        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### EXAMPLE 5-2: ERASING A PROGRAM MEMORY BLOCK (C LANGUAGE CODE)

| <pre>// C example using MPLAB C30     unsigned long progAddr = 0xXXXXXX;     unsigned int offset;</pre>                     | // Address of row to write                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| <pre>//Set up pointer to the first memory locati     TBLPAG = progAddr&gt;&gt;16;     offset = progAddr &amp; 0xFFFF;</pre> | on to be written<br>// Initialize PM Page Boundary SFR<br>// Initialize lower word of address |

| builtin_tblwtl(offset, 0x0000);                                                                                             | <pre>// Set base address of erase block // with dummy latch write</pre>                       |

| NVMCON = $0 \times 4042$ ;                                                                                                  | // Initialize NVMCON                                                                          |

| asm("DISI #5");                                                                                                             | <pre>// Block all interrupts with priority &lt;7 // for next 5 instructions</pre>             |

| builtin_write_NVM();                                                                                                        | // C30 function to perform unlock<br>// sequence and set WR                                   |

### EXAMPLE 5-3: LOADING THE WRITE BUFFERS (ASSEMBLY LANGUAGE CODE)

| <pre>MOV #0x4001, W0 ;<br/>MOV W0, NVMCON ; Initialize NVMCON<br/>; Set up a pointer to the first program memory location to be written<br/>; program memory selected, and writes enabled<br/>MOV #0x0000, W0 ;<br/>MOV W0, TBLPAG ; Initialize PM Page Boundary SFR<br/>MOV #0x6000, W0 ; An example program memory address<br/>; Perform the TBLWT instructions to write the latches<br/>; Oth_program_word<br/>MOV #LOW_WORD_0, W2 ;<br/>MOV #HIGH_BYTE_0, W3 ;<br/>TELWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0+1] ; Write PM high byte into program latch<br/>; Ist_program_word<br/>MOV #LOW_WORD_1, W2 ;<br/>MOV #HIGH_BYTE_1, W3 ;<br/>TELWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>; 2nd_program_word<br/>MOV #LOW_WORD_2, W2 ;<br/>MOV #HIGH_BYTE_2, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM low word into program latch<br/>; 2nd_program_word<br/>MOV #LOW_WORD_2, W2 ;<br/>MOV #HIGH_BYTE_2, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>TBLWTH W3, [W0++] ; Write PM low word into program latch<br/>; 63rd_program_word<br/>MOV #LOW_WORD_31, W2 ;<br/>MOV #HIGH_BYTE_31, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0] ; Write PM low word into program latch<br/>the the top top the program latch top top top the program latch top top the program latch top top top the top top top the program latch top top top the program latch top top top the program latch top top the top top top the program latch top top the program latch top top top top the program latch top top top top the program latch top top top top top the program latch top top top top top top top top top top</pre> | ; Set up NVMCC | ON for row programming operatio | ons                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------------------------|-----------------------------------------|

| <pre>; Set up a pointer to the first program memory location to be written<br/>; program memory selected, and writes enabled<br/>MOV #0x0000, W0 ;<br/>MOV #0x6000, W0 ; Initialize PM Page Boundary SFR<br/>MOV #0x6000, W0 ; An example program memory address<br/>; Perform the TBLWT instructions to write the latches<br/>; Oth_program_word<br/>MOV #LOW_WORD_0, W2 ;<br/>MOV #HIGH_BYTE_0, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTL W2, [W0] ; Write PM high byte into program latch<br/>TBLWTL W2, [W0] ; Write PM high byte into program latch<br/>TBLWTL W2, [W0] ; Write PM high byte into program latch<br/>TBLWTL W2, [W0] ; Write PM high byte into program latch<br/>TBLWTL W3, [W0++] ; Write PM high byte into program latch<br/>TBLWTL W2, [W0] ; Write PM high byte into program latch<br/>TBLWTL W2, [W0] ; Write PM high byte into program latch<br/>TBLWTL W2, [W0] ; Write PM high byte into program latch<br/>TBLWTL W3, [W0++] ; Write PM high byte into program latch<br/>TBLWTL W3, [W0++] ; Write PM high byte into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MOV            | #0x4001, W0                     | ;                                       |

| <pre>; program memory selected, and writes enabled<br/>MOV #0x0000, W0 ;<br/>MOV W0, TBLPAG ; Initialize PM Page Boundary SFR<br/>MOV #0x6000, W0 ; An example program memory address<br/>; Perform the TBLWT instructions to write the latches<br/>; Oth_program_word<br/>MOV #LOW_WORD_0, W2 ;<br/>MOV #HIGH_BYTE_0, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>TBLWTL W2, [W0] ; Write PM high byte into program latch<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>; 2nd_program_word<br/>MOV #LOW_WORD_2, W2 ;<br/>MOV #LOW_WORD_2, W2 ;<br/>MOV #LOW_WORD_2, W2 ;<br/>MOV #LOW_WORD_1 ; Write PM high byte into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>TBLWTL W2, [W0] ; Write PM high byte into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>TBLWTT W2, [W0] ; Write PM high byte into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>TBLWTL W2, [W0] ; Write PM high byte into program latch</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | MOV            | W0, NVMCON                      | ; Initialize NVMCON                     |

| <pre>MOV #0x0000, W0 ;<br/>MOV W0, TELPAG ; Initialize PM Page Boundary SFR<br/>MOV #0x6000, W0 ; An example program memory address<br/>Perform the TBLWT instructions to write the latches<br/>0th_program_word<br/>MOV #LOW_WORD_0, W2 ;<br/>MOV #HIGH_BYTE_0, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTL W3, [W0++] ; Write PM high byte into program latch<br/>TBLWTL W3, [W0++] ; Write PM high byte into program latch<br/>ist_program_word<br/>MOV #LOW_WORD_1, W2 ;<br/>MOV #HIGH_BYTE_1, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>TBLWTL W2, [W0] ; Write PM high byte into program latch<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>ist_program_word<br/>MOV #LOW_WORD_2, W2 ;<br/>MOV #HIGH_BYTE_2, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTL W3, [W0++] ; Write PM high byte into program latch<br/>ist_ist_ist_ist_ist_ist_ist_ist_ist_ist_</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ; Set up a poi | nter to the first program memo  | ory location to be written              |

| <pre>MOV W0, TELPAG ; Initialize PM Page Boundary SFR<br/>MOV #0x6000, W0 ; An example program memory address<br/>; Perform the TBLWT instructions to write the latches<br/>; Oth_program_word<br/>MOV #LOW_WORD_0, W2 ;<br/>MOV #HIGH_BYTE_0, W3 ;<br/>TELWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>; lst_program_word<br/>MOV #LOW_WORD_1, W2 ;<br/>MOV #HIGH_BYTE_1, W3 ;<br/>TELWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTL W2, [W0] ; Write PM high byte into program latch<br/>TBLWTL W3, [W0++] ; Write PM high byte into program latch<br/>; 2nd_program_word<br/>MOV #HIGH_BYTE_2, W3 ;<br/>TELWTL W2, [W0] ; Write PM low word into program latch<br/>; 2nd_program_word<br/>MOV #HIGH_BYTE_2, W3 ;<br/>TELWTL W2, [W0] ; Write PM low word into program latch<br/>; 63rd_program_word<br/>MOV #LOW_WORD_31, W2 ;<br/>MOV #HIGH_BYTE_31, W3 ;<br/>TELWTL W2, [W0] ; Write PM low word into program latch</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ; program memo | ory selected, and writes enable | ed                                      |

| <pre>MOV #0x6000, W0 ; An example program memory address ; Perform the TBLWT instructions to write the latches ; Oth_program_word     MOV #LOW_WORD_0, W2 ;     MOV #LIGH_BYTE_0, W3 ;     TBLWTL W2, [W0] ; Write PM low word into program latch     TBLWTH W3, [W0++] ; Write PM high byte into program latch     TBLWTL W2, [W0] ; Write PM low word into program latch     TBLWTL W2, [W0] ; Write PM low word into program latch     TBLWTL W2, [W0] ; Write PM low word into program latch     TBLWTL W2, [W0] ; Write PM low word into program latch     TBLWTL W2, [W0] ; Write PM high byte into program latch ; 2nd_program_word     MOV #LIGH_BYTE_2, W3 ;     TBLWTL W2, [W0] ; Write PM low word into program latch     TBLWTL W2, [W0] ; Write PM high byte into program latch     i     i     for a state of the program_word     MOV #LOW_WORD_31, W2 ;     MOV #LIGH_BYTE_31, W3 ;     TBLWTL W2, [W0] ; Write PM low word into program latch     i     to y = TBLWTL W2, [W0] ; Write PM low word into program latch     i     to y = TBLWTL W2, [W0] ; Write PM low word into program latch     to y = TBLWTL W2, [W0] ; Write PM low word into program latch     to y = TBLWTL W2, [W0] ; Write PM low word into program latch     to y = TBLWTL W2, [W0] ; Write PM low word into program latch     to y = TBLWTL W2, [W0] ; Write PM low word into program latch     to y = TBLWTL W2, [W0] ; Write PM low word into program latch     to y = TBLWTL W2, [W0] ; Write PM low word into program latch     to y = TBLWTL W2, [W0] ; Write PM low word into program latch     to y = TBLWTL W2, [W0] ; Write PM low word into program latch     to y = TBLWTL W2, [W0] ; Write PM low word into program latch     to y = TBLWTL W2, [W0] ; Write PM low word into program latch     to y = TBLWTL W2, [W0] ; Write PM low word into program latch     to y = TBLWTL W2, [W0] ; Write PM low word into program latch     to y = TBLWTL W2, [W0] ; Write PM low word into program latch     to y = TBLWTL W2, [W0] ; Write PM low word into program latch     to y = TBLWTL W2, [W0] ; Write PM low word into</pre>                                                           | MOV            | #0x0000, W0                     | ;                                       |

| <pre>; Perform the TBLWT instructions to write the latches<br/>; Oth_program_word</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | MOV            | W0, TBLPAG                      | ; Initialize PM Page Boundary SFR       |

| <pre>; Oth_program_word<br/>MOV #LOW_WORD_0, W2 ;<br/>MOV #HIGH_BYTE_0, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>; lst_program_word<br/>MOV #LOW_WORD_1, W2 ;<br/>MOV #LOW_WORD_1, W2 ;<br/>MOV #HIGH_BYTE_1, W3 ;<br/>TBLWTL W3, [W0++] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>; 2nd_program_word<br/>MOV #LOW_WORD_2, W2 ;<br/>MOV #HIGH_BYTE_2, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>; 63rd_program_word<br/>MOV #LOW_MORD_31, W2 ;<br/>MOV #HIGH_BYTE_31, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | MOV            | #0x6000, W0                     | ; An example program memory address     |

| <pre>MOV #LOW_WORD_0, W2 ;<br/>MOV #HIGH_BYTE_0, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>; lst_program_word<br/>MOV #LOW_WORD_1, W2 ;<br/>MOV #HIGH_BYTE_1, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>; 2nd_program_word<br/>MOV #LOW_WORD_2, W2 ;<br/>MOV #HIGH_BYTE_2, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>; 63rd_program_word<br/>MOV #LOW_WORD_31, W2 ;<br/>MOV #HIGH_BYTE_31, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ; Perform the  | TBLWT instructions to write th  | ne latches                              |

| <pre>MOV #HIGH_BYTE_0, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>; lst_program_word<br/>MOV #LOW_WORD_1, W2 ;<br/>MOV #HIGH_BYTE_1, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>; 2nd_program_word<br/>MOV #HIGH_BYTE_2, W2 ;<br/>MOV #HIGH_BYTE_2, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>; 63rd_program_word<br/>MOV #LOW_WORD_31, W2 ;<br/>MOV #HIGH_BYTE_31, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ; 0th_program_ | -                               |                                         |

| <pre>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>ist_program_word<br/>MOV #LOW_WORD_1, W2 ;<br/>MOV #HIGH_BYTE_1, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>; 2nd_program_word<br/>MOV #HIGH_BYTE_2, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM low word into program latch<br/>• • •<br/>• •<br/>• •<br/>• •<br/>• •<br/>• •<br/>• •<br/>• •<br/>• •</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | MOV            |                                 | ;                                       |

| <pre>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>; lst_program_word<br/>MOV #LOW_WORD_1, W2 ;<br/>MOV #HIGH_BYTE_1, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>; 2nd_program_word<br/>MOV #LOW_WORD_2, W2 ;<br/>MOV #HIGH_BYTE_2, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>•<br/>•<br/>•<br/>•<br/>; 63rd_program_word<br/>MOV #LOW_WORD_31, W2 ;<br/>MOV #HIGH_BYTE_31, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                |                                 | ;                                       |

| <pre>; lst_program_word<br/>MOV #LOW_WORD_1, W2 ;<br/>MOV #HIGH_BYTE_1, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>; 2nd_program_word<br/>MOV #LOW_WORD_2, W2 ;<br/>MOV #HIGH_BYTE_2, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>•<br/>•<br/>•<br/>•<br/>; 63rd_program_word<br/>MOV #LOW_WORD_31, W2 ;<br/>MOV #HIGH_BYTE_31, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                | ,                               |                                         |

| <pre>MOV #LOW_WORD_1, W2 ;<br/>MOV #HIGH_BYTE_1, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>? 2nd_program_word<br/>MOV #LOW_WORD_2, W2 ;<br/>MOV #HIGH_BYTE_2, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |                                 | ; Write PM high byte into program latch |

| <pre>MOV #HIGH_BYTE_1, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>? 2nd_program_word<br/>MOV #LOW_WORD_2, W2 ;<br/>MOV #HIGH_BYTE_2, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>•<br/>•<br/>•<br/>; 63rd_program_word<br/>MOV #LOW_WORD_31, W2 ;<br/>MOV #HIGH_BYTE_31, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                |                                 |                                         |

| <pre>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>; 2nd_program_word<br/>MOV #LOW_WORD_2, W2 ;<br/>MOV #HIGH_BYTE_2, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>•<br/>•<br/>•<br/>; 63rd_program_word<br/>MOV #LOW_WORD_31, W2 ;<br/>MOV #HIGH_BYTE_31, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                |                                 | ;                                       |

| <pre>TBLWTH W3, [W0++] ; Write PM high byte into program latch ; 2nd_program_word MOV #LOW_WORD_2, W2 ; MOV #HIGH_BYTE_2, W3 ; TBLWTL W2, [W0] ; Write PM low word into program latch TBLWTH W3, [W0++] ; Write PM high byte into program latch ; 63rd_program_word MOV #LOW_WORD_31, W2 ; MOV #HIGH_BYTE_31, W3 ; TBLWTL W2, [W0] ; Write PM low word into program latch</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |                                 | 1                                       |

| <pre>; 2nd_program_word<br/>MOV #LOW_WORD_2, W2 ;<br/>MOV #HIGH_BYTE_2, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>•<br/>•<br/>•<br/>; 63rd_program_word<br/>MOV #LOW_WORD_31, W2 ;<br/>MOV #HIGH_BYTE_31, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                | ,                               |                                         |

| <pre>MOV #LOW_WORD_2, W2 ;<br/>MOV #HIGH_BYTE_2, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>•<br/>•<br/>•<br/>; 63rd_program_word<br/>MOV #LOW_WORD_31, W2 ;<br/>MOV #HIGH_BYTE_31, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                | ,                               | ; Write PM high byte into program latch |

| <pre>MOV #HIGH_BYTE_2, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch<br/>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br/>; 63rd_program_word<br/>MOV #LOW_WORD_31, W2 ;<br/>MOV #HIGH_BYTE_31, W3 ;<br/>TBLWTL W2, [W0] ; Write PM low word into program latch</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                | —                               |                                         |

| TBLWTL W2, [W0] ; Write PM low word into program latch<br>TBLWTH W3, [W0++] ; Write PM high byte into program latch<br>; 63rd_program_word<br>MOV #LOW_WORD_31, W2 ;<br>MOV #HIGH_BYTE_31, W3 ;<br>TBLWTL W2, [W0] ; Write PM low word into program latch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |                                 | ;                                       |

| TBLWTH W3, [W0++] ; Write PM high byte into program latch<br>; 63rd_program_word<br>MOV #LOW_WORD_31, W2 ;<br>MOV #HIGH_BYTE_31, W3 ;<br>TBLWTL W2, [W0] ; Write PM low word into program latch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |                                 |                                         |

| •<br>•<br>•<br>; 63rd_program_word<br>MOV #LOW_WORD_31, W2 ;<br>MOV #HIGH_BYTE_31, W3 ;<br>TBLWTL W2, [W0] ; Write PM low word into program latch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |                                 |                                         |

| MOV#LOW_WORD_31, W2;MOV#HIGH_BYTE_31, W3;TBLWTLW2, [W0];WritePM low word into program latch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | TBLWTH         | W3, [W0++]                      | ; Write PM high byte into program latch |